Académique Documents

Professionnel Documents

Culture Documents

FX2 MIB - RM - RevA

Transféré par

Alberto Chillon NavarreteTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

FX2 MIB - RM - RevA

Transféré par

Alberto Chillon NavarreteDroits d'auteur :

Formats disponibles

F FX X2 2 M MI IB B

R Re ef fe er re en nc ce e M Ma an nu ua al l

www. di gi l ent i nc. com

Revision: January 14, 2009

Note: This document applies to REV A of the board.

215 E Main Suite D | Pullman, WA 99163

(509) 334 6306 Voice and Fax

Doc: 502-161 page 1 of 4

Copyright Digilent, Inc. All rights reserved. Other product and company names mentioned may be trademarks of their respective owners.

Overview

The Digilent FX2 Module Interface Board (MIB)

offers a ready-made solution for interfacing

peripheral modules to Digilent system boards.

Features include:

FX2 peripheral board connector

four 12-pin and two 6-pin Pmod

connectors

access to JTAG scan chain

access to signals for test points

provision for oscillator for clock input to

system board

Functional Description

Power Connections

The FX2 MIB provides two power busses and

a ground bus. The two power busses are

labeled VCC and VCCFX2. These two busses

are made available at each connector position

on the board. There is also a ground plane that

connects the ground pins from all connectors.

The usual Digilent convention is to power the

VCC bus at 3.3V and the VCCFX2 bus at 5.0V.

However, depending on the system board

connected and the power supply used, other

voltages may be present. Use caution when

using any voltage other than 3.3V on the VCC

bus. Most Digilent system boards will be

damaged if the voltage on the VCC bus is

greater than 3.3V.

FX2 connector J10 is provided on one side of

the board for connection to Digilent system

boards, like the Nexys2, that contain an FX2-

style connector. The Digilent FX2 connector

signal convention provides for forty general-

purpose I/O signals, three clock signals, JTAG

signals, and power busses.

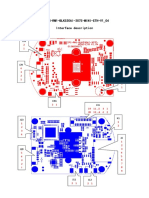

FX2 MIB Block Diagram

Digilent, Inc.

FX2 MIB Reference Manual

www.digilentinc.com

www.digilentinc.com page 2 of 4

Copyright Digilent, Inc. All rights reserved. Other product and company names mentioned may be trademarks of their respective owners.

The forty general-purpose I/O signals from the

FX2 connector are brought out to connector

J7. These signals are labeled IO1-IO40. See

Table 1 for a description of the relationship

between FX2 connector pins and signal names

on J7. The remaining signals from the FX2

connector are brought out to connectors J8,

J9, J11, and J12. See Table 1 for a description

of the relationship between FX2 connector pins

and connectors J8 and J9 signal names.

In addition to the FX2 connector signals,

connector J11 and J12 also provide access to

the power and ground busses.

Pmod Connectors

Digilent Pmods provide various peripheral

functions. These can be as simple as buttons

or switches for inputs and LEDs for outputs, or

as complex as graphical LCD display panels,

accelerometers, and keypads.

All Digilent Pmods use either a six-wire

interface or a twelve-wire interface. The six-

wire interface provides four I/O signals, power,

and ground. The twelve-wire interface provides

eight I/O signals, two powers, and two

grounds. The signal definitions for the I/O

signals as well as the voltage requirements for

the power supply depend on the specific

module.

The FX2 MIB provides four twelve-pin and two

six-pin Pmod connectors.

The twelve-pin connector provides access

such that the top set of four pins are the odd

labeled signals while the bottom set are even

labeled signals. See Table 2.

The signals for Pmod connectors J1-J6 are

brought out to connector J7. These signals are

labeled IO1-IO40.

Each Pmod connector has an associated

power select jumper. The power select jumper

for J1 is JP1, and so on. These jumpers are

used to select one of the two power busses on

the FX2 MIB to provide power to the power

supply pin on a Pmod plugged into that

connector position. Placing a shorting block in

the 3V3 position provides VCC power to the

Pmod. Placing a shorting block in the 5V0

position provides VCCFX2 power to the Pmod.

Place a shorting block so that it hangs off of

the center pin only to disconnect power to the

Pmod.

FPGA Configuration

The FX2 MIB provides JTAG access via

unloaded jumper J9. Given that the jumper

JP7 labeled JTSEL is shorted, this jumper

allows a connected board to be programmed

via a JTAG cable.

See Table 1 for a description of the

relationship between the FX2 connector pins

and the connections on the JTAG jumper J9.

Clocks

The FX2 MIB provides an oscillator clock input

to a system board via socket connector IC1.

This socket can be used to input a clock signal

to a system board when an external oscillator

is placed on it. It will then output a clock signal

on the CLKIO pin of the FX2 connector.

The unloaded jumper J8 provides access to all

possible clock signals into and out of the FX2

MIB. This includes the signal CLKIO from the

external oscillator socket connector as well as

CLKIO and CLKOUT signals directly from the

FX2 connector.

See Table1 for more details.

Digilent, Inc.

FX2 MIB Reference Manual

www.digilentinc.com

www.digilentinc.com page 3 of 4

Copyright Digilent, Inc. All rights reserved. Other product and company names mentioned may be trademarks of their respective owners.

Table 1 FX2 Signals and Connector Pinout

A Pinout B Pinout

1 VCC 1 SHLD

2 VCC 2 GND

3 TMS 3 TDI

4 JTSEL 4 TCK

5 TDO 5 GND

6 IO1 6 GND

7 IO2 7 GND

8 IO3 8 GND

9 IO4 9 GND

10 IO5 10 GND

11 IO6 11 GND

12 IO7 12 GND

13 IO8 13 GND

14 IO9 14 GND

15 IO10 15 GND

16 IO11 16 GND

17 IO12 17 GND

18 IO13 18 GND

19 IO14 19 GND

20 IO15 20 GND

21 IO16 21 GND

22 IO17 22 GND

23 IO18 23 GND

24 IO19 24 GND

25 IO20 25 GND

26 IO21 26 GND

27 IO22 27 GND

28 IO23 28 GND

29 IO24 29 GND

30 IO25 30 GND

31 IO26 31 GND

32 IO27 32 GND

33 IO28 33 GND

34 IO29 34 GND

35 IO30 35 GND

36 IO31 36 GND

37 IO32 37 GND

38 IO33 38 GND

39 IO34 39 GND

40 IO35 40 GND

41 IO36 41 GND

42 IO37 42 GND

43 IO38 43 GND

44 IO39 44 GND

45 IO40 45 GND

46 GND 46 CLKIN

47 CLKOUT 47 GND

48 GND 48 CLKIO

49 VU 49 VU

50 VU 50 SHLD

Digilent, Inc.

FX2 MIB Reference Manual

www.digilentinc.com

www.digilentinc.com page 4 of 4

Copyright Digilent, Inc. All rights reserved. Other product and company names mentioned may be trademarks of their respective owners.

Table 2 Pmod Connector Pin Layouts

J1 Top Set of Pins

Pin Pinout

1 IO1

2 IO3

3 IO5

4 IO7

5 GND

6 VDD

J2 Top Set of Pins

Pin Pinout

1 IO9

2 IO11

3 IO13

4 IO15

5 GND

6 VDD

J3 Top Set of Pins

Pin Pinout

1 IO17

2 IO19

3 IO21

4 IO23

5 GND

6 VDD

J4 Top Set of Pins

Pin Pinout

1 IO25

2 IO27

3 IO29

4 IO31

5 GND

6 VDD

J5 Pins

Pin Pinout

1 IO33

2 IO34

3 IO35

4 IO36

5 GND

6 VDD

J1 Bottom Set of Pins

Pin Pinout

7 IO2

8 IO4

9 IO6

10 IO8

11 GND

12 VDD

J2 Bottom Set of Pins

Pin Pinout

7 IO10

8 IO12

9 IO14

10 IO16

11 GND

12 VDD

J3 Bottom Set of Pins

Pin Pinout

7 IO18

8 IO20

9 IO22

10 IO24

11 GND

12 VDD

J4 Bottom Set of Pins

Pin Pinout

7 IO26

8 IO28

9 IO30

10 IO32

11 GND

12 VDD

J6 Pins

Pin Pinout

1 IO37

2 IO38

3 IO39

4 IO40

5 GND

6 VDD

Vous aimerez peut-être aussi

- Nissan Serena c24 Repair Manual IndexDocument18 pagesNissan Serena c24 Repair Manual IndexAditya Pratama0% (2)

- PC 2 Route For Mach Rev 1-9Document18 pagesPC 2 Route For Mach Rev 1-9Kenn FerroPas encore d'évaluation

- P091 084 Ioiscm Um 1105Document30 pagesP091 084 Ioiscm Um 1105Badescu Ionut100% (1)

- RT Box Launchpad Interface: User Manual May 2020Document30 pagesRT Box Launchpad Interface: User Manual May 2020Shanon RustoffPas encore d'évaluation

- IDBS07 and IDBM07 Wiring Manual: February 2008Document16 pagesIDBS07 and IDBM07 Wiring Manual: February 2008phankhoa83-1Pas encore d'évaluation

- Z TurnboardDocument9 pagesZ Turnboardjobey erfeePas encore d'évaluation

- Esp32 PDFDocument5 pagesEsp32 PDFIrfan ZuhriPas encore d'évaluation

- JUMPtec Intelligent LVDS InterfaceDocument11 pagesJUMPtec Intelligent LVDS InterfaceDalek SkaroPas encore d'évaluation

- 42LK520 LVDS Interconnect DiagramDocument7 pages42LK520 LVDS Interconnect DiagramErnesto SuarezPas encore d'évaluation

- RSR Electronics Pldt-2 User'S Manual Ver 1.08Document19 pagesRSR Electronics Pldt-2 User'S Manual Ver 1.08Matthew TowerPas encore d'évaluation

- LS6410 S3C6410 ARM11 Core BoardDocument20 pagesLS6410 S3C6410 ARM11 Core BoardTRIGUN-XPas encore d'évaluation

- Launchpad f28027ptt Pinout PDFDocument2 pagesLaunchpad f28027ptt Pinout PDFNathanael Günter PrangePas encore d'évaluation

- Student's ManualDocument69 pagesStudent's ManualMichael CagaoanPas encore d'évaluation

- Basic Digital Circuits: 1 Logic Gates and CircuitsDocument18 pagesBasic Digital Circuits: 1 Logic Gates and CircuitsssfofoPas encore d'évaluation

- BotboarduinomanualDocument8 pagesBotboarduinomanualAlvaroPas encore d'évaluation

- HDBB2 ManualDocument14 pagesHDBB2 ManualJonathan Louie PondaraPas encore d'évaluation

- User'S Manual User'S Manual: 1. ApplicationDocument4 pagesUser'S Manual User'S Manual: 1. ApplicationAhmed TalaatPas encore d'évaluation

- 2533EK2Document8 pages2533EK2daviPas encore d'évaluation

- P091 084 Ioibl UmDocument22 pagesP091 084 Ioibl UmamappsPas encore d'évaluation

- JZC 80X50PSB RG Interface DescriptionDocument5 pagesJZC 80X50PSB RG Interface DescriptionyatnierPas encore d'évaluation

- Zybo ™ FPGA Board Reference Manual: Revised April 11, 2016 This Manual Applies To The ZYBO Rev. BDocument26 pagesZybo ™ FPGA Board Reference Manual: Revised April 11, 2016 This Manual Applies To The ZYBO Rev. BRykudou ZudynPas encore d'évaluation

- PO-2033C LCD Panel Controller Board Support TTL & LVDS Panel For 4.3" 22" Digital LCD PanelDocument12 pagesPO-2033C LCD Panel Controller Board Support TTL & LVDS Panel For 4.3" 22" Digital LCD Panelamir rudinPas encore d'évaluation

- Контроллер MESA 6I25-SPDocument20 pagesКонтроллер MESA 6I25-SPandriiPas encore d'évaluation

- Infineon Tle7230r Ds v03 04 enDocument15 pagesInfineon Tle7230r Ds v03 04 enياسين الطنفوريPas encore d'évaluation

- PCBs Frontal A320 Eng V1.0Document12 pagesPCBs Frontal A320 Eng V1.0veronlePas encore d'évaluation

- Junebug PiCKIT2Document12 pagesJunebug PiCKIT2wos22100% (1)

- Electronic Keyboard Troubleshooting GuideDocument28 pagesElectronic Keyboard Troubleshooting GuidegachichuPas encore d'évaluation

- MinimaConstructionGuide R7Document65 pagesMinimaConstructionGuide R7fox7878100% (1)

- DSASL0037380Document40 pagesDSASL0037380Yaseen GhulamPas encore d'évaluation

- LM220WE4Document8 pagesLM220WE4acostaricciPas encore d'évaluation

- TMPA 8823-5VA4 Service Manual: IC Functions and I2C Bus ControlDocument16 pagesTMPA 8823-5VA4 Service Manual: IC Functions and I2C Bus ControlAndy AnsahPas encore d'évaluation

- Ec49222 e Cmos PDFDocument19 pagesEc49222 e Cmos PDFKiinhooPas encore d'évaluation

- Quick Tip: Serial Protocol Converter 2.5 (SPC2.5) Quick ReferenceDocument2 pagesQuick Tip: Serial Protocol Converter 2.5 (SPC2.5) Quick ReferenceSergio Augusto Correa FierroPas encore d'évaluation

- StreamCaster 4400 OEM Integration Manual v1.0Document9 pagesStreamCaster 4400 OEM Integration Manual v1.0236251457.hcPas encore d'évaluation

- Anykits MagazineDocument45 pagesAnykits Magazinemaniarchadan100% (1)

- 8 Channel PWM LED ChaserDocument11 pages8 Channel PWM LED Chaserkagemaruokami100% (1)

- 4channel RemoteDocument15 pages4channel Remoteryan cooperPas encore d'évaluation

- T 69 B 1Document3 pagesT 69 B 1seiscincocerodosPas encore d'évaluation

- Wireles S Home Security System: R.N. Modi Engineering College, KotaDocument17 pagesWireles S Home Security System: R.N. Modi Engineering College, KotaUtkarsh BhaskarPas encore d'évaluation

- Pines CPLD4 PDFDocument8 pagesPines CPLD4 PDFJOSE LENIN RIVERA VILLALOBOSPas encore d'évaluation

- Users Manual 1249702Document15 pagesUsers Manual 1249702Faber Alexis Maldonado PembertyPas encore d'évaluation

- Tpm4.1ela 689Document64 pagesTpm4.1ela 689fvictor1Pas encore d'évaluation

- All in One PCB v3.2 by Synthex - Quick ManualDocument6 pagesAll in One PCB v3.2 by Synthex - Quick ManualNatacha GonzalezPas encore d'évaluation

- Philips Chassis Tpm6.1e LaDocument112 pagesPhilips Chassis Tpm6.1e LatarpinoPas encore d'évaluation

- JZC 80X30PSB RG Interface DescriptionDocument6 pagesJZC 80X30PSB RG Interface DescriptionAkhiroedinPas encore d'évaluation

- ARM STM32F107 Development Board ManualDocument66 pagesARM STM32F107 Development Board ManualTiago AveiroPas encore d'évaluation

- Descripcion Partes Mini2440EssentialsDocument20 pagesDescripcion Partes Mini2440EssentialsFernando EspañaPas encore d'évaluation

- ChipKIT Uno32 JumpersDocument2 pagesChipKIT Uno32 Jumpersyanuar1976Pas encore d'évaluation

- LPC2148 EbookDocument89 pagesLPC2148 Ebookkarthikeyan_mani1987Pas encore d'évaluation

- TV Led Philips Chassi LC9.2LADocument85 pagesTV Led Philips Chassi LC9.2LAJandira Santos0% (1)

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSID'EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIPas encore d'évaluation

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsD'EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsÉvaluation : 3 sur 5 étoiles3/5 (2)

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysD'EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysPas encore d'évaluation

- Diode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesD'EverandDiode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesÉvaluation : 4.5 sur 5 étoiles4.5/5 (7)

- Exploring Arduino: Tools and Techniques for Engineering WizardryD'EverandExploring Arduino: Tools and Techniques for Engineering WizardryÉvaluation : 4.5 sur 5 étoiles4.5/5 (5)

- 1641689Document62 pages1641689Alberto Chillon NavarretePas encore d'évaluation

- Sh080891engf MELSEC-L CPU Module User's Manual (Built-In Ethernet Function)Document146 pagesSh080891engf MELSEC-L CPU Module User's Manual (Built-In Ethernet Function)Alberto Chillon NavarretePas encore d'évaluation

- 2060 402Document1 page2060 402Alberto Chillon NavarretePas encore d'évaluation

- Main CofDocument32 pagesMain CofAlberto Chillon NavarretePas encore d'évaluation

- High Current Plugs Marechal 75A 700A Power Connector Plugs Sockets DecontactorsDocument16 pagesHigh Current Plugs Marechal 75A 700A Power Connector Plugs Sockets DecontactorsmagnodiasfarahPas encore d'évaluation

- Pressure MechanicalDocument67 pagesPressure MechanicalDian PramadiPas encore d'évaluation

- 1.81.90801 TSG Safety Door OperatorDocument1 page1.81.90801 TSG Safety Door OperatorMario NascimentoPas encore d'évaluation

- Kas 150 PDFDocument11 pagesKas 150 PDFvladimir2426Pas encore d'évaluation

- Lifepak CR Plus and Lifepak Express Defibrillators: User's ChecklistDocument2 pagesLifepak CR Plus and Lifepak Express Defibrillators: User's ChecklistLuis EsparzaPas encore d'évaluation

- Machine Stop Alarms and Door IssuesDocument49 pagesMachine Stop Alarms and Door IssuesSalva Petanas EstebanPas encore d'évaluation

- X Cube Lift: Model: XCU 600 XCU 700 Installation InstructionsDocument26 pagesX Cube Lift: Model: XCU 600 XCU 700 Installation InstructionsMohit ComputerPas encore d'évaluation

- Vi Physics WorksheetDocument4 pagesVi Physics WorksheetpodhigaifarmPas encore d'évaluation

- LIELBA EdibonDocument27 pagesLIELBA EdibondondidendiPas encore d'évaluation

- Grade 9 (SPTVE) CSS (1) Diagnostic TestDocument6 pagesGrade 9 (SPTVE) CSS (1) Diagnostic TestGODSLEE SUACILLOPas encore d'évaluation

- All Wiring Diagrams For Nissan Sentra CA 2002Document63 pagesAll Wiring Diagrams For Nissan Sentra CA 2002tellossaposPas encore d'évaluation

- Kalimat Nominal Negative (-)Document5 pagesKalimat Nominal Negative (-)Amelia RamadhaniPas encore d'évaluation

- LT 1055 SuperestruturaDocument132 pagesLT 1055 SuperestruturaHernan Reyes CarbonellPas encore d'évaluation

- User's Manual: Professional Rack Mount LCD Series PR3000ELCDRT2UDocument61 pagesUser's Manual: Professional Rack Mount LCD Series PR3000ELCDRT2UMANAN BELANIPas encore d'évaluation

- Valvulas Conexion Hammer CWPDocument56 pagesValvulas Conexion Hammer CWPALEXIS CASTILLAPas encore d'évaluation

- Bodas Temperature Sensor For Fluid TSF: Replaces: 07.06Document2 pagesBodas Temperature Sensor For Fluid TSF: Replaces: 07.06Irina VarzouPas encore d'évaluation

- M3.6-Pure Solar-Add 3xZXD3000+3tech DG+DCPD7 and LTE-M3.6-Pure Solar Add 3xZXD3000+3techDG+2xMCB - 20181129 - V1.0Document26 pagesM3.6-Pure Solar-Add 3xZXD3000+3tech DG+DCPD7 and LTE-M3.6-Pure Solar Add 3xZXD3000+3techDG+2xMCB - 20181129 - V1.0Kyaw Kyaw WinPas encore d'évaluation

- Fujitsu-General LM Series 2013Document8 pagesFujitsu-General LM Series 2013Dejan JovanovicPas encore d'évaluation

- Emergency Fairlite LightingDocument3 pagesEmergency Fairlite LightingawadalmekawyPas encore d'évaluation

- Color Image Reader-L1 SM 021909Document83 pagesColor Image Reader-L1 SM 021909RAFTELPas encore d'évaluation

- Bedhboperation r41 FRDocument229 pagesBedhboperation r41 FRBen Aissa ChokriPas encore d'évaluation

- Truth Hardware Accessory ItemsDocument6 pagesTruth Hardware Accessory ItemsWindow HardwarePas encore d'évaluation

- Service Manual: DEH-P3500MPDocument69 pagesService Manual: DEH-P3500MPRenatoMaiaPas encore d'évaluation

- Wildlife PhotographyDocument22 pagesWildlife PhotographyFabio LopesPas encore d'évaluation

- Manual de Partes Gestetner 2713Document194 pagesManual de Partes Gestetner 2713desechablePas encore d'évaluation

- Electrical Wiring InstallationDocument11 pagesElectrical Wiring InstallationDurrahKhazalle100% (26)

- Emergency Showers G1691: Guardian EquipmentDocument2 pagesEmergency Showers G1691: Guardian Equipmenteisenbarger5607Pas encore d'évaluation

- Filehost - KONICA MINOLTA BizHub 163, 211, 220 Field Service ManualDocument563 pagesFilehost - KONICA MINOLTA BizHub 163, 211, 220 Field Service ManualCalin Ciurdas100% (3)

- General Procedures For Escalators & Moving Walkways - Doc-1Document2 pagesGeneral Procedures For Escalators & Moving Walkways - Doc-1Bartz SantosPas encore d'évaluation