Académique Documents

Professionnel Documents

Culture Documents

Cse590490 HW2

Transféré par

Adip ChyDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Cse590490 HW2

Transféré par

Adip ChyDroits d'auteur :

Formats disponibles

CSE 490/590 Homework2 Spring 2014

Section 1:

1. This exercise is intended to help you understand the relationship between

delay slots, control hazards, and branch execution in a pipelined processor. In this

exercise, we assume that the following MIPS code is executed on a pipelined

processor with a fivestage pipeline, full forwarding and a predicttaken branch

predictor:

a. Label 1: lw $1,40 ($6)

beq $2, $3, Label 2 : Taken

add $1, $6, $4

Label 2: beq $1, $2, Label 1 : Not taken

sw $2, 20 ($4)

and $1, $1, $4

b. add $1, $5, $3

Label 1: sw $1, 0 ($2)

add $2, $2, $3

beq $2, $4, Label 1 : Not taken

add $5, $5, $1

sw $1, 0 ($2)

Draw the pipeline execution diagram for this code, assuming there are no delay slots and

that branches execute in the EX stage.

2. Assume that we have a multiple-issue pipelined processor with the following number of

pipeline stages, instructions issued per cycle, stage in which branch outcomes are resolved,

and branch predictor accuracy:

Pipeline Issue Width Branches execute in Branch Predictor Branches as a % of

Depth stage accuracy instructions

a. 10 4 7 80% 20%

b. 25 2 17 92% 25%

Control hazards can be eliminated by adding branch delay slots. How many delay slots must

follow each branch if we want to eliminate all control hazards in this processor?

3. This exercise examines how exception handling interacts with branch and load/store

instructions. Problems in this exercise refer to the following branch instruction and the

corresponding delay slot instruction:

Branch and delay slot

a. beq $1, $0, Label

sw $6, 50 ($1)

b. beq $5, $0, Label

nor $5, $4, $3

a. Assume that this branch is correctly predicted as taken, but then the instruction at

Label is an undefined instruction. Describe what is done in each pipeline stage for

each cycle, starting with the cycle in which the branch is decoded up to the cycle in

which the first instruction of the exception handle is fetched.

b. Repeat Exercise 3.1, but this time assume that the instruction in the delay slot also

causes a hardware error exception when it is in MEM stage.

c. What is the value in the EPC if the branch is taken but the delay slot causes an

exception? What happens after the execution of the exception handler is completed?

Section 2:

1. We have a program core consisting of five conditional branches. The program core will be

executed thousands of times. Below are the outcomes of each branch for one execution of the

program core (T for taken, N for not taken).

Branch 1: T - T - T

Branch 2: N - N - N N

Branch 3: T N T N T N

Branch 4: T T T N T

Branch 5: T T N T T N T

Assume the behavior of each branch remains the same for each program core execution. For

dynamic schemes, assume each branch has its own prediction buffer and each buffer initialized to

the same state before each execution. List the predictions for the following branch prediction

schemes:

A. Always taken

B. Always not taken

C. 1-bit predictor, initialized to predict taken

D. 2-bit predictor, initialized to weakly predict taken

What are the prediction accuracies? [15 points]

2. In this exercise, we make several assumptions. First, we assume that an Nissue superscalar

processor can execute any N instructions in the same cycle, regardless of their types. Second, we

assume that every instruction is independently chosen, without regard for the instruction that

precedes or follows it. Third, we assume that there are no stalls due to data dependences that

no delay slots are used, and that branches execute in the EX stage of the pipeline. Finally, we

assume that instructions executed in the program are distributed as follows:

ALU Correctly predicted beq Incorrectly predicted beq lw sw

a. 50% 18% 2% 20% 10%

b. 40% 10% 5% 35% 15%

a. What is the CPI achieved by a 2-issue static superscalar processor on this program?

b. In a 2-issue static superscalar processor that only has one register write port, what speedup is

achieved by adding a second register write port?

c. For a 2-issue static superscalar processor with a classic five-stage pipeline, what speed-up is

achieved by making the branch prediction perfect?

d. Repeat exercise C, but for a 4-issue processor. What conclusion can you draw about the importance

of good branch prediction when the issue width of the processor is increased?

3. Here is a series of address references given as word addresses: 2, 3, 11, 16, 21, 13, 64, 48, 19,

11, 3, 22, 4, 27, 6 and 11. Using the series references show the hits and misses and the final cache

contents for a direct-mapped cache with four-word blocks and a total size of 16 words.

4.

lw $1, 40($6)

beq $2, $0, Label ; Assume $2 = $0

sw $6, 50($2)

Label: add $2, $3, $4

sw $3, 50($4)

a. For this problem, assume that all branches are perfectly predicted, eliminating all control hazards,

and that no delay slots are used. If we change load/store instructions to use a register without an

offset as the address, these instructions no longer need to use the ALU. As a result, MEM and EX

can be overlapped and the pipeline has only 4 stages. Change the code to accommodate this

changed ISA. Assuming this change does not affect clock cycle time, what speedup is achieved in

this instruction sequence?

b. Assuming stall on branch and no delay slots, what speedup is achieved on this code if branch

outcomes are determined in the ID stage, relative to the execution where branch outcomes are

determined in the EX stage?

Vous aimerez peut-être aussi

- Revision Questions 2Document4 pagesRevision Questions 2tinhtrilacPas encore d'évaluation

- 491 Part%2B1%2B-%2BTareaDocument3 pages491 Part%2B1%2B-%2BTareaDiana PanchanaPas encore d'évaluation

- Sample Problems Pipe&MemoryDocument57 pagesSample Problems Pipe&Memoryacc1444Pas encore d'évaluation

- CO Assignment 4 SolutionDocument10 pagesCO Assignment 4 SolutionMuhammadShazaibPas encore d'évaluation

- M116C 1 EE116C-Midterm2-w15 SolutionDocument8 pagesM116C 1 EE116C-Midterm2-w15 Solutiontinhtrilac100% (1)

- Tuesday, October 31, 2023 10:53 PM: Discuss, The Schemes For Dealing With The Pipeline Stalls Caused by Branch HazardsDocument7 pagesTuesday, October 31, 2023 10:53 PM: Discuss, The Schemes For Dealing With The Pipeline Stalls Caused by Branch Hazardskrahul74714Pas encore d'évaluation

- Ca CT2Document4 pagesCa CT2krahul74714Pas encore d'évaluation

- Computer Organization: An Introduction To RISC Hardware: 6.1 An Overview of PipeliningDocument12 pagesComputer Organization: An Introduction To RISC Hardware: 6.1 An Overview of PipeliningAmrendra Kumar MishraPas encore d'évaluation

- Homework Set - 5Document2 pagesHomework Set - 5tinhtrilacPas encore d'évaluation

- Instruction Level Parallelism: PipeliningDocument6 pagesInstruction Level Parallelism: PipeliningkbkkrPas encore d'évaluation

- Computer Science 37 Lecture 22Document14 pagesComputer Science 37 Lecture 22Alexander TaylorPas encore d'évaluation

- High Performance Computer Architecture (CS60003)Document2 pagesHigh Performance Computer Architecture (CS60003)Venkata PranavPas encore d'évaluation

- CS60003 High Performance Computer ArchitectureDocument3 pagesCS60003 High Performance Computer ArchitectureNarayan KunalPas encore d'évaluation

- Comparch Comparch-002 Exams Midterm A8Xj46NCRoDocument9 pagesComparch Comparch-002 Exams Midterm A8Xj46NCRoMattia LePas encore d'évaluation

- Indian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Document4 pagesIndian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Utkarsh PatelPas encore d'évaluation

- Assignment5 SolnDocument5 pagesAssignment5 Solnshantanu pathakPas encore d'évaluation

- hw5 SolnDocument4 pageshw5 SolnThanh TrúcPas encore d'évaluation

- EE352 HW3 Nazarian Spring10Document8 pagesEE352 HW3 Nazarian Spring10skdejhloiewPas encore d'évaluation

- CS151B/EE116C Homework 6Document2 pagesCS151B/EE116C Homework 6tinhtrilacPas encore d'évaluation

- Ecen 324 Practice Exam: Midterm #2: Int Unknown (A B && B C: B B A && A C: A 1: C )Document5 pagesEcen 324 Practice Exam: Midterm #2: Int Unknown (A B && B C: B B A && A C: A 1: C )ThatOnePerson123Pas encore d'évaluation

- Mit VliwDocument30 pagesMit VliwjahPas encore d'évaluation

- Integrating The Timing Analysis of Pipelining and Instruction CachingDocument11 pagesIntegrating The Timing Analysis of Pipelining and Instruction CachingRohan T ReddyPas encore d'évaluation

- Sheet7 SolutionDocument11 pagesSheet7 SolutionMd. Imran AhmedPas encore d'évaluation

- CENG400-Final-Fall 2014Document11 pagesCENG400-Final-Fall 2014Mohamad IssaPas encore d'évaluation

- Exam2 Fa2014 SolutionDocument14 pagesExam2 Fa2014 Solutionrafeak rafeakPas encore d'évaluation

- National University of Computer and Emerging Sciences, Lahore CampusDocument4 pagesNational University of Computer and Emerging Sciences, Lahore CampusxxxPas encore d'évaluation

- Proj2 Report-1-1Document13 pagesProj2 Report-1-1api-697702568Pas encore d'évaluation

- Ovn MainDocument54 pagesOvn MainAvenir BajraktariPas encore d'évaluation

- CS433 hw1 Fall 07Document3 pagesCS433 hw1 Fall 0798140207Pas encore d'évaluation

- Chapter 1Document42 pagesChapter 1JaiPas encore d'évaluation

- Computer Architecture hw6Document3 pagesComputer Architecture hw6Jason WheelerPas encore d'évaluation

- Lab 2: Modifying Legup To Limit The Number of Hardware Functional UnitsDocument8 pagesLab 2: Modifying Legup To Limit The Number of Hardware Functional UnitsSuresh KumarPas encore d'évaluation

- Table 1: Control Signals and OpcodesDocument6 pagesTable 1: Control Signals and Opcodesxzlosx1999Pas encore d'évaluation

- NDocument4 pagesNAzri Mohd Khanil0% (1)

- Ayson Lab8Document9 pagesAyson Lab8Crisha Ken AysonPas encore d'évaluation

- VLSI Interview QuestionsDocument7 pagesVLSI Interview QuestionsVlsi GuruPas encore d'évaluation

- Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. Lipasti PDFDocument5 pagesSolution Manual For Modern Processor Design by John Paul Shen and Mikko H. Lipasti PDFtargeties0% (1)

- BFE Final Organization Fall 2014 AnswerDocument8 pagesBFE Final Organization Fall 2014 AnswerArpan DesaiPas encore d'évaluation

- CSC 424 AssignmentDocument8 pagesCSC 424 AssignmentBalsesbiz Consults100% (1)

- Instructions: Csce 212: Final Exam Spring 2009Document5 pagesInstructions: Csce 212: Final Exam Spring 2009NapsterPas encore d'évaluation

- 06 Solutions For Chapter 6 ExercisesDocument14 pages06 Solutions For Chapter 6 ExercisesSyed Zeshan AliPas encore d'évaluation

- Ebook Computer Organization and Design 5Th Edition Patterson Test Bank Full Chapter PDFDocument42 pagesEbook Computer Organization and Design 5Th Edition Patterson Test Bank Full Chapter PDFjoanneesparzagwjxmyqont100% (11)

- Lab 11 Hannan Mazin WajahatDocument8 pagesLab 11 Hannan Mazin WajahatHannan AamirPas encore d'évaluation

- CENG400 Midterm Fall 2015Document10 pagesCENG400 Midterm Fall 2015Mohamad IssaPas encore d'évaluation

- Comp Architecture Sample QuestionsDocument9 pagesComp Architecture Sample QuestionsMohamaad SihatthPas encore d'évaluation

- Cs2106 1617s1 Midterm SolutionDocument13 pagesCs2106 1617s1 Midterm SolutionReynard ArdianPas encore d'évaluation

- Ebook Computer Organization and Design Mips Edition 5Th Edition Patterson Solutions Manual Full Chapter PDFDocument43 pagesEbook Computer Organization and Design Mips Edition 5Th Edition Patterson Solutions Manual Full Chapter PDFjoanneesparzagwjxmyqont100% (9)

- Assignment QuestionsDocument3 pagesAssignment QuestionsSarbendu PaulPas encore d'évaluation

- Solution Assignment No 2Document8 pagesSolution Assignment No 2Mian EjazPas encore d'évaluation

- KTMT AssignmentsDocument3 pagesKTMT AssignmentsNguyên NguyễnPas encore d'évaluation

- Assignment - 1Document4 pagesAssignment - 1ZAEEM SULTAN KHAN0% (1)

- Nmam Institute of Technology: Department of Computer Science and EngineeringDocument8 pagesNmam Institute of Technology: Department of Computer Science and Engineeringsmitha shettyPas encore d'évaluation

- Homework 2Document8 pagesHomework 2Deepak BegrajkaPas encore d'évaluation

- Midterm s09 SolutionDocument12 pagesMidterm s09 SolutionIsmail MabroukPas encore d'évaluation

- COE301 Final Solution 162Document10 pagesCOE301 Final Solution 162Karim IbrahimPas encore d'évaluation

- Ripple Carry and Carry Lookahead Adders: 1 ObjectivesDocument7 pagesRipple Carry and Carry Lookahead Adders: 1 ObjectivesMercely Christy PriyaPas encore d'évaluation

- Sample Final Exam EECS388 - Fall 2020Document19 pagesSample Final Exam EECS388 - Fall 2020Jeren ChenPas encore d'évaluation

- Instruction Level Paralleliusm AssignmentDocument2 pagesInstruction Level Paralleliusm AssignmentAnkit KumarPas encore d'évaluation

- Projects With Microcontrollers And PICCD'EverandProjects With Microcontrollers And PICCÉvaluation : 5 sur 5 étoiles5/5 (1)

- Integer Optimization and its Computation in Emergency ManagementD'EverandInteger Optimization and its Computation in Emergency ManagementPas encore d'évaluation

- 17 Allocation BasicDocument33 pages17 Allocation BasicAdip ChyPas encore d'évaluation

- Microelectronics Reliability: P.F. Butzen, V. Dal Bem, A.I. Reis, R.P. RibasDocument5 pagesMicroelectronics Reliability: P.F. Butzen, V. Dal Bem, A.I. Reis, R.P. RibasAdip ChyPas encore d'évaluation

- EE538 Homework 2Document1 pageEE538 Homework 2Adip ChyPas encore d'évaluation

- Google C++ Testing Framework: Running Test Programs: Advanced OptionsDocument18 pagesGoogle C++ Testing Framework: Running Test Programs: Advanced OptionsAdip ChyPas encore d'évaluation

- EE538 HW1 SolutionDocument4 pagesEE538 HW1 SolutionAdip ChyPas encore d'évaluation

- Multicores, Multiprocessors, and P, ClustersDocument51 pagesMulticores, Multiprocessors, and P, ClustersAdip ChyPas encore d'évaluation

- Chapter 4B: The Processor, Part B: Mary Jane IrwinDocument56 pagesChapter 4B: The Processor, Part B: Mary Jane IrwinAdip ChyPas encore d'évaluation

- Instructions: Language of The Computer PDocument92 pagesInstructions: Language of The Computer PAdip ChyPas encore d'évaluation

- Arithmetic For ComputersDocument48 pagesArithmetic For ComputersAdip ChyPas encore d'évaluation

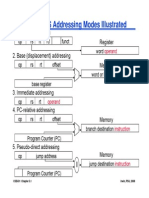

- Review: MIPS Addressing Modes Illustrated: 1. Register Addressing Register 2. Base (Displacement) Addressing MemoryDocument31 pagesReview: MIPS Addressing Modes Illustrated: 1. Register Addressing Register 2. Base (Displacement) Addressing MemoryAdip ChyPas encore d'évaluation

- Homework #3 Solutions: Spring 2013Document2 pagesHomework #3 Solutions: Spring 2013Adip ChyPas encore d'évaluation

- EE 536 Fall2013 SyllabusDocument1 pageEE 536 Fall2013 SyllabusAdip ChyPas encore d'évaluation

- Gem 5Document3 pagesGem 5Adip ChyPas encore d'évaluation

- EE 478 Lec02 DD Fundamentals1Document25 pagesEE 478 Lec02 DD Fundamentals1Adip ChyPas encore d'évaluation

- A10 5.1.0 FirewallDocument350 pagesA10 5.1.0 Firewallamel6320% (1)

- Yugabytedb Managed: Product BriefDocument6 pagesYugabytedb Managed: Product BriefSujasvi GhritlahrePas encore d'évaluation

- UNO-220 - EN - AdvRaspbian - User Manual - V1.2Document9 pagesUNO-220 - EN - AdvRaspbian - User Manual - V1.2tatajabarphPas encore d'évaluation

- Computer Networks Questions & Answers - Basics - 2: Answer: D Explanation: NoneDocument2 pagesComputer Networks Questions & Answers - Basics - 2: Answer: D Explanation: NoneAman Deep SinghPas encore d'évaluation

- Lab 5 (BGP-Slide) PDFDocument17 pagesLab 5 (BGP-Slide) PDFhiPas encore d'évaluation

- An0005-Using Unitedsic Spice Model in LtspiceDocument5 pagesAn0005-Using Unitedsic Spice Model in LtspiceLuis Felipe Colque MirandaPas encore d'évaluation

- VFP ServerDocument8 pagesVFP ServerBIosFilePas encore d'évaluation

- OnlineToday 4of4 1987 09Document22 pagesOnlineToday 4of4 1987 09chris8055Pas encore d'évaluation

- 4.1-1 Plan Conduct MaintenanceDocument14 pages4.1-1 Plan Conduct MaintenanceTabata Qbz TawinPas encore d'évaluation

- MuCAD5 EnglishDocument220 pagesMuCAD5 EnglishGroup NAVPas encore d'évaluation

- ZesaruxDocument10 pagesZesaruxquimicosdelestePas encore d'évaluation

- I. 8-Bit Microprocessors Architecture, Instruction Set and Their ProgrammingDocument4 pagesI. 8-Bit Microprocessors Architecture, Instruction Set and Their ProgrammingSaorabh KumarPas encore d'évaluation

- Pacsystems Rx3I Cpus: Industrial Internet ReadyDocument5 pagesPacsystems Rx3I Cpus: Industrial Internet ReadyJaob2Pas encore d'évaluation

- MCUmgr Bluetooth ProtocolDocument8 pagesMCUmgr Bluetooth ProtocolyudopplyrPas encore d'évaluation

- 02 BVMS VERSION 5 5 ReleaseNotes v3 PDFDocument38 pages02 BVMS VERSION 5 5 ReleaseNotes v3 PDFLucianaPas encore d'évaluation

- Cisco SWH Config - & - Run PuttyDocument7 pagesCisco SWH Config - & - Run PuttymuhammadsohPas encore d'évaluation

- WillowLynx Product Information r3Document14 pagesWillowLynx Product Information r3Ibrahim AdhamPas encore d'évaluation

- Manual Reefer ManagerDocument30 pagesManual Reefer ManagerelvasclimaPas encore d'évaluation

- SXoM Reference Manual B.01Document39 pagesSXoM Reference Manual B.01laichih1Pas encore d'évaluation

- Accelerate 3592-C07 V3Document41 pagesAccelerate 3592-C07 V3BillcPas encore d'évaluation

- Read Me First-Firmware Update Instructions-Le700Document4 pagesRead Me First-Firmware Update Instructions-Le700dinotopia1Pas encore d'évaluation

- Transparent Squid Web Proxy Server Using PFSenseDocument6 pagesTransparent Squid Web Proxy Server Using PFSensejoshua muanPas encore d'évaluation

- j1939 BootloaderDocument4 pagesj1939 Bootloaderveeresh ambePas encore d'évaluation

- Pro:Centric Server Admin Client User Guide: Standard and Read-Only UsersDocument33 pagesPro:Centric Server Admin Client User Guide: Standard and Read-Only UsersEsteban Zarikian TovarPas encore d'évaluation

- Experiment #2: Assembly Programming Using Subroutines & StacksDocument12 pagesExperiment #2: Assembly Programming Using Subroutines & StacksErgin ÖzdikicioğluPas encore d'évaluation

- EXP 6 Serial AdderDocument2 pagesEXP 6 Serial Adderubuntu 13.0450% (2)

- Samsung m2070 FW Printer Diagnostics - Buscar Con GoogleDocument2 pagesSamsung m2070 FW Printer Diagnostics - Buscar Con GoogleDavid LamillaPas encore d'évaluation

- Protocols LandscapeDocument3 pagesProtocols Landscapenapoleon_velasc3617Pas encore d'évaluation

- SCOM - GATEWAY SessionDocument30 pagesSCOM - GATEWAY SessionSamee ChougulePas encore d'évaluation

- Tong Hop - Share FinalDocument160 pagesTong Hop - Share FinalTran Quang Khoa (K18 HCM)Pas encore d'évaluation