Académique Documents

Professionnel Documents

Culture Documents

Trabajo de Investigacion

Transféré par

Jose Ordoñez0 évaluation0% ont trouvé ce document utile (0 vote)

11 vues4 pagesCopyright

© © All Rights Reserved

Formats disponibles

DOCX, PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme DOCX, PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

11 vues4 pagesTrabajo de Investigacion

Transféré par

Jose OrdoñezDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme DOCX, PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 4

Facultad de Informtica y Electrnica

Escuela de Ingeniera Electrnica en

Telecomunicaciones y Redes

Tercero B

Sistemas Digitales II

ALGORITMOS DE MAQUINAS DE ESTADO

Jos Ordoez 617

2014_2015

1.1 INTRODUCCIN

Las ASM (Maquinas De Estado Algortmica) primero definiremos que es Un algoritmo es

una secuencia de pasos bien definida que produce una secuencia deseada de acciones

en respuesta a una secuencia dada de entradas. Y un diagrama ASM (algorithmic state

machines) es una herramienta conveniente para expresar los algoritmos que sern

realizados por circuitos lgicos secuenciales.

En otras palabras, imaginemos una maquina capaz de seguir una secuencia de pasos al

introducir un conjunto de datos en ella, solo se puede leer un dato en cada paso que se

realice, por tanto el nmero de pasos a seguir est dado por el nmero de datos a

introducir. Cada entrada diferente genera una salida diferente, pero siempre el mismo

resultado con los mismos datos de entrada.

Por lo tanto una computacin es capaz de resolver un problema, si solo si tiene una

solucin algortmica, es decir, puede ser descrito mediante una secuencia de pasos

definidos.

1.2 CARACTERISTICAS

MQUINAS DE ESTADOS

El modelo de mquina de estados contiene los

elementos necesarios para describir la

conducta de un sistema en trminos de

entradas, salidas y del tiempo.

EL ALGORITMO DE LA MQUINA DE

ESTADOS

El algoritmo de la mquina de estados juega un

papel muy importante en el diseo de sistemas

digitales. Para circuitos sncronos la tcnica de la

carta ASM (Algorithm State Machine / Algoritmo de

la Mquina de Estados) es la mejor notacin, por lo

tanto, se adoptar para el resto de la obra.

Tambin existen otras tcnicas como la de los diagramas de estados que son diagramas

muy parecidos a las cartas ASM. Los diagramas de estados muestran grficamente la

secuencia de estados en un sistema y las condiciones de cada estado y de las

transiciones entre cada uno de ellos. Como ejemplo, en la figura 2.2 se describe el

comportamiento de un contador binario de 3 bits mediante un diagrama de estados. Este

circuito en particular no tiene ninguna entrada aparte de la de reloj, y ninguna otra salida

ms que las que se toman en cada flip-flop del contador.

ESTADOS Y RELOJ

El algoritmo de la mquina de estados se mueve a travs de una secuencia de estados

con base en la posicin del estado presente y las variables de entrada. Los tiempos del

estado estn determinados por un reloj maestro.

1.3 ELEMENTOS

NOTACIN DE LA CARTA ASM

REPRESENTACIN DE ESTADOS

El estado de una mquina de estados es la memoria de la historia pasada, suficiente para

determinar las condiciones futuras. En la siguiente figura se muestra la representacin del

estado. Un estado se representa con un rectngulo y con su nombre simblico en el

extremo superior, encerrado en un crculo.

REPRESENTACIN DE DECISIONES

Las decisiones permiten seleccionar el camino que el algoritmo de la mquina de estados

debe tomar de acuerdo a la variable o variables de entrada evaluadas. Las decisiones se

representan mediante un rombo con el nombre de la variable a probar o una funcin que

evale varias variables.

REPRESENTACIN DE SALIDAS

Salidas no condicionales. Sirven para indicar la activacin de una variable de salida. Para

representarlas, se escriben dentro del rectngulo de estado, los nombres de las variables

de salida que se activan en ese estado. Las salidas no condicionales no dependen de las

condiciones de entrada, slo dependen del estado actual.

Se emplean tres elementos para construir diagramas ASM:

Caja de estado: Representa un estado del circuito y equivale a un nodo del

diagrama de estados. En la caja se etiqueta el nombre del estado y en el caso de

circuitos Moore, las salidas por producir.

Caja de decisin: Representa una decisin de transicin de estado con base en

una prueba de una entrada del circuito. Una caja de decisin tiene un nico punto

de entrada y dos puntos de salida.

Caja de salida condicional: Especifica la salidas asociadas a las transiciones de

estado para una entrada dada en un circuito Me al y. Por lo general se ubican en

la ruta entre una caja de decisin y una caja de estado. Tiene una nica entrada y

un punto de salida

.

1.4 FUNCIONAMIENTO

El mtodo de ASM se compone de los siguientes pasos:

1. Crear un algoritmo, utilizando pseudocdigo para describir la operacin deseada

del dispositivo.

2. Convertir el pseudocdigo en un diagrama ASM.

3. Diseo del camino de datos basado en el diagrama ASM.

4. Crear diagrama ASM detallado basado en el camino de datos.

5. Diseo de la lgica de control basada en el diagrama ASM detallado.

Vous aimerez peut-être aussi

- Ruben Paiz "El Rancho" PDFDocument179 pagesRuben Paiz "El Rancho" PDFErick Espinoza100% (1)

- Habitos para Ser MILLONARIODocument3 pagesHabitos para Ser MILLONARIOedinson 1Pas encore d'évaluation

- Los Viajes de Mi Yo PDFDocument94 pagesLos Viajes de Mi Yo PDFCeska ChaskaPas encore d'évaluation

- Ericka Flores Blanco MovilDocument72 pagesEricka Flores Blanco MovilJulio Giraldo DiazPas encore d'évaluation

- Fase 1 - Pre Test Calculo IntegralDocument6 pagesFase 1 - Pre Test Calculo Integralkeko1976100% (3)

- BD JoDocument7 pagesBD JoJose OrdoñezPas encore d'évaluation

- Co Co: Agosto 2010Document71 pagesCo Co: Agosto 2010Jose OrdoñezPas encore d'évaluation

- Anteproyecto de Tesis Jose Ordoñez - 2Document25 pagesAnteproyecto de Tesis Jose Ordoñez - 2Jose OrdoñezPas encore d'évaluation

- Anteproyecto de Tesis Jose Ordoñez - 2Document25 pagesAnteproyecto de Tesis Jose Ordoñez - 2Jose OrdoñezPas encore d'évaluation

- AsistenciaDocument1 pageAsistenciaJose OrdoñezPas encore d'évaluation

- Proyectos CuestionarioDocument36 pagesProyectos CuestionarioJose OrdoñezPas encore d'évaluation

- Taller 1Document6 pagesTaller 1Jose OrdoñezPas encore d'évaluation

- Modelo SIG para zonas permitidas y restringidasDocument6 pagesModelo SIG para zonas permitidas y restringidasJose OrdoñezPas encore d'évaluation

- Instructivo 2019 Becas de Cooperación InternacionalDocument29 pagesInstructivo 2019 Becas de Cooperación InternacionalJose OrdoñezPas encore d'évaluation

- Cuestionario-Examen-Princiapal-Finanzas CorporativasDocument24 pagesCuestionario-Examen-Princiapal-Finanzas CorporativasJose OrdoñezPas encore d'évaluation

- Jose Ordoñez 473 HubDocument4 pagesJose Ordoñez 473 HubJose OrdoñezPas encore d'évaluation

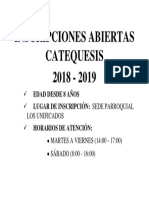

- Inscripciones Abiertas CatequesisDocument1 pageInscripciones Abiertas CatequesisJose OrdoñezPas encore d'évaluation

- JOSE ORDOÑEZ 473 FabricacionAeronavesDocument5 pagesJOSE ORDOÑEZ 473 FabricacionAeronavesJose OrdoñezPas encore d'évaluation

- Jose Ordoñez 473 HubDocument4 pagesJose Ordoñez 473 HubJose OrdoñezPas encore d'évaluation

- Planificación del transporte enDocument7 pagesPlanificación del transporte enJose OrdoñezPas encore d'évaluation

- ANALISISDocument40 pagesANALISISJose OrdoñezPas encore d'évaluation

- Ajustes de Regulacion - OdtDocument3 pagesAjustes de Regulacion - OdtJose OrdoñezPas encore d'évaluation

- ANALISISDocument40 pagesANALISISJose OrdoñezPas encore d'évaluation

- Sistema de cuenta múltiple o inventario periódicoDocument3 pagesSistema de cuenta múltiple o inventario periódicoJose Ordoñez67% (3)

- AsistenciaDocument1 pageAsistenciaJose OrdoñezPas encore d'évaluation

- Inscripciones Abiertas CatequesisDocument1 pageInscripciones Abiertas CatequesisJose OrdoñezPas encore d'évaluation

- Preguntas 2do Grupo. LeyesDocument2 pagesPreguntas 2do Grupo. LeyesJose OrdoñezPas encore d'évaluation

- Especialidad - Cpa Angel Preciado 16092016 3Document64 pagesEspecialidad - Cpa Angel Preciado 16092016 3Jose OrdoñezPas encore d'évaluation

- SABER PARA SER - OdtDocument9 pagesSABER PARA SER - OdtJose OrdoñezPas encore d'évaluation

- Especialidad - Cpa Angel Preciado 16092016 3Document64 pagesEspecialidad - Cpa Angel Preciado 16092016 3Jose OrdoñezPas encore d'évaluation

- Manual de presentación de estructurasDocument62 pagesManual de presentación de estructurasJose OrdoñezPas encore d'évaluation

- Conta AjustesDocument6 pagesConta AjustesJose OrdoñezPas encore d'évaluation

- Manual de presentación de estructurasDocument62 pagesManual de presentación de estructurasJose OrdoñezPas encore d'évaluation

- Balame de ComprobaciomDocument7 pagesBalame de ComprobaciomJose OrdoñezPas encore d'évaluation

- Producción de textos escritosDocument4 pagesProducción de textos escritosAranda DianaPas encore d'évaluation

- CorporativismoDocument3 pagesCorporativismoNico GarciPas encore d'évaluation

- MAPA CONCEPTUAL ÉTICA PROFESIONAL UNIDAD IIIDocument1 pageMAPA CONCEPTUAL ÉTICA PROFESIONAL UNIDAD IIIYovanna del J. Echazarreta PechPas encore d'évaluation

- LA PRUDENCIA - ScribDocument2 pagesLA PRUDENCIA - ScribcrisvillaraPas encore d'évaluation

- FonéticaDocument2 pagesFonéticaTreissy GarcíaPas encore d'évaluation

- Plan LectorDocument23 pagesPlan LectorNolberto Rodriguez Silvano0% (1)

- 34658-Texto Del Artículo-97682-1-10-20181123Document14 pages34658-Texto Del Artículo-97682-1-10-20181123marqkPas encore d'évaluation

- (Manual) Vargas Carreño Eduardo Derecho Internacional Público PDFDocument690 pages(Manual) Vargas Carreño Eduardo Derecho Internacional Público PDFFrancisco Aguilera Toro0% (1)

- Conectores de Lenguaje 2Document2 pagesConectores de Lenguaje 2ismaelPas encore d'évaluation

- LaExcelenciaPersonalComoEstiloDeVidaDocument3 pagesLaExcelenciaPersonalComoEstiloDeVidarasec250Pas encore d'évaluation

- El Derecho de SobreelevarDocument3 pagesEl Derecho de SobreelevarDEIVI24Pas encore d'évaluation

- La educación como proceso de formación integral del ser humanoDocument2 pagesLa educación como proceso de formación integral del ser humanoMARIA TERESA FRUET CARDOZOPas encore d'évaluation

- Proyecto EducativoDocument154 pagesProyecto EducativoChinaCuevaCruzadoPas encore d'évaluation

- La columna periodísticaDocument5 pagesLa columna periodísticaRonald Pedro Chavez Ureta100% (4)

- Informe pericial sobre daño social causado por privación de libertad de 24 años sin sentenciaDocument13 pagesInforme pericial sobre daño social causado por privación de libertad de 24 años sin sentenciaMulti Empresas BoliviaPas encore d'évaluation

- Lo Absurdo y El SuicidioDocument3 pagesLo Absurdo y El SuicidioHypu Gamerl100% (1)

- Estrategia DigitalDocument36 pagesEstrategia DigitalYeli ZuletaPas encore d'évaluation

- Aldea Caparja Camotan ChiquimulaDocument2 pagesAldea Caparja Camotan ChiquimulaLeo MancillaPas encore d'évaluation

- PornosonetosDocument6 pagesPornosonetosAriel Pavon100% (1)

- Detalles Constructivos de Las TensoestructurasDocument10 pagesDetalles Constructivos de Las TensoestructurasClaudio Ulloa CanalesPas encore d'évaluation

- De Sensibilización SistemáticaDocument4 pagesDe Sensibilización SistemáticaJheyson Cesar Garcia ApacllaPas encore d'évaluation

- Heráclito y ParménidesDocument2 pagesHeráclito y ParménidesGabriel MartínPas encore d'évaluation

- Teoría ColorDocument33 pagesTeoría ColorAntonella BriceñoPas encore d'évaluation

- Primer Nivel A - Guía 1Document5 pagesPrimer Nivel A - Guía 1Marcelo Mardones100% (1)

- Kant y La Isla de La VerdadDocument16 pagesKant y La Isla de La VerdadJOSÉ MIGUEL ESCOBAR CASTAÑEDAPas encore d'évaluation