Académique Documents

Professionnel Documents

Culture Documents

Clase 05 - 2 SPI Sincronico

Transféré par

Gus NeriCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Clase 05 - 2 SPI Sincronico

Transféré par

Gus NeriDroits d'auteur :

Formats disponibles

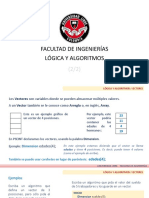

SERIAL PERIPHERAL INTERFACE

(SPI)

Mdulo Serial Sincrnico

SERIAL PERIPHERAL INTERFACE MODULE

68HC08

CPU

System

Integration

Module

(SIM)

Clock

Generation

Module

(CGM)

Timer

Interface

Module

(TIM)

Direct

Memory

Access

Module

(DMA)

Serial

Communications

Interface

(SCI)

Internal Bus (IBUS)

Serial

Peripheral

Interface

(SPI)

Random

Access

Memory

(RAM)

Electronically

Programmable

ROM

LVI

COP

Monitor

ROM

IRQ

BREAK

RESET

Las caracteristicas del mdulo SPI incluyen lo siguiente:

Operacin Full-Duplex

Modos Master y Slave

Registros separados Transmit y Receive

4 Frecuencias modo Master ( Mximo = Bus Frequency / 2 )

Frecuencia Mxima modo Slave = Bus Frequency

Serial Clock con Polaridad y Fase programables

Flag de error Bus Contention ( contencin del Bus )

Flag Overrun Error

2 habilitaciones de interrupcin separadas :

SPRF (SPI Receiver Full)

SPTE (SPI Transmitter Empty)

Modo programable Wired-OR

Compatibilidad I2C (Inter-Integrated Circuit)

Registros I/O del SPI

Tres registros controlan y monitorean las operaciones del SPI :

SPI Control Register (SPCR)

SPI Status and Control Register (SPSCR)

SPI Data Register (SPDR)

Modos del SPI

Modo Master (Amo)

Solamente un SPI master inicia la transmisin

Los Datos son desplazados hacia afuera va la lnea Master Out Slave In (MOSI)

Los Datos son desplazados hacia adentro va la lnea Master In Slave Out (MISO)

La Transmisin finaliza despus de 8 ciclos del serial clock (SPSCK) , ya que se trata de

una transmisin serial sincrnizada con el Clock generado por el master y cada dato

est sincronizado con dicho clock (8 pulsos de clock y no mas que ello).

Modo Slave (Esclavo)

Transferencia sincronizada al serial clock (SPSCK) desde el Master

Los Datos son desplazados hacia adentro va la lnea Master Out Slave In (MOSI)

Los Datos son desplazados hacia afuera va la lnea Master In Slave Out (MISO)

Pin seleccin Slave

SS

Shift Register Shift Register

MOSI

MISO

+5v

SS

MASTER SLAVE

Baud Rate Gen.

SPSCK

Slave Select (SS)

Modo Master

SS se mantiene alto ( 1 ) durante la transmisin (se fuerza a 1)

Actua como una entrada de deteccin de error (si algo la fuerza a 0, hay un error !!)

Puede ser una salida de propsitos generales.

Modo Slave

SS debe permanecer bajo ( 0 ) hasta que se completa la transmisin (forma de habilitar al

dispositvo slave)

0 = Habilita el slave

1 = Deshabilita el slave

SPI Control Register

SPI Control Register (SPCR)

SPI Master (SPMSTR)

Seleccin del modo de operacin master o slave

1 = Modo Master

0 = Modo Slave

SPI Master y Slave necesitan seteo de polaridad y fase de clock idnticas (1*)

Clock Polarity (CPOL)

Determina el estado del clock cuando esta idle

Clock Phase (CPHA)

1 = Comienza la captura de datos en el 2do. flanco del ciclo de clock

0 = Comienza la captura de datos en el 1er. Flanco del ciclo de clock*

RESET: 0 0 0 0 1 0 0 0

WRITE:

READ:

SPRIE DMAS SPMSTR CPOL CPHA SPWOM SPE SPTIE SPCR

SPI Enable (SPE)

1 = Habilita el SPI module

0 = Deshabilita SPI module

1* NOTA: Consultar en el manual de datos del MCU elegdo y del dispositvo SPI a conectar, para determinar con

exactitud el seteo de los bits CPOL y CPHA para una correcta comunicacin entre ambos.

Baud Rate del SPI

SPI Status and Control Register (SPSCR)

SPI rate select bits (SPR1, SPR0) (seleccin velocidad)

Setea la frecuencia del Master SPSCK clock

No tiene efecto en los dispositivos Slave

Baud Rate = CGMOUT / Baud Rate Divisor

SPR1:SPR0

Divided By

System Clock

(System Clock Freq. = 8 MHz)

Baud Rate

00

01

10

11

2

8

32

128

4 MHz

1 MHz

250 KHz

62.5 KHz

RESET: 0 0 0 0 1 0 0 0

WRITE:

READ: SPRF 0 OVRF MODF SPTE

SPR1 SPR0

SPSCR

0

SPI Data Register

SPI Data Register (SPDR)

Buffer de Lectura / Escrituta para los datos SPI

Operacin de escritura

Escribe datos al transmit data register

Operacin de lectura

Lee datos en el receive data register

Un SOLO buffer tanto para la lectura de datos (recepcin) como para la escritura de

datos (transmisin). Tener en cuenta que en una conexin SPI, los datos forman un

anillo circular entre los buffers del dispositivo master y el dispositvo slave.

RESET: UNAFFECTED BY RESET

WRITE:

READ:

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 SPDR

Flags de estados del SPI

SPI Status and Control Register (SPSCR)

SPI Receiver Full (SPRF)

Seteado cuando un byte es desplazado desde el shift register al receive data

register

Limpiado por la lectura del SPSCR luego de la lectura del SPDR.

1 = Receive data register full

0 = Receive data register not full

SPI Transmitter Empty (SPTE)

Seteado cuando un byte se transfiere desde el SPDR al shift register

Limpiado por la lectura del SPDR register

1 = Transmit data register vacio

0 = Transmit data register no vacio

RESET: 0 0 0 0 1 0 0 0

WRITE:

READ: SPRF 0 OVRF MODF SPTE

SPR1 SPR0

SPSCR

0

Interrupciones del SPI

SPI Control Register (SPCR)

SPI Receiver Interrupt Enable Bit (SPRIE)

Interrupcin generada cuando se setea el flag SPRF

SPI Transmit Interrupt Enable (SPTIE)

Interrupcin generada cuando se setea el flag SPTE

1 = Interrupcin habilitada

0 = Interrupcin deshabilitada

Direct Memory Access Select (DMAS)

No disponible en esta familia de HC08 !!!

RESET: 0 0 0 0 1 0 0 0

WRITE:

READ:

SPRIE DMAS SPMSTR CPOL CPHA SPWOM SPE SPTIE

SPCR

Inicializacin

Sequencia de inicializacin del SPI

1) Inicializar la frecuencia de clock del SPI ( SPR1 y SPR0 en SPSCR )

2) Setear la configuracin del clock ( bits CPOL y CPHA en SPSCR )

3) Seleccionar operacin Master/Slave ( SPMSTR en SPCR )

4) Habilitar las interrupciones si es necesario ( SPTIE, SPRIE en SPCR )

5) Habilitar el sistema SPI ( SPE en SPCR )

Deber habilitarse el dispositvo Master antes del Slaves !!!

(Para evitar falsas operaciones)

Transferencia -- Master a Slave

Operacin Poleada simple ( x polling )

1) Inicializar el SPI

2) Seleccionar el SS en el dispositivo Slave ( hardware dependiente )

3) Escribir un byte en el SPDR

4) En espera de la activacin del Flag SPI Transmitter Empty (SPTE)

5) Leer el SPDR

6) Liberar el SS en dispositivo Slave ( hardware dependiente )

Informacin Adicional

Modo Wired-Or

SPI Control Register (SPCR)

SPI Wired OR Mode (SPWOM)

Configura las salidas MISO, MOSI, y al SPSCK como open-drain

Permite sistemas de Masters Mltiples

Provee algo de proteccin contra el CMOS latchup.

RESET: 0 0 0 0 1 0 0 0

WRITE:

READ:

SPRIE DMAS SPMSTR CPOL CPHA SPWOM SPE SPTIE SPCR

Informacin Adicional

Flags de estados Overflow y Mode Fault

SPI Status and Control Register (SPSCR)

Overflow flag (OVRF)

Se activa cuando el Receive data register no es leido antes de sobrescribirlo

El byte de datos entrante se pierde

El contenido del data register no es afectado

Limpiado por la lectura del data register

Mode Fault flag (MODF)

Modo Master solamente

Indica que otro master trata de acceder a ese dispositivo

Seteado cuando otro dispositivo pone el pin SS a Low

Limpiado por una escritura al SPSCR

RESET: 0 0 0 0 1 0 0 0

WRITE:

READ: SPRF 0 OVRF MODF SPTE

SPR1 SPR0

SPSCR

0

SPSCR

WRITE:

READ:

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

SPDR

SPRIE SPCR

WRITE:

READ:

DMAS

SPMSTR

CPOL

CPHA SPWOM

SPE SPTIE

Sumario de Registros

SPR1 SPR0

WRITE:

READ:

SPRF 0 OVRF

MODF SPTE

0

Vous aimerez peut-être aussi

- Estructura de Datos I Reparado PDFDocument105 pagesEstructura de Datos I Reparado PDFBrenda PattersonPas encore d'évaluation

- Lab4-Configuración y Programación de Un PLC Allen Bradley Micrologix 1100Document25 pagesLab4-Configuración y Programación de Un PLC Allen Bradley Micrologix 1100Henrry Campos Nicodemoos100% (1)

- LF FinalDocument4 pagesLF FinalSantiago RojasPas encore d'évaluation

- Practica 3Document5 pagesPractica 3Cristofer SagasPas encore d'évaluation

- Estructura General de WindowsDocument3 pagesEstructura General de WindowsMauricio Pérez CortésPas encore d'évaluation

- ABE1 Escenario RemotoDocument9 pagesABE1 Escenario RemotoANI mangaPas encore d'évaluation

- Manual de UsuariosDocument48 pagesManual de UsuariosLeo Jared PadillaPas encore d'évaluation

- Sistemas Operativos - Tarea Semana 7 - Julian Guillermo Castro MurciaDocument3 pagesSistemas Operativos - Tarea Semana 7 - Julian Guillermo Castro MurciaAngie Alejandra fuquen montañezPas encore d'évaluation

- Aficio 1022-1027Document2 pagesAficio 1022-1027Edgardo Carrillo OyolaPas encore d'évaluation

- CAPITULO 3: Diseño de RedesDocument64 pagesCAPITULO 3: Diseño de RedesjbleokingPas encore d'évaluation

- CrackDocument2 pagesCrackHansHanson3Pas encore d'évaluation

- Cuestionario Logica ComputacionalDocument4 pagesCuestionario Logica ComputacionalJam AlcPas encore d'évaluation

- Operador BotDocument21 pagesOperador BotAndres BenitezPas encore d'évaluation

- Logica y Algoritmos 2de2 20230509Document61 pagesLogica y Algoritmos 2de2 20230509Sonia GilPas encore d'évaluation

- Exámenes de Informática Comentados Cuerpo Auxiliar Del EstadoDocument38 pagesExámenes de Informática Comentados Cuerpo Auxiliar Del EstadoSilvia Ramírez Divaret100% (1)

- Clase9 VBADocument4 pagesClase9 VBApipesalgado7Pas encore d'évaluation

- S3 SB2 C1 01 EnfoquesHerramientasDocument2 pagesS3 SB2 C1 01 EnfoquesHerramientasgohujonaPas encore d'évaluation

- Automatización COM en PROGRESSDocument9 pagesAutomatización COM en PROGRESSLopez HeradioPas encore d'évaluation

- COT1903 - Inversiones Medicas de VenezuelaDocument1 pageCOT1903 - Inversiones Medicas de Venezuelacarlos marcanoPas encore d'évaluation

- Soprte Tecnico-1Document7 pagesSoprte Tecnico-1Anthony Ramirez JumboPas encore d'évaluation

- Qué Es La InformáticaDocument2 pagesQué Es La InformáticaGenesis GuerreroPas encore d'évaluation

- Informe AdcDocument20 pagesInforme AdcJouleshans BradleyPas encore d'évaluation

- 12 Google DriveDocument9 pages12 Google DriveEri ABPas encore d'évaluation

- Guia Apache PDFDocument13 pagesGuia Apache PDFYei PeinadoPas encore d'évaluation

- Trabajo Práctico Individual Ii - Arquitectura de ComputadoresDocument8 pagesTrabajo Práctico Individual Ii - Arquitectura de ComputadoresTrucho De MiércolesPas encore d'évaluation

- Cuestionario U7 - V7 Portátiles Iker GuzmanDocument11 pagesCuestionario U7 - V7 Portátiles Iker GuzmanIker GuzmánPas encore d'évaluation

- Reporte 1.4Document11 pagesReporte 1.4Distribución MartinezPas encore d'évaluation

- Cómo Configurar Los Jumpers de Un Disco Duro IDEDocument3 pagesCómo Configurar Los Jumpers de Un Disco Duro IDEflores31Pas encore d'évaluation

- renderPDF - PHP Herramientas Julio 28 2020 PDFDocument9 pagesrenderPDF - PHP Herramientas Julio 28 2020 PDFcarlos Alfonso Rivera diazPas encore d'évaluation

- Datasheet - WMC01cDocument1 pageDatasheet - WMC01cluicar8909Pas encore d'évaluation