Académique Documents

Professionnel Documents

Culture Documents

4M (512K X 8) Static Ram: Cy62148V Mobl

Transféré par

Aurelian ZaharescuDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

4M (512K X 8) Static Ram: Cy62148V Mobl

Transféré par

Aurelian ZaharescuDroits d'auteur :

Formats disponibles

4M (512K x 8) Static RAM

CY62148V MoBL

Cypress Semiconductor Corporation 3901 North First Street San Jose CA 95134 408-943-2600

Document #: 38-05070 Rev. *A Revised August 27, 2002

Features

Wide voltage range: 2.7V3.6V

Ultra low active power

Low standby power

TTL-compatible inputs and outputs

Automatic power-down when deselected

CMOS for optimum speed/power

Package available in a 32 pin TSOPII and a 32-pin SOIC

package

Functional Description

[1]

The CY62148V is a high-performance CMOS static RAM

organized as 512K words by eight bits. This device features

advanced circuit design to provide ultra-low active current.

This is ideal for providing More Battery Life (MoBL

) in

portable applications such as cellular telephones. The device

also has an automatic power-down feature that significantly

reduces power consumption by 99% when addresses are not

toggling. The device can be put into standby mode when

deselected (CE HIGH).

Writing to the device is accomplished by taking Chip Enable

(CE) and Write Enable (WE) inputs LOW. Data on the eight I/O

pins (I/O

0

through I/O

7

) is then written into the location

specified on the address pins (A

0

through A

18

).

Reading from the device is accomplished by taking Chip

Enable (CE) and Output Enable (OE) LOW while forcing Write

Enable (WE) HIGH. Under these conditions, the contents of

the memory location specified by the address pins will appear

on the I/O pins.

The eight input/output pins (I/O

0

through I/O

7

) are placed in a

high-impedance state when the device is deselected (CE

HIGH), the outputs are disabled (OE HIGH), or during a write

operation (CE LOW and WE LOW).

Logic Block Diagram

Note:

1. For best practice recommendations, please refer to the Cypress application note System Design Guidelines on http://www.cypress.com.

1

7

1

5

A

1

A

2

A

3

A

4

A

5

A

6

A

7

A

8

COLUMN

DECODER

R

O

W

D

E

C

O

D

E

R

S

E

N

S

E

A

M

P

S

Data in Drivers

POWER

DOWN

WE

OE

I/O

0

I/O

1

I/O

2

I/O

3 512K x 8

ARRAY

I/O

7

I/O

6

I/O

5

I/O

4

A

0

A

1

2

A

1

4

A

1

3

A A

1

1

CE

AA

1

6

A

1

0

1

8

A

A

9

CY62148V MoBL

Document #: 38-05070 Rev. *A Page 2 of 9

Maximum Ratings

(Above which the useful life may be impaired. For user guide-

lines, not tested.)

Storage Temperature ................................. 65C to +150C

Ambient Temperature with

Power Applied............................................... 55C to +125C

Supply Voltage to Ground Potential ............... 0.5V to +4.6V

DC Voltage Applied to Outputs

in High-Z State

[2]

....................................0.5V to V

CC

+ 0.5V

DC Input Voltage

[2]

................................ 0.5V to V

CC

+ 0.5V

Output Current into Outputs (LOW)............................. 20 mA

Static Discharge Voltage.......................................... > 2001V

(per MIL-STD-883, Method 3015)

Latch-up Current.................................................... > 200 mA

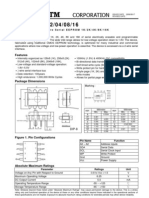

Pin Configurations

WE

1

2

3

4

5

6

7

8

9

10

11

14

31

32

Top View

12

13

16

15

29

30

V

CC

A

3

A

2

A

1

A

17

A

16

OE

A

6

A

14

CE

I/O

2

I/O

0

I/O

1

A

12

A

7

21

22

19

20

I/O

7

27

28

25

26

17

18

23

24

V

SS

A

5

A

4

I/O

6

I/O

5

I/O

4

I/O

3

A

10

A

18

A

11

TSOPII/SOIC

A

0

A

9

A

8

A

13

A

15

Operating Range

Range Ambient Temperature V

CC

Industrial 40C to +85C 2.7V to 3.6V

Product Portfolio

Product

V

CC

Range (V)

Speed

(ns)

Power Dissipation

Operating I

CC

, (mA) Standby I

SB2

, (A)

Min. Typ.

[3]

Max. Typ.

[3]

Maximum Typ.

[3]

Maximum

CY62148VLL 2.7 3.0 3.6 70 7 15 2 20

Electrical Characteristics Over the Operating Range

Parameter Description Test Conditions

CY62148V-70

Unit Min. Typ.

[3]

Max.

V

OH

Output HIGH Voltage I

OH

= 1.0 mA V

CC

= 2.7V 2.4 V

V

OL

Output LOW Voltage I

OL

= 2.1 mA V

CC

= 2.7V 0.4 V

V

IH

Input HIGH Voltage V

CC

= 3.6V 2.2 V

CC

+

0.5V

V

V

IL

Input LOW Voltage V

CC

= 2.7V 0.5 0.8 V

I

IX

Input Load Current GND < V

I

< V

CC

1 +1 +1 A

I

OZ

Output Leakage Current GND < V

O

< V

CC

, Output Disabled 1 +1 +1 A

I

CC

V

CC

Operating Supply

Current

I

OUT

= 0 mA, f = f

MAX

= 1/t

RC

CMOS Levels

V

CC

= 3.6V 7 15 mA

I

OUT

= 0 mA, f = 1 MHz CMOS Levels 1 2 mA

I

SB1

Automatic CE

Power-down Current

CMOS Inputs

CE > V

CC

0.3V, V

IN

> V

CC

0.3V or V

IN

< 0.3V, f =

f

MAX

2 20 A

I

SB2

Automatic CE

Power-down Current

CMOS Inputs

CE > V

CC

0.3V

V

IN

> V

CC

0.3V

or V

IN

< 0.3V, f = 0

V

CC

= 3.6V

Notes:

2. V

IL(min.)

= 2.0V for pulse durations less than 20 ns.

3. Typical values are included for reference only and are not guaranteed or tested. Typical values are measured at V

CC

= V

CC(typ.)

, T

A

= 25C.

CY62148V MoBL

Document #: 38-05070 Rev. *A Page 3 of 9

AC Test Loads and Waveforms

Capacitance

[4]

Parameter Description Test Conditions Max. Unit

C

IN

Input Capacitance T

A

= 25C, f = 1 MHz,

V

CC

= 3.0V

6 pF

C

OUT

Output Capacitance 8 pF

Thermal Resistance

Parameter Description Test Conditions Others BGA Units

JA

Thermal Resistance

[4]

(Junction to Ambient)

Still Air, soldered on a 4.25 x 1.125 inch, 4-layer

printed circuit board

TBD TBD C/W

JC

Thermal Resistance

[4]

(Junction to Case)

TBD TBD C/W

Parameters 3.0V Unit

R1 1105 Ohms

R2 1550 Ohms

R

TH

645 Ohms

V

TH

1.75V Volts

Data Retention Characteristics (Over the Operating Range)

Parameter Description Conditions Min. Typ.

[3]

Max. Unit

V

DR

V

CC

for Data Retention 1.0 3.6 V

I

CCDR

Data Retention Current V

CC

= 1.0V, CE > V

CC

0.3V, V

IN

> V

CC

0.3V or V

IN

<

0.3V; No input may exceed V

CC

+ 0.3V

0.2 5.5 A

t

CDR

[4]

Chip Deselect to Data

Retention Time

0 ns

t

R

[5]

Operation Recovery Time t

RC

ns

Data Retention Waveform

Notes:

4. Tested initially and after any design or process changes that may affect these parameters.

5. Full-device AC operation requires linear V

CC

ramp from V

DR

to V

CC(min.)

> 10 s or stable at V

CC(min.)

> 10 s.

V

CC

TYP

V

CC

OUTPUT

R2

50 pF

INCLUDING

JIG AND

SCOPE

GND

90%

10%

90%

10%

Rise time: 1V/ns Fall time: 1V/ns

OUTPUT V

th

Equivalent to: TH VENIN EQUIVALENT

ALL INPUT PULSES

R1

R

th

1.0V 1.0V

t

CDR

V

DR

> 1.0 V

DATA RETENTION MODE

t

R

CE

V

CC

CY62148V MoBL

Document #: 38-05070 Rev. *A Page 4 of 9

Switching Characteristics Over the Operating Range

[6]

Parameter Description

CY62148V-70

Unit Min. Max.

Read Cycle

t

RC

Read Cycle Time 70 ns

t

AA

Address to Data Valid 70 ns

t

OHA

Data Hold from Address Change 10 ns

t

ACE

CE LOW to Data Valid 70 ns

t

DOE

OE LOW to Data Valid 35 ns

t

LZOE

OE LOW to Low-Z

[7]

5 ns

t

HZOE

OE HIGH to High-Z

[8]

25 ns

t

LZCE

CE LOW to Low-Z

[7]

10 ns

t

HZCE

CE HIGH to High-Z

[7, 8]

25 ns

t

PU

CE LOW to Power-up 0 ns

t

PD

CE HIGH to Power-down 70 ns

Write Cycle

[9, 10]

t

WC

Write Cycle Time 70 ns

t

SCE

CE LOW to Write End 60 ns

t

AW

Address Set-up to Write End 60 ns

t

HA

Address Hold from Write End 0 ns

t

SA

Address Set-up to Write Start 0 ns

t

PWE

WE Pulse Width 50 ns

t

SD

Data Set-up to Write End 30 ns

t

HD

Data Hold from Write End 0 ns

t

HZWE

WE LOW to High-Z

[7, 8]

25 ns

t

LZWE

WE HIGH to Low-Z

[7]

10 ns

Switching Waveforms

Notes:

6. Test conditions assume signal transition time of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to V

CC(typ.)

, and output loading of the

specified I

OL

/I

OH

and 30 pF load capacitance.

7. At any given temperature and voltage condition, t

HZCE

is less than t

LZCE

, t

HZOE

is less than t

LZOE

, and t

HZWE

is less than t

LZWE

for any given device.

8. t

HZOE

, t

HZCE

, and t

HZWE

are specified with C

L

= 5 pF as in (b) of AC Test Loads. Transition is measured 200 mV from steady-state voltage.

9. The internal write time of the memory is defined by the overlap of CE LOW and WE LOW. Both signals must be LOW to initiate a write and either signal can

terminate a write by going HIGH. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.

10. The minimum write cycle time for Write Cycle #3 (WE controlled, OE LOW) is the sum of t

HZWE

and t

SD

.

ADDRESS

DATA OUT PREVIOUS DATA VALID DATA VALID

t

RC

t

AA

t

OHA

Read Cycle No. 1

[11, 12]

CY62148V MoBL

Document #: 38-05070 Rev. *A Page 5 of 9

Notes:

11. Device is continuously selected. OE, CE = V

IL

.

12. WE is HIGH for read cycle.

13. Address valid prior to or coincident with CE transition LOW.

14. Data I/O is high impedance if OE = V

IH

.

15. If CE goes HIGH simultaneously with WE HIGH, the output remains in a high-impedance state.

16. During this period, the I/Os are in output state and input signals should not be applied.

Switching Waveforms (continued)

50% 50%

DATA VALID

t

RC

t

ACE

t

DOE

t

LZOE

t

LZCE

t

PU

DATA OUT

HIGH IMPEDANCE IMPEDANCE

I

CC

I

SB

t

HZOE

t

HZCE

t

PD

OE

CE

HIGH

V

CC

SUPPLY

CURRENT

Read Cycle No. 2

[12, 13]

t

HD

t

SD

t

PWE

t

SA

t

HA

t

AW

t

WC

DATA I/O

ADDRESS

CE

WE

OE

t

HZOE

DATA

IN

VALID NOTE

Write Cycle No. 1 (WE Controlled)

[9, 14, 15]

16

t

WC

t

AW

t

SA

t

HA

t

HD

t

SD

t

SCE

WE

DATA I/O

ADDRESS

CE

DATA

IN

VALID

Write Cycle No. 2 (CE Controlled)

[9, 14, 15]

CY62148V MoBL

Document #: 38-05070 Rev. *A Page 6 of 9

Switching Waveforms (continued)

DATA I/O

ADDRESS

t

HD

t

SD

t

LZWE

t

SA

t

HA

t

AW

t

WC

CE

WE

t

HZWE

DATA

IN

VALID

Write Cycle No. 3 (WE Controlled, OE LOW)

[10, 15]

NOTE 16

Typical DC and AC Characteristics

70

80

60

40

30

20

1.0

1.9 2.8 3.7

SUPPLY VOLTAGE (V)

Access Time vs. Supply Voltage

10

50

T

A

A

(

n

s

)

40

45

35

25

20

15

1.0

1.9 2.8 3.7

10

30

I

S

B

(

A

)

Standby Current vs. Supply Voltage

SUPPLY VOLTAGE (V)

1.2

1.4

1.0

0.6

0.4

0.2

1.7 2.2 2.7 3.2 3.7

0.0

0.8

I

C

C

Normalized Operating Current

SUPPLY VOLTAGE (V)

vs. Supply Voltage

CY62148V MoBL

Document #: 38-05070 Rev. *A Page 7 of 9

Truth Table

CE WE OE Inputs/Outputs Mode Power

H X X High-Z Deselect/Power-down Standby (I

SB

)

L H L Data Out Read Active (I

CC

)

L L X Data In Write Active (I

CC

)

L H H High-Z Output Disabled Active (I

CC

)

Ordering Information

Speed

(ns) Ordering Code

Package

Name Package Type

Operating

Range

70 CY62148VLL-70ZI ZS32 32-lead TSOPII Industrial

CY62148VLL-70SI S34 32-lead 450-mil. molded SOIC

Package Diagrams

32-Lead (450-mil) Molded SOIC S34

51-85081-A

CY62148V MoBL

Document #: 38-05070 Rev. *A Page 8 of 9

Cypress Semiconductor Corporation, 2002. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use

of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize

its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress

Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.

MoBL is a registered trademark, and More Battery Life is a trademark, of Cypress Semiconductor. All product and company

names mentioned in this document are the trademarks of their respective holders.

Package Diagrams (continued)

32-lead TSOP II ZS32

51-85095

CY62148V MoBL

Document #: 38-05070 Rev. *A Page 9 of 9

Document Title: CY62148V MoBL

4M (512K x 8) Static RAM

Document Number: 38-05070

REV. ECN NO. Issue Date

Orig. of

Change Description of Change

** 107263 09/15/01 SZV Changed from Spec number: 38-00646 to 38-05070

*A 116515 09/04/02 GBI Added footnote 1.

Deleted fBGA package.

Removed fBGA package (replacement fBGA package is available in

CY62148CV30)

Vous aimerez peut-être aussi

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Pas encore d'évaluation

- A Primer On A Good Instrument Grounding SystemDocument26 pagesA Primer On A Good Instrument Grounding SystemwlmostiaPas encore d'évaluation

- Library and Information ScienceDocument32 pagesLibrary and Information Scienceneilesh300100% (2)

- Datasheet EEPROMDocument9 pagesDatasheet EEPROMIram Loya ValladaresPas encore d'évaluation

- Stream CipherDocument214 pagesStream CipherAyush TibrewalaPas encore d'évaluation

- CH112-02 System Architecture - RevBDocument18 pagesCH112-02 System Architecture - RevBzvonkomihajlovic4891Pas encore d'évaluation

- Memoria Ram 6264Document14 pagesMemoria Ram 6264DOMINGOS ALADIRPas encore d'évaluation

- Cypress SRAM CY62256Document11 pagesCypress SRAM CY62256MicroemissionPas encore d'évaluation

- 6116ASP20Document9 pages6116ASP20BeNz BarrigaPas encore d'évaluation

- IS61LV25616AL: 256K X 16 High Speed Asynchronous Cmos Static Ram With 3.3V SupplyDocument17 pagesIS61LV25616AL: 256K X 16 High Speed Asynchronous Cmos Static Ram With 3.3V SupplywarekinPas encore d'évaluation

- DS1270W 3.3V 16Mb Nonvolatile SRAM: Features Pin AssignmentDocument8 pagesDS1270W 3.3V 16Mb Nonvolatile SRAM: Features Pin AssignmentAndré CastroPas encore d'évaluation

- Datasheet CY62146DV30LDocument11 pagesDatasheet CY62146DV30LedgarlibanioPas encore d'évaluation

- SM 1994Document10 pagesSM 1994Jesus J. SalasPas encore d'évaluation

- 32kx8bit CMOS SRAM: HY62256B SeriesDocument9 pages32kx8bit CMOS SRAM: HY62256B SeriesShiwam IsriePas encore d'évaluation

- 000 0 Hy628100bllg 70Document9 pages000 0 Hy628100bllg 70Deepa DevarajPas encore d'évaluation

- 4Mb-SRAM 512Kx1BDocument18 pages4Mb-SRAM 512Kx1BserjaniPas encore d'évaluation

- 28 C 16Document10 pages28 C 16Omar Santiago AvalosPas encore d'évaluation

- EEPROMDocument16 pagesEEPROMTutankhalmoxePas encore d'évaluation

- 24 LC 64Document12 pages24 LC 64achuthkumarPas encore d'évaluation

- Atmel 8568 SEEPROM AT24C256C Datasheet PDFDocument21 pagesAtmel 8568 SEEPROM AT24C256C Datasheet PDFhanifPas encore d'évaluation

- 64K (8Kx8) Parallel Eeproms AT28C64 AT28C64X: FeaturesDocument13 pages64K (8Kx8) Parallel Eeproms AT28C64 AT28C64X: FeaturesJi HooPas encore d'évaluation

- Datasheet Cy7c199Document13 pagesDatasheet Cy7c199m_manu8588Pas encore d'évaluation

- 4-Mbit (256 K × 16) Static RAM: Features Functional DescriptionDocument18 pages4-Mbit (256 K × 16) Static RAM: Features Functional Descriptionprasanna_npPas encore d'évaluation

- HY6264A - (I) Series: 8kx8bit CMOS SRAMDocument9 pagesHY6264A - (I) Series: 8kx8bit CMOS SRAMLexuanhoa ProPas encore d'évaluation

- 1-Mbit (128 K × 8) Static RAM: Features Functional DescriptionDocument18 pages1-Mbit (128 K × 8) Static RAM: Features Functional Descriptionjj71Pas encore d'évaluation

- 2114 SramDocument4 pages2114 SramKarloz IbarraPas encore d'évaluation

- 24 LC 2561Document12 pages24 LC 2561ricardo_MassisPas encore d'évaluation

- Two-Wire Serial EEPROM: FeaturesDocument28 pagesTwo-Wire Serial EEPROM: FeaturesdobsrdjanPas encore d'évaluation

- 8-Bit Shift Register With Input Storage Registers (3-State) : Integrated CircuitsDocument14 pages8-Bit Shift Register With Input Storage Registers (3-State) : Integrated CircuitsskiziltoprakPas encore d'évaluation

- DS1220Y 16k Nonvolatile SRAM: Features Pin AssignmentDocument8 pagesDS1220Y 16k Nonvolatile SRAM: Features Pin AssignmentChico SouzaPas encore d'évaluation

- 74ACT323 8-Bit Universal Shift/Storage Register With Synchronous Reset and Common I/O PinsDocument7 pages74ACT323 8-Bit Universal Shift/Storage Register With Synchronous Reset and Common I/O PinsPiero SotoPas encore d'évaluation

- 512K (64K X 8) CMOS EPROM: Features Package TypesDocument8 pages512K (64K X 8) CMOS EPROM: Features Package Types81968Pas encore d'évaluation

- 24 LC 16Document32 pages24 LC 16Jos RoPas encore d'évaluation

- Memoria CAT24M01-D-91485Document15 pagesMemoria CAT24M01-D-91485Feer Rusk EdgarPas encore d'évaluation

- 24lc08 EepromDocument27 pages24lc08 EepromIsmael Minchola CarhuasPas encore d'évaluation

- A42L0616 Series: Preliminary 1M X 16 Cmos Dynamic Ram With Edo Page ModeDocument25 pagesA42L0616 Series: Preliminary 1M X 16 Cmos Dynamic Ram With Edo Page ModeSaleem IqbalPas encore d'évaluation

- Eeproms 24CXXDocument18 pagesEeproms 24CXXAlberto YepezPas encore d'évaluation

- Cy62146dv30 Ram NokiaDocument12 pagesCy62146dv30 Ram NokiaandersonbheringPas encore d'évaluation

- 27C512Document12 pages27C512technicalavrPas encore d'évaluation

- Dual D-Type Flip-Flop: Integrated CircuitsDocument8 pagesDual D-Type Flip-Flop: Integrated CircuitsRakesh Kumar DPas encore d'évaluation

- Atmel 24C1024Document19 pagesAtmel 24C1024vax1Pas encore d'évaluation

- W27E257 Eprom PDFDocument15 pagesW27E257 Eprom PDFAvi Ramirez CervantesPas encore d'évaluation

- 24 LC 02Document13 pages24 LC 02MoshikoRanPas encore d'évaluation

- 74LS374Document8 pages74LS374Bechtel LanutanPas encore d'évaluation

- 24Lc04B/08B: 4K/8K 2.5V I C Serial EepromsDocument13 pages24Lc04B/08B: 4K/8K 2.5V I C Serial EepromsJose Antonio Lopez JuradoPas encore d'évaluation

- 93C66 Microwire EepromDocument13 pages93C66 Microwire EepromadrianramonPas encore d'évaluation

- 24C512Document13 pages24C512kimbo23Pas encore d'évaluation

- 64K (8K X 8) Cmos Eprom: Features Package TypesDocument13 pages64K (8K X 8) Cmos Eprom: Features Package TypesIngrid XytrasPas encore d'évaluation

- 128K X 8 Static RAM: PreliminaryDocument8 pages128K X 8 Static RAM: PreliminaryRoozbeh BahmanyarPas encore d'évaluation

- 74F191Document8 pages74F191Alexandre S. CorrêaPas encore d'évaluation

- Mid Semester 2012 TID203Document17 pagesMid Semester 2012 TID203peas002Pas encore d'évaluation

- Flip Flop D 74ls74Document13 pagesFlip Flop D 74ls74Kath EmiPas encore d'évaluation

- N25S818HA 256 KB Low Power Serial Srams: 32 K X 8 Bit OrganizationDocument12 pagesN25S818HA 256 KB Low Power Serial Srams: 32 K X 8 Bit OrganizationSyed ShahPas encore d'évaluation

- Adc 0804 PDFDocument18 pagesAdc 0804 PDFCinthya VillenaPas encore d'évaluation

- MC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738Document8 pagesMC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738greentea601Pas encore d'évaluation

- Document Title: GM76C256CDocument11 pagesDocument Title: GM76C256CFrenk EndyPas encore d'évaluation

- IS62C1024L: 128K X 8 Low Power Cmos Static RamDocument9 pagesIS62C1024L: 128K X 8 Low Power Cmos Static RamRoozbeh BahmanyarPas encore d'évaluation

- 27C020Document11 pages27C020technicalavrPas encore d'évaluation

- DM7474 PDFDocument5 pagesDM7474 PDFRaffi SkPas encore d'évaluation

- 74VHCT374A Octal D-Type Flip-Flop With 3-STATE Outputs: Features General DescriptionDocument9 pages74VHCT374A Octal D-Type Flip-Flop With 3-STATE Outputs: Features General DescriptionΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Hanbit Hmn1288D: Non-Volatile Sram Module 1mbit (128K X 8-Bit), 32Pin-Dip, 5V Part No. Hmn1288DDocument9 pagesHanbit Hmn1288D: Non-Volatile Sram Module 1mbit (128K X 8-Bit), 32Pin-Dip, 5V Part No. Hmn1288DDeepa DevarajPas encore d'évaluation

- Atmel AT250x0 MemoryDocument19 pagesAtmel AT250x0 MemoryNamburi NandanPas encore d'évaluation

- tosL30BL3 MBDocument30 pagestosL30BL3 MBrasrozi5170Pas encore d'évaluation

- MC34063ADocument15 pagesMC34063AAlfredo Valencia RodriguezPas encore d'évaluation

- Analog Devices REF01CSZ DatasheetDocument12 pagesAnalog Devices REF01CSZ DatasheetAurelian ZaharescuPas encore d'évaluation

- CL50 Rooftop Air Cool Air IOM 1107 EDocument78 pagesCL50 Rooftop Air Cool Air IOM 1107 EMarko BukovčanPas encore d'évaluation

- Bzv49 - Series - NXP - PDF Zenner SMD CodeDocument10 pagesBzv49 - Series - NXP - PDF Zenner SMD CodeAurelian ZaharescuPas encore d'évaluation

- BF 421Document5 pagesBF 421Aurelian ZaharescuPas encore d'évaluation

- Me 9926Document5 pagesMe 9926Aurelian ZaharescuPas encore d'évaluation

- Vdocuments - MX Rotalign Ultra System ManualDocument31 pagesVdocuments - MX Rotalign Ultra System ManualTanPas encore d'évaluation

- Datasheet AMX Navigate 2021 JB05588USDocument13 pagesDatasheet AMX Navigate 2021 JB05588USmanoellocoPas encore d'évaluation

- Dean of Industry Interface JDDocument3 pagesDean of Industry Interface JDKrushnasamy SuramaniyanPas encore d'évaluation

- TEK SAP 08 SodtwareArch ShowfilesDocument42 pagesTEK SAP 08 SodtwareArch Showfilesapi-3759021Pas encore d'évaluation

- Arturo B. Del Ayre's Curriculum Vitae & ResumeDocument14 pagesArturo B. Del Ayre's Curriculum Vitae & ResumeArturo Brondial del Ayre100% (6)

- Delta Tester 9424 Training ModuleDocument35 pagesDelta Tester 9424 Training ModuleNini FarribasPas encore d'évaluation

- CD Final PDFDocument140 pagesCD Final PDFGursimar SinghPas encore d'évaluation

- Man Inst Mru 5 r9Document148 pagesMan Inst Mru 5 r9Miguel Martinez100% (1)

- Travel Request Form: Traveller InformationDocument1 pageTravel Request Form: Traveller InformationMohammad Nabil AbdullahPas encore d'évaluation

- 1.2D Viewing TransformationsDocument127 pages1.2D Viewing TransformationsAbhigyan HarshaPas encore d'évaluation

- UPS Operating Modes: A Global StandardDocument8 pagesUPS Operating Modes: A Global StandardAmila KumanayakePas encore d'évaluation

- E WASTE Seminar ReportDocument27 pagesE WASTE Seminar Reportmonika thakurPas encore d'évaluation

- Blazing Angels - Manual For PCDocument16 pagesBlazing Angels - Manual For PCM_MolliPas encore d'évaluation

- Learning Unit 9Document26 pagesLearning Unit 9sphamandla kubhekaPas encore d'évaluation

- GCE Advanced Level - ICT - தரவுத்தள முகாமைத்துவ முறைமைDocument57 pagesGCE Advanced Level - ICT - தரவுத்தள முகாமைத்துவ முறைமைThanuPas encore d'évaluation

- Hydra Big TutorialDocument49 pagesHydra Big TutorialMicke OlofssonPas encore d'évaluation

- Online Dictionaries Today and TomorrowDocument16 pagesOnline Dictionaries Today and TomorrowGuillermo GonzálezPas encore d'évaluation

- Client Peripherals Product Lines 1Document27 pagesClient Peripherals Product Lines 1prakistaoPas encore d'évaluation

- Forecasting With EntropyDocument19 pagesForecasting With EntropyKuntal DasPas encore d'évaluation

- Simlab Section 9 - Mesh CleanupDocument19 pagesSimlab Section 9 - Mesh Cleanupvandamme789Pas encore d'évaluation

- Session 01Document58 pagesSession 01S SamPas encore d'évaluation

- Dcit 26 ReviewerDocument8 pagesDcit 26 ReviewerHunter KurusakiPas encore d'évaluation

- DiyuDocument8 pagesDiyunaturewisdomPas encore d'évaluation

- A Fully 3D Printable GlaDOS Robotic Ceiling Arm LaDocument36 pagesA Fully 3D Printable GlaDOS Robotic Ceiling Arm LaJosé Elías Garza VázquezPas encore d'évaluation

- LG 42LK450 (SM) PDFDocument72 pagesLG 42LK450 (SM) PDFSandroCezardeAraujoPas encore d'évaluation

- AX40 DatamodelDocument156 pagesAX40 Datamodelaxapta7Pas encore d'évaluation