Académique Documents

Professionnel Documents

Culture Documents

Saurabh Tripathi 201311013 Assignment

Transféré par

saurabh07tripathiTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Saurabh Tripathi 201311013 Assignment

Transféré par

saurabh07tripathiDroits d'auteur :

Formats disponibles

SAURABH TRIPATHI

201311013

ASSIGNMENT

Develop a Verilog HDL code for shift register functionality (74595) and test that it works upto

20 MHz frequency.

Please use the post place and route analysis to determine Fmax.

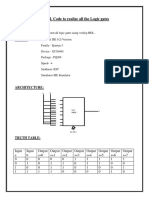

74ls595 is a 8-bit serial-in parallel out shift register. The data is shifted serially in 8-D Flipflops

and then transferred to storage registers. Shift registers have reset, clk, data-in. Storage

registers have input as output of the shift register. Tri-state buffer is used to enable output to

be seen parallelly.

Storage 0

Shifter 0

Shifter 1

Shifter 2

Shifter 3

Shifter 4

Shifter 5

Shifter 6

Shifter 7

Storage 1

Storage 2

Storage 3

Storage 4

Storage 5

Storage 6

Storage 7

ctrl

output

Verilog Code

Test bench

Simulation result

Synthesis report

Release 14.4 - xst P.49d (nt64)

Copyright (c) 1995-2012 Xilinx, Inc. All rights reserved.

--> Parameter TMPDIR set to xst/projnav.tmp

Total REAL time to Xst completion: 0.00 secs

Total CPU time to Xst completion: 0.20 secs

--> Parameter xsthdpdir set to xst

Total REAL time to Xst completion: 0.00 secs

Total CPU time to Xst completion: 0.20 secs

--> Reading design: shift_reg.prj

TABLE OF CONTENTS

1) Synthesis Options Summary

2) HDL Compilation

3) Design Hierarchy Analysis

4) HDL Analysis

5) HDL Synthesis

5.1) HDL Synthesis Report

6) Advanced HDL Synthesis

6.1) Advanced HDL Synthesis Report

7) Low Level Synthesis

8) Partition Report

9) Final Report

9.1) Device utilization summary

9.2) Partition Resource Summary

9.3) TIMING REPORT

=========================================================================

* Synthesis Options Summary *

=========================================================================

---- Source Parameters

Input File Name : "shift_reg.prj"

Input Format : mixed

Ignore Synthesis Constraint File : NO

---- Target Parameters

Output File Name : "shift_reg"

Output Format : NGC

Target Device : xc3s500e-4-vq100

---- Source Options

Top Module Name : shift_reg

Automatic FSM Extraction : YES

FSM Encoding Algorithm : Auto

Safe Implementation : No

FSM Style : LUT

RAM Extraction : Yes

RAM Style : Auto

ROM Extraction : Yes

Mux Style : Auto

Decoder Extraction : YES

Priority Encoder Extraction : Yes

Shift Register Extraction : YES

Logical Shifter Extraction : YES

XOR Collapsing : YES

ROM Style : Auto

Mux Extraction : Yes

Resource Sharing : YES

Asynchronous To Synchronous : NO

Multiplier Style : Auto

Automatic Register Balancing : No

---- Target Options

Add IO Buffers : YES

Global Maximum Fanout : 100000

Add Generic Clock Buffer(BUFG) : 24

Register Duplication : YES

Slice Packing : YES

Optimize Instantiated Primitives : NO

Use Clock Enable : Yes

Use Synchronous Set : Yes

Use Synchronous Reset : Yes

Pack IO Registers into IOBs : Auto

Equivalent register Removal : YES

---- General Options

Optimization Goal : Speed

Optimization Effort : 1

Keep Hierarchy : No

Netlist Hierarchy : As_Optimized

RTL Output : Yes

Global Optimization : AllClockNets

Read Cores : YES

Write Timing Constraints : NO

Cross Clock Analysis : NO

Hierarchy Separator : /

Bus Delimiter : <>

Case Specifier : Maintain

Slice Utilization Ratio : 100

BRAM Utilization Ratio : 100

Verilog 2001 : YES

Auto BRAM Packing : NO

Slice Utilization Ratio Delta : 5

=========================================================================

=========================================================================

* HDL Compilation *

=========================================================================

Compiling verilog file "shift_reg.v" in library work

Module <shift_reg> compiled

No errors in compilation

Analysis of file <"shift_reg.prj"> succeeded.

=========================================================================

* Design Hierarchy Analysis *

=========================================================================

Analyzing hierarchy for module <shift_reg> in library <work>.

=========================================================================

* HDL Analysis *

=========================================================================

Analyzing top module <shift_reg>.

Module <shift_reg> is correct for synthesis.

=========================================================================

* HDL Synthesis *

=========================================================================

Performing bidirectional port resolution...

INFO:Xst:2679 - Register <i> in unit <shift_reg> has a constant value of 0 during circuit operation. The

register is replaced by logic.

Synthesizing Unit <shift_reg>.

Related source file is "shift_reg.v".

Found 8-bit tristate buffer for signal <out>.

Found 8-bit register for signal <temp1>.

Found 8-bit register for signal <temp2>.

Summary:

inferred 16 D-type flip-flop(s).

inferred 8 Tristate(s).

Unit <shift_reg> synthesized.

=========================================================================

HDL Synthesis Report

Macro Statistics

# Registers : 9

1-bit register : 8

8-bit register : 1

# Tristates : 8

1-bit tristate buffer : 8

=========================================================================

=========================================================================

* Advanced HDL Synthesis *

=========================================================================

=========================================================================

Advanced HDL Synthesis Report

Macro Statistics

# Registers : 16

Flip-Flops : 16

=========================================================================

=========================================================================

* Low Level Synthesis *

=========================================================================

Optimizing unit <shift_reg> ...

Mapping all equations...

Building and optimizing final netlist ...

Found area constraint ratio of 100 (+ 5) on block shift_reg, actual ratio is 0.

Final Macro Processing ...

=========================================================================

Final Register Report

Macro Statistics

# Registers : 16

Flip-Flops : 16

=========================================================================

=========================================================================

* Partition Report *

=========================================================================

Partition Implementation Status

-------------------------------

No Partitions were found in this design.

-------------------------------

=========================================================================

* Final Report *

=========================================================================

Final Results

RTL Top Level Output File Name : shift_reg.ngr

Top Level Output File Name : shift_reg

Output Format : NGC

Optimization Goal : Speed

Keep Hierarchy : No

Design Statistics

# IOs : 12

Cell Usage :

# BELS : 1

# INV : 1

# FlipFlops/Latches : 16

# FDC : 8

# FDR : 8

# Clock Buffers : 1

# BUFGP : 1

# IO Buffers : 11

# IBUF : 3

# OBUFT : 8

=========================================================================

Device utilization summary:

---------------------------

Selected Device : 3s500evq100-4

Number of Slices: 9 out of 4656 0%

Number of Slice Flip Flops: 16 out of 9312 0%

Number of 4 input LUTs: 1 out of 9312 0%

Number of IOs: 12

Number of bonded IOBs: 12 out of 66 18%

Number of GCLKs: 1 out of 24 4%

---------------------------

Partition Resource Summary:

---------------------------

No Partitions were found in this design.

---------------------------

=========================================================================

TIMING REPORT

NOTE: THESE TIMING NUMBERS ARE ONLY A SYNTHESIS ESTIMATE.

FOR ACCURATE TIMING INFORMATION PLEASE REFER TO THE TRACE REPORT

GENERATED AFTER PLACE-and-ROUTE.

Clock Information:

------------------

-----------------------------------+------------------------+-------+

Clock Signal | Clock buffer(FF name) | Load |

-----------------------------------+------------------------+-------+

clk | BUFGP | 16 |

-----------------------------------+------------------------+-------+

Asynchronous Control Signals Information:

----------------------------------------

-----------------------------------+------------------------+-------+

Control Signal | Buffer(FF name) | Load |

-----------------------------------+------------------------+-------+

reset | IBUF | 8 |

-----------------------------------+------------------------+-------+

Timing Summary:

---------------

Speed Grade: -4

Minimum period: 1.346ns (Maximum Frequency: 742.942MHz)

Minimum input arrival time before clock: 3.163ns

Maximum output required time after clock: 4.283ns

Maximum combinational path delay: 6.371ns

Timing Detail:

--------------

All values displayed in nanoseconds (ns)

=========================================================================

Timing constraint: Default period analysis for Clock 'clk'

Clock period: 1.346ns (frequency: 742.942MHz)

Total number of paths / destination ports: 15 / 15

-------------------------------------------------------------------------

Delay: 1.346ns (Levels of Logic = 0)

Source: temp1_7 (FF)

Destination: temp1_6 (FF)

Source Clock: clk rising

Destination Clock: clk rising

Data Path: temp1_7 to temp1_6

Gate Net

Cell:in->out fanout Delay Delay Logical Name (Net Name)

---------------------------------------- ------------

FDC:C->Q 2 0.591 0.447 temp1_7 (temp1_7)

FDC:D 0.308 temp1_6

----------------------------------------

Total 1.346ns (0.899ns logic, 0.447ns route)

(66.8% logic, 33.2% route)

=========================================================================

Timing constraint: Default OFFSET IN BEFORE for Clock 'clk'

Total number of paths / destination ports: 9 / 9

-------------------------------------------------------------------------

Offset: 3.163ns (Levels of Logic = 1)

Source: reset (PAD)

Destination: temp2_0 (FF)

Destination Clock: clk rising

Data Path: reset to temp2_0

Gate Net

Cell:in->out fanout Delay Delay Logical Name (Net Name)

---------------------------------------- ------------

IBUF:I->O 16 1.218 1.034 reset_IBUF (reset_IBUF)

FDR:R 0.911 temp2_0

----------------------------------------

Total 3.163ns (2.129ns logic, 1.034ns route)

(67.3% logic, 32.7% route)

=========================================================================

Timing constraint: Default OFFSET OUT AFTER for Clock 'clk'

Total number of paths / destination ports: 8 / 8

-------------------------------------------------------------------------

Offset: 4.283ns (Levels of Logic = 1)

Source: temp2_7 (FF)

Destination: out<7> (PAD)

Source Clock: clk rising

Data Path: temp2_7 to out<7>

Gate Net

Cell:in->out fanout Delay Delay Logical Name (Net Name)

---------------------------------------- ------------

FDR:C->Q 1 0.591 0.420 temp2_7 (temp2_7)

OBUFT:I->O 3.272 out_7_OBUFT (out<7>)

----------------------------------------

Total 4.283ns (3.863ns logic, 0.420ns route)

(90.2% logic, 9.8% route)

=========================================================================

Timing constraint: Default path analysis

Total number of paths / destination ports: 8 / 8

-------------------------------------------------------------------------

Delay: 6.371ns (Levels of Logic = 3)

Source: ctrl (PAD)

Destination: out<7> (PAD)

Data Path: ctrl to out<7>

Gate Net

Cell:in->out fanout Delay Delay Logical Name (Net Name)

---------------------------------------- ------------

IBUF:I->O 1 1.218 0.420 ctrl_IBUF (ctrl_IBUF)

INV:I->O 8 0.704 0.757 ctrl_inv1_INV_0 (ctrl_inv)

OBUFT:T->O 3.272 out_7_OBUFT (out<7>)

----------------------------------------

Total 6.371ns (5.194ns logic, 1.177ns route)

(81.5% logic, 18.5% route)

=========================================================================

Total REAL time to Xst completion: 10.00 secs

Total CPU time to Xst completion: 9.49 secs

-->

Total memory usage is 267872 kilobytes

Number of errors : 0 ( 0 filtered)

Number of warnings : 0 ( 0 filtered)

Number of infos : 1 ( 0 filtered)

RTL schematic

Technology schematic

Post place and route synthesis

Started : "Synthesize - XST".

Running xst...

Command Line: xst -intstyle ise -ifn "E:/daiict/xilinx/my_work/shifting/shift_reg.xst" -ofn

"E:/daiict/xilinx/my_work/shifting/shift_reg.syr"

Reading design: shift_reg.prj

=========================================================================

* HDL Compilation *

=========================================================================

Compiling verilog file "shift_reg.v" in library work

Module <shift_reg> compiled

No errors in compilation

Analysis of file <"shift_reg.prj"> succeeded.

=========================================================================

* Design Hierarchy Analysis *

=========================================================================

Analyzing hierarchy for module <shift_reg> in library <work>.

=========================================================================

* HDL Analysis *

=========================================================================

Analyzing top module <shift_reg>.

Module <shift_reg> is correct for synthesis.

=========================================================================

* HDL Synthesis *

=========================================================================

Performing bidirectional port resolution...

INFO:Xst:2679 - Register <i> in unit <shift_reg> has a constant value of 0 during circuit operation. The

register is replaced by logic.

Synthesizing Unit <shift_reg>.

Related source file is "shift_reg.v".

Found 8-bit tristate buffer for signal <out>.

Found 8-bit register for signal <temp1>.

Found 8-bit register for signal <temp2>.

Summary:

inferred 16 D-type flip-flop(s).

inferred 8 Tristate(s).

Unit <shift_reg> synthesized.

=========================================================================

HDL Synthesis Report

Macro Statistics

# Registers : 9

1-bit register : 8

8-bit register : 1

# Tristates : 8

1-bit tristate buffer : 8

=========================================================================

=========================================================================

* Advanced HDL Synthesis *

=========================================================================

=========================================================================

Advanced HDL Synthesis Report

Macro Statistics

# Registers : 16

Flip-Flops : 16

=========================================================================

=========================================================================

* Low Level Synthesis *

=========================================================================

Optimizing unit <shift_reg> ...

Mapping all equations...

Building and optimizing final netlist ...

Found area constraint ratio of 100 (+ 5) on block shift_reg, actual ratio is 0.

Final Macro Processing ...

=========================================================================

Final Register Report

Macro Statistics

# Registers : 16

Flip-Flops : 16

=========================================================================

=========================================================================

* Partition Report *

=========================================================================

Partition Implementation Status

-------------------------------

No Partitions were found in this design.

-------------------------------

=========================================================================

* Final Report *

=========================================================================

Clock Information:

------------------

-----------------------------------+------------------------+-------+

Clock Signal | Clock buffer(FF name) | Load |

-----------------------------------+------------------------+-------+

clk | BUFGP | 16 |

-----------------------------------+------------------------+-------+

Asynchronous Control Signals Information:

----------------------------------------

-----------------------------------+------------------------+-------+

Control Signal | Buffer(FF name) | Load |

-----------------------------------+------------------------+-------+

reset | IBUF | 8 |

-----------------------------------+------------------------+-------+

Timing Summary:

---------------

Speed Grade: -4

Minimum period: 1.346ns (Maximum Frequency: 742.942MHz)

Minimum input arrival time before clock: 3.163ns

Maximum output required time after clock: 4.283ns

Maximum combinational path delay: 6.371ns

=========================================================================

Process "Synthesize - XST" completed successfully

Started : "Translate".

Running ngdbuild...

Command Line: ngdbuild -intstyle ise -dd _ngo -nt timestamp -i -p xc3s500e-fg320-4 shift_reg.ngc

shift_reg.ngd

Command Line: C:\Xilinx\14.7\ISE_DS\ISE\bin\nt\unwrapped\ngdbuild.exe -intstyle

ise -dd _ngo -nt timestamp -i -p xc3s500e-fg320-4 shift_reg.ngc shift_reg.ngd

Reading NGO file "E:/daiict/xilinx/my_work/shifting/shift_reg.ngc" ...

Gathering constraint information from source properties...

Done.

Resolving constraint associations...

Checking Constraint Associations...

Done...

Checking expanded design ...

Partition Implementation Status

-------------------------------

No Partitions were found in this design.

-------------------------------

NGDBUILD Design Results Summary:

Number of errors: 0

Number of warnings: 0

Writing NGD file "shift_reg.ngd" ...

Total REAL time to NGDBUILD completion: 2 sec

Total CPU time to NGDBUILD completion: 2 sec

Writing NGDBUILD log file "shift_reg.bld"...

NGDBUILD done.

Process "Translate" completed successfully

Started : "Map".

Running map...

Command Line: map -intstyle ise -p xc3s500e-fg320-4 -cm area -ir off -pr off -c 100 -o shift_reg_map.ncd

shift_reg.ngd shift_reg.pcf

Using target part "3s500efg320-4".

Mapping design into LUTs...

Running directed packing...

Running delay-based LUT packing...

Running related packing...

Updating timing models...

Design Summary:

Number of errors: 0

Number of warnings: 0

Logic Utilization:

Number of Slice Flip Flops: 16 out of 9,312 1%

Logic Distribution:

Number of occupied Slices: 8 out of 4,656 1%

Number of Slices containing only related logic: 8 out of 8 100%

Number of Slices containing unrelated logic: 0 out of 8 0%

*See NOTES below for an explanation of the effects of unrelated logic.

Number of bonded IOBs: 12 out of 232 5%

Number of BUFGMUXs: 1 out of 24 4%

Average Fanout of Non-Clock Nets: 2.53

Peak Memory Usage: 202 MB

Total REAL time to MAP completion: 4 secs

Total CPU time to MAP completion: 2 secs

NOTES:

Related logic is defined as being logic that shares connectivity - e.g. two

LUTs are "related" if they share common inputs. When assembling slices,

Map gives priority to combine logic that is related. Doing so results in

the best timing performance.

Unrelated logic shares no connectivity. Map will only begin packing

unrelated logic into a slice once 99% of the slices are occupied through

related logic packing.

Note that once logic distribution reaches the 99% level through related

logic packing, this does not mean the device is completely utilized.

Unrelated logic packing will then begin, continuing until all usable LUTs

and FFs are occupied. Depending on your timing budget, increased levels of

unrelated logic packing may adversely affect the overall timing performance

of your design.

Mapping completed.

See MAP report file "shift_reg_map.mrp" for details.

Process "Map" completed successfully

Started : "Place & Route".

Running par...

Command Line: par -w -intstyle ise -ol high -t 1 shift_reg_map.ncd shift_reg.ncd shift_reg.pcf

Constraints file: shift_reg.pcf.

Loading device for application Rf_Device from file '3s500e.nph' in environment

C:\Xilinx\14.7\ISE_DS\ISE\.

"shift_reg" is an NCD, version 3.2, device xc3s500e, package fg320, speed -4

Initializing temperature to 85.000 Celsius. (default - Range: -40.000 to 100.000 Celsius)

Initializing voltage to 1.140 Volts. (default - Range: 1.140 to 1.320 Volts)

INFO:Par:282 - No user timing constraints were detected or you have set the option to ignore timing

constraints ("par

-x"). Place and Route will run in "Performance Evaluation Mode" to automatically improve the

performance of all

internal clocks in this design. Because there are not defined timing requirements, a timing score will

not be

reported in the PAR report in this mode. The PAR timing summary will list the performance achieved

for each clock.

Note: For the fastest runtime, set the effort level to "std". For best performance, set the effort level to

"high".

Device speed data version: "PRODUCTION 1.27 2013-10-13".

Design Summary Report:

Number of External IOBs 12 out of 232 5%

Number of External Input IOBs 4

Number of External Input IBUFs 4

Number of External Output IOBs 8

Number of External Output IOBs 8

Number of External Bidir IOBs 0

Number of BUFGMUXs 1 out of 24 4%

Number of Slices 8 out of 4656 1%

Number of SLICEMs 0 out of 2328 0%

Overall effort level (-ol): High

Placer effort level (-pl): High

Placer cost table entry (-t): 1

Router effort level (-rl): High

Starting initial Timing Analysis. REAL time: 2 secs

Finished initial Timing Analysis. REAL time: 2 secs

Starting Placer

Total REAL time at the beginning of Placer: 2 secs

Total CPU time at the beginning of Placer: 1 secs

Phase 1.1 Initial Placement Analysis

Phase 1.1 Initial Placement Analysis (Checksum:d7) REAL time: 3 secs

Phase 2.7 Design Feasibility Check

Phase 2.7 Design Feasibility Check (Checksum:d7) REAL time: 3 secs

Phase 3.31 Local Placement Optimization

Phase 3.31 Local Placement Optimization (Checksum:d7) REAL time: 3 secs

Phase 4.2 Initial Clock and IO Placement

..............

Phase 4.2 Initial Clock and IO Placement (Checksum:c2eadd7) REAL time: 3 secs

Phase 5.30 Global Clock Region Assignment

Phase 5.30 Global Clock Region Assignment (Checksum:c2eadd7) REAL time: 3 secs

Phase 6.36 Local Placement Optimization

Phase 6.36 Local Placement Optimization (Checksum:c2eadd7) REAL time: 3 secs

Phase 7.3 Local Placement Optimization

.............

Phase 7.3 Local Placement Optimization (Checksum:de382d37) REAL time: 3 secs

Phase 8.5 Local Placement Optimization

Phase 8.5 Local Placement Optimization (Checksum:de382d37) REAL time: 3 secs

Phase 9.8 Global Placement

..

Phase 9.8 Global Placement (Checksum:762a8db3) REAL time: 5 secs

Phase 10.5 Local Placement Optimization

Phase 10.5 Local Placement Optimization (Checksum:762a8db3) REAL time: 5 secs

Phase 11.18 Placement Optimization

Phase 11.18 Placement Optimization (Checksum:6c946ce9) REAL time: 5 secs

Phase 12.5 Local Placement Optimization

Phase 12.5 Local Placement Optimization (Checksum:6c946ce9) REAL time: 5 secs

Total REAL time to Placer completion: 5 secs

Total CPU time to Placer completion: 3 secs

Writing design to file shift_reg.ncd

Starting Router

Phase 1 : 50 unrouted; REAL time: 9 secs

Phase 2 : 41 unrouted; REAL time: 9 secs

Phase 3 : 8 unrouted; REAL time: 9 secs

Phase 4 : 10 unrouted; (Par is working to improve performance) REAL time: 9 secs

Phase 5 : 0 unrouted; (Par is working to improve performance) REAL time: 9 secs

Updating file: shift_reg.ncd with current fully routed design.

Phase 6 : 0 unrouted; (Par is working to improve performance) REAL time: 9 secs

Phase 7 : 0 unrouted; (Par is working to improve performance) REAL time: 10 secs

Updating file: shift_reg.ncd with current fully routed design.

Phase 8 : 0 unrouted; (Par is working to improve performance) REAL time: 10 secs

Phase 9 : 0 unrouted; (Par is working to improve performance) REAL time: 10 secs

Phase 10 : 0 unrouted; (Par is working to improve performance) REAL time: 10 secs

Phase 11 : 0 unrouted; (Par is working to improve performance) REAL time: 10 secs

Total REAL time to Router completion: 10 secs

Total CPU time to Router completion: 8 secs

Partition Implementation Status

-------------------------------

No Partitions were found in this design.

-------------------------------

Generating "PAR" statistics.

**************************

Generating Clock Report

**************************

+---------------------+--------------+------+------+------------+-------------+

| Clock Net | Resource |Locked|Fanout|Net Skew(ns)|Max Delay(ns)|

+---------------------+--------------+------+------+------------+-------------+

| clk_BUFGP | BUFGMUX_X2Y10| No | 8 | 0.010 | 0.176 |

+---------------------+--------------+------+------+------------+-------------+

* Net Skew is the difference between the minimum and maximum routing

only delays for the net. Note this is different from Clock Skew which

is reported in TRCE timing report. Clock Skew is the difference between

the minimum and maximum path delays which includes logic delays.

* The fanout is the number of component pins not the individual BEL loads,

for example SLICE loads not FF loads.

Timing Score: 0 (Setup: 0, Hold: 0)

Asterisk (*) preceding a constraint indicates it was not met.

This may be due to a setup or hold violation.

----------------------------------------------------------------------------------------------------------

Constraint | Check | Worst Case | Best Case | Timing | Timing

| | Slack | Achievable | Errors | Score

----------------------------------------------------------------------------------------------------------

Autotimespec constraint for clock net clk | SETUP | N/A| 1.771ns| N/A| 0

_BUFGP | HOLD | 1.021ns| | 0| 0

----------------------------------------------------------------------------------------------------------

All constraints were met.

INFO:Timing:2761 - N/A entries in the Constraints List may indicate that the

constraint is not analyzed due to the following: No paths covered by this

constraint; Other constraints intersect with this constraint; or This

constraint was disabled by a Path Tracing Control. Please run the Timespec

Interaction Report (TSI) via command line (trce tsi) or Timing Analyzer GUI.

Generating Pad Report.

All signals are completely routed.

Total REAL time to PAR completion: 10 secs

Total CPU time to PAR completion: 8 secs

Peak Memory Usage: 211 MB

Placement: Completed - No errors found.

Routing: Completed - No errors found.

Number of error messages: 0

Number of warning messages: 0

Number of info messages: 1

Writing design to file shift_reg.ncd

PAR done!

Process "Place & Route" completed successfully

Started : "Generate Post-Place & Route Static Timing".

Running trce...

Command Line: trce -intstyle ise -v 3 -s 4 -n 3 -fastpaths -xml shift_reg.twx shift_reg.ncd -o shift_reg.twr

shift_reg.pcf

Loading device for application Rf_Device from file '3s500e.nph' in environment

C:\Xilinx\14.7\ISE_DS\ISE\.

"shift_reg" is an NCD, version 3.2, device xc3s500e, package fg320, speed -4

Analysis completed Fri Mar 07 00:42:11 2014

--------------------------------------------------------------------------------

Generating Report ...

Number of warnings: 0

Total time: 1 secs

Process "Generate Post-Place & Route Static Timing" completed successfully

Vous aimerez peut-être aussi

- Vlsi Waveform 1Document32 pagesVlsi Waveform 1gr_391129080Pas encore d'évaluation

- VLSI ProgramsDocument159 pagesVLSI Programsr44257345Pas encore d'évaluation

- System Design Using PLL: EX - NO: 3 DATE: 3.3.2011Document11 pagesSystem Design Using PLL: EX - NO: 3 DATE: 3.3.2011pstephen0Pas encore d'évaluation

- Final Record 1st Sem MtechDocument106 pagesFinal Record 1st Sem Mtechvenkata satishPas encore d'évaluation

- Objective:: MELAY FSM (0110)Document21 pagesObjective:: MELAY FSM (0110)siddhiPas encore d'évaluation

- Tugas Praktikum VHDL 3.2 MultiplexerDocument18 pagesTugas Praktikum VHDL 3.2 MultiplexerEdy PribadiPas encore d'évaluation

- Date: AIM:-: 1. Logic GatesDocument52 pagesDate: AIM:-: 1. Logic Gatesseena_123Pas encore d'évaluation

- Synopsys LabDocument13 pagesSynopsys Lab黃于瑄Pas encore d'évaluation

- SynthesisDocument2 pagesSynthesiskingmibPas encore d'évaluation

- ASIC LabDocument75 pagesASIC LabMayur AgarwalPas encore d'évaluation

- Vlsi LabDocument161 pagesVlsi LabNaveen Kumar RavillaPas encore d'évaluation

- Design and implement CMOS digital/analog circuitsDocument86 pagesDesign and implement CMOS digital/analog circuitslakshmikala giddaluruPas encore d'évaluation

- VLSI Record 6th Sem NIT TrichyDocument67 pagesVLSI Record 6th Sem NIT TrichysumantabosePas encore d'évaluation

- Clock Calibration Alarm Remove For IBSDocument26 pagesClock Calibration Alarm Remove For IBSasusf6ve100% (1)

- Chapter 6 Logic SynthesisDocument14 pagesChapter 6 Logic Synthesishafiz0007Pas encore d'évaluation

- Lec39 FullDocument27 pagesLec39 FullnmaravindPas encore d'évaluation

- Half Adder Using Different Data Flow Models: Experiment No: 1Document49 pagesHalf Adder Using Different Data Flow Models: Experiment No: 1Nihas SirajdheenPas encore d'évaluation

- A Division of Labor: B.1 Test Labkit.vDocument31 pagesA Division of Labor: B.1 Test Labkit.vraymar2kPas encore d'évaluation

- Test Verification GuideDocument7 pagesTest Verification GuideArchana KorePas encore d'évaluation

- Single Precision Floating Point UnitDocument45 pagesSingle Precision Floating Point UnitSumeet SauravPas encore d'évaluation

- Thiet Ke Vi Mach Voi HDL Pham Quoc Cuong Chapter7 Parameters Functions Task (Cuuduongthancong - Com)Document38 pagesThiet Ke Vi Mach Voi HDL Pham Quoc Cuong Chapter7 Parameters Functions Task (Cuuduongthancong - Com)Smith JadenPas encore d'évaluation

- Lecture2 CuongDocument51 pagesLecture2 Cuongsongoku711Pas encore d'évaluation

- Digital Design With HDLDocument29 pagesDigital Design With HDLw.nPas encore d'évaluation

- Digital Design and Synthesis: Fall 09Document35 pagesDigital Design and Synthesis: Fall 09Lua Dinh ThiPas encore d'évaluation

- Cluster Mode Map To 7-ModeDocument61 pagesCluster Mode Map To 7-Modestoarge_kingsPas encore d'évaluation

- PS2 Controller LCD DisplayDocument28 pagesPS2 Controller LCD DisplayAlan BasiliskPas encore d'évaluation

- Realtek RF MP Tool Guidelines V19Document24 pagesRealtek RF MP Tool Guidelines V19Luan SantosPas encore d'évaluation

- ET5080E Digital Design Using Verilog HDL: Fall 21Document35 pagesET5080E Digital Design Using Verilog HDL: Fall 21ifirePas encore d'évaluation

- UartDocument19 pagesUartapi-26691029Pas encore d'évaluation

- DSD - 1Document67 pagesDSD - 1Mehzin BakerPas encore d'évaluation

- IRF Piso4 TechDocument1 959 pagesIRF Piso4 TechLeonardo De LucaPas encore d'évaluation

- Unit 3 DSDDocument107 pagesUnit 3 DSDGuru VelmathiPas encore d'évaluation

- Gs0001 Xilinx CH 4 HDL Coding TechniquesDocument102 pagesGs0001 Xilinx CH 4 HDL Coding TechniquesterteryPas encore d'évaluation

- Synthesizeable Verilog Code ExamplesDocument9 pagesSynthesizeable Verilog Code ExamplesSiva Krishna BandiPas encore d'évaluation

- VLSI Lab Record 2023Document47 pagesVLSI Lab Record 2023HARISABARISH J 21ECPas encore d'évaluation

- Memory BIST TutorialDocument22 pagesMemory BIST Tutorialdkadao100% (3)

- Collect Fault FinishDocument119 pagesCollect Fault Finish8051Pas encore d'évaluation

- Single Precision Floating Point UnitDocument46 pagesSingle Precision Floating Point UnitSumeet SauravPas encore d'évaluation

- Verilog Codes for Code Converters and ComparatorDocument53 pagesVerilog Codes for Code Converters and Comparatorvenkata satishPas encore d'évaluation

- DSD Lab 9 HandoutDocument5 pagesDSD Lab 9 HandoutFaiza Tabassam 546-FET/BSEE/F19Pas encore d'évaluation

- Lab 4Document9 pagesLab 4Waqas Bin KhalidPas encore d'évaluation

- Common Problems in Clock Tree SynthesisDocument3 pagesCommon Problems in Clock Tree SynthesisSri Krishna Chaitanya100% (1)

- Lab 5 DR Muslim (Latest)Document15 pagesLab 5 DR Muslim (Latest)a ThanhPas encore d'évaluation

- Vlsi Lab Expt - 9&10Document37 pagesVlsi Lab Expt - 9&10gayathriPas encore d'évaluation

- Compile With Scan InsertDocument17 pagesCompile With Scan InsertjagruthimsPas encore d'évaluation

- Logic Synthesis 5 FSM and Retiming PDFDocument6 pagesLogic Synthesis 5 FSM and Retiming PDFAre VijayPas encore d'évaluation

- Data Logic Cells Unit3 AsicDocument34 pagesData Logic Cells Unit3 AsicYashwanthReddyPas encore d'évaluation

- Lab2 DCDocument52 pagesLab2 DCRavi Krishna MalkaPas encore d'évaluation

- Best Practices Oracle Cluster Ware Session 355Document30 pagesBest Practices Oracle Cluster Ware Session 355Fakiruddin KhanPas encore d'évaluation

- UNIT2Document59 pagesUNIT2YashwanthReddyPas encore d'évaluation

- 15EC302J Vlsi Lab Students PDFDocument54 pages15EC302J Vlsi Lab Students PDFakaash ramnathPas encore d'évaluation

- Vineeth Full PD FlowDocument21 pagesVineeth Full PD FlowprakashPas encore d'évaluation

- MAJOR DB2 CONFIGURATION DOCUMENTDocument6 pagesMAJOR DB2 CONFIGURATION DOCUMENTDevender5194Pas encore d'évaluation

- PDF 2Document13 pagesPDF 2Nivedita Acharyya 2035Pas encore d'évaluation

- 03 AVR ProgrammingDocument38 pages03 AVR ProgrammingPriscillaPas encore d'évaluation

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960D'EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Pas encore d'évaluation

- 61 64WV51232Axx BXXDocument19 pages61 64WV51232Axx BXXsaurabh07tripathiPas encore d'évaluation

- Understanding The Basics of Setup and Hold TimeDocument7 pagesUnderstanding The Basics of Setup and Hold TimeLatasha PerryPas encore d'évaluation

- Adc CharacterisationDocument3 pagesAdc Characterisationsaurabh07tripathiPas encore d'évaluation

- Abcs of AdcsDocument63 pagesAbcs of AdcsMTReis_Pas encore d'évaluation

- Standard Cell LibrariesDocument11 pagesStandard Cell Librariessaurabh07tripathiPas encore d'évaluation

- Atmel 8456 8 and 32 Bit AVR Microcontrollers AVR127 Understanding ADC Parameters Application NoteDocument20 pagesAtmel 8456 8 and 32 Bit AVR Microcontrollers AVR127 Understanding ADC Parameters Application NoteSapna NarayananPas encore d'évaluation

- Transmission Line TerminationsDocument12 pagesTransmission Line TerminationsMaham TariqPas encore d'évaluation

- Saurabh Tripathi 201311013 AssignmentDocument23 pagesSaurabh Tripathi 201311013 Assignmentsaurabh07tripathiPas encore d'évaluation

- Receiver: Max Speed 115.2 KB/psDocument3 pagesReceiver: Max Speed 115.2 KB/pssaurabh07tripathiPas encore d'évaluation

- HELINA MISSILE GUIDANCE SYSTEMDocument10 pagesHELINA MISSILE GUIDANCE SYSTEMsaurabh07tripathiPas encore d'évaluation