Académique Documents

Professionnel Documents

Culture Documents

Chapitre 8

Transféré par

Abdessalem Mohamed AchrafTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Chapitre 8

Transféré par

Abdessalem Mohamed AchrafDroits d'auteur :

Formats disponibles

CH VIII Fabrication des circuits

Composants lmentaires associes

Connexions et boitiers

Vitesse de fonctionnement, Vitesse de fonctionnement, Vitesse de fonctionnement, Vitesse de fonctionnement,

consommation et performances. consommation et performances.

Obsolescence programme Obsolescence programme

Remerciements

F Dupont;

Ainsi que

M Angenieux ;

Michal Beuve / IPNL/ UCB Lyon1 2

M Angenieux ;

M. Boylestad ;

M. Nashelsky ;

M. Herv.

Plan du cours

Fabrication des circuits

Composants lmentaires associes

Diode

Transistor

Mmoire

Michal Beuve / IPNL/ UCB Lyon1 3

Connexions et boitiers

Vitesse de fonctionnement, consommation et performances Vitesse de fonctionnement, consommation et performances

Obsolescence programme Obsolescence programme

La jonction PN (diode)

diffusion des porteurs libres

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

P

N

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

+

+

+

-

-

-

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

P

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

N

Michal Beuve / IPNL/ UCB Lyon1 4

+

+

+

+

+

+

+

+

+

+

- -

-

-

-

-

-

-

- -

Diffusion

Recombinaisons de paires lectron-trou

+

+

+

+

+

+

+

+

+

+

-

-

-

-

-

-

-

-

-

-

Fabrication dune diode jonction

N

P

P

N

Jonction PN

Michal Beuve / IPNL/ UCB Lyon1 5

Le afer

Germe

Monocristal

de Si

Sciage,

Tirage

Michal Beuve / IPNL/ UCB Lyon1 6

Si fondu

Silicium trs pur et monocristallin

Sciage,

polissage

R!alisation de la jonction PN

Rsine photosensible

Michal Beuve / IPNL/ UCB Lyon1 7

Substrat (Silicium pur )

Couche pitaxiale de S

i

Oxydation (S

i

O

2

)

Rsine photosensible

R!alisation de la jonction PN

Michal Beuve / IPNL/ UCB Lyon1 8

R!alisation de la jonction PN

Rsine photosensible

Masque

du dessin

raliser

Rsine insole

Rayonnement UV

Michal Beuve / IPNL/ UCB Lyon1 9

Substrat (Silicium pur )

Couche pitaxiale de S

i

Oxydation (S

i

O

2

)

Rsine photosensible

Rsine insole

polymrise

Report du mas"ue

Rsine insole

polymrise

Solvant Solvant

Dessin report sur la rsine

rsistante lacide

Michal Beuve / IPNL/ UCB Lyon1 10

Substrat (Silicium pur )

Couche pitaxiale de S

i

S

i

O

2

#ra$ure du %

i

&

'

Rsine insole

polymrise

SO

2

Acide fluorhydrique Acide fluorhydrique

Fentre

dans le S

i

O

2

pour le

dopage

Michal Beuve / IPNL/ UCB Lyon1 11

Substrat (Silicium pur )

Couche pitaxiale de S

i

S

i

O

2

dopage

slectif

S

i

O

2

(opa)e s!lectif P

S

i

intrinsque

S

i

dop P

Premier caisson

A

Implantation dions accepteur

Michal Beuve / IPNL/ UCB Lyon1 12

Substrat (Silicium pur )

S

i

intrinsque

S

i

dop P

(opa)e s!lectif P

Rsine masquage insolation nettoyage gravure dcapage dopage N

S

i

dop N

S

i

dop P

Michal Beuve / IPNL/ UCB Lyon1 13

Substrat (Silicium pur )

S

i

intrinsque

Substrat

Dpt dor

(aprs masquage)

La puce pr*te mettre en bo+tier

S

i

dop P

Prise de contact

aprs dcoupage

Passivation S

i

dop N

Michal Beuve / IPNL/ UCB Lyon1 14

Substrat

S

i

intrinsque

,uel"ues e-emples de circuits int!)r!s

Michal Beuve / IPNL/ UCB Lyon1 15

Plan du cours

Fabrication des circuits

Composants lmentaires associes (diode,

transistor),

Diode

Transistor

Michal Beuve / IPNL/ UCB Lyon1 16

Transistor

Mmoire

Connexion et boitier

Connexion et boitier

Vitesse de fonctionnement, consommation et Vitesse de fonctionnement, consommation et

performances. performances.

1948 Le transistor

1960 Les premiers C.I.

1970 Le microprocesseur

1980 Le PC

,uel"ues rep.res/

Michal Beuve / IPNL/ UCB Lyon1 17

1980 Le PC

1990 Dbuts dinternet

2000 Lexplosion des tlcom mobiles

2010 Le rseau global trs haut

dbit ?

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

P +

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

P

Le transistor bipolaire

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

N

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

P P

-

-

-

-

+

+

+

+

-

-

-

-

+

+

+

+

Michal Beuve / IPNL/ UCB Lyon1 18

Emetteur Base Collecteur

PNP PNP

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

P

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

N N +

+

+

+

+

+

+

+

-

-

-

-

-

-

-

-

Le transistor bipolaire

Michal Beuve / IPNL/ UCB Lyon1 19

Emetteur Base Collecteur

- - - - - -

NPN NPN

R!alisation tec0nolo)i"ue

N

Base Base

Dopage faible Dopage faible

Emetteur Emetteur

Dopage fort Dopage fort

Michal Beuve / IPNL/ UCB Lyon1 20

Substrat (Silicium pur )

S

i

intrinsque

N

P

N

Collecteur Collecteur

Dopage moyen Dopage moyen

Base Base

mince mince

Le transistor 1&%F23

FET = Field Effect Transistor

Catgorie de transistor monopolaire

Commande

par le champ appliqu entre la grille (G) et la source (S)

du courant entre la source (G) et le drain (D)

Michal Beuve / IPNL/ UCB Lyon1 21

MOS = Mtal Oxyde Semi-conducteur

Couche disolant => faible courant dentre

Utilis notamment dans les mmoires (USB)

+++ Sa consommation moindre que celle du transistor

bipolaire et sa tenue en tension meilleure

- - - Sensible au chargement et un peu lent

de Cyril BUTTAY

Mtal Mtal

Le transistor 1&% appau$rissement

Source Source

Drain Drain

Grille Grille

Substrat Substrat

Oxyde (isolant) Oxyde (isolant)

N+ N+

Contact

ohmique

Canal N Canal N

Michal Beuve / IPNL/ UCB Lyon1 22

V

GS

= 0 et V

GS

>0

Courant depuis la source vers le drain par le canal

Substrat P

Mtal Mtal

Le transistor 1&% appau$rissement

Source Source

Drain Drain

Grille Grille

Substrat Substrat

Oxyde (isolant) Oxyde (isolant)

N+ N+

Contact

ohmique

- - - - - - - -

+ + + + + + + +

Michal Beuve / IPNL/ UCB Lyon1 23

pinc

V

GS

< 0

N+ N+

Canal N Canal N

I

D

V

GS

-V

p

V

GS

>0

possible

Substrat P

Mtal Mtal

Le transistor 1&% appau$rissement

Source Source

Drain Drain

Grille Grille

Substrat Substrat

Oxyde (isolant) Oxyde (isolant)

N+ N+

Contact

ohmique

Canal N Canal N

Michal Beuve / IPNL/ UCB Lyon1 24

Note : existence dune saturation si la tension entre le

drain et la grille devient trop forte

En effet, partir d'une tension de drain suprieure la

tension de grille (moins la tension de seuil), les

lectrons disparaissent au voisinage du drain, le

courant sature.

I

D

V

DS

Substrat P

Mtal Mtal

Le transistor 1&% enric0issement

Source Source

Drain Drain

Grille Grille

Substrat Substrat

Oxyde (isolant) Oxyde (isolant)

N+ N+

Contact

ohmique

Michal Beuve / IPNL/ UCB Lyon1 25

Substrat P

Pas de canal Pas de canal

N initial N initial

Pas de courant source -drain

Mtal Mtal

Le transistor 1&% enric0issement

Oxyde (isolant) Oxyde (isolant)

Source Source

Drain Drain

Grille Grille

Substrat Substrat

N+ N+

Contact

ohmique

--------

++++++++

Michal Beuve / IPNL/ UCB Lyon1 26

I

D

V

GS

V

T

V

GS

> 0

=> accumulation de porteur N prs de lisolant

=> Cration dun canal N induit

=> Gnration dun courant sourcedrain partir dun

seuil

Substrat P

In$erseur N1&% r!sistance

I

D

V

GS

=5v

V

GS

=6v

V

GS

=7v

V

GS

=8.5v

V

GS

=9v

V

GS

=3v

V

DD

V

GS

V

DS

R

V

GS

=8.5v

Michal Beuve / IPNL/ UCB Lyon1 27

V

DS

1 v 5 v

10 v

V

GS

=3v

V

GS

V

DS

V

GS

7v

3v

10v

Transistor MOSFET

enrichissement

In$erseur C1&%

I

D

V

D

D

V

S

V =<6

V

GS

=7v

V

GS

=9v

V

GS

=8v

Michal Beuve / IPNL/ UCB Lyon1 28

Blocage des 2 Transistors

V

DS

1 v 5 v

10 v

V

GS

V

DS

7v

6v

10v

V

e

I

D

V

DS

V

T

V

GS

=0v

V

GS

=<6

v

Plan du cours

Fabrication des circuits

Composants lmentaires associes (diode,

transistor),

Diode

Transistor

Michal Beuve / IPNL/ UCB Lyon1 29

Transistor

Mmoire

Connexion et boitier

Connexion et boitier

Vitesse de fonctionnement, consommation et Vitesse de fonctionnement, consommation et

performances. performances.

1!moire

Mmoire ensemble de mots de N bits

1 bit = Une coordonne

= 1 nligne (mot) + 1 ncolonne (bit du mot)

Ecriture

Michal Beuve / IPNL/ UCB Lyon1 30

Lecture

Slection du mot

1!moire

Dynamic Random Access Memory (DRAM)

+++ Hautes densits

- - - Besoin rafraichissement toutes

les 10-100 ns (fuite du condensateur)

Michal Beuve / IPNL/ UCB Lyon1 31

1!moire

Static random access memory (SRAM)

+++ Pas besoin de rafraichissement

- - - Faibles densits

Michal Beuve / IPNL/ UCB Lyon1 32

Bascules

transistors

MosFet

Plan du cours

Fabrication des circuits

Composants lmentaires associes (diode, transistor),

Diode

Transistor

Mmoire

Connexion et boitier

Michal Beuve / IPNL/ UCB Lyon1 33

Connexion et boitier

Vitesse de fonctionnement, consommation et Vitesse de fonctionnement, consommation et

performances. performances.

Obsolescence programme Obsolescence programme

Lon)ueur des interconne-ions

sur la puce

20 000

25 000

30 000

Michal Beuve / IPNL/ UCB Lyon1 34

0

5 000

10 000

15 000

20 000

1997 1999 2001 2003 2006 2009 2012

anne

l

(

m

t

r

e

s

)

Les principau- effets des interconne-ions

Rebonds

dpassements

Dformation

Michal Beuve / IPNL/ UCB Lyon1 35

A

Retard

dpassements

chos

Attnuation

Les interconne-ions tous les ni$eau-

Michal Beuve / IPNL/ UCB Lyon1 36

Ni$eau 45 sur la puce

Michal Beuve / IPNL/ UCB Lyon1 37

Local : l < 1 mm ; R > 500 /m

Intermed. : 3 4 mm ; R > 100 /m

Global : l < 10 20 mm ; R < 100 /m

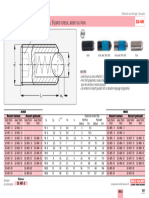

Ni$eau 67 La conne-ion par bondin) filaires

Michal Beuve / IPNL/ UCB Lyon1 38

C.I.

Substrat

C.I.

C.I.

C.I.

Substrat

Ni$eau 6 7 1onta)e de la puce

A

B

C

D

Michal Beuve / IPNL/ UCB Lyon1 39

A

Wire

bonding

B

TAB

D

Bump

Flip chip

C

Direct

L (pH) 1000-3000 500-2000 < 100 < 10

C (fF) "10-50" 20-40 < 10 < 1

R (m )

30-100 13-50 "2-6" <1

Continuit

lectromagntique

NON Faible Bonne Excellente

C.I.

Substrat Substrat

Ni$eau 65 le bo+tier (pac8a)in))

Michal Beuve / IPNL/ UCB Lyon1 40

Ni$eau 659 le 1ulti C0ip 1odule

Michal Beuve / IPNL/ UCB Lyon1 41

1ulti C0ip 1odule

Michal Beuve / IPNL/ UCB Lyon1 42

Le ni$eau 659

200x300 mm 20x30 mm

Michal Beuve / IPNL/ UCB Lyon1 43

11 Multichip Multichip

module module

11 Multichip Multichip

module module

1 Carte 1 Carte 1 Carte 1 Carte

Ni$eau 659

Michal Beuve / IPNL/ UCB Lyon1 44

Ni$eau 659 7 Int!)ration :(

Michal Beuve / IPNL/ UCB Lyon1 45

Plan du cours

Fabrication des circuits

Composants lmentaires associes (diode, transistor),

Diode

Transistor

Mmoire

Connexion et boitier

Michal Beuve / IPNL/ UCB Lyon1 46

Connexion et boitier

Vitesse de fonctionnement, consommation et Vitesse de fonctionnement, consommation et

performances. performances.

Obsolescence programme Obsolescence programme

100

1000

10000

100000

1000000

M

i

l

l

i

o

n

s

d

e

t

r

a

n

s

i

s

t

o

r

s

/

p

u

c

e

Microprocesseurs

Mmoires

La loi de 1oore

Michal Beuve / IPNL/ UCB Lyon1 47

0,001

0,01

0,1

1

10

1965 1970 1975 1980 1985 1990 1995 2000 2005 2010 2015

Anne

M

i

l

l

i

o

n

s

d

e

t

r

a

n

s

i

s

t

o

r

s

/

p

u

c

e

Gnrations technologiques (nm)

250

300

Lignes denses (DRAM half pitch), (nm)

La r!duction des dimensions

Michal Beuve / IPNL/ UCB Lyon1 48

0

50

100

150

200

1997 1999 2001 2003 2006 2009 2012

Lignes isoles (MPU), (nm)

MPU : Micro-Processing Units

1000m3

1m3

DRAM

Tores magntique

1K

La r!duction des dimensions

Michal Beuve / IPNL/ UCB Lyon1 49

1dm3

1cm3

1950

64K

64M

1K

1970

1M

1990

16G

2010

Volume dun Mbit de mmoire

1000

10000

F

r

q

u

e

n

c

e

d

'

h

o

r

l

o

g

e

e

n

M

H

z

P

a

s

m

i

n

i

e

n

n

a

n

o

m

t

r

e

s

Intgration / Vitesse

Michal Beuve / IPNL/ UCB Lyon1 50

10

100

1975 1980 1985 1990 1995 2000 2005 2010 2015

Pas (nm)

Fclock Cost

Fclock Perf

F

r

q

u

e

n

c

e

d

'

h

o

r

l

o

g

e

e

n

M

H

z

P

a

s

m

i

n

i

e

n

n

a

n

o

m

t

r

e

s

Les points cl!s5 "uel"ues !tapes

Anne 1997-2001 2003-2006 2009-2012

Besoins en technologie des

semi-conducteurs

Dimensions (nm) lignes denses 250-150 130-100 70-50

Dimensions (nm) lignes isoles 200-140 120-100 70-35

Millions Transistors/cm

2

4-10 18-39 84-180

Niveaux d'interconnexions 6-7 7-8 8-9

Michal Beuve / IPNL/ UCB Lyon1 51

Niveaux d'interconnexions 6-7 7-8 8-9

Besoins en technologie

d'assemblage et de packaging

Puissance (W) 1,2-61 2-96 2,8-109

Dimension de puce (mm

2

) 50-385 60-520 70-750

Tension (V) 1,2-2,5 0,9-1,5 0,5-0,9

Nombre d'I/O 100-900 160-1475 260-2690

Source S.I.A. roadmap 98

20

25

30

35

40

45

R

e

t

a

r

d

(

p

s

)

Gate

Inter Cu+Low k

Total Cu + low k

Inter Al+SiO

2

Total Al+SiO

2

Al : 3 cm

Low k : k = 2

Cu : 1,7 cm

SiO

2

: k = 4

Ligne : paisseur 0,8 m

longueur 43 m

Les interconne-ions5 le point cl!

Michal Beuve / IPNL/ UCB Lyon1 52

0

5

10

15

20

100 200 300 400 500 600

Gnration (nm)

R

e

t

a

r

d

(

p

s

)

longueur 43 m

0,28m

0,18m

Les interconne-ions5 le point cl!

L longueur de ligne

h hauteur de ligne

w largeur de ligne

s espace entre les

deux lignes

Michal Beuve / IPNL/ UCB Lyon1 53

deux lignes

pitch = w+s

s w

L

RC

.

2

0

=

Les limitations dues au- interconne-ions

1900

2400

2900

F

r

q

u

e

n

c

e

d

'

h

o

r

l

o

g

e

(

M

H

z

)

Cu-Low k

Al-low k

Cu-SiO2

Al-SiO2

Michal Beuve / IPNL/ UCB Lyon1 54

400

900

1400

40 60 80 100 120 140 160 180 200 220 240

Dimensions (nm)

F

r

q

u

e

n

c

e

d

'

h

o

r

l

o

g

e

(

M

H

z

)

Plan du cours

Fabrication des circuits

Composants lmentaires associes (diode, transistor),

Diode

Transistor

Mmoire

Connexion et boitier

Michal Beuve / IPNL/ UCB Lyon1 55

Connexion et boitier

Vitesse de fonctionnement, consommation et Vitesse de fonctionnement, consommation et

performances. performances.

Obsolescence programme Obsolescence programme

&bsolescence pro)ramm!e ;

d!finition

Dure de vie technique

Dure moyenne pendant laquelle un composant, un produit

rpond aux fonctions pour lesquels il a t conu.

Obsolescence programme (ou la dsutude planifie)

Soppose la recherche de stabilit, fiabilit

Vise crer un bien en prvoyant sa date de dsutude.

Vise crer un bien en prvoyant sa date de dsutude.

fabricants conoivent des objets dont la dure de vie

commerciale est dlibrment courte.

Note: dure de vie commerciale pas ncessairement dure de vie

technique

1924 : lampe incandescence classique

Comit Phbus : accord entre les principaux fabricants mondiaux d'ampoules

(OSRAM, Philips) pour rduire la dure de vie des ampoules

R&D : passage de 2500 heures 1000 heures

&bsolescence pro)ramm!e ; t<pes

Dfaut fonctionnel

Optimisation des dures de vie des composants

majeurs

en fonction de la dure de garantie , dure commerciale

Ex: roulement billes, composants lectroniques

Ajouter sciemment des dfauts de conception au

produit vendu produit vendu

Exemple Imprimante:

Mmoire EPROM => comptage du nombre de pages

Si (Nb page> valeur max) blocage de limprimante

Astuce : entretien (nettoyage des rcuprateur dencre) +

logiciel libre pour dbloquer

&bsolescence pro)ramm!e ; t<pes

Obsolescence indirecte

Pices de rechange / dtaches

dlais, plus fabriques, couteuses

Ex: batteries, chargeurs

Produits non dmontables Produits non dmontables

(lments colls ou fondus, vis spciales)

Apple : iPhones/iPods batterie non-changeables par l'utilisateur

Changement dun fusible dans un grille- pain

Support et maintenance

Ex: juillet 2006, Microsoft abandonne le service de support et de

maintenance corrective pour les logiciels Windows 98 et Millenium

&bsolescence pro)ramm!e ; t<pes

Obsolescence indirecte (suite)

Obsolescence par notification

Ex: cartouche dencre

annonce cartouche vide

Dpose/Repose => rgle le problme

Obsolescence par incompatibilits

Logiciels informatiques

Obsolescence esthtique

Fin du modle T de Ford

&bsolescence pro)ramm!e ; informati"ue

Ressources permettant de

dvelopper de nouveau produit soft

Pr-installation de systme

Besoin de

ressources

hard

Software Hardware

&bsolescence pro)ramm!e ; informati"ue

March du micro-processeur

Vrification surprenante de la loi (conjecture) de

Moore

Deux explications possibles

Rythme de progression rgulier (cycles de recherche et

dveloppement, validation des nouveaux processus de

microgravure) pour tous les constructeurs

Stratgie dlibre???

rpartition distille de l'offre.

modle stable de consommation

correspondance contrle entre efforts

d'innovation et renouvellements de la clientle

bnfices

&bsolescence pro)ramm!e ; bilan

+++ Modle conomique permettant de :

dynamiser le march

crer des conditions favorables aux entreprises innovantes.

Anticiper et prvoir l'volution des ventes sur le long terme

rduit les risques conomiques

facilite la planification des investissements industriels. facilite la planification des investissements industriels.

--- Produire des objets rapidement obsoltes

Globalement pas trs efficace

Consommation

temps humain (Manpower)

matire premire

nergie

Production importante de dchets

Vous aimerez peut-être aussi

- CC1 2014PDocument5 pagesCC1 2014PAbdessalem Mohamed AchrafPas encore d'évaluation

- Complement 1Document9 pagesComplement 1Abdessalem Mohamed AchrafPas encore d'évaluation

- Automates PileDocument12 pagesAutomates PileAbdessalem Mohamed AchrafPas encore d'évaluation

- Td7 Pc2i FinalDocument8 pagesTd7 Pc2i FinalAbdessalem Mohamed AchrafPas encore d'évaluation

- Chapitre 5Document7 pagesChapitre 5Abdessalem Mohamed AchrafPas encore d'évaluation

- Chapitre 1Document7 pagesChapitre 1Abdessalem Mohamed AchrafPas encore d'évaluation

- Rappel MathDocument13 pagesRappel MathhassanbfkPas encore d'évaluation

- Chapitre 6Document3 pagesChapitre 6Abdessalem Mohamed AchrafPas encore d'évaluation

- Chapitre 3Document9 pagesChapitre 3Abdessalem Mohamed AchrafPas encore d'évaluation

- Interro 5Document2 pagesInterro 5Abdessalem Mohamed AchrafPas encore d'évaluation

- Chapitre 2Document5 pagesChapitre 2Abdessalem Mohamed AchrafPas encore d'évaluation

- Chapitre 4Document5 pagesChapitre 4Abdessalem Mohamed AchrafPas encore d'évaluation

- Chapitre 7Document9 pagesChapitre 7Abdessalem Mohamed AchrafPas encore d'évaluation

- Chapitre 9Document8 pagesChapitre 9Abdessalem Mohamed AchrafPas encore d'évaluation

- Philo Methode.pDocument2 pagesPhilo Methode.pAbdessalem Mohamed AchrafPas encore d'évaluation

- Corrections Des Exercices SupplémentairesDocument4 pagesCorrections Des Exercices SupplémentairesAbdessalem Mohamed AchrafPas encore d'évaluation

- Le Livre Du C Pour Les Vrais DВbutants en ProgrammationDocument165 pagesLe Livre Du C Pour Les Vrais DВbutants en ProgrammationManuelGonzalezAnidoPas encore d'évaluation

- Philo L'inconscientDocument3 pagesPhilo L'inconscientAbdessalem Mohamed AchrafPas encore d'évaluation

- Complement 2Document8 pagesComplement 2Abdessalem Mohamed AchrafPas encore d'évaluation

- AtomistiqueDocument1 pageAtomistiqueAbdessalem Mohamed AchrafPas encore d'évaluation

- Philo La ConscienceDocument5 pagesPhilo La ConscienceAbdessalem Mohamed AchrafPas encore d'évaluation

- 11 Septembre 1973 ChiliDocument1 page11 Septembre 1973 ChiliAbdessalem Mohamed AchrafPas encore d'évaluation

- Physique - OnDESDocument3 pagesPhysique - OnDESAbdessalem Mohamed AchrafPas encore d'évaluation

- Physique - Ondes Sonores Et UltrasonoresDocument3 pagesPhysique - Ondes Sonores Et UltrasonoresAbdessalem Mohamed AchrafPas encore d'évaluation

- Physique - ONDES PÉRIODIQUESDocument3 pagesPhysique - ONDES PÉRIODIQUESAbdessalem Mohamed AchrafPas encore d'évaluation

- Physique - INTERFÉRENCESDocument4 pagesPhysique - INTERFÉRENCESAbdessalem Mohamed AchrafPas encore d'évaluation

- Physique - ONDES DANS LES MILIEUX MATÉRIELSDocument3 pagesPhysique - ONDES DANS LES MILIEUX MATÉRIELSAbdessalem Mohamed AchrafPas encore d'évaluation

- Auto Betonniere Merlo Gamme DBMDocument16 pagesAuto Betonniere Merlo Gamme DBMfcbarca2020ifyPas encore d'évaluation

- Puissance D-Une Eolienne MOOC UVED PDFDocument13 pagesPuissance D-Une Eolienne MOOC UVED PDFAyoub Django RFPas encore d'évaluation

- Relais Et Fusibles (FR)Document4 pagesRelais Et Fusibles (FR)Toufik BenamrouchePas encore d'évaluation

- Les Familles de REVIT Pour Le BIM 2017Document331 pagesLes Familles de REVIT Pour Le BIM 2017Arnoldas Šneideris100% (13)

- Catalogo MotoresDocument2 pagesCatalogo MotoresJames VeraPas encore d'évaluation

- Générateur Synchrone Standard KATO - FRDocument49 pagesGénérateur Synchrone Standard KATO - FRamekhzoumiPas encore d'évaluation

- Reseau GlobalstarDocument29 pagesReseau GlobalstarSanaa OulaourfPas encore d'évaluation

- MortierDocument19 pagesMortierAnonymous depAph9Pas encore d'évaluation

- Amdec Processus PDFDocument18 pagesAmdec Processus PDFAdil Abdou100% (2)

- Exercice 3Document3 pagesExercice 3Ahmed DjebbiPas encore d'évaluation

- Polycope Outil MathématiqueDocument45 pagesPolycope Outil MathématiqueTaha Can50% (2)

- Calcul TunnelDocument51 pagesCalcul TunnelAbakarTahir100% (3)

- VBA Pour ExcelDocument138 pagesVBA Pour ExcelmmozarttPas encore d'évaluation

- GindroDocument150 pagesGindropascalPas encore d'évaluation

- Gestion de Projet ADocument10 pagesGestion de Projet AinteractifPas encore d'évaluation

- Procedure Analyse Des Risques Liés Au Fonctionnement - CopieDocument7 pagesProcedure Analyse Des Risques Liés Au Fonctionnement - CopieBEN ABBES100% (1)

- Poussoir Ressort Bille 6 Pans Creux Acier Inox 32 40 PDF 32 - 40 Lmod1Document1 pagePoussoir Ressort Bille 6 Pans Creux Acier Inox 32 40 PDF 32 - 40 Lmod1aavartPas encore d'évaluation

- Machine Asynchrone TriphaséeDocument26 pagesMachine Asynchrone TriphaséekeylogPas encore d'évaluation

- TD 18 Corrigé - Loi Entrée-Sortie Par Fermeture GéométriqueDocument4 pagesTD 18 Corrigé - Loi Entrée-Sortie Par Fermeture GéométriqueImen Hammouda100% (2)

- Exercices SoudageDocument4 pagesExercices SoudageserePas encore d'évaluation

- Manuel Onduleur3kWDocument100 pagesManuel Onduleur3kWsmarcos67Pas encore d'évaluation

- Fabrication Mécanique. Cours N° 2Document3 pagesFabrication Mécanique. Cours N° 2James BluntPas encore d'évaluation

- 08.levage Et ManutentionDocument22 pages08.levage Et Manutentionodje jules cesar Anoh100% (1)

- Guide Normes ArrimageDocument76 pagesGuide Normes ArrimageDavid Ortega0% (1)

- Fiche de Poste Ingénieur CivilDocument3 pagesFiche de Poste Ingénieur Civiljuv933Pas encore d'évaluation

- B4 - 0 - Déchargeurs À Benne - FR - 1 PDFDocument158 pagesB4 - 0 - Déchargeurs À Benne - FR - 1 PDFpirjgfeiorPas encore d'évaluation

- Avis Technique - Syst Me Lucem Choc v3Document15 pagesAvis Technique - Syst Me Lucem Choc v3NabilPas encore d'évaluation

- Rapport D Stage Marsa MarocDocument56 pagesRapport D Stage Marsa MarocNidalPas encore d'évaluation

- AM Gestion de Pojet - EMI - Oct 2019Document175 pagesAM Gestion de Pojet - EMI - Oct 2019boofPas encore d'évaluation

- Proforma Projet Htas Cidsa Rivera2Document3 pagesProforma Projet Htas Cidsa Rivera2Ahossan Michel EhoumanPas encore d'évaluation