Académique Documents

Professionnel Documents

Culture Documents

Procesamiento Paralelo

Transféré par

Carlos EQTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Procesamiento Paralelo

Transféré par

Carlos EQDroits d'auteur :

Formats disponibles

1.

- INTRODUCCIN:

La tecnologa detrs del desarrollo de componentes de sistemas computacionales ha

alcanzado su madurez y los desarrollos estn a punto de producirse en la era del

procesamiento en paralelo, lo que significa que la tecnologa de la computacin

paralela necesita avanzar, an cuando no est lo suficientemente madura como para

ser explotado como una tecnologa de disponibilidad masiva.

La razn principal para crear y utilizar computacin paralela es que el paralelismo es

una de las mejores formas de salvar el problema del cuello de botella que significa la

velocidad de un nico procesador.

La razn de ser del procesamiento en paralelo es acelerar la resolucin de un

problema, la aceleracin que puede alcanzarse depende tanto del problema en s

como de la arquitectura de la computadora.

Las aplicaciones que se benefician de una aceleracin ms significativa son aquellas

que describen procesos intrnsicamente paralelos, las simulaciones de modelos

moleculares, climticos o econmicos tienen todas una amplia componente paralela,

como los sistemas que representan. el hardware de la mquina entra en juego ya que

es preciso maximizar la relacin entre el tiempo de clculo til y el perdido en el paso

de mensajes, parmetros que dependen de la capacidad de proceso de las CPUs y de

la velocidad de la red de comunicaciones.

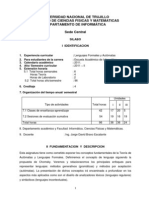

2.- INDICE:

1. Conceptos bsicos

2. Arquitecturas de procesamiento paralelo

2.1 Multiprocesamiento simtrico

2.2 Procesamiento masivamente paralelo

2.3 Procesamiento paralelo escalable

3. Clases de computadoras paralelas

o 3.1 Computacin multincleo

o 3.2 Multiprocesamiento simtrico

o 3.3 Computadoras paralelas especializadas

4. Clster de Computadoras

5. Clasificacin de Flynn

1. CONCEPTOS BSICOS

La idea bsica detrs del procesamiento paralelo es que varios dispositivos

(procesadores), ejecutan-do simultnea y coordinadamente las tareas, pueden rendir

ms que un nico dispositivo. El problema fundamental son las innovaciones

tecnolgicas que se requieren para obtener ese rendimiento mejorado.

Si bien el procesamiento paralelo ofrece una ventaja definitiva en cuanto a costos, su

principal beneficio, la escalabilidad (capacidad de crecimiento), puede ser difcil de

alcanzar. Esto se debe a que conforme se aaden procesadores, las disputas por los

recursos compartidos se intensifican.

2. ARQUITECTURAS DE PROCESAMIENTO PARALELO

Algunas alternativas de arquitecturas de procesamiento paralelo enfrentan este

problema fundamental, con diferentes resultados, entre las que se puede mencionar:

Multiprocesamiento simtrico

Procesamiento masivamente paralelo

Procesamiento paralelo escalable

2.1MULTIPROCESAMIENTO SIMTRICO:

El Multiprocesamiento Simtrico (Symmetric

Multiprocessing / SMP) tiene un diseo

simple, efectivo y econmico. En SMP,

muchos procesadores comparten la misma

memoria RAM y el bus del sistema.

La presencia de un solo espacio de memoria

simplifica tanto el diseo del sistema fsico

(hardware) como la programacin de las

aplicaciones (software). Esa memoria

compartida permite que un Sistema

Operativo con Multiconexin distribuya las

tareas entre varios procesadores, o que una

aplicacin obtenga toda la memoria que

necesita para una simulacin compleja. La

memoria globalmente compartida tambin vuelve fcil la sincronizacin de los datos.

SMP es uno de los diseos de

procesamiento paralelo ms

maduros. Sin embargo, la

memoria global contribuye al

problema ms grande de SMP:

conforme se aaden

procesadores, el trfico en el bus

de memoria se satura. Al aadir

memoria cach a cada procesador

se puede reducir algo del trfico

en el bus.

Al manejarse ocho o ms

procesadores, el cuello de botella

se vuelve crtico, inclusive para los

mejores diseos, por lo que SMP

es considerada una tecnologa

poco escalable.

2.2 PROCESAMIENTO MASIVAMENTE PARALELO:

El Procesamiento Masiva-mente

Paralelo (Massively Parallel

Processing / MPP) es una

arquitectura computacio-nal de

alto rendimiento. Para evitar los

cuellos de botella en el bus de

memoria, MPP no utiliza memoria

compartida; en su lugar, distribuye

equitativamente la memoria RAM

entre los procesadores de modo

que se asemeja a una red (cada

procesador con su memoria

distribuida asociada es similar a

un computador dentro de una red

de procesamiento distribuido).

Para tener acceso a las reas de memoria fuera de su propia RAM (memoria libre no

empleada por los otros procesadores), los procesadores utilizan un esquema de paso

de mensajes anlogo a los paquetes de datos en redes. Este sistema reduce el

trfico del bus, debido a que cada seccin de memoria interacta nicamente con

aquellos accesos que le estn destinados, en lugar de interactuar con todos los

accesos a memoria, como ocurre en un sistema SMP. Esto permite la construccin de

sistemas MPP de gran tamao, con cientos y an miles de procesadores, por lo que

MPP es una tecnologa altamente escalable.

La parte negativa de MPP desde el punto de vista tecnolgico es que la programacin

se vuelve difcil, debido a que la memoria se rompe en pequeos espacios separados.

Sin la existencia de un espacio de memoria globalmente compartido, ejecutar una

aplicacin que requiere una gran cantidad de RAM (comparada con la memoria local),

puede ser difcil. La sincronizacin de datos entre tareas ampliamente distribuidas

tambin se complica, particularmente si un mensaje debe pasar por muchos

componentes de hardware hasta alcanzar la memoria del procesador destino.

Escribir una aplicacin MPP tambin requiere estar al tanto de la organizacin de la

memoria manejada por el programa. Donde sea necesario, se deben insertar

comandos de paso de mensajes dentro del cdigo del programa. Adems de

complicar el diseo del software, tales comandos pueden crear dependencias de

hardware en las aplicaciones (slo funcionara en equipos de cierta marca y modelo).

Sin embargo, la mayor parte de vendedores de computadores han salvaguardado la

portabilidad de las aplicaciones adoptando, sea un mecanismo de dominio pblico

para paso de mensajes conocido como Mquina Virtual Paralela (Parallel Virtual

Machine / PVM), o un estndar llamado Interfaz de Paso de Mensajes (Message

Passing Interface / MPI).

2.3 PROCESAMIENTO PARALELO ESCALABLE:

La tercera arquitectura paralela, el

Procesamiento Paralelo Escalable

(Scalable Parallel Processing / SPP),

es un hbrido de SMP y MPP, que

utiliza una memoria jerrquica de dos

niveles para alcanzar la escalabilidad.

La primera capa consiste de

componentes de memoria distribuida

que son esencialmente parte de

sistemas MPP completos, con

mltiples nodos (nodo = procesador +

memoria distribuida), y el segundo

nivel de memoria est globalmente

compartido al estilo SMP.

Se construyen sistemas SPP grandes

interconectando dos o ms nodos a

travs de la segunda capa de memoria, de modo que esta capa aparece, lgicamente,

como una extensin de la memoria individual de cada nodo.La memoria de dos niveles

reduce el trfico de bus debido a que solamente ocurren actualizaciones para

mantener coherencia de memoria. Por tanto, SPP ofrece la facilidad de programacin

del modelo SMP, a la vez que provee una escalabilidad similar a la de un diseo MPP.

3. CLASES DE COMPUTADORAS PARALELAS

Las computadoras paralelas se pueden clasificar de acuerdo con el nivel en el que el

hardware soporta paralelismo. Esta clasificacin es anloga a la distancia entre los

nodos bsicos de cmputo.

3.1 Computacin multincleo

Un procesador multincleo es un procesador que incluye mltiples unidades

de ejecucin (ncleos) en el mismo chip. Los procesadores superescalares

pueden ejecutar mltiples instrucciones por ciclo de un flujo de instrucciones

(hilo), a diferencia de este, un procesador multincleo puede ejecutar mltiples

instrucciones por ciclo de secuencias de instrucciones mltiples. Cada ncleo

en un procesador multincleo potencialmente puede ser superescalar, es

decir, en cada ciclo, cada ncleo puede ejecutar mltiples instrucciones de un

flujo de instrucciones.

El ''Multithreading'' simultneo de la cual Intel HyperThreading es el ms

conocido era una forma de pseudo-multincleo. Un procesador con

capacidad de multithreading simultneo tiene una sola unidad de ejecucin

(ncleo), pero cuando esa unidad de ejecucin est desocupada por

ejemplo, durante un error de cach, se utiliza para procesar un segundo hilo.

El microprocesador Cell de IBM, diseado para su uso en la

consola Sony PlayStation 3, es otro prominente procesador multincleo.

3.2 Computacin distribuida

La computacin distribuida es la forma ms distribuida de la computacin

paralela. Se hace uso de ordenadores que se comunican a travs de la

Internet para trabajar en un problema dado. Debido al bajo ancho de banda y

la latencia extremadamente alta de Internet, la computacin distribuida

normalmente slo se refiere a problemas vergonzosamente paralelos. Se han

creado muchas aplicaciones de computacin distribuidas.

La mayora de las aplicaciones de computacin distribuida utilizan middleware,

software que se encuentra entre el sistema operativo y la aplicacin para

administrar los recursos de red y estandarizar la interfaz de software. El ms

comn es la Infraestructura Abierta de Berkeley para Computacin en

Red (BOINC). A menudo, los programas de computacin distribuida hacen uso

de ciclos de repuesto, realizando clculos cuando el procesador de un

equipo est desocupado.

3.3 Computadoras paralelas especializadas

Dentro de la computacin paralela, existen dispositivos paralelos

especializados que generan inters. Aunque no son especficos para un

dominio, tienden a ser aplicables slo a unas pocas clases de problemas

paralelos.

4. CLSTER DE COMPUTADORAS

La tecnologa cluster tiene su inicio entre la dcada del 50 y del 60, en plena

revolucin tecnolgica.

El principal fundamento que dio origen a la existencia de los clusters es la Ley de

Amdahl que describe matemticamente cuanto se puede esperar de hacer en paralelo

una serie de tareas mediante una arquitectura que lo permita. Dicha ley es aplicable a

cualquier medio de multiprocesamiento, ya sea

en hardware o entornos de redes.

Un cluster es un grupo de equipos

independientes que ejecutan una serie de

aplicaciones de forma conjunta y aparecen

ante clientes y aplicaciones como un solo

sistema. Los clusters permiten aumentar la

escalabilidad, disponibilidad y fiabilidad de

mltiples niveles de red.

Es decir se usa un clster con varios

computadores para crear un supercomputador.

Los clsters se han desarrollado en varias ramas, como son las aplicaciones para

solucin de alto cmputo, servidores Web y comercio electrnico, as como bases de

datos de alto rendimiento, entre otros usos.

Pero principalmente la existencia de los clster est motivada por la necesidad de

potencia computacional para la solucin de problemas muy complejos.

Una de las herramientas de ms auge en la actualidad son los llamados clster

Beowulf.

5. CLASIFICACIN DE FLYNN

Existen dos clasificaciones de computadores ms conocidas en la actualidad.

La primera clasificacin, es la clasificacin clsica de Flynn en dnde se tienen en

cuenta sistemas con uno o varios procesadores.

La segunda clasificacin es una clasificacin moderna en la que slo tienen en cuenta

los sistemas con ms de un procesador.

Clasificacin clsica de arquitectura de computadores que hace alusin a sistemas

con uno o varios procesadores. Esta clasificacin o taxonoma se basa en el flujo que

siguen los datos dentro de la mquina (flujo secuencial de datos requeridos por el flujo

de instrucciones) y flujo de las instrucciones (conjunto de instrucciones secuenciales

que son ejecutadas por un nico procesador) sobre esos datos. Con estas

consideraciones, Flynn clasifica los sistemas en cuatro categoras:

SISD (Single Instruction stream, Single Data

stream)

Los sistemas de este tipo se caracterizan por

tener un nico flujo de instrucciones sobre un

nico flujo de datos, es decir, se ejecuta una

instruccin detrs de otra. Este es el

concepto de arquitectura serie de Von

Neumann donde, en cualquier momento,

slo se ejecuta una nica instruccin. No

explota el paralelismo en las instrucciones ni

en flujos de datos.

Un ejemplo de estos sistemas son las mquinas secuenciales convencionales.

Instruccin

individual

Instruccin

mltiple

Datos

individuales

SISD MISD

Mltiples datos SIMD MIMD

SIMD (Single Instruction stream, Multiple Data stream)

Estos sistemas tienen un nico flujo de instrucciones que operan sobre mltiples flujos

de datos. Ejemplos de estos sistemas los tenemos en las mquinas vectoriales con

hardware escalar y vectorial.

La ejecucin de las instrucciones sigue siendo secuencial como en el caso anterior,

todos los elementos realizan una misma instruccin pero sobre una gran cantidad de

datos. Por este motivo existir concurrencia de operacin, es decir, esta clasificacin

es el origen de la mquina paralela.

El funcionamiento de este tipo de sistemas es el siguiente. La Unidad de Control

manda una misma instruccin a todas las unidades de proceso (ALUs). Las unidades

de proceso operan sobre datos diferentes pero con la misma instruccin recibida.

Existen dos alternativas distintas que aparecen despus de realizarse esta

clasificacin:

Arquitectura Vectorial con

segmentacin:

Una CPU nica particionada en unidades

funcionales independientes trabajando sobre flujos

de datos concretos. La CPU contiene un nico

procesador con instrucciones que procesa un nico

flujo de estas liberando cada instante una. Debido a

que las unidades funcionales operan

independientemente, es posible liberar nuevas

instrucciones antes de que finalice la ejecucin de

las instrucciones previas.

Arquitectura Matricial (matriz de

procesadores):

Varias ALUs idnticas a las que el procesador de

instrucciones asigna una nica instruccin pero

trabajando sobre diferentes partes del programa.

Existe un nico procesador que maneja el flujo de

instrucciones del programa y que transfiere todas

las instrucciones a las diferentes unidades aritmtico/lgicas.

MISD (Multiple Instruction stream, Single

Data stream)

Sistemas con mltiples instrucciones que operan

sobre un nico flujo de datos. Este tipo de

sistemas no ha tenido implementacin hasta

hace poco tiempo.

Los sistemas MISD se contemplan de dos

maneras distintas:

Varias instrucciones operando

simultneamente sobre un nico dato.

Varias instrucciones operando sobre un dato que se va convirtiendo en un

resultado que ser la entrada para la siguiente etapa. Se trabaja de forma

segmentada, todas las unidades de proceso pueden trabajar de forma concurrente.

Ejemplos de estos tipos de sistemas son los arrays sistlicos o arrays de

procesadores. Tambin podemos encontrar aplicaciones de redes neuronales en

mquinas masivamente paralelas.

MIMD (Multiple Instruction stream, Multiple Data stream)

Sistemas con un flujo de mltiples instrucciones

que operan sobre mltiples datos. Estos

sistemas empezaron a utilizarse a principios de

los 80.

Son sistemas con memoria compartida que

permiten ejecutar varios procesos

simultneamente (sistema multiprocesador).

Cuando las unidades de proceso reciben datos

de una memoria no compartida estos sistemas

reciben el nombre de MULTIPLE SISD (MSISD).

En arquitecturas con varias unidades de control

(MISD Y MIMD), existe otro nivel superior con

una unidad de control que se encarga de

controlar todas las unidades de control del

sistema.

Ejemplo de estos sistemas son las mquinas paralelas actuales.

BIBLIOGRAFA:

http://es.wikipedia.org/wiki/Computaci%C3%B3n_paralela

http://sistemas-distribuidos.wikispaces.com/1.+Introducci-rocesamiento+en+paralelo

http://www.sites.upiicsa.ipn.mx/polilibros/portal/Polilibros/P_terminados/Polilibrupcp-

procesamient.paralelo

http://rua.ua.es/dspace/bitstream/10045/10020/4/ZamoraParallelprocessing

Vous aimerez peut-être aussi

- Arquitecturas MPP & SMPDocument7 pagesArquitecturas MPP & SMPMagaly CedroPas encore d'évaluation

- Sistemas de multiprocesamiento y procesamiento paraleloDocument9 pagesSistemas de multiprocesamiento y procesamiento paraleloElmerCuencaBalabarca0% (1)

- MPP y SMPDocument5 pagesMPP y SMPEfra26100% (1)

- Arquitectura SMP, MPP, SPPDocument4 pagesArquitectura SMP, MPP, SPPZuzan PeñaPas encore d'évaluation

- Arquitectura SMP MPPDocument4 pagesArquitectura SMP MPPAlfredo MontoyaPas encore d'évaluation

- Multiprocesamiento Paralelo 3 - 3parte 1PDocument6 pagesMultiprocesamiento Paralelo 3 - 3parte 1PTomiko FelizPas encore d'évaluation

- Arquitectura SMP y MPPDocument4 pagesArquitectura SMP y MPPManuel71110Pas encore d'évaluation

- Procesamiento ParaleloDocument35 pagesProcesamiento ParaleloJEFFERSON MUÑOZ PARDOPas encore d'évaluation

- Memoria CompartidaDocument5 pagesMemoria CompartidaRolando HuayllaniPas encore d'évaluation

- SMP Arquitectura Multiprocesamiento SimétricoDocument4 pagesSMP Arquitectura Multiprocesamiento Simétricotoxic_gabriel1207Pas encore d'évaluation

- La Arquitectura SMPDocument4 pagesLa Arquitectura SMPliracruzgustavoPas encore d'évaluation

- MPPDocument1 pageMPPchicharo09Pas encore d'évaluation

- Definicion de NUMA y OtrosDocument41 pagesDefinicion de NUMA y OtrosRamón Moreno MalavéPas encore d'évaluation

- Procesamiento ParaleloDocument6 pagesProcesamiento ParaleloResendiz AguilaPas encore d'évaluation

- Programacion en ParaleloDocument6 pagesProgramacion en ParaleloJoshep DPas encore d'évaluation

- Arquitectura ParalelaDocument37 pagesArquitectura ParalelaHitsuji KuroiPas encore d'évaluation

- MultiprocesadoresDocument7 pagesMultiprocesadoresmorris starPas encore d'évaluation

- Procesos Concurrentes - Sistemas OperativosDocument10 pagesProcesos Concurrentes - Sistemas OperativosMICHAELPas encore d'évaluation

- Multi Pro Ces AdoresDocument5 pagesMulti Pro Ces AdoreslalometallicaPas encore d'évaluation

- 4.5 Casos de EstudioDocument5 pages4.5 Casos de EstudioSilvio Dresser0% (1)

- Arquitectura SMPDocument2 pagesArquitectura SMPAldo Buchon GarciaPas encore d'évaluation

- UNIPROCESADORES y MultiprocesadoresDocument21 pagesUNIPROCESADORES y MultiprocesadoresLuis Soriano OsoresPas encore d'évaluation

- Actividad 1.1.1Document14 pagesActividad 1.1.1luisPas encore d'évaluation

- Procesamiento paralelo MIMD: Multiprocesadores y MulticomputadorasDocument11 pagesProcesamiento paralelo MIMD: Multiprocesadores y MulticomputadorasdysanPas encore d'évaluation

- Sistemas MIMD y formas de acoplamiento multiprocesadoresDocument8 pagesSistemas MIMD y formas de acoplamiento multiprocesadoresHernan CastroPas encore d'évaluation

- Configuraciones de MCDDocument12 pagesConfiguraciones de MCDSergio RiveraPas encore d'évaluation

- Tipos de Arquitectura Del Procesador 1 Marzo 2021Document24 pagesTipos de Arquitectura Del Procesador 1 Marzo 2021Jose Luis ZabaletaPas encore d'évaluation

- Arquitectura MPPDocument2 pagesArquitectura MPPBereb RosqueroPas encore d'évaluation

- MultiprocesadorDocument19 pagesMultiprocesadorCHINO JIMENEZPas encore d'évaluation

- Aspectos Basicos de La Computacion Paralela y DistribuidaDocument10 pagesAspectos Basicos de La Computacion Paralela y Distribuidaluis hernandez100% (1)

- Arquitectura de ComputadorasDocument8 pagesArquitectura de ComputadorasSorel TorresPas encore d'évaluation

- 00881-Tema 3.3 Multiples ProcesadoresDocument45 pages00881-Tema 3.3 Multiples ProcesadoresAbraham SanchezPas encore d'évaluation

- Multiprocesadores SimétricosDocument9 pagesMultiprocesadores SimétricosRobin PereiraPas encore d'évaluation

- MemoriaDocument5 pagesMemoriaMaryi Becerra TorresPas encore d'évaluation

- Memoria Compartida DistribuidaDocument11 pagesMemoria Compartida DistribuidaRoger VaaPas encore d'évaluation

- Arquitecturas y Procesamiento ParaleloDocument17 pagesArquitecturas y Procesamiento ParaleloRaul L. Zamorano FerrerPas encore d'évaluation

- Arquitectura MIMDDocument6 pagesArquitectura MIMDpdelacruzrPas encore d'évaluation

- 53 Unidad6 Coherencia de CacheDocument12 pages53 Unidad6 Coherencia de CacheDoracelia Gazga LovePas encore d'évaluation

- Como Funciona El Procesamiento en ParaleloDocument4 pagesComo Funciona El Procesamiento en ParaleloFrancesco RuggieroPas encore d'évaluation

- SMP (Symmetric Multi-Processing Ó Multiproceso Simétrico)Document2 pagesSMP (Symmetric Multi-Processing Ó Multiproceso Simétrico)Markos MartinPas encore d'évaluation

- Arquitecturas Paralelas Existentes en El MercadoDocument4 pagesArquitecturas Paralelas Existentes en El MercadoEmma Collin100% (1)

- Procesamiento ParaleloDocument23 pagesProcesamiento ParaleloAlejandro Pérez García0% (1)

- Actividad 3 - Procesos y ProcesamientoDocument9 pagesActividad 3 - Procesos y ProcesamientoErik Ramírez MonteroPas encore d'évaluation

- Guía de Estudio - Arquitectura de Las ComputadorasDocument8 pagesGuía de Estudio - Arquitectura de Las ComputadorasSHAINA ALEXANDRA XOCHITIOTZI ROJASPas encore d'évaluation

- Trabajo de Investigación Unidad 4 Arquitectura Del ComputadorDocument6 pagesTrabajo de Investigación Unidad 4 Arquitectura Del ComputadorFrandersson BarretoPas encore d'évaluation

- Computación ParalelaDocument7 pagesComputación ParalelaLuis HermenegildoPas encore d'évaluation

- Sistemas de Memoria Compartida DistribuidaDocument15 pagesSistemas de Memoria Compartida DistribuidaJuan Carlos Gonzalez GutierrezPas encore d'évaluation

- Arquitectura MultiprocesamientoDocument10 pagesArquitectura MultiprocesamientoWiler Falcon CarbajalPas encore d'évaluation

- La Arquitectura SMPDocument5 pagesLa Arquitectura SMPKevin Hernandez RamosPas encore d'évaluation

- Arquitecturas Cisc, Risc o en ParaleloDocument12 pagesArquitecturas Cisc, Risc o en ParaleloArmand DarkPas encore d'évaluation

- MultiprocesamientoDocument5 pagesMultiprocesamientoEberth A. LeónPas encore d'évaluation

- Tendencias de Los Sistemas Operativos DistribuidosDocument7 pagesTendencias de Los Sistemas Operativos Distribuidosbaghead8Pas encore d'évaluation

- Modelos de Máquinas ParalelasDocument7 pagesModelos de Máquinas ParalelasPablo JonasPas encore d'évaluation

- MultiprocesadoresDocument17 pagesMultiprocesadoresmorris starPas encore d'évaluation

- Resumen MultiprocesadoresDocument6 pagesResumen MultiprocesadoresYohan MorelPas encore d'évaluation

- 03306-Tema 4. Organización ParalelaDocument8 pages03306-Tema 4. Organización Paralelapapatv100% (1)

- Unidad 4 Arqui de ComputadorasDocument11 pagesUnidad 4 Arqui de ComputadorasIrving CobainPas encore d'évaluation

- Sistemas MultiprocesamientoDocument9 pagesSistemas MultiprocesamientolalometallicaPas encore d'évaluation

- Programación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeD'EverandProgramación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubePas encore d'évaluation

- UF0852 - Instalación y actualización de sistemas operativosD'EverandUF0852 - Instalación y actualización de sistemas operativosÉvaluation : 5 sur 5 étoiles5/5 (1)

- Programacion AsincronaDocument53 pagesProgramacion AsincronaCarlos EQPas encore d'évaluation

- Rúbrica T3 APLICAC Videojuegos Aplicaciones Móviles 2016 2Document10 pagesRúbrica T3 APLICAC Videojuegos Aplicaciones Móviles 2016 2Carlos EQPas encore d'évaluation

- Sesion 4-Geometría ComputacionalDocument9 pagesSesion 4-Geometría ComputacionalCarlos EQPas encore d'évaluation

- Bicicle TaDocument5 pagesBicicle TaCarlos EQPas encore d'évaluation

- Silabo 2014-I Informatica ADocument6 pagesSilabo 2014-I Informatica ACarlos EQPas encore d'évaluation

- Geometría Computacional-Sesion 2Document8 pagesGeometría Computacional-Sesion 2Carlos EQPas encore d'évaluation

- Lab 2 Especif Formal 2015 IiDocument3 pagesLab 2 Especif Formal 2015 IiCarlos EQPas encore d'évaluation

- Resume NDocument1 pageResume NCarlos EQPas encore d'évaluation

- Estado de Un Proceso01Document5 pagesEstado de Un Proceso01Carlos EQPas encore d'évaluation

- BdinfoalumDocument1 pageBdinfoalumCarlos EQPas encore d'évaluation

- Spring Framework - ArquitectureDocument2 pagesSpring Framework - ArquitectureCarlos EQPas encore d'évaluation

- Todo Excepto 4.1 y 4.2 S.ODocument24 pagesTodo Excepto 4.1 y 4.2 S.OCarlos EQPas encore d'évaluation

- Transform AdoresDocument4 pagesTransform AdoresgonzalochecalimaPas encore d'évaluation

- Configuración de Apache, PHP y MySQL para desarrollo localDocument114 pagesConfiguración de Apache, PHP y MySQL para desarrollo localJesus BolivarPas encore d'évaluation

- Carga Por Aula.Document9 pagesCarga Por Aula.Carlos EQPas encore d'évaluation

- 4lenguajes FormalesDocument6 pages4lenguajes FormalesKeven S. AltamiranoPas encore d'évaluation

- Silabo 2014-I Informatica ADocument6 pagesSilabo 2014-I Informatica ACarlos EQPas encore d'évaluation

- AnexoDocument1 pageAnexoAnonymous Z0enekPas encore d'évaluation

- 4modelos de Lenguajes de ProgramacionDocument6 pages4modelos de Lenguajes de ProgramacionCarlos EQPas encore d'évaluation

- Oracle Clase 1Document4 pagesOracle Clase 1Carlos EQPas encore d'évaluation

- Practicas TransformadoresDocument12 pagesPracticas TransformadoresJulio Pino MirandaPas encore d'évaluation

- Tru Ji 080215Document103 pagesTru Ji 080215Instituto de Investigación Académica: PraxisPas encore d'évaluation

- Sistemas InformaticosDocument3 pagesSistemas InformaticosCarlos EQPas encore d'évaluation

- Informatica y SociedadDocument5 pagesInformatica y SociedadCarlos EQPas encore d'évaluation

- Npros La Escuela DelDocument7 pagesNpros La Escuela DelCarlos EQPas encore d'évaluation

- Computacion GraficaDocument9 pagesComputacion GraficaCarlos EQPas encore d'évaluation

- Ex EmploDocument5 pagesEx EmploCarlos EQPas encore d'évaluation

- IntroducciónDocument6 pagesIntroducciónAarón Jesús RamosPas encore d'évaluation

- Organizacion de ArchivosDocument5 pagesOrganizacion de ArchivosCarlos EQPas encore d'évaluation

- IntroducciónDocument6 pagesIntroducciónAarón Jesús RamosPas encore d'évaluation

- Sistemas Operativos.Document6 pagesSistemas Operativos.Gabrielito AlejandroPas encore d'évaluation

- Qué son las siglas BIOS y otros conceptos básicos de computaciónDocument8 pagesQué son las siglas BIOS y otros conceptos básicos de computaciónAdministrador Leonardo GarciaPas encore d'évaluation

- Historia de Las Computadoras Trabajo PracticoDocument21 pagesHistoria de Las Computadoras Trabajo PracticoorianaantonelaPas encore d'évaluation

- Alfabetización Tecnológica VenezuelaDocument14 pagesAlfabetización Tecnológica VenezuelaAyoleida Lopez100% (2)

- 2.laboratorio John TejadaDocument20 pages2.laboratorio John TejadaJhonatan MartinezPas encore d'évaluation

- Sistemas Operativos - Introducción - UNSaDocument41 pagesSistemas Operativos - Introducción - UNSaOscar VargasPas encore d'évaluation

- Los Lenguajes de Programacion.Document8 pagesLos Lenguajes de Programacion.Alicia GarciaPas encore d'évaluation

- Unidad 1 - HardwareDocument9 pagesUnidad 1 - HardwareperuggininaiaraPas encore d'évaluation

- Programacion Con ScratchDocument216 pagesProgramacion Con ScratchVictor C. Ccari100% (1)

- Marketing para la inserción laboralDocument5 pagesMarketing para la inserción laboralJaimito Valdivia M'Pas encore d'évaluation

- La Programación en La Ingenieria CivilDocument18 pagesLa Programación en La Ingenieria CivilJose Armando Bautista AntonioPas encore d'évaluation

- Metrología - El Osciloscopio y Generador de FuncionesDocument12 pagesMetrología - El Osciloscopio y Generador de FuncionesPascual Vargas VelasquezPas encore d'évaluation

- FACTUSOL Primeros Pasos 2017Document17 pagesFACTUSOL Primeros Pasos 2017Jose Luis Garcia LopezPas encore d'évaluation

- IPN-ESIME Culhuacán Circuitos Digitales Comparador lógicoDocument8 pagesIPN-ESIME Culhuacán Circuitos Digitales Comparador lógicoAldo David Bonilla SanchezPas encore d'évaluation

- EstilosDocument4 pagesEstilosGonzalo GVPas encore d'évaluation

- Partes de la computadora y su historiaDocument28 pagesPartes de la computadora y su historiaGaby GonzalezPas encore d'évaluation

- SurvCE 1 62 Manual SpanishDocument267 pagesSurvCE 1 62 Manual SpanishCarlos Jhimmi Anze BenitesPas encore d'évaluation

- Sistemas Operativos Por LotesDocument9 pagesSistemas Operativos Por LotesMaicol RaizorPas encore d'évaluation

- QUE ES EL CNC Manual Contruccion CaseraDocument24 pagesQUE ES EL CNC Manual Contruccion CaseraAlex MartinezPas encore d'évaluation

- Proceso de Carga en La Memoria RAMDocument4 pagesProceso de Carga en La Memoria RAMJezuzz Araujoxx ヅPas encore d'évaluation

- ProyectoDocument21 pagesProyectoBrenick RamosPas encore d'évaluation

- Tabla de Las Generaciones de La Educación A Distancia. InstrucciónDocument5 pagesTabla de Las Generaciones de La Educación A Distancia. Instrucciónclaudia veraPas encore d'évaluation

- Capitulo-1.Ingeniería de Software Un Enfoque Desde La Guía SwebokDocument29 pagesCapitulo-1.Ingeniería de Software Un Enfoque Desde La Guía SwebokEver Alfonzo FrancoPas encore d'évaluation

- Estructuras de Datos Con C - TenenbaumLangsamAugensteinDocument240 pagesEstructuras de Datos Con C - TenenbaumLangsamAugensteinDaniel LezcanoPas encore d'évaluation

- Computación e InformáticaDocument17 pagesComputación e InformáticaJulio Cesar KiraPas encore d'évaluation

- Generaciones Del SoftwareDocument9 pagesGeneraciones Del SoftwareAlben Baphomet Pirobus0% (1)

- 1.1. Competencias DigitalesDocument25 pages1.1. Competencias Digitalesedson marin chamanPas encore d'évaluation

- Sistema de Comunicación y Sensorial de Un RobotDocument19 pagesSistema de Comunicación y Sensorial de Un Roboteverret08100% (1)

- 4.2.3.normatividad de SeguridadDocument4 pages4.2.3.normatividad de SeguridadJoshua Velasquez VelasquezPas encore d'évaluation

- Control y Monitoreo de Sesiones de Internet Mediante Un Servidor SQUID en LinuxDocument72 pagesControl y Monitoreo de Sesiones de Internet Mediante Un Servidor SQUID en LinuxINGSAMC7Pas encore d'évaluation