Académique Documents

Professionnel Documents

Culture Documents

UApCircuitos logicosJUN2011

Transféré par

Jonathan NavaTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

UApCircuitos logicosJUN2011

Transféré par

Jonathan NavaDroits d'auteur :

Formats disponibles

INSTITUTO POLITCNICO NACIONAL

SECRETARA ACADMICA

DIRECCIN DE EDUCACIN SUPERIOR

PROGRAMA SINTTICO

UNIDAD ACADMICA:

UNIDAD PROFESIONAL INTERDISCIPLINARIA EN INGENIERA Y TECNOLOGAS

AVANZADAS

PROGRAMA Ingeniera Mecatrnica

ACADMICO:

UNIDAD DE APRENDIZAJE:

Circuitos Lgicos

NIVEL:

II

PROPSITO DE LA UNIDAD DE APRENDIZAJE:

Implementa control digital mediante dispositivos lgicos programables y lenguaje descriptivo de hardware.

CONTENIDOS:

I. Introduccin a los sistemas digitales.

II. Fundamentos del HDL.

III. Diseo y ensamble de circuitos lgicos combinacionales.

IV. Diseo y ensamble de circuitos lgicos secuenciales.

V. Diseo y ensamble de mquinas de estado finito.

ORIENTACIN DIDCTICA:

Se utilizar la estrategia de Aprendizaje Orientado a Proyectos (POL) en el que se desarrollan proyectos que dan soluciones a los

problemas planteados y desarrollan en los estudiantes la capacidad de defender sus ideas tanto de forma escrita como expositiva. Se

fomentar el trabajo colaborativo para compartir diversas soluciones a un mismo problema, lo que contribuye al trabajo colectivo y

lectura de cdigos. Se realizarn prcticas de laboratorio y dinmicas de diseo y ensamble, que integra el conocimiento terico con lo

prctico y contribuye con la escritura de reportes y exposiciones orales. Se aplicarn tcnicas de aprendizaje individual con la

resolucin de problemas y bsqueda de informacin, y como actividad adicional, al final de la unidad de aprendizaje los alumnos

realizarn autoevaluaciones y coevaluaciones.

EVALUACIN Y ACREDITACIN:

Para acreditar la unidad de aprendizaje por competencia, con la autorizacin de la Academia de Electrnica se consideran los

siguientes puntos:

Realizar una evaluacin oral sumativa de las unidades temticas I a V.

Mostrar funcionando y reportar (cdigos y simulacin) las prcticas de laboratorio 5, 10 y 13.

Realizar un proyecto dado por la Academia de Electrnica.

Para la evaluacin de la unidad de aprendizaje si se cursa, se considera:

Evaluacin formativa y evaluacin sumativa de los conceptos vistos en clase y en laboratorio, a travs de:

Prcticas de laboratorio funcionando.

Proyecto solo o en conjunto con otra(s) UAp (a consideracin del profesor) con prototipo funcionando.

Problemas, tareas y dinmicas de grupo, solucionados correctamente.

Evaluacin escrita.

Llevando como sustento los reportes escritos, y el prototipo o circuito funcionando para defenderlo de forma oral. Adems se utilizarn

rubricas de autoevaluacin y coevaluacin.

Para acreditar la unidad de aprendizaje en examen extraordinario o a titulo de suficiencia ETS:

Presentar funcionando dos tareas prcticas dadas por el profesor y reportar de forma escrita (cdigos y simulacin), siendo

requisito aprobarlas para presentar la evaluacin escrita.

Realizar una evaluacin escrita de las unidades temticas I a V.

La Subdireccin Acadmica en conjunto con la academia de Electrnica determinar la equivalencia de la competencia con otras

unidades de aprendizaje, tanto de unidades acadmicas del IPN as como externas.

BIBLIOGRAFA:

1.

2.

3.

4.

Brown S., Vranesic Z. (2008), Fundamentals of Digital Logic with VHDL Design with CD-ROM (3a edicin), USA: Mcgraw Hill,

ISBN: 9780077221430.

Morris Mano M. (2007), Digital design, (4 edicin), USA: Pearson Prentice Hall, ISBN: 9780131989245.

Pardo F., Boluda J. A. (2004), VHDL, lenguajes para sntesis y modelado de circuitos (2 edicin), Mxico: Alfaomega Ra Ma,

ISBN 970-15-1017-8. Este es un libro clsico.

Prez S. A, Soto E., Fernndez S. (2002), Diseo de Sistemas Digitales con VHDL, Espaa: Ed. Thomson, ISBN 84-9732-081-6.

INSTITUTO POLITCNICO NACIONAL

SECRETARA ACADMICA

DIRECCIN DE EDUCACIN SUPERIOR

5.

Wakerly John F. (2007), Digital design: principles and practices (4 edicin), USA: Pearson Prentice Hall, ISBN: 9780132016117.

UNIDAD ACADMICA: Unidad Profesional

Interdisciplinaria en Ingeniera y Tecnologas

Avanzadas.

UNIDAD DE APRENDIZAJE: Circuitos Lgicos.

TIPO DE UNIDAD DE APRENDIZAJE: Terico prctica.

Obligatoria.

PROGRAMA ACADMICO: Ingeniera Mecatrnica

VIGENCIA: Agosto 2009.

SALIDA LATERAL: En Automatizacin.

NIVEL: II.

REA DE FORMACIN: Profesional.

CRDITOS: 6.0 (TEPIC), 4.52 (SATCA).

MODALIDAD: Presencial.

INTENCIN EDUCATIVA

Aplicar los dispositivos lgicos programables (FPGA o CPLD) y Lenguaje Descriptivo de Hardware (HDL),

en la solucin de problemas reales de ingeniera mecatrnica. Durante las actividades de aprendizaje se

fomenta el trabajo colaborativo, la creatividad, la diversidad de roles, el respeto y tolerancia hacia sus

compaeros. Esta UAp se relaciona con: fundamentos de electrnica, sensores y acondicionadores de

seal, simulacin electrnica y diseo de circuitos impresos, dispositivos lgicos programables,

microprocesadores, microcontroladores e interfaz y procesador digital de seales.

PROPSITO DE LA UNIDAD DE APRENDIZAJE

Implementa control digital mediante dispositivos lgicos programables y lenguaje descriptivo de hardware.

TIEMPOS ASIGNADOS

HORAS TEORA/SEMANA: 1.5

HORAS PRCTICA/SEMANA:3.0

HORAS TEORA/SEMESTRE:27

UNIDAD

DE

APRENDIZAJE

REDISEADA

POR: Academia de Electrnica.

REVISADA POR: Subdireccin Acadmica

AUTORIZADO POR: Comisin

de Programas Acadmicos del

Consejo General Consultivo del

IPN.

APROBADA POR:

Consejo Tcnico Consultivo Escolar.

HORAS PRCTICA/SEMESTRE:54

HORAS TOTALES/SEMESTRE:81

M. en C. Arod R. Carvallo Domnguez

Sello de la UA

Ing. Rodrigo de Jess Serrano

Domnguez

Secretario Tcnico de la

Comisin de Programas

Acadmicos

INSTITUTO POLITCNICO NACIONAL

SECRETARA ACADMICA

DIRECCIN DE EDUCACIN SUPERIOR

UNIDAD DE APRENDIZAJE:

Circuitos Lgicos.

N UNIDAD TEMTICA: I

HOJA:

DE

11

NOMBRE: Introduccin a los Sistemas Digitales

UNIDAD DE COMPETENCIA

Disea circuitos combinacionales de bajo nivel de integracin mediante el lgebra de Boole.

No.

CONTENIDOS

HORAS AD

Actividades

de docencia

T

1.1

1.1.1

Introduccin a los sistemas digitales.

Elementos y descripcin de un sistema digital.

Sistemas numricos y cdigos (BCD, GRAY,

ASCII).

1.0

1.2

1.2.1

Compuertas bsicas.

And, or, nand, nor, not, xor, xnor, buffer, triestado.

Implementacin de compuertas bsicas con

elementos discretos y prctica guiada de

compuertas con HDL.

1.0

1.3

1.3.1

1.3.2

1.3.3

lgebra de Boole y funciones booleanas.

Operadores lgicos.

Teoremas y postulados.

Suma de productos (mintrminos) y producto de

sumas (maxtrminos).

2.0

1.1.2

HORAS TAA

Actividades de

Aprendizaje

Autnomo

T

0.5

1.5

0.5

CLAVE

BIBLIOGRFICA

2B, 4C, 5B

1.5

1.0

4.0

1.5

Subtotales:

ESTRATEGIAS DE APRENDIZAJE

2.0

1.5

Se utiliza la estrategia de POL.

Presentacin del encuadre del curso, formacin de equipos de trabajo, socializacin con el grupo.

Indagacin de los temas solicitados de los sistemas digitales, y realizar dinmicas de diseo y ensamble.

Discusin y conclusin en forma grupal de los conceptos vistos en la unidad temtica.

Desarrollo de una prctica guiada utilizando elementos discretos.

Definicin del proyecto a consideracin del profesor (solo o en conjunto con otra(s) UAp).

Resolucin de ejercicios prcticos de sistemas numricos, cdigos, compuertas, funciones booleanas, por medio del

trabajo colaborativo y dinmicas dentro y fuera del aula.

EVALUACIN DE LOS APRENDIZAJES

Examen Diagnstico

Portafolio de evidencias:

Tareas de investigacin y dinmicas de grupo

Prctica de laboratorio introductoria a los sistemas digitales

Evaluacin escrita de la introduccin de los sistemas digitales

Avance del proyecto

Autoevaluacin (Rbrica) y Coevaluacin (Rbrica)

25%

25%

25%

25%

INSTITUTO POLITCNICO NACIONAL

SECRETARA ACADMICA

DIRECCIN DE EDUCACIN SUPERIOR

UNIDAD DE APRENDIZAJE:

Circuitos Lgicos.

HOJA:

N UNIDAD TEMTICA: II

DE

11

NOMBRE: Fundamentos del HDL

UNIDAD DE COMPETENCIA ESPECFICA

Desarrolla programas mediante un lenguaje descriptivo de hardware HDL (VHDL y/o Verilog) en un ambiente de

desarrollo.

No.

CONTENIDOS

HORAS AD

Actividades

de docencia

T

HORAS TAA

Actividades de

Aprendizaje

Autnomo

T

2.1

2.1.1.

Dispositivos programables.

Generalidades de GAL, CPLD, FPGA.

1.0

0.5

2.2.

2.2.1

2.2.2

2.2.3.

Introduccin al HDL.

VHDL: Palabras reservadas, entidad y arquitectura.

Verilog: Palabras reservadas, mdulos.

Descripcin funcional, flujo de datos y estructural

en VHDL y en Verilog.

2.0

1.0

2.3

Ambientes de desarrollo (software y hardware) y

los simuladores.

1.5

3.0

1.5

Subtotales:

ESTRATEGIAS DE APRENDIZAJE

CLAVE

BIBLIOGRFICA

P

1C, 6B, 7C

3.0

1.5

3.0

Se utiliza la estrategia de POL.

Indagacin de los temas solicitados de los fundamentos de HDL, y realizar dinmicas de diseo y ensamble.

Discusin y conclusin en forma grupal de los conceptos vistos en la unidad temtica.

Desarroll de prcticas utilizando una tarjeta de desarrollo con FPGA o CPLD.

Desarrollo del proyecto solo o en conjunto con otra(s) UAp (a consideracin del profesor) de la unidad de aprendizaje.

Resolucin de ejercicios prcticos de sistemas numricos, cdigos, compuertas, funciones booleanas, utilizando HDL

(VHDL y/o Verilog), por medio del trabajo colaborativo y dinmicas dentro y fuera del aula.

EVALUACIN DE LOS APRENDIZAJES

Portafolio de evidencias:

Tareas de investigacin y dinmicas de grupo

Prctica de laboratorio del ambiente de desarrollo

Evaluacin escrita de los fundamentos de HDL

Avance del proyecto

Autoevaluacin (Rbrica) y Coevaluacin (Rbrica)

25%

25%

25%

25%

INSTITUTO POLITCNICO NACIONAL

SECRETARA ACADMICA

DIRECCIN DE EDUCACIN SUPERIOR

UNIDAD DE APRENDIZAJE:

N UNIDAD TEMTICA: III

Circuitos Lgicos

HOJA:

DE

11

NOMBRE: Diseo y ensamble de circuitos lgicos

combinacionales.

UNIDAD DE COMPETENCIA ESPECFICA

Desarrolla etapas de control digital y automatizacin con base en los circuitos combinacionales en los FPGA o CPLD y

el lenguaje descriptivo de hardware HDL (VHDL y/o Verilog).

No.

CONTENIDOS

HORAS AD

Actividades

de docencia

T

3.1

Minimizacin de funciones Booleanas empleando

mapas de Karnaugh de 3, 4 y 5 variables.

1.0

3.2

Riesgos estticos y dinmicos.

0.5

3.3

Diseo, ensamble y simulacin de circuitos

combinacionales con HDL.

Codificadores,

decodificadores,

multiplexores,

demultiplexores, circuitos aritmticos (sumador,

restador, multiplicador y divisor), comparador de

magnitud de n bits, ALU.

3.0

3.0

Desarrollo de etapas de control digital y

automatizacin con circuitos combinacionales para

su

aplicacin

en

sistemas

mecatrnicos.

Simulacin y sntesis en FPGA y CPLD.

1.5

1.5

3.3.1

3.4

HORAS TAA

Actividades de

Aprendizaje

Autnomo

T

0.5

6.0

4.5

Subtotales:

ESTRATEGIAS DE APRENDIZAJE

1.5

CLAVE

BIBLIOGRFICA

8B, 9B, 10B

7.5

4.5

2.0

12.0

Se utiliza la estrategia de POL.

Indagacin de los temas solicitados de los circuitos combinacionales, y realizar dinmicas de diseo y ensamble.

Discusin y conclusin en forma grupal de los conceptos vistos en la unidad temtica.

Desarroll de prcticas utilizando una tarjeta de desarrollo con FPGA o CPLD y componentes discretos.

Desarrollo del proyecto solo o en conjunto con otra(s) UAp (a consideracin del profesor) de la unidad de aprendizaje.

Resolucin de ejercicios prcticos de mtodos de minimizacin, sistemas combinacionales (comparadores, ALU, etc.)

utilizando HDL (VHDL y/o Verilog), por medio del trabajo colaborativo y dinmicas dentro y fuera del aula.

EVALUACIN DE LOS APRENDIZAJES

Portafolio de evidencias:

Tareas de investigacin y dinmicas de grupo

Prctica de laboratorio de circuitos combinacionales

Evaluacin escrita de circuitos combinacionales

Avance del proyecto

Autoevaluacin (Rbrica) y Coevaluacin (Rbrica)

25%

25%

25%

25%

INSTITUTO POLITCNICO NACIONAL

SECRETARA ACADMICA

DIRECCIN DE EDUCACIN SUPERIOR

UNIDAD DE APRENDIZAJE:

Circuitos Lgicos.

N UNIDAD TEMTICA: IV

HOJA:

DE

11

NOMBRE: Diseo y ensamble de circuitos lgicos secuenciales.

UNIDAD DE COMPETENCIA ESPECFICA

Desarrolla etapas de control digital y automatizacin con base a los circuitos lgicos secuenciales en los FPGA o

CPLD y el HDL (VHDL y/o Verilog).

HORAS TAA

HORAS AD

Actividades de

Actividades

CLAVE

Aprendizaje

No.

CONTENIDOS

de docencia

BIBLIOGRFICA

Autnomo

T

Elementos de los circuitos secuenciales.

Conceptos de mquinas secuenciales.

Circuitos de temporizacin (Oscilador a cristal y

circuitos integrados).

Funcionamiento y caractersticas del Latch y Flip

flops (SR, JK, T, D).

Implementacin y simulacin de latchs, flipflops y

registros con HDL.

2.5

0.5

0.5

2.5

4.2

Diseo, ensamble y simulacin de una memoria

RAM y una ROM con HDL.

1.0

0.5

1.0

4.3

Diseo, ensamble y simulacin de contadores:

sncrono y asncrono, de anillo, Johnson,

ascendente-descendente, de inicio programado,

mdulo fijo y variable).

1.0

2.0

1.0

4.4

Diseo, ensamble y simulacin de registros de

corrimiento (PIPO, SISO, SIPO, PISO y Universal)

incluyendo desplazamiento y rotacin con HDL.

1.0

0.5

1.0

4.5

Desarrollo de etapas de control digital y

automatizacin para su aplicacin en sistemas

mecatrnicos. Simulacin y sntesis

0.5

1.5

4.5

Subtotales:

6.0

5.0

4.1

4.1.1

4.1.2

4.1.3

4.1.4

0.5

3C, 6B, 9B

10.0

ESTRATEGIAS DE APRENDIZAJE

Se utiliza la estrategia de POL.

Indagacin de los temas solicitados de los circuitos secuenciales, y realizar dinmicas de diseo y ensamble.

Discusin y conclusin en forma grupal de los conceptos vistos en la unidad temtica.

Desarroll de prcticas utilizando una tarjeta de desarrollo con FPGA o CPLD y componentes discretos.

Desarrollo del proyecto solo o en conjunto con otra(s) UAp (a consideracin del profesor) de la unidad de aprendizaje.

Resolucin de ejercicios prcticos de sistemas secuenciales (registros, contadores, etc.), utilizando HDL (VHDL y/o Verilog) por medio del trabajo

colaborativo y dinmicas dentro y fuera del aula.

EVALUACIN DE LOS APRENDIZAJES

Portafolio de evidencias:

Tareas de investigacin y dinmicas de grupo

Prctica de laboratorio de circuitos secuenciales

Evaluacin escrita de los circuitos secuenciales

Avance del proyecto

Autoevaluacin (Rbrica) y Coevaluacin (Rbrica)

25%

25%

25%

25%

INSTITUTO POLITCNICO NACIONAL

SECRETARA ACADMICA

DIRECCIN DE EDUCACIN SUPERIOR

UNIDAD DE APRENDIZAJE:

N UNIDAD TEMTICA: V

Circuitos Lgicos.

HOJA:

DE

11

NOMBRE: Diseo y ensamble de mquinas de

estado finito.

UNIDAD DE COMPETENCIA ESPECFICA

Desarrolla las mquinas de estado finito dentro de un FPGA o CPLD mediante un editor de estados y con HDL (VHDL

y/o Verilog).

No.

CONTENIDOS

Por el

profesor

HORAS AD

Actividades

de docencia

T

Por el alumno

HORAS TAA

Actividades de

Aprendizaje

Autnomo

T

5.1

Conceptos de las mquinas de estado finito (FSM)

y uso del editor de FSM para implementarlas en los

ambientes de desarrollo.

0.5

1.0

0.5

5.2

5.2.1

5.2.2

5.2.3

Diseo, ensamble y simulacin de FSM con HDL.

Mquinas de Mealy.

Mquinas de Moore.

Mquinas mixtas.

1.0

1.5

4.5

0.5

1.5

6.0

5.3

Desarrollo de etapas de control y automatizacin

para su aplicacin en sistemas mecatrnicos

utilizando las FSM. Simulacin y sntesis en FPGA

o CPLD

2.0

4.0

Subtotales:

ESTRATEGIAS DE APRENDIZAJE

0.0

CLAVE

BIBLIOGRFICA

2B, 5B, 10B

11.0

Se utiliza la estrategia de POL.

Indagacin de los temas solicitados de las FSM.

Discusin y conclusin en forma grupal de los conceptos vistos en la unidad temtica.

Desarroll de prcticas utilizando una tarjeta de desarrollo con FPGA o CPLD y componentes discretos.

Trmino del proyecto solo o en conjunto con otra(s) UAp (a consideracin del profesor) de la unidad de aprendizaje.

Resolucin de ejercicios prcticos de las mquinas de estado finito empleando tanto los editores de FSM como el HDL

(VHDL y/o Verilog), por medio del trabajo colaborativo y dinmicas dentro y fuera del aula.

EVALUACIN DE LOS APRENDIZAJES

Portafolio de evidencias:

Tareas de investigacin y dinmicas de grupo

Prctica de laboratorio de mquinas de estado finito

Evaluacin escrita de las FSM

Proyecto terminado

Autoevaluacin (Rbrica) y Coevaluacin (Rbrica)

25%

25%

25%

25%

INSTITUTO POLITCNICO NACIONAL

SECRETARA ACADMICA

DIRECCIN DE EDUCACIN SUPERIOR

UNIDAD DE APRENDIZAJE:

Circuitos Lgicos

HOJA:

DE

11

RELACIN DE PRCTICAS

PRCTICA No.

NOMBRE DE LA PRCTICA

UNIDADES

TEMTICAS

DURACIN

LUGAR DE REALIZACIN

Compuertas bsicas con elementos

discretos y prctica guiada.

3.0

Laboratorio de Sistemas

Digitales

Ambiente

simulador.

II

4.5

Circuitos combinacionales bsicos.

III

4.5

Circuitos combinacionales aritmticos

y lgicos.

III

6.0

Control digital y automatizacin con

circuitos combinacionales.

III

6.0

Temporizadores, Flip-flops y registros.

IV

3.0

Memorias RAM y ROM.

IV

1.5

Contadores.

IV

3.0

Registro de corrimiento universal.

IV

1.5

10

Control digital y automatizacin con

circuitos secuenciales.

IV

6.0

11

Editor de FSM.

1.5

12

Diseo, sntesis y simulacin de FSM

(Mealy, Moore y mixta).

6.0

13

Control digital y automatizacin con

FSM.

7.5

TOTAL DE

HORAS

54.0

de

desarrollo

su

EVALUACIN Y ACREDITACIN:

La evaluacin de las prcticas de laboratorio corresponde al 25% de la evaluacin total de la UAp, siendo requisito

aprobarlas para tener derecho a la evaluacin de los otros rubros y acreditar la UAp.

Las prcticas sern evaluadas considerando la entrega de la investigacin previa (pre-reporte) dentro de los primeros 10

minutos de clase, el correcto funcionamiento de todos los puntos del desarrollo en cada prctica, la entrega del reporte

escrito y el cumplimiento de las normas del laboratorio. El reporte escrito contendr una introduccin, todos los puntos del

desarrollo con los cdigos en HDL comentados, conclusiones y referencias.

INSTITUTO POLITCNICO NACIONAL

SECRETARA ACADMICA

DIRECCIN DE EDUCACIN SUPERIOR

UNIDAD DE APRENDIZAJE:

CIRCUITOS LGICOS

HOJA:

DE

PROCEDIMIENTO DE EVALUACIN

Para la evaluacin y acreditacin de la unidad de aprendizaje se considera:

Evaluacin diagnostica de conocimientos previos (sin ponderacin), evaluacin formativa y

evaluacin sumativa de los conceptos vistos en clase y en laboratorio, a travs de evaluaciones

escritas, prcticas de laboratorio, tareas de investigacin, dinmicas de grupo y proyecto, en cada

unidad temtica; adems se utilizarn rubricas de autoevaluacin y coevaluacin. Presentando como

sustento los reportes escritos, defensa oral y circuitos o prototipos funcionando. La evaluacin

diagnstica tambin proporciona informacin para definir si el proyecto es solo o es integrador.

Tareas de investigacin y dinmicas de grupo

Prctica de laboratorio

Evaluacin escrita

Proyecto solo o en conjunto con otra(s) UAp

Autoevaluacin (Rbrica) y Coevaluacin (Rbrica)

25%

25%

25%

25%

Los porcentajes a cubrir por unidad temtica para valorar el 100% de la unidad de aprendizaje son:

Unidad Temtica I

Unidad Temtica II

Unidad Temtica III

Unidad Temtica IV

Unidad Temtica V

20%

20%

20%

20%

20%

Para evaluar la unidad de aprendizaje en examen extraordinario o a titulo de suficiencia ETS:

Realizar una evaluacin escrita de las unidades temticas I a V (50%).

Presentar funcionando y reportar (cdigos y simulacin) dos tareas dedicadas o realizar un

proyecto, ambos asignados por el profesor que aplica el examen, con soporte de la

Academia de Electrnica (50%).

Para acreditar esta unidad de aprendizaje por competencia, se deber solicitar dentro de las tres

primeras semanas de inicio del semestre la autorizacin de la Academia de Electrnica y deber

cubrir los siguientes puntos: (i) Realizar una evaluacin sumativa terica de todas las unidades

temticas, 30%, (ii) Presentar funcionando y defender 4 prcticas asignadas por la Academia de

Electrnica, 35%, y (iii) Realizar un proyecto dado por la Academia de Electrnica, 35%. En todos los

incisos es necesario entregar los cdigos escritos en HDL y su simulacin.

La Subdireccin Acadmica en conjunto con la Academia de Electrnica determinar la equivalencia

de la competencia con otras unidades de aprendizaje, tanto de unidades acadmicas del IPN as

como externas.

11

INSTITUTO POLITCNICO NACIONAL

SECRETARA ACADMICA

DIRECCIN DE EDUCACIN SUPERIOR

UNIDAD DE APRENDIZAJE:

CLAVE

1

CIRCUITOS LGICOS

C

X

HOJA:

10

DE

11

BIBLIOGRAFA

Botros Nazeih M. (2006), HDL Programming Fundamentals: VHDL and

Verilog (1st. Edition), USA: Da Vinci Engineering, ISBN: 1-58450-855-8.

Brown S., Vranesic Z. (2008), Fundamentals of Digital Logic with VHDL

Design with CD-ROM (3a edicin), USA: Mcgraw Hill, ISBN:

9780077221430.

Chu Pong P. (2008), FPGA Prototyping by VHDL Examples, USA: John

Wiley and Sons, ISBN: 978-0-470-18531-5.

Floyd T. L. (2006), Fundamentos de Sistemas Digitales (9 edicin),

Mxico: Pearson, ISBN: 9788483220856.

Morris Mano M. (2007), Digital design, (4 edicin), USA: Pearson

Prentice Hall, ISBN: 9780131989245.

Pardo F., Boluda J. A. (2004), VHDL, lenguajes para sntesis y modelado

de circuitos (2 edicin), Mxico: Alfaomega Ra Ma, ISBN 970-15-10178. Este es un libro clsico.

Prez S. A, Soto E., Fernndez S. (2002), Diseo de Sistemas Digitales

con VHDL, Espaa: Ed. Thomson, ISBN 84-9732-081-6.

Tocci R. J., et.al. (2007), Sistemas Digitales: principios y aplicaciones(10

edicin), Mxico: Prentice Hall, ISBN: 970-26-0297-1.

Wakerly John F. (2007), Digital design: principles and practices (4

edicin), USA: Pearson Prentice Hall, ISBN: 9780132016117.

10

Software de desarrollo, varias compaas, (ISE) www.xilinx.com,

(QuartusII) www.altera.com, (Libero) www.actel.com.

INSTITUTO POLITCNICO NACIONAL

SECRETARA ACADMICA

DIRECCIN DE EDUCACIN SUPERIOR

PERFIL DOCENTE POR UNIDAD DE APRENDIZAJE

1. DATOS GENERALES

UNIDAD ACADMICA:

PROGRAMA

ACADMICO:

UNIDAD PROFESIONAL INTERDISCIPLINARIA EN INGENIERA Y TECNOLOGAS

AVANZADAS

Ingeniera Mecatrnica

REA DE FORMACIN:

ACADEMIA:

II

NIVEL

Institucional

Cientfica

Bsica

Electrnica

Profesional

Terminal y de

Integracin

UNIDAD DE APRENDIZAJE: Circuitos Lgicos

ESPECIALIDAD Y NIVEL ACADMICO REQUERIDO:

Maestra en Ciencias o en Ingeniera rea electrnica

2. PROPSITO DE LA UNIDAD DE APRENDIZAJE: Implementa control digital mediante dispositivos

lgicos programables y lenguaje descriptivo de hardware.

3. PERFIL DOCENTE:

CONOCIMIENTOS

Electricidad y Circuitos

elctricos,

Electrnica analgica,

digital y de potencia,

Sensores y Actuadores,

Lenguajes de Descripcin

de Hardware,

Tarjetas de desarrollo,

Software de desarrollo

(Xilinx, Altera, Lattice,

Actel, etc.) para PLD,

CPLD y FPGA.

Modelo Educativo

Institucional (MEI).

EXPERIENCIA

PROFESIONAL

Dos aos de experiencia

mnima profesional en el

campo de la

Ingeniera en

Comunicaciones,

Electrnica, Control,

Mecatrnica,

Mantenimiento elctricoelectrnico.

Diseo electrnico.

HABILIDADES

ACTITUDES

Dominio de la asignatura.

El manejo de equipo de

medicin y de prueba.

Manejo de grupos.

Comunicacin oral y

escrita.

Capacidad de anlisis y

sntesis.

Manejo de materiales

Didcticos.

Organizacin.

Creatividad.

Liderazgo.

Manejo del MEI.

Responsabilidad.

Tolerancia.

Honestidad.

Compromiso social.

Proactivo.

Comunicativo.

Previsor.

Respeto (maestro-alumno).

tica profesional y personal.

Superacin docente y

profesional.

Solidaridad.

Compromiso social y

ambiental.

Puntualidad.

ELABOR

REVIS

AUTORIZ

M. en C. Blanca Esther Carvajal Gmez

Presidente de Academia

M. en C. Jorge Fonseca Campos

Enc. de la Subdireccin Acadmica

M. en C. Arod Rafael Carvallo Domnguez

Director de la Unidad Acadmica

Vous aimerez peut-être aussi

- Lenguaje de Programacion VDHLDocument36 pagesLenguaje de Programacion VDHLAlex PAPas encore d'évaluation

- Los Principios de La Relatividad, Una Introducción PedagógicaDocument5 pagesLos Principios de La Relatividad, Una Introducción PedagógicaJonathan NavaPas encore d'évaluation

- LCD Con El AVRDocument14 pagesLCD Con El AVRJonathan NavaPas encore d'évaluation

- Politica de Dividendos PDFDocument13 pagesPolitica de Dividendos PDFAnnie224100% (1)

- Nuestro Curso de HebreoDocument94 pagesNuestro Curso de HebreoSalomé Subiela100% (11)

- Programa de Estudio Especialidad ELECTRÓNICA PDFDocument228 pagesPrograma de Estudio Especialidad ELECTRÓNICA PDFErmiz KiPas encore d'évaluation

- Aplicación de Simulación Cuadro ComparativoDocument9 pagesAplicación de Simulación Cuadro ComparativoMaria Del Rosario Martinez Geronimo100% (1)

- 0318 - Trabajo de Investigación 1 - Huaycos - Prof SandraDocument17 pages0318 - Trabajo de Investigación 1 - Huaycos - Prof SandraMarioPas encore d'évaluation

- Carta Gantt Elo307Document5 pagesCarta Gantt Elo307Javier EscobarPas encore d'évaluation

- Mecánica para Ingeniería Estática (Anthony Bedford, Wallace Fowler)Document628 pagesMecánica para Ingeniería Estática (Anthony Bedford, Wallace Fowler)AndreaKarol Escobar Contreras81% (31)

- Plan de Emergencia y EvacuaciónDocument11 pagesPlan de Emergencia y EvacuaciónGISNEY PAOLA PEREZ PACHECO100% (1)

- Ley de Newton Del EnfriamientoDocument13 pagesLey de Newton Del EnfriamientoJohn RamírezPas encore d'évaluation

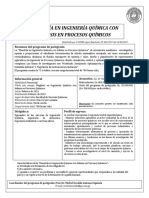

- Maestria en Ingeniería Química Con Énfasis en Procesos QuímicosDocument1 pageMaestria en Ingeniería Química Con Énfasis en Procesos QuímicosRodney UcedoPas encore d'évaluation

- Feliu, Torruella - La Simulacion y Los JuegosDocument7 pagesFeliu, Torruella - La Simulacion y Los JuegosAlen SayavedraPas encore d'évaluation

- Estudio de Caso - Modelado de La Dispersión de ContaminantesDocument19 pagesEstudio de Caso - Modelado de La Dispersión de ContaminanteshijueputamancoPas encore d'évaluation

- Análisis de Vaciado de Un TúnelDocument2 pagesAnálisis de Vaciado de Un Túnelmarlon mosqueraPas encore d'évaluation

- I.E.3. Simulacros de EvacuaciónDocument21 pagesI.E.3. Simulacros de EvacuaciónelisabtePas encore d'évaluation

- Unidad 3 Caracterizacion e Interpretacion SismicaDocument39 pagesUnidad 3 Caracterizacion e Interpretacion SismicaGladis Ethel Madrigal HernándezPas encore d'évaluation

- Mod FlowDocument9 pagesMod FlowMilagros De La CruzPas encore d'évaluation

- Taller 2 Gusano ExcursionistaDocument2 pagesTaller 2 Gusano ExcursionistaAna RodriguezPas encore d'évaluation

- Informe Sobre Los Programas de Seguridad Completo CreoDocument13 pagesInforme Sobre Los Programas de Seguridad Completo CreoKka OaapPas encore d'évaluation

- Informe de Proceso y ProcedimientoDocument33 pagesInforme de Proceso y ProcedimientoDaniel RiosPas encore d'évaluation

- 01 Fundamento Red PresionDocument77 pages01 Fundamento Red PresionPats LitumaPas encore d'évaluation

- Planteamiento Del Problema Tesis de GradoDocument4 pagesPlanteamiento Del Problema Tesis de GradoAbi Josue AcostaPas encore d'évaluation

- Decisiones de InversionDocument70 pagesDecisiones de InversionDaniel SaPas encore d'évaluation

- Modelizacion de La Aleatoriedad en Sistemas Discretos DocumentoDocument4 pagesModelizacion de La Aleatoriedad en Sistemas Discretos DocumentoKevin James100% (1)

- Modelo Heuristico para Analisis de Flujo VehicularDocument125 pagesModelo Heuristico para Analisis de Flujo VehicularManuel VhPas encore d'évaluation

- Ingenieria de Trafico Doc.1Document3 pagesIngenieria de Trafico Doc.1Pablo José Farfan GuerreroPas encore d'évaluation

- 1 Uso de Simulación para La SemiologíaDocument9 pages1 Uso de Simulación para La SemiologíaKarl MarxPas encore d'évaluation

- Sistemas Informáticos - 4° Año Contador - Módulo - UNIDAD I - II - III - IV - VDocument223 pagesSistemas Informáticos - 4° Año Contador - Módulo - UNIDAD I - II - III - IV - VJulieta Malica NanternePas encore d'évaluation

- Original DT264Document457 pagesOriginal DT264Freddy Astucuri QuispePas encore d'évaluation

- Modhidro 5Document4 pagesModhidro 5Frank Eduardo Ramírez GutierrezPas encore d'évaluation

- Tarea 03Document8 pagesTarea 03YonatanOrlandoCuervoCamargo0% (1)

- Cricuitos - de - Comminucion - y - Molienda - Operacion - y - Optimizacion 3Document109 pagesCricuitos - de - Comminucion - y - Molienda - Operacion - y - Optimizacion 3ericka7.Pas encore d'évaluation