Académique Documents

Professionnel Documents

Culture Documents

Uso y Funcionamiento de Xilinx ISE Design Suite 12

Transféré par

John Walter Ticona QuispeCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Uso y Funcionamiento de Xilinx ISE Design Suite 12

Transféré par

John Walter Ticona QuispeDroits d'auteur :

Formats disponibles

1. Uso y funcionamiento de Xilinx ISE Design Suite 12.

1

1.1. Creacin de un nuevo proyecto

Pasos a seguir:

1. Presionamos Ok o tambin cerramos el cuadro de Did you know.

2. Presionamos File New project y aparecer el cuadro Create New Project

3. En Name editamos el nombre de nuestro proyecto en este caso como ejemplo:

nuevo_proyecto.

4. En Location elegimos la ruta donde se guardar nuestro proyecto, como ejemplo:

C:\Users\John\Desktop\EJEMPLO MICROELECTRONICA\nuevo_proyecto.

5. En Working directory se deja as como est, y si se desea se edita en Description lo

que consiste nuestro proyecto.

6. En Top-level source type: es para elegir el tipo fuente en este caso se elige HDL,

despus de haber seguido los pasos anteriores debe quedar el cuadro Create New

Project de esta forma:

7. Presionamos Next y nos aparece el cuadro Project settings

8. El cuadro tendr que estar con las siguientes caractersticas:

Family: Spartan3E

Device :XC3S500E

Package:FG320

Speed: -4

Preferred Languaje: VHDL

Son los datos que corresponden al Datasheet del FPGA Spartan3E; el resto se deja

como est.

9. Presionamos Next y aparecer todo lo que se seleccion anteriormente, y

presionamos Finish.

1.2. Programacin en el entorno de Xilinx ISE Design Suite 12.1

Pasos a seguir:

1. Despus de haber creado nuestro Proyecto, vamos a la seccin donde dice

Hierarchy que est en la parte superior izquierda, y damos clic derecho a la sub-

opcin que lo contiene xc3s500e-4fg320 y damos en la primera opcin New

source.

2. Nos aparecer una ventana Select source type y donde seleccionamos haciendo clic

VHDL Module

3. Nos dirigimos al costado derecho de la ventana en la opcin File name, y editamos

un nombre; como ejemplo: inicio, luego en Location no realizamos cambios ya que

es mejor que se guarde en la misma ruta; debemos verificar que este activada la

opcin Add to Project. Y presionamos Next.

4. Nos aparecer una ventana Define module , editamos en Architecture name y

como ejemplo: compuerta ; para iniciar con el proceso de programacin realizaremos

una compuerta OR con dos entradas y una salida definiendo los puertos a ,b como in

(entradas) y c como out (salida) todo ello lo definimos en Port name y Direction

y luego damos clic a Next.

5. Nos aparecer una ventana Summary donde nos indica las entradas y salidas

seleccionadas anteriormente ; le damos clic a Finish

6. Tendremos el entorno de programacin de Xilinx donde se realizar el programa

respectivo de la compuerta OR de dos entradas y una salida, para el FPGA Spartan3.

1.2.1. Entorno Xilinx de programacin

1.2.2. Ejemplo: Compuerta OR: Dos entradas y una salida

Pasos a seguir:

1. Colocaremos en el Campo de programacin c <=a or b; donde se realizar la operacin

OR entre las dos variables de entrada a y b; y se almacenar el resultado en la

variable c mediante la igualdad expresada <=. Y tenemos diseado una compuerta

OR.

Uso de libreras

Declaracin de variables

Campo de programacin

2. Ya realizado el programa diseando la compuerta OR, comprobamos si no existen

errores y para ello nos dirigimos a la parte inferior izquierda Process hacemos clic

en el botn + en la opcin Synthesize XST y realizamos doble clic o clic derecho

y luego Run en Check Syntax.

3. Los resultados de esta comprobacin de errores se observan en el cuadro inferior

donde se muestran los errores y/o advertencias. Si no existen errores, en Check

Sintax aparecer un check de lo contrario un aspa si es error; adems en el cuadro

inferior aparece Process "Check Syntax" completed successfully si est correcto.

1.3. Simulacin en Xilinx ISE Design Suite 12.1

Pasos a seguir:

1. Luego de haber comprobado y no haber obtenido ningn error; vamos a realizar la

simulacin para ver si cumple la compuerta OR; nos dirigimos en la ventana superior

izquierda Hierarchy; y hacemos clic derecho en inicio- compuerta (inicio.vhd) y

clic en New Source.

2. Nos aparecer la ventana Select Source Type

3. Lamentablemente en esta versin de Xilinx 12.1 quedo bloqueada la opcin Test

Bench waveform a diferencia de las versiones anteriores; sin embargo se explicar

segn a las versiones anteriores. Seleccionamos Test Bench Waveform y en File

name colocamos el nombre diferente al anterior como ejemplo: inicio_tb dejamos en

misma ruta de siempre, no cambiamos nada; y Presionamos Next.

4. Luego volvemos a Presionar Next

5. Aparecer la ventana que resume todo lo que hemos seleccionado anteriormente para

simular; y presionamos Finish

6. Aparecer una ventana Initial timing and Clock wizard Initialize Timing ; hacemos

clic en Combinational (or internal clock) que est dentro de Clock information el

resto se deja por defecto, y se modifica posteriormente. Presionamos Finish

7. Nos aparecer el siguiente entorno; donde se modifica diferentes valores lgicos (0 y

1) en las variables de entradas a y b que van desde 0 a 1000ns, ese rango de

tiempo se puede modificar as como el ancho de pulso.

8. Para modificar el fin del Test Bench, es decir el fin del tiempo (1000ns) hacemos clic

derecho en el entorno y seleccionamos Set End of Test Bench

9. Dentro de la ventana colocaremos 1500ns y presionaremos ok, veremos que la

escala se ajusta.

10. El ancho de pulso se puede cambiar haciendo clic derecho en el entorno tambin, y se

leccionando Rescale Timing , como ejemplo modificaremos a 20ns el ancho en

Check outputs y Assign inputs y presionamos ok.

11. Podemos establecer los valores lgicos de manera manual en las variables a y b de

manera simultnea. Haciendo clic y estableciendo unos y ceros hasta el End

time(1500ns).

12. O sino podemos hacer doble clic en cualquiera de las variables a o b y nos

aparecer Set value que es un generador de valores lgicos; hacemos clic luego en el

botn Pattern Wizard.

13. Aparecer la ventana Pattern Wizard donde podemos seleccionar una seal

randomica de valores variados al azar, seleccionamos en Pattern Type la opcin

Random signal y presionamos ok.

14. Nos aparecer una seal ya generada en la variable donde hayamos hecho doble clic

para generarla, en este caso en a.

15. Guardamos los cambios efectuados en general apretando el botn Guardar y

cerramos el entorno en x superior derecha (no confundir con el cerrar del

programa).

16. Para ya observar los resultados nos ubicamos en Sources (superior izquierda) y en

Sources for seleccionamos la opcin Behavorial simulation

17. Luego nos ubicamos en Processes (inferior izquierda), hacemos clic en el botn +

de la opcin Xillinx ISE simulator , y por ltimo hacemos doble clic en Simulate

Behavorial Model

18. Y Obtenemos el resultado de nuestra compuerta en un nuevo entorno.

19. En el entorno se puede utilizar markers dndole clic derecho en el entorno y

seleccionando Add Marker

Vous aimerez peut-être aussi

- Guía Xilinx para Contador.Document34 pagesGuía Xilinx para Contador.Thais M. Batista V.Pas encore d'évaluation

- PNT Cromatografo IónicoDocument3 pagesPNT Cromatografo IónicoJorge RamonPas encore d'évaluation

- Wincupl5winsim GuiapracticaesencialDocument8 pagesWincupl5winsim GuiapracticaesencialEli GarciaPas encore d'évaluation

- Tutorial Sistema ScadaDocument27 pagesTutorial Sistema ScadaRonald Pineda100% (1)

- Manual de Migraciones - SLC500 A CompactLogix (Rev 1)Document22 pagesManual de Migraciones - SLC500 A CompactLogix (Rev 1)rguzmanabundis100% (1)

- Ejecicio 9 - Julian Octavio Garcia MIguelDocument52 pagesEjecicio 9 - Julian Octavio Garcia MIguelJulian MiguelPas encore d'évaluation

- Manual de Practicas para Tarjeta Fpga Mediante Lenguaje VHDLDocument17 pagesManual de Practicas para Tarjeta Fpga Mediante Lenguaje VHDLAriel Del AngelPas encore d'évaluation

- LD MICRO Guia PLC AlternativoDocument49 pagesLD MICRO Guia PLC AlternativoJuan Fco Rocha Paredes80% (5)

- Configuración en Exstream - Communication BuilderDocument33 pagesConfiguración en Exstream - Communication BuilderJohan RoldanPas encore d'évaluation

- Contador Ascendente y Descendente en VHDLDocument12 pagesContador Ascendente y Descendente en VHDLStephany BradburyPas encore d'évaluation

- Guia para Quemar en VivadoDocument2 pagesGuia para Quemar en VivadomntxPas encore d'évaluation

- Tutorial WINDLDRDocument8 pagesTutorial WINDLDRAthos27Pas encore d'évaluation

- Simulacion de Reservorios CMGDocument4 pagesSimulacion de Reservorios CMGJerick Andre Rodriguez MottaPas encore d'évaluation

- Guía básica Pspice análisis transitorioDocument5 pagesGuía básica Pspice análisis transitorioMMLaguzPas encore d'évaluation

- Manual para RSviewDocument29 pagesManual para RSviewuscanga0301Pas encore d'évaluation

- Tutorial de Intouch UltimoDocument38 pagesTutorial de Intouch UltimoSamael SickPas encore d'évaluation

- Uso de - RSLogix EmulateDocument65 pagesUso de - RSLogix EmulateHelmer RamosPas encore d'évaluation

- Tutoriale Cary50Document12 pagesTutoriale Cary50Belen RosalesPas encore d'évaluation

- Crear proyecto ispLEVERDocument29 pagesCrear proyecto ispLEVERAntonioPas encore d'évaluation

- Práctica - 05 PetrelDocument106 pagesPráctica - 05 PetrelEder VasquezPas encore d'évaluation

- Manual Flex VSCodeDocument24 pagesManual Flex VSCodeXime BelloPas encore d'évaluation

- Tutorial PSpice circuitos básicosDocument5 pagesTutorial PSpice circuitos básicosEnrique LopezPas encore d'évaluation

- Practica1 CuartusDocument13 pagesPractica1 CuartusartnosPas encore d'évaluation

- Programación LADDERDocument9 pagesProgramación LADDERDarth VaderPas encore d'évaluation

- Reporte Practica 1Document11 pagesReporte Practica 1Joel Rojas DuartePas encore d'évaluation

- Datamine Studio 3D guía paso a pasoDocument56 pagesDatamine Studio 3D guía paso a pasoRicardo Contreras100% (1)

- Tutorial Básico de Uso de VivadoDocument12 pagesTutorial Básico de Uso de VivadoAngel YaaelPas encore d'évaluation

- Tutorial Básico de Uso de VivadoDocument12 pagesTutorial Básico de Uso de VivadoAngel YaaelPas encore d'évaluation

- Guía Enlace Codesys V2.3 FestofluidsimDocument19 pagesGuía Enlace Codesys V2.3 FestofluidsimRicardo Ricce VictorioPas encore d'évaluation

- Programación de PLC y simulador SILO para control de equipo MecatrónicaDocument4 pagesProgramación de PLC y simulador SILO para control de equipo MecatrónicaAlvaro Samuel Macias TortelliniPas encore d'évaluation

- Tutorial Compuertas lógicas, medio sumador y sumador completo en FPGA Nexys 4Document25 pagesTutorial Compuertas lógicas, medio sumador y sumador completo en FPGA Nexys 4AlexiKleeoPas encore d'évaluation

- Tutorial WarpDocument8 pagesTutorial WarpMario Merino MárquezPas encore d'évaluation

- Guía de Configuración de Test CasesDocument50 pagesGuía de Configuración de Test CasesEduardo Antonio Díaz FredesPas encore d'évaluation

- Programacion de PLC Micrologix 1200 - ABDocument28 pagesProgramacion de PLC Micrologix 1200 - ABgamh13100% (9)

- Manual Rápido Del MPLABDocument62 pagesManual Rápido Del MPLABpunkyjairPas encore d'évaluation

- SFC en Codesys PDFDocument26 pagesSFC en Codesys PDFManuel CornejoPas encore d'évaluation

- PRÁCTICA SILO simulador LogixPro-500Document4 pagesPRÁCTICA SILO simulador LogixPro-500Alvaro Samuel Macias TortelliniPas encore d'évaluation

- Tutorial Vulcan 8.0 2-2013Document56 pagesTutorial Vulcan 8.0 2-2013Miguel Angel Contreras Madariaga100% (6)

- MANUAL DE MATLAB Y LABVIEW PARA ADQUISICIÓN Y ANÁLISIS DE DATOSDocument22 pagesMANUAL DE MATLAB Y LABVIEW PARA ADQUISICIÓN Y ANÁLISIS DE DATOSDiego Frias ParedesPas encore d'évaluation

- Guia Instalacion Sap Ides 4.7Document104 pagesGuia Instalacion Sap Ides 4.7Mario VargasPas encore d'évaluation

- PLC RSViewDocument28 pagesPLC RSViewCarlos GranilloPas encore d'évaluation

- Manual Comunicación Labview-Tia PortalDocument33 pagesManual Comunicación Labview-Tia PortaldavidPas encore d'évaluation

- Manual Movicon PDFDocument28 pagesManual Movicon PDFOmar GodoyPas encore d'évaluation

- Samuel Leon - Tarea 5Document13 pagesSamuel Leon - Tarea 5Samuel LeonPas encore d'évaluation

- Manual de Introducción A Active HDLDocument14 pagesManual de Introducción A Active HDLAdolfo LunaPas encore d'évaluation

- 1 Manual ConstruccionModeloSWATDocument22 pages1 Manual ConstruccionModeloSWATFranz Urb FloPas encore d'évaluation

- Manual de Uso Eg Star ReplanteoDocument8 pagesManual de Uso Eg Star ReplanteoF Javier MalleaPas encore d'évaluation

- Modelacion HidraulicaDocument16 pagesModelacion HidraulicaFabian MunevarPas encore d'évaluation

- Programación con lenguajes de guión en páginas web. IFCD0110D'EverandProgramación con lenguajes de guión en páginas web. IFCD0110Pas encore d'évaluation

- Programación Java - Una Guía para Principiantes para Aprender Java Paso a PasoD'EverandProgramación Java - Una Guía para Principiantes para Aprender Java Paso a PasoÉvaluation : 3 sur 5 étoiles3/5 (7)

- Aprender Adobe After Effects CS5.5 con 100 ejercicios prácticosD'EverandAprender Adobe After Effects CS5.5 con 100 ejercicios prácticosPas encore d'évaluation

- Aprender Postproducción Avanzada con After Effects con 100 ejercicios prácticosD'EverandAprender Postproducción Avanzada con After Effects con 100 ejercicios prácticosPas encore d'évaluation

- Compilador C CCS y Simulador Proteus para Microcontroladores PICD'EverandCompilador C CCS y Simulador Proteus para Microcontroladores PICÉvaluation : 2.5 sur 5 étoiles2.5/5 (5)

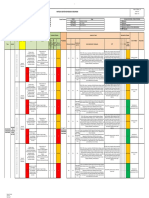

- Planificación de supervisores y áreas de la planta por semanaDocument1 pagePlanificación de supervisores y áreas de la planta por semanaJohn Walter Ticona QuispePas encore d'évaluation

- Acreditacion 8 MergedDocument25 pagesAcreditacion 8 MergedJohn Walter Ticona QuispePas encore d'évaluation

- 1.1 EC - Miperc - 175 REV02 C2Document2 pages1.1 EC - Miperc - 175 REV02 C2John Walter Ticona QuispePas encore d'évaluation

- Informe DC DrivesDocument8 pagesInforme DC DrivesJohn Walter Ticona QuispePas encore d'évaluation

- Reporte Diario 16-09-2021Document4 pagesReporte Diario 16-09-2021John Walter Ticona QuispePas encore d'évaluation

- EpaDocument16 pagesEpaJohn Walter Ticona QuispePas encore d'évaluation

- MaletaDocument1 pageMaletaJohn Walter Ticona QuispePas encore d'évaluation

- Supervisores Mantenimiento SMCV - 40avo Acuartelamiento v1Document1 pageSupervisores Mantenimiento SMCV - 40avo Acuartelamiento v1John Walter Ticona QuispePas encore d'évaluation

- Reporte Diario 19-09-2021Document4 pagesReporte Diario 19-09-2021John Walter Ticona QuispePas encore d'évaluation

- Factura Electronica INTELLIALLDocument1 pageFactura Electronica INTELLIALLJohn Walter Ticona QuispePas encore d'évaluation

- Mmparte 13Document11 pagesMmparte 13John Walter Ticona QuispePas encore d'évaluation

- Ait 10591910 Bitacora Servicio Mtto Instrumental Molinos C1 y Servicios VariosDocument4 pagesAit 10591910 Bitacora Servicio Mtto Instrumental Molinos C1 y Servicios VariosJohn Walter Ticona QuispePas encore d'évaluation

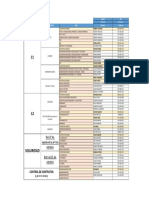

- Apellidos y NombresDocument1 pageApellidos y NombresJohn Walter Ticona QuispePas encore d'évaluation

- Ayuda Teoria AcidoDocument4 pagesAyuda Teoria AcidoJohn Walter Ticona QuispePas encore d'évaluation

- TrabajoDocument10 pagesTrabajoJohn Walter Ticona QuispePas encore d'évaluation

- LeemeDocument1 pageLeemeJohn Walter Ticona QuispePas encore d'évaluation

- Gen BrokerDocument70 pagesGen BrokerJohn Walter Ticona QuispePas encore d'évaluation

- Debido A Que La Sección 404Document8 pagesDebido A Que La Sección 404John Walter Ticona QuispePas encore d'évaluation

- Gauge ActiveXDocument10 pagesGauge ActiveXJohn Walter Ticona QuispePas encore d'évaluation

- Diagrama de Flujo para Una InterrupcionDocument5 pagesDiagrama de Flujo para Una InterrupcionJohn Walter Ticona QuispePas encore d'évaluation

- 225 PubDocument88 pages225 PubJohn Walter Ticona QuispePas encore d'évaluation

- Envío SMS Alarma PIC MóvilDocument27 pagesEnvío SMS Alarma PIC MóvilJohn Walter Ticona QuispePas encore d'évaluation

- TrabajoDocument10 pagesTrabajoJohn Walter Ticona QuispePas encore d'évaluation

- Diagrama de Flujo para Una InterrupcionDocument5 pagesDiagrama de Flujo para Una InterrupcionJohn Walter Ticona QuispePas encore d'évaluation

- Archivo Capítulo 5.aspen Hysys. Dest - Atmos. de Crudo PetróliferoDocument42 pagesArchivo Capítulo 5.aspen Hysys. Dest - Atmos. de Crudo PetróliferoJohn Walter Ticona QuispePas encore d'évaluation

- UasDocument1 pageUasJohn Walter Ticona QuispePas encore d'évaluation

- Caratula Ing. ElectrónicaDocument1 pageCaratula Ing. ElectrónicaJohn Walter Ticona QuispePas encore d'évaluation

- DIA Planta Acido LagunasDocument73 pagesDIA Planta Acido LagunasJohn Walter Ticona QuispePas encore d'évaluation

- Img PDFDocument1 pageImg PDFJohn Walter Ticona QuispePas encore d'évaluation

- Codigo MatlabDocument2 pagesCodigo MatlabJohn Walter Ticona QuispePas encore d'évaluation

- Tesis Universidad de LeonDocument40 pagesTesis Universidad de Leonarisnordico100% (1)

- Como Enviar Correspondencia Por Correo ElectronicoDocument7 pagesComo Enviar Correspondencia Por Correo ElectronicoLevin MeridaPas encore d'évaluation

- Evidencia 1 Reconocer Las Características Básicas Del Comercio ElectrónicoDocument8 pagesEvidencia 1 Reconocer Las Características Básicas Del Comercio ElectrónicoKalethistas MonteriaPas encore d'évaluation

- Megger - Instrumentos de Prueba Eléctrica y Medición-2Document10 pagesMegger - Instrumentos de Prueba Eléctrica y Medición-2joseangelmarinPas encore d'évaluation

- SoftwareDocument4 pagesSoftwareRosa GonzálezPas encore d'évaluation

- Verificacion AuthyDocument6 pagesVerificacion AuthyMaría Francisca ArayaPas encore d'évaluation

- Prog1-I02 - Clases Objetos y MetodosDocument15 pagesProg1-I02 - Clases Objetos y MetodosDante Alvarado TokomoPas encore d'évaluation

- Planificación en Base A La Metodología ScrumDocument3 pagesPlanificación en Base A La Metodología Scrumjavier lucio huanca huaranca50% (2)

- Apuntes CDocument191 pagesApuntes CMarco Antonio Sánchez PeribáñezPas encore d'évaluation

- PVS Gfe 112Document206 pagesPVS Gfe 112Julio Cesar VegaPas encore d'évaluation

- GUIA NUEVA T-NOMINA BANORTE 22 Marzo 22Document13 pagesGUIA NUEVA T-NOMINA BANORTE 22 Marzo 22Ivan GandaraPas encore d'évaluation

- Cómo Hacer La Copia de Seguridad de Un DongleDocument12 pagesCómo Hacer La Copia de Seguridad de Un DongleKimberlyMichelleHernandezAndresPas encore d'évaluation

- Adobe AcrobatDocument463 pagesAdobe AcrobatJosé Manuel Hita SeguraPas encore d'évaluation

- Hoja de Vida Maria Camila Leon Bertel PDFDocument4 pagesHoja de Vida Maria Camila Leon Bertel PDFCamii LeonPas encore d'évaluation

- 1392 Guia Intro Econometria Con GretlDocument166 pages1392 Guia Intro Econometria Con Gretlcova5609Pas encore d'évaluation

- TallerDocument3 pagesTallerNATHALIA ARROYO OCHOAPas encore d'évaluation

- Notas AVR Maestría Parte2Document147 pagesNotas AVR Maestría Parte2Seminario InvestigaciónPas encore d'évaluation

- Introduccion Metodos Numericos - Diego GonzalezDocument1 pageIntroduccion Metodos Numericos - Diego GonzalezDiego GonzalezPas encore d'évaluation

- Daniel Parra, Informe Expositivo, Suamtiva 2, Estadistica T1Document11 pagesDaniel Parra, Informe Expositivo, Suamtiva 2, Estadistica T1DanielPas encore d'évaluation

- Medidas de AlmacenamientoDocument2 pagesMedidas de AlmacenamientoCLAUDIA SALAS100% (1)

- Administración cadena abastecimiento FordDocument18 pagesAdministración cadena abastecimiento FordAlejandro Morales100% (2)

- Sistemas operativos, periféricos, formatos y procesosDocument5 pagesSistemas operativos, periféricos, formatos y procesosanthony0% (1)

- U1 Act3 Tabla Comparativa 1Document4 pagesU1 Act3 Tabla Comparativa 1Quirino Vidales GonzalezPas encore d'évaluation

- MVII - Simulación de Procesos (Compatibility Mode)Document103 pagesMVII - Simulación de Procesos (Compatibility Mode)Ele BaDoPas encore d'évaluation

- 9.1base de Datos de RiesgosDocument2 pages9.1base de Datos de RiesgosJosemanuel MartinezPas encore d'évaluation

- Superintendencia Financiera de Colombia: Radicación:2020281327-014-000Document3 pagesSuperintendencia Financiera de Colombia: Radicación:2020281327-014-000cristina camargoPas encore d'évaluation

- Ug Dialog4422 BP EsDocument114 pagesUg Dialog4422 BP EsPerico PalotesPas encore d'évaluation

- Lista de Insumos StocDocument5 pagesLista de Insumos StocTerry gutierresPas encore d'évaluation

- (PLICÓMETRO PROFESIONAL Y CINTA MÉTRICA ANATÓMICA) - Medidor de Grasa Corporal PRO y Cinta Corporal - Incluye Software GRATIS, VÍDocument1 page(PLICÓMETRO PROFESIONAL Y CINTA MÉTRICA ANATÓMICA) - Medidor de Grasa Corporal PRO y Cinta Corporal - Incluye Software GRATIS, VÍJose Gonzalez perezPas encore d'évaluation

- Tarea1 Investigacion Programacion 2Document8 pagesTarea1 Investigacion Programacion 2DavielPas encore d'évaluation