Académique Documents

Professionnel Documents

Culture Documents

Nand Gate

Transféré par

Neeraj Sharma0 évaluation0% ont trouvé ce document utile (0 vote)

571 vues5 pagesPhysics Project Class 12

Titre original

NAND GATE

Copyright

© © All Rights Reserved

Formats disponibles

DOC, PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentPhysics Project Class 12

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme DOC, PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

571 vues5 pagesNand Gate

Transféré par

Neeraj SharmaPhysics Project Class 12

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme DOC, PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 5

NAND GATE

NAND logic table

Input

Output

A B

0 0 1

0 1 1

1 0 1

1 1 0

The TTL 7400 chip, containing four NANDs. The two additional

pins supply power (! "# and connect the ground in digital

electronics, a NAND gate (Negated AND or NOT AND# is a logic

gate which produces an output that is false only if all its inputs are

true. A L$% (0# output results only if &oth the inputs to the gate

are '()' (1#* if one or &oth inputs are L$% (0#, a '()' (1#

output results. (t is +ade using transistors.

The NAND gate is significant &ecause any &oolean function can

&e i+ple+ented &y using a co+&ination of NAND gates. This

property is called functional co+pleteness.

Digital syste+s e+ploying certain logic circuits ta,e ad-antage of

NAND.s functional co+pleteness. (n co+plicated logical

e/pressions, nor+ally written in ter+s of other logic functions

such as AND, $0, and N$T, writing these in ter+s of NAND

sa-es on cost, &ecause i+ple+enting such circuits using NAND

gate yields a +ore co+pact result than the alternati-es.

112

The function NAND (a

1

, a

3

,..., a

n

# is logically e4ui-alent to N$T

(a

1

AND a

3

AND ... AND a

n

#.

Symbols

There are three sy+&ols for NAND gates5 the .distincti-e.

(6(L7AN8(# sy+&ol and the .rectangular. (9: sy+&ol, as well as a

deprecatedD(N sy+&ol so+eti+es found on old sche+atics. ;or

+ore infor+ation see logic gate sy+&ols.

MIL/ANSI Symbol IEC Symbol DIN Symbol

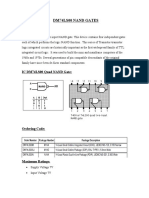

Hardware description and pinout

NAND gates are &asic logic gates, and as such they are

recognised in TTL and :6$8 (:s.

This sche+atic diagra+ shows the arrange+ent of NAND gates

within a standard 4011 :6$8 integrated circuit.

CMOS version

The standard, 4000 series, :6$8 (: is the 4011, which includes

four independent, two<input, NAND gates.

Availability

These de-ices are a-aila&le fro+ +ost se+iconductor

+anufacturers such as ;airchild 8e+iconductor, =hilips or Te/as

(nstru+ents. These are usually a-aila&le in &oth through<

hole D(L and 8$(: for+at. Datasheets are readily a-aila&le in

+ost datasheet data&ases.

The standard 3<, ><, 4< and ?<input NAND gates are a-aila&le5

:6$8

40115 @uad 3<input NAND gate

403>5 Triple ><input NAND gate

40135 Dual 4<input NAND gate

40A?5 6ono ?<input NAND gate

TTL

74005 @uad 3<input NAND gate

74105 Triple ><input NAND gate

74305 Dual 4<input NAND gate

74>05 6ono ?<input NAND gate

Implementations

The NAND gate has the property of functional co+pleteness. That

is, any other logic function (AND, $0, etc.# can

&e i+ple+ented using only NAND gates. An entire processor can

&e created using NAND gates alone. (n TTL (:s using +ultiple<

e+itter transistors, it also re4uires fewer transistors than a N$0

gate.

N6$8 NAND gate

:6$8 NAND gate TTL NAND gate

The physical layout of a :6$8 NAND

Vous aimerez peut-être aussi

- Propositional Logic Connectives SentencesDocument15 pagesPropositional Logic Connectives SentencesNavdeep JimmyPas encore d'évaluation

- 1.verification of Basic Logic GatesDocument7 pages1.verification of Basic Logic GatesVijay M0% (1)

- Business Ethics and Corporate GovernanceDocument29 pagesBusiness Ethics and Corporate GovernanceNeeraj SharmaPas encore d'évaluation

- Countdown Timer Documentation - Logic Circuit ProjectDocument32 pagesCountdown Timer Documentation - Logic Circuit Projectrpc_3100% (2)

- Experiment No.1 Aim: Objective:: Not Gate: IC 7404 (HEX Inverter) 14 Pin Supply Voltage:5vDocument10 pagesExperiment No.1 Aim: Objective:: Not Gate: IC 7404 (HEX Inverter) 14 Pin Supply Voltage:5vCharanpreet SinghPas encore d'évaluation

- The Logic Gates and Its Combinations.02Document17 pagesThe Logic Gates and Its Combinations.02Ajay SuppalPas encore d'évaluation

- CELL CULTURE: GROWING CELLS OUTSIDE THE BODYDocument8 pagesCELL CULTURE: GROWING CELLS OUTSIDE THE BODYNeeraj SharmaPas encore d'évaluation

- Expt 4 Truth Table Verification of Logic GatesDocument5 pagesExpt 4 Truth Table Verification of Logic GatesSwapnil Babele100% (1)

- DLD Notes SummaryDocument7 pagesDLD Notes SummaryProgrammer Beats (KalimUllahkhan)Pas encore d'évaluation

- Digital Logic Design Lab Manual Assignment 1Document13 pagesDigital Logic Design Lab Manual Assignment 1Pirzada SwatiPas encore d'évaluation

- Digital Electronics 3rd SemDocument39 pagesDigital Electronics 3rd SemPriyanshu ThawaitPas encore d'évaluation

- LAB MANUAL EXPERIMENTSDocument61 pagesLAB MANUAL EXPERIMENTSKhurshid AlamPas encore d'évaluation

- Co Lab Manual 1Document72 pagesCo Lab Manual 1Hafza GhafoorPas encore d'évaluation

- Interfacing With The ISA BusDocument12 pagesInterfacing With The ISA BusseyfiPas encore d'évaluation

- Digital Logic DesignDocument55 pagesDigital Logic DesignAditya GadgilPas encore d'évaluation

- Elec 2210 - Experiment 1 Basic Digital Logic Circuits: ObjectivesDocument5 pagesElec 2210 - Experiment 1 Basic Digital Logic Circuits: ObjectivesSameer IbrahimPas encore d'évaluation

- Digital Logic Fundamentals for ElectronicsDocument25 pagesDigital Logic Fundamentals for ElectronicsYadana1Pas encore d'évaluation

- DE EXP ListsDocument34 pagesDE EXP Liststixel62099Pas encore d'évaluation

- Assignment #02: Name: - Ahmad Raza 20-ARID-1665 Section: - BSCS 2 (A) Course: - Digital Logic & DesignDocument28 pagesAssignment #02: Name: - Ahmad Raza 20-ARID-1665 Section: - BSCS 2 (A) Course: - Digital Logic & DesignAhmad RazaPas encore d'évaluation

- De Lab PDFDocument36 pagesDe Lab PDFNaveen Yallapu100% (1)

- VERIFICATION OF TRUTH TABLES OF LOGIC GATES AND CIRCUITSDocument40 pagesVERIFICATION OF TRUTH TABLES OF LOGIC GATES AND CIRCUITSRockRahil100% (3)

- Chapter 11Document40 pagesChapter 11sandeep4672kvkPas encore d'évaluation

- Ecad & Vlsi Lab Manual - MrecwDocument104 pagesEcad & Vlsi Lab Manual - Mrecwvaseem_ahmedPas encore d'évaluation

- Lab Mannual For Digital Electronics LabDocument35 pagesLab Mannual For Digital Electronics LabSia ghoshPas encore d'évaluation

- Fundamentals of Digital Computers: Unit - IiDocument42 pagesFundamentals of Digital Computers: Unit - IirajagopalPas encore d'évaluation

- Experiment: Verification and Interpretation of Truth Table For AND, OR, NOT, NAND, NOR, Ex-OR, Ex-NOR GatesDocument42 pagesExperiment: Verification and Interpretation of Truth Table For AND, OR, NOT, NAND, NOR, Ex-OR, Ex-NOR GatesMAYANKPas encore d'évaluation

- VHDL ExperimentsDocument55 pagesVHDL Experimentssandeepsingh93Pas encore d'évaluation

- Synthesizing Combinational Logic Circuits: Laboratory Experiment No. 4Document8 pagesSynthesizing Combinational Logic Circuits: Laboratory Experiment No. 4DervPas encore d'évaluation

- DE LAB ManualC-18 FinalDocument85 pagesDE LAB ManualC-18 FinalBRAGPW,Karimnagar 087Pas encore d'évaluation

- PLDTUTORDocument13 pagesPLDTUTORAjay Nath S APas encore d'évaluation

- Logic GatesDocument8 pagesLogic GatesPaul Justine Ruelson MeriolesPas encore d'évaluation

- ArduinoDocument44 pagesArduinojocansino4496Pas encore d'évaluation

- Chapter 1: Digital Logic: I. OverviewDocument10 pagesChapter 1: Digital Logic: I. OverviewNihalPas encore d'évaluation

- Effective Study MaterialDocument74 pagesEffective Study MaterialSanthosh AnantharamanPas encore d'évaluation

- Logic DesignDocument4 pagesLogic DesignRoshan AjithPas encore d'évaluation

- Basic GateDocument5 pagesBasic Gatemsjunaid02Pas encore d'évaluation

- Logic Gates: DIET-Dept of ECEDocument7 pagesLogic Gates: DIET-Dept of ECESaurav SarkarPas encore d'évaluation

- De Lab Manual 21-22Document46 pagesDe Lab Manual 21-22AUTHOR SOULPas encore d'évaluation

- Computer HardwareDocument47 pagesComputer HardwareLaura SaparkhanPas encore d'évaluation

- Lab 1: Binary Numbers and Logic GatesDocument4 pagesLab 1: Binary Numbers and Logic GatesFatmir KelmendiPas encore d'évaluation

- De ManualDocument56 pagesDe ManualBhuvanesh Kakarla AP21110010593Pas encore d'évaluation

- LED Chaser Speed Control with Arduino & PotentiometerDocument3 pagesLED Chaser Speed Control with Arduino & PotentiometeraiiiiidPas encore d'évaluation

- Aim-Verifying Logic Gates Using Digital Trainer Kit.: TheoryDocument5 pagesAim-Verifying Logic Gates Using Digital Trainer Kit.: TheorySachin PatilPas encore d'évaluation

- DE Lab EXP.1,2,3Document18 pagesDE Lab EXP.1,2,3Saksham DhawanPas encore d'évaluation

- Experiment No.1 Digital Logic Gates Familirization: I. ObjectivesDocument8 pagesExperiment No.1 Digital Logic Gates Familirization: I. ObjectivesJun TobiasPas encore d'évaluation

- Vlsi LabDocument57 pagesVlsi LabsasdikaPas encore d'évaluation

- ENGI 3861 - Digital Logic: Introduction - 1Document15 pagesENGI 3861 - Digital Logic: Introduction - 1omgcharlie12Pas encore d'évaluation

- Lab FlipflopsDocument71 pagesLab FlipflopsDani Raj100% (1)

- This Article Is On Reaching PortsDocument9 pagesThis Article Is On Reaching PortsNipurba KonarPas encore d'évaluation

- Introduction To Basic Gates and FunctionsDocument20 pagesIntroduction To Basic Gates and FunctionsMs. Betsybha Evangeline S.Pas encore d'évaluation

- DC Lab ManualDocument71 pagesDC Lab ManualVishal NairPas encore d'évaluation

- Unit 2Document56 pagesUnit 2kaustubhPas encore d'évaluation

- STLD Lab 2-1Document44 pagesSTLD Lab 2-1penumallu srinivasa reddyPas encore d'évaluation

- 7400 Nand GatesDocument4 pages7400 Nand Gatessrc e-solutionsPas encore d'évaluation

- Project Ideas: 1. What Is A PLD?Document27 pagesProject Ideas: 1. What Is A PLD?محمد فصیح آفتابPas encore d'évaluation

- Assignment 1Document12 pagesAssignment 1abuzarkazmi779Pas encore d'évaluation

- Cs8382 Digital Manual PrintDocument47 pagesCs8382 Digital Manual PrintSaravana kumarPas encore d'évaluation

- List of Experiments: SR. NO. Name of Experiment NODocument40 pagesList of Experiments: SR. NO. Name of Experiment NOSourabh BARIKPas encore d'évaluation

- STLD Lab Manual ExperimentsDocument42 pagesSTLD Lab Manual ExperimentssaikiranPas encore d'évaluation

- Business Ethics: Prepared By: Jyoti Bala ROLL NO. 1563 M. COM. (1 Sem)Document9 pagesBusiness Ethics: Prepared By: Jyoti Bala ROLL NO. 1563 M. COM. (1 Sem)Neeraj SharmaPas encore d'évaluation

- Biology 1Document5 pagesBiology 1ayushkrishnanPas encore d'évaluation

- CDocument16 pagesCNeeraj SharmaPas encore d'évaluation

- AdulterantsDocument7 pagesAdulterantsNeeraj SharmaPas encore d'évaluation

- Jammu & Kashmir BankDocument107 pagesJammu & Kashmir BankNeeraj SharmaPas encore d'évaluation

- DiwaliDocument11 pagesDiwaliNeeraj SharmaPas encore d'évaluation

- HTML ProjectDocument16 pagesHTML ProjectNeeraj SharmaPas encore d'évaluation

- DiwaliDocument11 pagesDiwaliNeeraj SharmaPas encore d'évaluation

- Financial AdvisorDocument4 pagesFinancial Advisorzywang wangPas encore d'évaluation

- Artificial Intelligence Knowledge Representation Lecture 05Document22 pagesArtificial Intelligence Knowledge Representation Lecture 05Shut UpPas encore d'évaluation

- Daa Regular Practical Workbook FinalDocument126 pagesDaa Regular Practical Workbook FinalOppo HousePas encore d'évaluation

- Unit 3Document106 pagesUnit 3A Good YoutuberPas encore d'évaluation

- Algorithms Solution - 2Document9 pagesAlgorithms Solution - 2MiltonPas encore d'évaluation

- Data Structures CourseDocument3 pagesData Structures CoursehaseenaPas encore d'évaluation

- Equivalence Class: Set or The Quotient Space ofDocument5 pagesEquivalence Class: Set or The Quotient Space ofTim VermeersPas encore d'évaluation

- Recursive TypesDocument23 pagesRecursive TypesYuyun JoePas encore d'évaluation

- MultiplexerDocument11 pagesMultiplexerSeashells Do ImpossiblePas encore d'évaluation

- MATH 240 NotesDocument51 pagesMATH 240 NotesSaeclusPas encore d'évaluation

- Basic Analysis: Introduction To Real AnalysisDocument161 pagesBasic Analysis: Introduction To Real AnalysisĐỗ DươngPas encore d'évaluation

- An Introduction To Kolmogorov Complexity and Its ADocument31 pagesAn Introduction To Kolmogorov Complexity and Its ANikhil VasanPas encore d'évaluation

- MATH7 Week1Document5 pagesMATH7 Week1Kalia SharPas encore d'évaluation

- AristotlesSyllogistic JanLukasiewiczDocument119 pagesAristotlesSyllogistic JanLukasiewiczCarlos Eduardo Correa RoquePas encore d'évaluation

- Laws of Boolean AlgebraDocument22 pagesLaws of Boolean AlgebraRoy Vera CruzPas encore d'évaluation

- CSC312 Automata Theory Languages: Lecture # 2Document50 pagesCSC312 Automata Theory Languages: Lecture # 2NABEEL AHMADPas encore d'évaluation

- Boolean Algebra Applications (Reliability of Circuits)Document62 pagesBoolean Algebra Applications (Reliability of Circuits)EmadPas encore d'évaluation

- MylehillDocument11 pagesMylehillArjun SinghPas encore d'évaluation

- EE351Chap3-2.0 - Transfer FTN & SFGsDocument19 pagesEE351Chap3-2.0 - Transfer FTN & SFGsSardar Hamid ullahPas encore d'évaluation

- FAL (2022-23) STS3006 TH AP2022232000027 Reference Material I 08-Nov-2022 L-7 ArraysDocument15 pagesFAL (2022-23) STS3006 TH AP2022232000027 Reference Material I 08-Nov-2022 L-7 ArraysBodagala RamadeviPas encore d'évaluation

- Fuzzy SetDocument13 pagesFuzzy SetSoumya PaikPas encore d'évaluation

- Theory of Automata Assignment 1Document3 pagesTheory of Automata Assignment 1Tooba Hassan 364-FSS/BSIAA/F19Pas encore d'évaluation

- Lecture 03 Relational ALgebra and Relational CalculusDocument45 pagesLecture 03 Relational ALgebra and Relational CalculusTrịnh Thái TuấnPas encore d'évaluation

- Simple Search Algorithm: S Q Q (S) Visited (S) Q X Q X X X Q X Visited Q XDocument36 pagesSimple Search Algorithm: S Q Q (S) Visited (S) Q X Q X X X Q X Visited Q XfarazPas encore d'évaluation

- Here are the solutions:A. 1. False 2. True3. True4. TrueB. See attached truth tablesDocument45 pagesHere are the solutions:A. 1. False 2. True3. True4. TrueB. See attached truth tablesKreal VilePas encore d'évaluation

- Introduction to Automata Theory, Languages, and ComputationDocument9 pagesIntroduction to Automata Theory, Languages, and ComputationGautam KumarPas encore d'évaluation

- Math8 q3 Mod1Document18 pagesMath8 q3 Mod1Kirby DiazPas encore d'évaluation

- 03-Operators in CDocument5 pages03-Operators in CRekha V RPas encore d'évaluation

- Lecture 011 - Logic ImplementationDocument18 pagesLecture 011 - Logic ImplementationAnurag DubeyPas encore d'évaluation