Académique Documents

Professionnel Documents

Culture Documents

Bie Stables

Transféré par

Alexis ChafloqueCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Bie Stables

Transféré par

Alexis ChafloqueDroits d'auteur :

Formats disponibles

Flip flop

Los flip flop son dispositivos sncronos de dos estados (estado alto o

estado bajo), tambin conocidos como multivibradores biestables. La

salida de estado cambia de manera sincronizada con el pulso de reloj.

Un flip flop de disparo por flanco cambia de estado cambia de estado

don el flanco positivo (flanco de subida) o con el flanco negativo

(flanco de bajada) del impulso de reloj y solo es sensible a sus

entrada solo en esa transicin del reloj.

Detector de flancos

Los Flip-Flop son unidades bsicas de todos

los sistemas secuenciales, existen cuatro tipos: el SR, el JK, el T y el

D. Y los ltimos tres son implementados a partir del primero.

Tipos de Flip Flop:

Biestable RS:

Dispositivo de almacenamiento temporal de 2 estados (alto y bajo), cuyas

entradas principales permiten al ser activadas:

R: el borrado (reset en ingls), puesta a 0 nivel bajo de la salida.

S: el grabado (set en ingls), puesta a 1 nivel alto de la salida.

Adems de las entradas R y S, posee una entrada C de sincronismo cuya

misin es la de permitir o no el cambio de estado del biestable. En la siguiente

figura se muestra un ejemplo de un biestable sncrono a partir de una

asncrona, junto con su esquema normalizado:

Su tabla de verdad es la siguiente:

Tabla de verdad biestable RS

C R S Q (NOR)

0 X X Q

1 0 0 Q

1 0 1 1

1 1 0 0

1 1 1 N. D.

X=no importa

Biestable D (Data o Delay)[editar]

Smbolos normalizados: Biestables D a) activo por nivel alto y b) activo por

flanco de subida.

El flip-flop D resulta muy til cuando se necesita almacenar un nico bit de

datos (1 o 0). Si se aade un inversor a un flip-flop S-R obtenemos un flip-flop

D bsico. El funcionamiento de un dispositivo activado por el flanco negativo

es, por supuesto, idntico, excepto que el disparo tiene lugar en el flanco de

bajada del impulso del reloj. Recuerde que Q sigue a D en cada flanco del

impulso de reloj.

Para ello, el dispositivo de almacenamiento temporal es de dos estados (alto y

bajo), cuya salida adquiere el valor de la entrada D cuando se activa la entrada

de sincronismo, C. En funcin del modo de activacin de dicha entrada de

sincronismo, existen dos tipos:

Activo por nivel (alto o bajo), tambin denominado registro o cerrojo

(latch en ingls).

Activo por flanco (de subida o de bajada).

La ecuacin caracterstica del biestable D que describe su comportamiento es:

y su tabla de verdad:

D Q Q

siguiente

0 X 0

1 X 1

X=no importa

Biestable T (Toggle)[editar]

Smbolo normalizado: Biestable T activo por flanco de subida.

Dispositivo de almacenamiento temporal de 2 estados (alto y bajo). El biestable

T cambia de estado ("toggle" en ingls) cada vez que la entrada de sincronismo

o de reloj se dispara mientras la entrada T est a nivel alto. Si la entrada T est

a nivel bajo, el biestable retiene el nivel previo. Puede obtenerse al unir las

entradas de control de unbiestable JK, unin que se corresponde a la entrada

T. No estn disponibles comercialmente.

La ecuacin caracterstica del biestable T que describe su comportamiento es:

y la tabla de verdad:

T Q Q

siguiente

0 0 0

0 1 1

1 0 1

1 1 0

Biestable JK[editar]

Es verstil y es uno de los tipos de flip-flop ms usados. Su funcionamiento es

idntico al del flip-flop S-R en las condiciones SET, RESET y de permanencia

de estado. La diferencia est en que el flip-flop J-K no tiene condiciones no

vlidas como ocurre en el S-R.

Este dispositivo de almacenamiento es temporal que se encuentra dos estados

(alto y bajo), cuyas entradas principales, J y K, a las que debe el nombre,

permiten al ser activadas:

J: El grabado (set en ingls), puesta a 1 nivel alto de la salida.

K: El borrado (reset en ingls), puesta a 0 nivel bajo de la salida.

Si no se activa ninguna de las entradas, el biestable permanece en el estado

que posea tras la ltima operacin de borrado o grabado. A diferencia

del biestable RS, en el caso de activarse ambas entradas a la vez, la salida

adquirir el estado contrario al que tena.

La ecuacin caracterstica del biestable JK que describe su comportamiento es:

Y su tabla de verdad es:

J K Q Q

siguiente

0 0 0 0

0 0 1 1

0 1 X 0

1 0 X 1

1 1 0 1

1 1 1 0

X=no importa

Una forma ms compacta de la tabla de verdad es (Q representa el estado

siguiente de la salida en el prximo flanco de reloj y q el estado actual):

J K Q

0 0 q

0 1 0

1 0 1

1 1

El biestable se denomina as por Jack Kilby, el inventor de los circuitos

integrados en 1958, por lo cual se le concedi el Premio Nobel en fsica

de 2000.

Biestable JK activo por flanco[editar]

Smbolos normalizados: Biestables JK activo a) por flanco de subida y b) por

flanco de bajada

Junto con las entradas J y K existe una entrada C de sincronismo o de reloj

cuya misin es la de permitir el cambio de estado del biestable cuando se

produce un flanco de subida o de bajada, segn sea su diseo. Su

denominacin en ingls es J-K Flip-Flop Edge-Triggered. De acuerdo con la

tabla de verdad, cuando las entradas J y K estn a nivel lgico 1, a cada flanco

activo en la entrada de reloj, la salida del biestable cambia de estado. A este

modo de funcionamiento se le denomina modo de basculacin (toggle en

ingls).

Ejemplo: 74LS73

Biestable JK Maestro-Esclavo[editar]

Smbolos normalizados: Biestable JK Maestro-Esclavo a) activo por nivel alto y

b) activo por nivel bajo

Aunque an puede encontrarse en algunos equipos, este tipo de biestable,

denominado en ingls J-K Flip-Flop Master-Slave, ha quedado obsoleto ya que

ha sido reemplazado por el tipo anterior.

Su funcionamiento es similar al JK activo por flanco: en el nivel alto (o bajo) se

toman los valores de las entradas J y K y en el flanco de bajada (o de subida)

se refleja en la salida.

Otra forma de expresar la tabla de verdad del biestable JK es mediante la

denominada tabla de excitacin:

q Q J K

0 0 0 X

0 1 1 X

1 0 X 1

1 1 X 0

Siendo q el estado presente y Q el estado siguiente.

La ecuacin caracterstica del flip flop jk es: Q(t+1)=JQ+KQ la cual se obtiene

de la tabla caracterstica del flip flop.

Latch:

El latch o cerrojo es un dispositivo lgico capaz de almacenar temporalmente

dos estados debido a su sistema de realimentacin.

O mas extensamente podemos decir de los latch (lat memori inglet) es

un circuito electrnico usado para almacenar informacin en sistemas lgicos

asncronos. Un latch puede almacenar un bit de informacin. Los latches se

pueden agrupar, algunos de estos grupos tienen nombres especiales, como por

ejemplo el 'latch quad ' (que puede almacenar cuatro bits) y el 'latch octal' (ocho

bits). Los latches pueden ser dispositivosbiestables asncronos que no tienen

entrada de reloj y cambian el estado de salida solo en respuesta a datos de

entrada, o bien biestables sncronos por nivel, que cuando tienen datos de

entrada, cambian el estado de salida slo si lo permite una entrada de reloj.

El latch mas simple que tenemos es:

Latch RS[editar]

Los latches a diferencia de los conectores no necesitan una seal de reloj para

su funcionamiento.

RS latch.

El latch lgico ms simple es el RS, donde R y S permanecen en estado 'reset'

y 'set'. El latch es construido mediante la interconexin retroalimentada

depuertas lgicas NOR (negativo OR), o bien de puertas

lgicas NAND (aunque en este caso la tabla de verdad tiene salida en lgica

negativa para evitar la incongruencia de los datos). El bit almacenado est

presente en la salida marcada como Q.

Se pueden dar las siguientes combinaciones de entrada: set a 1 y reset a 0

(estado 'set'), en cuyo caso la salida Q pasa a valer 1; set a 0 y reset a 0

(estado 'hold'), que mantiene la salida que tuviera anteriormente el sistema; set

a 0 y reset a 1 (estado 'reset'), en cuyo caso la salida Q pasa a valer 0; y

finalmente set a 1 y reset a 1, que es un estado indeseado en los biestables de

tipo RS, pues provoca oscilaciones que hacen imposible determinar el estado

de salida Q.

Esta situacin indeseada se soluciona con los biestables tipo JK, donde se

aade un nivel ms de retroalimentacin al circuito, logrando que dicha entrada

haga conmutar a las salidas, denominndose estado de 'toggle'.

Set Reset Q

1 0 1

0 0 Q

n

1

0 1 0

1 1 X

GENERADOR DE PULSOS

1.- DEFINICION

Los generadores de pulsos ofrecen pulsos o trenes de pulsos de tensin o de

corriente (para transformadores de pulsos y otros circuitos magnticos), no

como salida secundaria como ofrecen otros generadores, sino como salida

fundamental, y a veces nica.

2.- PULSO

Un pulso es una seal que pasa de un nivel inicial a otro final en un intervalo

finito de tiempo y luego retorna al nivel inicial en otro tiempo finito igual o

distinto. Los principales parmetros que definen un pulso son:

-la amplitud y polaridad.

-El tiempo de subida, BD, (del 10% al 90% de la amplitud) (rise time), en el

flanco anterior o ascendente, AE.

-el tiempo de bajada, GI, (del 90% al 10% de la amplitud) (fall time), en el flanco

posterior, FJ.

-la duracin, CH, (entre los niveles del 50%de la amplitud) o anchura del pulso.

-el periodo del pulso, AA, que coincide con el reciproco de la frecuencia de

repeticin si es una seal peridica.

-el retardo respecto a una referencia, que es el tiempo desde dicha referencia

hasta C.

10

El tiempo de subida y el de bajada se denominan tiempos de transicin, y

pueden ser mucho mas cortos que los de la seal cuadrada que ofrecen los

generadores de funciones simples. Hay otros parmetros secundarios, como lo

son el sobrepasamiento, que es la amplitud por encima del valor final, y el

tiempo de establecimiento (hasta que la amplitud quede dentro de un intervalo

predefinido).

Los pulsos se emplean como estimulo o entrada para un sistema cuya

respuesta se observa luego en un osciloscopio. Se pueden medir as

parmetros de circuitos digitales tales como el tiempo e conmutacin., el

tiempo de propagacin, el tiempo de retardo, el tiempo de recuperacin, etc. Y

tambin se pueden obtener los datos equivalentes a la respuesta en

frecuencia.

Los denominados generadores de datos (o palabras digitales) generan trenes

de pulsos que simulan informacin o datos digitales.

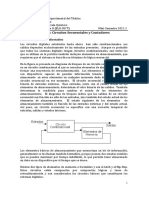

3.- ESQUEMA FUCIONAL

La figura 4.11 muestra el esquema de bloques funcional de un generador de

pulsos. La seal cuadrada, procedente de un oscilador, pasa sucesivamente

por dos monoestables que determinan su retardo (respecto a una seal de

sincronismo, que se ofrece como salida) y su duracin. Un integrador posterior

determina los tiempos de transicin, mientras que un recortador y un

amplificador final determinan las caractersticas de salida; amplitud, polaridad, y

lnea de base (nivel de continua).

La accin de los monoestables y el integrador sobre la seal del oscilador se

muestra en la figura 4.12. Obviamente, los tiempos de transicin no son

11

instantneos tal como lo aparecen en las seales de control, pero se muestran

as para destacar la funcin de cada etapa.

Los pulsos dobles son interesantes para medir la velocidad de recuperacin de

circuitos. Se obtienen haciendo que el monoestable que determina la duracin

sea disparado no solo por el flanco posterior del pulso que sale del

monoestable que determina el retardo, sino tambin por el flanco anterior de la

seal del oscilador.

Los controles disponibles normalmente permiten ajustar: el periodo de repeticin,

entre 10mHz y 660mHz o ms; la duracin, desde menos de 2 ns hasta 10-4 s; el

retardo, respecto a la seal de sincronismo; los tiempos de transicin (permiten

generar desde seales triangulares hasta trapezoidales); la

amplitud, que normalmente es de 20 V en circuito abierto 10 V para una carga

adaptada (50); la polaridad; y la lnea de base.

Algunas opciones adicionales son: pulsos complementarios; salidas co

amplitud fija (TTL, ECL, CMOS,...); funcionamiento en ciclo nico, o con

disparo externo (sncrono o asncrono), y determinacin externa de la duracin.

Timer 555:

El dispositivo 555 es un circuito integrado muy estable cuya funcin primordial es la de

producir pulsos de temporizacin con una gran precisin y que, adems, puede

funcionar como oscilador.

Sus caractersticas ms destacables son:

Temporizacin desde microsegundos hasta horas.

Modos de funcionamiento:

o Monoestable.

o Astable.

aplicaciones,

tales como:

Control de sistemas secuenciales,

Generacin de tiempos de retraso,

Divisor de frecuencias,

Modulacin por anchura de pulsos,

Repeticin de pulsos,

Generacin de pulsos controlados por tensin, etc.

Configuracin de pines

Se puede ver de la figura que independientemente del tipo de encapsulado la

numeracin de las pines es la misma.

Descripcin de las pines del 555

1 Tierra o masa: ( Ground ) Conexin a tierra del circuito en general.

2 Disparo: ( Trigger ) Es en esta patilla, donde se establece el inicio del tiempo de

retardo, si el 555 es configurado como monostable. Este proceso de disparo ocurre

cuando este pin va por debajo del nivel de 1/3 del voltaje de alimentacin. Este pulso

debe ser de corta duracin, pues si se mantiene bajo por mucho tiempo la salida se

quedar en alto hasta que la entrada de disparo pase a alto otra vez.

3 Salida: ( Output ) Aqu veremos el resultado de la operacin del temporizador, ya sea

que este conectado como monostable, astable u otro. Cuando la salida es alta, el

voltaje ser el voltaje de aplicacin (Vcc) menos 1.7 Voltios. Esta salida se puede

obligar a estar en casi 0 voltios con la ayuda de la patilla # 4 (reset) 4 Reset: Si se pone

a un nivel por debajo de 0.7 Voltios, pone la patilla de salida # 3 a nivel bajo. Si por

algn motivo esta patilla no se utiliza hay que conectarla a Vcc paraevitar que el 555 se

"resetee"

5 Control de voltaje: ( Control ) Cuando el temporizador se utiliza en el modo de

controlador de voltaje, el voltaje en esta patilla puede variar casi desde Vcc (en la

practica como Vcc -1 voltio) hasta casi 0 V (aprox. 2 Voltios ). As es posible modificar

los tiempos en que la patilla # 3 esta en alto o en bajo independiente del diseo

(establecido por las resistencias y condensadores conectados externamente al 555) . El

voltaje aplicado a la patilla # 5 puede variar entre un 45 y un 90 % de Vcc en la

configuracin monostable.

Cuando se utiliza la configuracin astable, el voltaje puede variar desde 1.7 voltios

hasta Vcc. Modificando el voltaje en esta patilla en la configuracin astable causar la

frecuencia original del astable sea modulada en frecuencia (FM). Si esta patilla no se

utiliza, se recomienda ponerle un capacitor de 0.01uF para evitar las interferencias

6 Umbral: ( Threshold) Es una entrada a un comparador interno que tiene el 555 y se

utiliza para poner la salida (Pin # 3) a nivel bajo bajo

7 Descarga: ( Discharge ) Utilizado para descargar con efectividad el condensador

externo utilizado por el temporizador para su funcionamiento.

8 V+: Tambin llamado Vcc, es el pin donde se conecta el voltaje de alimentacin que

va de 4.5 voltios hasta 16 voltios (mximo). Hay versiones militares de este integrado

que llegan hasta 18 Voltios

Multivibrador astable:

Este tipo de funcionamiento se caracteriza por una salida con forma de onda cuadrada

(o rectangular) continua de ancho predefinido por el diseadordel circuito. El esquema

de conexin e s el que se muestra. La seal, de salida tiene un nivel alto por un tiempo

T1 y en un nivel bajo un tiempo T2. Los tiempos de duracin dependen de los valores

de R1 y R2.

T1 = 0.693(R1+R2)C1 (seg) y T2 = 0.693 x R2 x C1 (seg)

Multivibrador Monostable:

En este caso el circuito entrega a su salida un slo pulso de un ancho establecido por el

diseador (tiempo de duracin). El esquema de conexin es el que se muestra. La

Frmula para calcular el tiempo de duracin (tiempo que la salida esta en nivel alto)

es: T = 1.1 x R1 x C1 (en segundos). Observa que es necesario que la seal de disparo,

sea de nivel bajo y de muy corta duracin en el PIN # 2 del C.I. para iniciar la seal de

salida.

Timer 556:

Este circuito integrado es un doble temporizador.

Descripcin de las terminales del Temporizador 556:

*Descarga 1(patilla 1): Utilizado para descargar con efectividad el condensador

externo utilizado por el temporizador para su funcionamiento.

*Umbral 1(patilla 2): Es una entrada a un comparador interno que tiene el 556

y se utiliza para poner la salida a nivel bajo.

*Control de voltaje 1(patilla 3): Cuando el temporizador se utiliza en el modo

de controlador de voltaje, el voltaje en esta patilla puede variar casi desde Vcc

(en la prctica como Vcc -1 voltio) hasta casi 0 V (aprox. 2 Voltios). As es

posible modificar los tiempos en que la salida est en alto o en bajo

independiente del diseo (establecido por los resistores y condensadores

conectados externamente al 556). El voltaje aplicado a la patilla de control de

voltaje puede variar entre un 45 y un 90 % de Vcc en la configuracin

monostable. Cuando se utiliza la configuracin astable, el voltaje puede variar

desde 1.7 voltios hasta Vcc. Modificando el voltaje en esta patilla en la

configuracin astable causar la frecuencia original del astable sea modulada en

frecuencia (FM). Si esta patilla no se utiliza, se recomienda ponerle un

condensador de 0.01F para evitar las interferencias.

*Reset 1 (patilla 4): Si se pone a un nivel por debajo de 0.7 Voltios, pone la

patilla de salida a nivel bajo. Si por algn motivo esta patilla no se utiliza hay

que conectarla a Vcc para evitar que el 556 se "resetee".

*Salida 1(patilla 5): Aqu veremos el resultado de la operacin del

temporizador, ya sea que est conectado como monostable, astable u otro.

Cuando la salida es alta, el voltaje ser el voltaje de alimentacin (Vcc) menos

1.7 Voltios. Esta salida se puede obligar a estar en casi 0 voltios con la ayuda de

la patilla de reset 1(normalmente la 4).

*Disparo 1(patilla 6): Es en esta patilla, donde se establece el inicio del tiempo

de retardo, si el 556 es configurado como monostable. Este proceso de disparo

ocurre cuando este pin va por debajo del nivel de 1/3 del voltaje de

alimentacin. Este pulso debe ser de corta duracin, pues si se mantiene bajo

por mucho tiempo la salida se quedar en alto hasta que la entrada de disparo

pase a alto otra vez.

*GND (patilla 7): es el polo negativo de la alimentacin, generalmente tierra.

**Disparo 2 :Patilla 8

**Salida 2 :Patilla 9

**Reset 2 :Patilla 10

**Control de voltaje 2:Patilla 11

**Humbral 2 :Patilla 12

**Descarga 2 :Patilla 13

*Vcc(Patilla 14):Alimentacin, es el pin donde se conecta el voltaje de

alimentacin que va de 4.5 voltios hasta 18 voltios (mximo). Hay versiones

militares de este integrado que llegan hasta 18 Voltios.

Integrados :

74ls123:

el 74123, son dos multivibradores monoestables, redisparables.

4047:

Bsicamente el Circuito Integrado CMOS CD4047 es un multivibrador que puede ser

utilizado como astable o monoestable. Para la implementacin de uno o de otro

circuito utiliza tan solo una capacidad con una resistencia, haciendo realmente sencillo

el clculo de la frecuencia de salida. El mismo posee tres salidas de frecuencia: la

frecuencia principal (pin 13) y dos salidas complementarias, una negada y la otra

normal, estas dos son divisores de frecuencias, es decir, son salidas equivalentes a la

mitad de la salida principal. La principal ventaja de este oscilador, es que su ciclo de

trabajo es constante del 50%, con una oscilacin muy estable. Admite un amplio rango

de tensiones de alimentacin desde 3 V hasta 15V y permite obtener frecuencias de

oscilacin de hasta 1 MHz.

Veamos el diagrama en bloques del circuito completo

Cristal de cuarzo.

Son componentes electrnicos utilizados en circuitos osciladores. Estos oscilan a una

frecuencia estable. Por lo que tienen una gran utilidad principalmente en la Electrnica

Digital y radiofrecuencia.

Caractersticas

En los cristales de cuarzo se produce un fenmeno llamado piezoelectricidad. Este

fenmeno consiste en que la aplicacin de una tensin elctrica produce una

deformacin del cristal, mientras que la deformacin del cristal genera una tensin

elctrica. Esta caracterstica se aprovecha en electrnica para producir tensiones alternas

con una gran estabilidad de frecuencia.

La frecuencia de oscilacin de un cristal viene determinada por el grueso de la lmina

de cuarzo y la direccin en que se dio el corte del cristal original para obtener la lmina.

Circuito RC

El texto que sigue es una traduccin defectuosa

o incompleta.

Si traducido|Circuito RC}} ~~~~

Circuito RC en configuracin paso bajo.

Un circuito RC es un circuito compuesto

de resistencias y condensadores alimentados por una fuente elctrica.

Un circuito RC de primer orden est compuesto de un resistor y un

condensador y es la forma ms simple de un circuito RC. Los circuitos RC

pueden usarse para filtrar una seal, al bloquear ciertas frecuencias y dejar

pasar otras. Los filtros RC ms comunes son el filtro paso alto, filtro paso

bajo, filtro paso banda, y el filtro elimina banda. Entre las caractersticas de los

circuitos RC est la propiedad de ser sistemas lineales e invariantes en el

tiempo; reciben el nombre de filtros debido a que son capaces de filtrar seales

elctricas de acuerdo a su frecuencia.

En la configuracin de paso bajo la seal de salida del circuito se coge en

bornes del condensador, estando este conectado en serie con la resistencia.

En cambio en la configuracin de paso alto la tensin de salida es la cada de

tensin en la resistencia.

Este mismo circuito tiene adems una utilidad de regulacin de tensin, y en tal

caso se encuentran configuraciones en paralelo de ambos, la resistencia y el

condensador, o alternativamente, como limitador de subidas y bajas bruscas de

tensin con una configuracin de ambos componentes en serie.

Registros:

Son dispositivos digitales donde se obtiene almacenamiento temporal.

Dado que la memoria y el desplazamiento de informacin son sus

caractersticas bsicas, los registros son circuitos secuenciales

constituidos por flip-flops, donde cada uno de ellos maneja un bit de la

palabra binaria. Registros de desplazamientos:

Un registro de desplazamiento es un circuito digital secuencial (es decir, que

los valores de sus salidas dependen de sus entradas y de los valores

anteriores) consistente en una serie de biestables, generalmente de tipo D,

conectados en cascada

Tipos de registros de desplazamiento[editar]

Dependiendo del tipo de entradas y salidas, los registros de desplazamiento se

clasifican como:

Serie-Serie: slo la entrada del primer flip-flop y la salida del ltimo son

accesibles externamente. Se emplean como lneas de retardo digitales y en

tareas de sincronizacin.

Paralelo-Serie: son accesibles las entradas de todos los flip-flops, pero

slo la salida del ltimo. Normalmente tambin existe una entrada serie,

que slo altera el contenido del primer flip-flop, pudiendo funcionar como los

del grupo anterior. Este tipo y el siguiente se emplean para convertir datos

serie en paralelo y viceversa.

Este tipo convierte: Dato en paralelo a dato en serie.

Serie-Paralelo: son accesibles las salidas de todos los flip-flops, pero slo

la entrada del primero. Este tipo y el anterior se emplean para convertir

datos serie en paralelo y viceversa, por ejemplo para conexiones serie

como el RS232.

Este tipo convierte: Dato en serie a dato en paralelo.

Paralelo-Paralelo: tanto las entradas como las salidas son accesibles. Se

usan para clculos aritmticos.

Un registro de desplazamiento muy utilizado, que es universal (se llama as

porque puede utilizarse en cualquiera de las cuatro configuraciones

anteriormente descritas) y bidireccional (porque puede desplazar los bits en un

sentido u otro) es el 74HC194, de cuatro bits de datos.

Otros registros de desplazamiento conocidos, fabricados tambin con la

tecnologa CMOS, son el 74HC165 (entrada paralelo, salida serie) y 74HC164

(entrada serie, salida paralelo).

Registro de almacenamiento:

Es un tema que interviene con la electronica digital y como su mismo nombre lo

indica son registos que almacenan informacion por medio de memoria,

generalmente biestables o flip-flops

como su nombre lo dice, son registro para almacenar datos de variables u otras

cosas que se necesita almacenar en un registro, es una posicin de memoria

Registro Universal palabras de 4 bits construido a base de cuatro comparadores de un

bit conectados en "cascada" Cerradura Codificada con Display sin Teclado: Una

cerradura elctrica codificada que emplea dos pulsadores para establecer el cdigo de

apertura (en lugar de un teclado) y un display que muestra la cantidad de veces que se

est presionando cada pulsador (un pulsador SW2, que define las unidades de cuenta y

otro SW1, que establece las decenas de cuenta) a 4 bits. El cdigo que debe ser

pulsado se fija por medio de llaves mini switch que se pueden colocar directamente en

la placa de circuito impreso o fuera de l.

Vous aimerez peut-être aussi

- CuadroMantenimientoPlantasElectricasDocument2 pagesCuadroMantenimientoPlantasElectricasChristian Gallegos OlaecheaPas encore d'évaluation

- Factor de PotenciaDocument20 pagesFactor de Potencia040457Pas encore d'évaluation

- 10 BiestablesDocument45 pages10 BiestablesFERMINPas encore d'évaluation

- Contadores J-KDocument14 pagesContadores J-KYessenia López0% (1)

- BiestableDocument8 pagesBiestableObeth Ortiz SedeñoPas encore d'évaluation

- AC3000-New Control Unit 09 08 SPDocument17 pagesAC3000-New Control Unit 09 08 SPBruno Mariano100% (1)

- Guia de SeñalizaciónDocument23 pagesGuia de SeñalizaciónEduardo ChagalaPas encore d'évaluation

- Flip FlopDocument12 pagesFlip FlopEmilys QuijadaPas encore d'évaluation

- Bies TableDocument27 pagesBies TablemarialaurarodriguezPas encore d'évaluation

- Multivibrador Biestable CircuitosDocument14 pagesMultivibrador Biestable CircuitosMario GonzalesPas encore d'évaluation

- Tipos de Biestables: RS, D, T, JK y sus Tablas de VerdadDocument7 pagesTipos de Biestables: RS, D, T, JK y sus Tablas de VerdadYefer Solis MazaPas encore d'évaluation

- Bies TableDocument37 pagesBies TableLuz Karina Lopez SaavedraPas encore d'évaluation

- Bies TableDocument11 pagesBies TableAlexis Resendiz PachecoPas encore d'évaluation

- FLIP FlopsDocument9 pagesFLIP FlopsDelfino OlivaresPas encore d'évaluation

- Circuitos SecuencialesDocument17 pagesCircuitos SecuencialesramosemilyPas encore d'évaluation

- Laboratorio N°6 - Flip FlopDocument18 pagesLaboratorio N°6 - Flip FlopJasser CahuiPas encore d'évaluation

- Flip FlopDocument6 pagesFlip FlopJesus VelasquezPas encore d'évaluation

- Biestable - Wikipedia, La Enciclopedia LibreDocument38 pagesBiestable - Wikipedia, La Enciclopedia LibreDIEGO ARON MILLAN COLQUEPas encore d'évaluation

- Analisis de Circuitos SecuencialesDocument19 pagesAnalisis de Circuitos SecuencialesNeiberPas encore d'évaluation

- MultivibradoresDocument39 pagesMultivibradoresLuis Fernando Calderon EchalarPas encore d'évaluation

- PDF Lógica Secuencial PDFDocument5 pagesPDF Lógica Secuencial PDFpagconePas encore d'évaluation

- Biestable JKDocument7 pagesBiestable JKMelina MoncayoPas encore d'évaluation

- BiestablesDocument9 pagesBiestablesEddy HernandezPas encore d'évaluation

- Previo 7 MedicionDocument13 pagesPrevio 7 MedicionLeslie Vp67% (3)

- MARCO TEÓRICO Informe Final 2Document7 pagesMARCO TEÓRICO Informe Final 2Luis Ignacio Ramirez MartinezPas encore d'évaluation

- Que es un flip flop y sus tipos más comunesDocument11 pagesQue es un flip flop y sus tipos más comunesKevin LauraPas encore d'évaluation

- Biestables VSRDocument54 pagesBiestables VSRDaniel AlvarezPas encore d'évaluation

- Examen Flip FlopDocument14 pagesExamen Flip FlopJavier ParragaPas encore d'évaluation

- Bies TableDocument8 pagesBies TableZarate BismkPas encore d'évaluation

- Sistema Lógico Secuencial Asincrónico y SincrónicoDocument38 pagesSistema Lógico Secuencial Asincrónico y SincrónicoNemessis Pacheco100% (1)

- Informe Previo 2 Digitales 2 CasimiroDocument12 pagesInforme Previo 2 Digitales 2 CasimirobandidoPas encore d'évaluation

- Laboratorio 1 Biestables Asíncronos y SincronosDocument16 pagesLaboratorio 1 Biestables Asíncronos y SincronosdaniPas encore d'évaluation

- Previo 2Document8 pagesPrevio 2Javier Zarate NeiraPas encore d'évaluation

- Flip FlopDocument23 pagesFlip FlopJoseph JesusPas encore d'évaluation

- Flip FlopDocument23 pagesFlip FlopRenzoPas encore d'évaluation

- ¿Qué Es Un Flip Flop?Document6 pages¿Qué Es Un Flip Flop?OLIVER ALVARADO MART�NEZPas encore d'évaluation

- Asincronos y SincronosDocument10 pagesAsincronos y SincronosjessicajulissaPas encore d'évaluation

- Practica 7 Lab DigitalDocument16 pagesPractica 7 Lab DigitalSergio RamirezPas encore d'évaluation

- BiestableDocument3 pagesBiestableAlejandra VasquezPas encore d'évaluation

- FsgsfgsDocument5 pagesFsgsfgsCarlos javier bellidoPas encore d'évaluation

- Contador Asincrono AscendeneDocument13 pagesContador Asincrono AscendeneAndiie RiveraPas encore d'évaluation

- Implementación de un multivibrador astable con flip flopsDocument18 pagesImplementación de un multivibrador astable con flip flopscesarPas encore d'évaluation

- Flipflop 27-11-13Document6 pagesFlipflop 27-11-13meoviedo2004Pas encore d'évaluation

- Investigacion Final FinalDocument17 pagesInvestigacion Final Finaljg325418Pas encore d'évaluation

- Flip Flop Tipo JKDocument5 pagesFlip Flop Tipo JKnohemy condo machacaPas encore d'évaluation

- Biestable JK controlado por flancoDocument14 pagesBiestable JK controlado por flancojuanPas encore d'évaluation

- Flip FlopsDocument12 pagesFlip FlopsArmando Galaviz100% (1)

- Informe Final 2 - Circuitos Digitales IIDocument31 pagesInforme Final 2 - Circuitos Digitales IIpperfectionnPas encore d'évaluation

- Actividad 13Document16 pagesActividad 13Stalin Armijos ZambranoPas encore d'évaluation

- FF Jk versátil con entradas J y K y tabla de verdadDocument14 pagesFF Jk versátil con entradas J y K y tabla de verdadEduard ContrerasPas encore d'évaluation

- Circuitos secuenciales: biestables, clasificación y tiposDocument9 pagesCircuitos secuenciales: biestables, clasificación y tiposAsia Lisbeth Del Jesús CasillaPas encore d'évaluation

- Biestables UTEGDocument7 pagesBiestables UTEGJUAN CARLOS QUINTERO GONZALEZPas encore d'évaluation

- Circuitos secuenciales básicosDocument13 pagesCircuitos secuenciales básicosVictoria Peralta Santa CruzPas encore d'évaluation

- Previo 9 Circuitos DigitalesDocument13 pagesPrevio 9 Circuitos DigitalesChristianCastilloPas encore d'évaluation

- Fundamentos de Lógica DigitalDocument11 pagesFundamentos de Lógica Digitalcecivec8Pas encore d'évaluation

- Contador AsíncronoDocument6 pagesContador AsíncronowwJMwwPas encore d'évaluation

- MultivibradoresDocument39 pagesMultivibradoresGabriel Alejandro Astete VargasPas encore d'évaluation

- El Flip FLop y Sus Tipos-Brian Bermudes 141413Document2 pagesEl Flip FLop y Sus Tipos-Brian Bermudes 141413Bermúdez Morales Brian YairPas encore d'évaluation

- Flip-Flops SincrónicosDocument6 pagesFlip-Flops SincrónicosjuanPas encore d'évaluation

- Sesion12 Diseño Secuencial (Parte 1)Document36 pagesSesion12 Diseño Secuencial (Parte 1)coroline24Pas encore d'évaluation

- Clase 8 - Tema 4. Dispositivos Secuenciales y Contadores 2021-2Document7 pagesClase 8 - Tema 4. Dispositivos Secuenciales y Contadores 2021-2Favela QuinteroPas encore d'évaluation

- Flip - FlopsDocument12 pagesFlip - FlopsCortazar CesarPas encore d'évaluation

- Biestables Asincronos y SincronosDocument8 pagesBiestables Asincronos y SincronosAndres WedemeyerPas encore d'évaluation

- Puerto Paralelo Ceictec FIEE UNACDocument8 pagesPuerto Paralelo Ceictec FIEE UNACAlexis ChafloquePas encore d'évaluation

- Ley 30222 - Ley Que Modifica La Ley 29783 - Ley de Seguridad y Salud en El TrabajoDocument5 pagesLey 30222 - Ley Que Modifica La Ley 29783 - Ley de Seguridad y Salud en El TrabajoFatima Velasco HuallancaPas encore d'évaluation

- PLC Arduino PaperDocument5 pagesPLC Arduino PaperAlexis ChafloquePas encore d'évaluation

- PLC ARduinoDocument1 pagePLC ARduinoAlexis ChafloquePas encore d'évaluation

- TarifasDocument8 pagesTarifasAnonymous ouFzvkzPas encore d'évaluation

- Cultura de La LegalidadDocument4 pagesCultura de La LegalidadAlexis ChafloquePas encore d'évaluation

- Teoria de RFDocument11 pagesTeoria de RFLucia AngelicaPas encore d'évaluation

- Del Piropo Al Acoso Sexual Callejero - Comentario - Alexis Jhonny Chafloque MorenoDocument1 pageDel Piropo Al Acoso Sexual Callejero - Comentario - Alexis Jhonny Chafloque MorenoAlexis ChafloquePas encore d'évaluation

- PLC ARduinoDocument1 pagePLC ARduinoAlexis ChafloquePas encore d'évaluation

- Sist Digitales Lab 3 (Unac)Document6 pagesSist Digitales Lab 3 (Unac)nothingtosee99Pas encore d'évaluation

- Teoria de RFDocument11 pagesTeoria de RFLucia AngelicaPas encore d'évaluation

- Arqui Laboratorio 5 Previo 2014BDocument2 pagesArqui Laboratorio 5 Previo 2014BAlexis ChafloquePas encore d'évaluation

- Trabajo de FibrasDocument8 pagesTrabajo de FibrasAlexis ChafloquePas encore d'évaluation

- Estado de Situacion Financiera - BriDocument6 pagesEstado de Situacion Financiera - BriAlexis ChafloquePas encore d'évaluation

- Bloques EconómicosDocument3 pagesBloques EconómicosAlexis ChafloquePas encore d'évaluation

- GMPLSDocument231 pagesGMPLSMiguel Angel BMPas encore d'évaluation

- Artículo 1Document3 pagesArtículo 1Alexis ChafloquePas encore d'évaluation

- Método de Newton RapshonDocument2 pagesMétodo de Newton RapshonAlexis ChafloquePas encore d'évaluation

- GMPLSDocument231 pagesGMPLSMiguel Angel BMPas encore d'évaluation

- Decodificador BCD A 7 SegmentosDocument10 pagesDecodificador BCD A 7 SegmentosAlexis ChafloquePas encore d'évaluation

- EdoDocument11 pagesEdoAlexis ChafloquePas encore d'évaluation

- Resumen de Los Metodos Antes ParcialDocument2 pagesResumen de Los Metodos Antes ParcialAlexis ChafloquePas encore d'évaluation

- Simulink TeoriaDocument39 pagesSimulink TeoriaAlexis ChafloquePas encore d'évaluation

- Manual Atlas TI. 5 EspanholDocument128 pagesManual Atlas TI. 5 EspanholLeandro GomesPas encore d'évaluation

- EL CAMPO ELECTRICO (Falta Las Mediciones Indirectas)Document2 pagesEL CAMPO ELECTRICO (Falta Las Mediciones Indirectas)Alexis ChafloquePas encore d'évaluation

- Lesgislacion ElectricaDocument9 pagesLesgislacion ElectricaLu RangelPas encore d'évaluation

- Alberto Farina 20200716 Motores Electricos Trifasicos Parte 7 Seleccion Del MotorDocument3 pagesAlberto Farina 20200716 Motores Electricos Trifasicos Parte 7 Seleccion Del MotorLUIS ANGEL CORDOVA FIALLOPas encore d'évaluation

- FusíveisNHgLgGBussmann PDFDocument6 pagesFusíveisNHgLgGBussmann PDFkappasrlPas encore d'évaluation

- Máquinas AsíncronasDocument82 pagesMáquinas Asíncronasjose lezcanoPas encore d'évaluation

- ELECTROSTATICA Capacidad ElectricaDocument16 pagesELECTROSTATICA Capacidad ElectricaMartín Espinoza Maraví100% (1)

- BRCDocument4 pagesBRCosvi009Pas encore d'évaluation

- Plantronics S12Document2 pagesPlantronics S12horacioterragnoPas encore d'évaluation

- TransformadoresDocument33 pagesTransformadoresCARLA YAMILE PERALES QUIROZPas encore d'évaluation

- Comm ViewDocument4 pagesComm ViewAnesimPas encore d'évaluation

- Práctica 3 PotenciaDocument14 pagesPráctica 3 PotenciaCalvin CantuPas encore d'évaluation

- Pruebas de ContinuidadDocument2 pagesPruebas de ContinuidadFabian PullaPas encore d'évaluation

- Practica 9 ElectrodeposiciónDocument3 pagesPractica 9 ElectrodeposiciónIván GonzálezPas encore d'évaluation

- Electroscopio CaseroDocument1 pageElectroscopio CaseroElito ZagalPas encore d'évaluation

- Calculo de Los Circuitos Derivados 1Document56 pagesCalculo de Los Circuitos Derivados 1STERVER DARKSO100% (1)

- Lab 5 Cee2 Jose Luis Valdivia GuillenDocument7 pagesLab 5 Cee2 Jose Luis Valdivia GuillenJOSE LUIS VALDIVIA GUILLENPas encore d'évaluation

- Aspectos Generales Del Sistema de DistribuciónDocument6 pagesAspectos Generales Del Sistema de DistribuciónEdna LópezPas encore d'évaluation

- Guia de Cableado de Fieldbus EspanolDocument43 pagesGuia de Cableado de Fieldbus Espanol1056Pas encore d'évaluation

- 1.1contactores y ArrancadoresDocument12 pages1.1contactores y ArrancadoresjeasonPas encore d'évaluation

- Recomendacion Conexion Neutro Tierra PAD 3 - b1Document8 pagesRecomendacion Conexion Neutro Tierra PAD 3 - b1luisPas encore d'évaluation

- Formato para Registro de Datos Laboratorio Fisica Electronica No 2Document11 pagesFormato para Registro de Datos Laboratorio Fisica Electronica No 2Lore GuerreroPas encore d'évaluation

- Laboratorio 4 de Ing ElectricaDocument7 pagesLaboratorio 4 de Ing ElectricaCésar NavarroPas encore d'évaluation

- TRS1 DS UsDocument1 pageTRS1 DS UsFrancisco ChuloPas encore d'évaluation

- Naturaleza de Los Circuitos Digitales IDocument16 pagesNaturaleza de Los Circuitos Digitales IWalter HerreraPas encore d'évaluation

- UltrasonidoDocument123 pagesUltrasonidoJuan Carlos GBPas encore d'évaluation

- Principales Hitos TL-EES-R3Document8 pagesPrincipales Hitos TL-EES-R3Román Buñay AndradePas encore d'évaluation

- TrafosDocument67 pagesTrafosMarcela GarcíaPas encore d'évaluation

- Proyecto Efecto JouleDocument17 pagesProyecto Efecto JouleCarlos AtúncarPas encore d'évaluation

- Wuolah Free Problemas ElectricaDocument128 pagesWuolah Free Problemas ElectricajaPas encore d'évaluation