Académique Documents

Professionnel Documents

Culture Documents

74LCX125 Low Voltage Quad Buffer With 5V Tolerant Inputs and Outputs

Transféré par

fenixtec1Description originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

74LCX125 Low Voltage Quad Buffer With 5V Tolerant Inputs and Outputs

Transféré par

fenixtec1Droits d'auteur :

Formats disponibles

7

4

L

C

X

1

2

5

L

o

w

V

o

l

t

a

g

e

Q

u

a

d

B

u

f

f

e

r

w

i

t

h

5

V

T

o

l

e

r

a

n

t

I

n

p

u

t

s

a

n

d

O

u

t

p

u

t

s

1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74LCX125 Rev. 1.7.0

February 2008

74LCX125

Low Voltage Quad Buffer with 5V Tolerant

Inputs and Outputs

Features

5V tolerant inputs and outputs

2.3V3.6V V

CC

specifications provided

6.0ns t

PD

max. (V

CC

=

3.3V), 10A I

CC

max.

Power down high impedance inputs and outputs

Supports live insertion/withdrawal

(1)

24mA output drive (V

CC

=

3.0V)

Latch-up performance exceeds JEDEC 78 conditions

ESD performance:

Human body model

>

2000V

Machine model

>

100V

Leadless DQFN package

Note:

1. To ensure the high-impedance state during power up

or down, OE should be tied to V

CC

through a pull-up

resistor: the minimum value of the resistor is

determined by the current-sourcing capability of the

driver.

General Description

The LCX125 contains four independent non-inverting

buffers with 3-STATE outputs. The inputs tolerate volt-

ages up to 7V allowing the interface of 5V systems to 3V

systems.

The 74LCX125 is fabricated with an advanced CMOS

technology to achieve high speed operation while main-

taining CMOS low power dissipation.

Ordering Information

Note:

2. DQFN package available in Tape and Reel only.

Device also available in Tape and Reel. Specify by appending suffix letter X to the ordering number.

All packages are lead free per JEDEC: J-STD-020B standard.

Order Number

Package

Number Package Description

74LCX125M M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow

74LCX125SJ M14D 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74LCX125BQX

(2)

MLP14A 14-Terminal Depopulated Quad Very-Thin Flat Pack No Leads (DQFN), JEDEC

MO-241, 2.5 x 3.0mm

74LCX125MTC MTC14 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm

Wide

Implements proprietary noise/EMI reduction circuitry

1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74LCX125 Rev. 1.7.0 2

7

4

L

C

X

1

2

5

L

o

w

V

o

l

t

a

g

e

Q

u

a

d

B

u

f

f

e

r

w

i

t

h

5

V

T

o

l

e

r

a

n

t

I

n

p

u

t

s

a

n

d

O

u

t

p

u

t

s

Connection Diagrams

Pin Assignments for SOIC, SOP, and TSSOP

(Top View)

Pad Assignments for DQFN

(Top Through View)

Pin Description

Logic Symbol

IEEE/IEC

Truth Table

H

=

HIGH Voltage Level

L

=

LOW Voltage Level

Z

=

High Impedance

X

=

Immaterial

Pin Names Description

A

n

Inputs

OE

n

Output Enable Inputs

O

n

Outputs

Inputs Output

OE

n

A

n

O

n

L L L

L H H

H X Z

1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74LCX125 Rev. 1.7.0 3

7

4

L

C

X

1

2

5

L

o

w

V

o

l

t

a

g

e

Q

u

a

d

B

u

f

f

e

r

w

i

t

h

5

V

T

o

l

e

r

a

n

t

I

n

p

u

t

s

a

n

d

O

u

t

p

u

t

s

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be

operable above the recommended operating conditions and stressing the parts to these levels is not recommended.

In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability.

The absolute maximum ratings are stress ratings only.

Note:

3. I

O

Absolute Maximum Rating must be observed.

Recommended Operating Conditions

(4)

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended

operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not

recommend exceeding them or designing to absolute maximum ratings.

Note:

4. Unused inputs must be held HIGH or LOW. They may not float.

Symbol Parameter Rating

V

CC

Supply Voltage 0.5V to +7.0V

V

I

DC Input Voltage 0.5V to +7.0V

V

O

DC Output Voltage,

Output in 3-STATE 0.5V to +7.0V

Output in HIGH or LOW State

(3)

0.5V to V

CC

+ 0.5V

I

IK

DC Input Diode Current, V

I

<

GND 50mA

I

OK

DC Output Diode Current

V

O

<

GND 50mA

V

O

>

V

CC

+50mA

I

O

DC Output Source/Sink Current 50mA

I

CC

DC Supply Current per Supply Pin 100mA

I

GND

DC Ground Current per Ground Pin 100mA

T

STG

Storage Temperature 65C to +150C

Symbol Parameter Min. Max. Units

V

CC

Supply Voltage

Operating 2.0 3.6 V

Data Retention 1.5 3.6

V

I

Input Voltage 0 5.5 V

V

O

Output Voltage

HIGH or LOW State 0 V

CC

V

3-STATE 0 5.5

I

OH

/

I

OL

Output Current

V

CC

=

3.0V3.6V 24 mA

V

CC

=

2.7V3.0V 12

V

CC

=

2.3V2.7V 8

T

A

Free-Air Operating Temperature 40 85 C

t

/

V Input Edge Rate, V

IN

=

0.8V2.0V, V

CC

=

3.0V 0 10 ns

/

V

1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74LCX125 Rev. 1.7.0 4

7

4

L

C

X

1

2

5

L

o

w

V

o

l

t

a

g

e

Q

u

a

d

B

u

f

f

e

r

w

i

t

h

5

V

T

o

l

e

r

a

n

t

I

n

p

u

t

s

a

n

d

O

u

t

p

u

t

s

DC Electrical Characteristics

Note:

5. Outputs disabled or 3-STATE only.

AC Electrical Characteristics

Note:

6. Skew is defined as the absolute value of the difference between the actual propagation delay for any two

separate outputs of the same device. The specification applies to any outputs switching in the same direction,

either HIGH-to-LOW (t

OSHL

) or LOW-to-HIGH (t

OSLH

).

Symbol Parameter V

CC

(V) Conditions

T

A

=

40C to +85C

Units Min. Max.

V

IH

HIGH Level Input Voltage 2.32.7 1.7 V

2.73.6 2.0

V

IL

LOW Level Input Voltage 2.32.7 0.7 V

2.73.6 0.8

V

OH

HIGH Level Output Voltage 2.33.6 I

OH

=

100A V

CC

0.2 V

2.3 I

OH

=

8mA 1.8

2.7 I

OH

=

12mA 2.2

3.0 I

OH

=

18mA 2.4

I

OH

=

24mA 2.2

V

OL

LOW Level Output Voltage 2.33.6 I

OL

=

100A 0.2 V

2.3 I

OL

=

8mA 0.6

2.7 I

OL

=

12mA 0.4

3.0 I

OL

=

16mA 0.4

I

OL

=

24mA 0.55

I

I

Input Leakage Current 2.33.6 0

V

I

5.5V 5.0 A

I

OZ

3-STATE Output Leakage 2.33.6 0 V

O

5.5V,

V

I

= V

IH

or V

IL

5.0 A

I

OFF

Power-Off Leakage Current 0 V

I

or V

O

= 5.5V 10 A

I

CC

Quiescent Supply Current 2.33.6 V

I

= V

CC

or GND 10 A

3.6V V

I

, V

O

5.5V

(5)

10

I

CC

Increase in I

CC

per Input 2.33.6 V

IH

= V

CC

0.6V 500 A

Symbol Parameter

T

A

= 40C to +85C, R

L

= 500

Units

V

CC

= 3.3V 0.3V,

C

L

= 50 pF

V

CC

= 2.7V,

C

L

= 50 pF

V

CC

= 2.5V 0.2V,

C

L

= 30 pF

Min. Max. Min. Max. Min. Max.

t

PHL

, t

PLH

Propagation Delay 1.5 6.0 1.5 6.5 1.5 7.2 ns

t

PZL

, t

PZH

Output Enable Time 1.5 7.0 1.5 8.0 1.5 9.1 ns

t

PLZ

, t

PHZ

Output Disable Time 1.5 6.0 1.5 7.0 1.5 7.2 ns

t

OSHL

, t

OSLH

Output to Output Skew

(6)

1.0 ns

1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74LCX125 Rev. 1.7.0 5

7

4

L

C

X

1

2

5

L

o

w

V

o

l

t

a

g

e

Q

u

a

d

B

u

f

f

e

r

w

i

t

h

5

V

T

o

l

e

r

a

n

t

I

n

p

u

t

s

a

n

d

O

u

t

p

u

t

s

Dynamic Switching Characteristics

Capacitance

Symbol Parameter V

CC

(V) Conditions

T

A

= 25C

Unit Typical

V

OLP

Quiet Output Dynamic Peak V

OL

3.3 C

L

= 50pF, V

IH

= 3.3V, V

IL

= 0V 0.8 V

2.5 C

L

= 30pF, V

IH

= 2.5V, V

IL

= 0V 0.6

V

OLV

Quiet Output Dynamic Valley V

OL

3.3 C

L

= 50pF, V

IH

= 3.3V, V

IL

= 0V 0.8 V

2.5 C

L

= 30pF, V

IH

= 2.5V, V

IL

= 0V 0.6

Symbol Parameter Conditions Typical Units

C

IN

Input Capacitance V

CC

= Open, V

I

= 0V or V

CC

7.0 pF

C

OUT

Output Capacitance V

CC

= 3.3V, V

I

= 0V or V

CC

8.0 pF

C

PD

Power Dissipation Capacitance V

CC

= 3.3V, V

I

= 0V or V

CC

, f = 10MHz 25.0 pF

1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74LCX125 Rev. 1.7.0 6

7

4

L

C

X

1

2

5

L

o

w

V

o

l

t

a

g

e

Q

u

a

d

B

u

f

f

e

r

w

i

t

h

5

V

T

o

l

e

r

a

n

t

I

n

p

u

t

s

a

n

d

O

u

t

p

u

t

s

AC Loading and Waveforms (Generic for LCX Family)

Figure 1. AC Test Circuit (C

L

includes probe and jig capacitance)

Waveform for Inverting and Non-Inverting Functions

Propagation Delay. Pulse Width and t

rec

Waveforms

3-STATE Output Low Enable and

Disable Times for Logic

3-STATE Output High Enable and

Disable Times for Logic

Setup Time, Hold Time and Recovery Time for Logic

t

rise

and t

fall

Figure 2. Waveforms (Input Characteristics; f = 1MHz, t

r

= t

f

= 3ns)

Test Switch

t

PLH

, t

PHL

Open

t

PZL

, t

PLZ

6V at V

CC

= 3.3 0.3V

V

CC

x 2 at V

CC

= 2.5 0.2V

t

PZH

, t

PHZ

GND

Symbol

V

CC

3.3V 0.3V 2.7V 2.5V 0.2V

V

mi

1.5V 1.5V V

CC

/ 2

V

mo

1.5V 1.5V V

CC

/ 2

V

x

V

OL

+ 0.3V V

OL

+ 0.3V V

OL

+ 0.15V

V

y

V

OH

0.3V V

OH

0.3V V

OH

0.15V

1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74LCX125 Rev. 1.7.0 7

7

4

L

C

X

1

2

5

L

o

w

V

o

l

t

a

g

e

Q

u

a

d

B

u

f

f

e

r

w

i

t

h

5

V

T

o

l

e

r

a

n

t

I

n

p

u

t

s

a

n

d

O

u

t

p

u

t

s

Schematic Diagram (Generic for LCX Family)

1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74LCX125 Rev. 1.7.0 8

7

4

L

C

X

1

2

5

L

o

w

V

o

l

t

a

g

e

Q

u

a

d

B

u

f

f

e

r

w

i

t

h

5

V

T

o

l

e

r

a

n

t

I

n

p

u

t

s

a

n

d

O

u

t

p

u

t

s

Tape and Reel Specification

Tape Format for DQFN

Tape Dimensions inches (millimeters)

Reel Dimensions inches (millimeters)

Package Designator Tape Section Number of Cavities Cavity Status Cover Tape Status

BQX Leader (Start End) 125 (Typ.) Empty Sealed

Carrier 3000 Filled Sealed

Trailer (Hub End) 75 (Typ.) Empty Sealed

Tape Size A B C D N W1 W2

12mm 13.0 (330.0) 0.059 (1.50) 0.512 (13.00) 0.795 (20.20) 2.165 (55.00) 0.488 (12.4) 0.724 (18.4)

1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74LCX125 Rev. 1.7.0 9

7

4

L

C

X

1

2

5

L

o

w

V

o

l

t

a

g

e

Q

u

a

d

B

u

f

f

e

r

w

i

t

h

5

V

T

o

l

e

r

a

n

t

I

n

p

u

t

s

a

n

d

O

u

t

p

u

t

s

Physical Dimensions

Figure 3. 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specications do not expand the terms of Fairchilds worldwide terms and conditions,

specically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductors online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/

LAND PATTERN RECOMMENDATION

NOTES: UNLESS OTHERWISE SPECIFIED

A) THIS PACKAGE CONFORMS TO JEDEC

MS-012, VARIATION AB, ISSUE C,

B) ALL DIMENSIONS ARE IN MILLIMETERS.

C) DIMENSIONS DO NOT INCLUDE MOLD

FLASH OR BURRS.

D) LANDPATTERN STANDARD:

SOIC127P600X145-14M

E) DRAWING CONFORMS TO ASME Y14.5M-1994

F) DRAWING FILE NAME: M14AREV13

PIN ONE

INDICATOR

8

0

SEATING PLANE

DETAIL A

SCALE: 20:1

GAGE PLANE

0.25

X 45

1

0.10

C

C

B C A

7

M

14

B

A

8

SEE DETAIL A

5.60

0.65

1.70 1.27

8.75

8.50

7.62

6.00

4.00

3.80

(0.33)

1.27

0.51

0.35

1.75 MAX

1.50

1.25

0.25

0.10

0.25

0.19

(1.04)

0.90

0.50

0.36

R0.10

R0.10

0.50

0.25

1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74LCX125 Rev. 1.7.0 10

7

4

L

C

X

1

2

5

L

o

w

V

o

l

t

a

g

e

Q

u

a

d

B

u

f

f

e

r

w

i

t

h

5

V

T

o

l

e

r

a

n

t

I

n

p

u

t

s

a

n

d

O

u

t

p

u

t

s

Physical Dimensions (Continued)

Figure 4. 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specications do not expand the terms of Fairchilds worldwide terms and conditions,

specically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductors online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/

1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74LCX125 Rev. 1.7.0 11

7

4

L

C

X

1

2

5

L

o

w

V

o

l

t

a

g

e

Q

u

a

d

B

u

f

f

e

r

w

i

t

h

5

V

T

o

l

e

r

a

n

t

I

n

p

u

t

s

a

n

d

O

u

t

p

u

t

s

Physical Dimensions (Continued)

Figure 5. 14-Terminal Depopulated Quad Very-Thin Flat Pack No Leads (DQFN), JEDEC MO-241, 2.5 x 3.0mm

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specications do not expand the terms of Fairchilds worldwide terms and conditions,

specically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductors online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/

1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74LCX125 Rev. 1.7.0 12

7

4

L

C

X

1

2

5

L

o

w

V

o

l

t

a

g

e

Q

u

a

d

B

u

f

f

e

r

w

i

t

h

5

V

T

o

l

e

r

a

n

t

I

n

p

u

t

s

a

n

d

O

u

t

p

u

t

s

Physical Dimensions (Continued)

Figure 6. 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specications do not expand the terms of Fairchilds worldwide terms and conditions,

specically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductors online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/

C. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH,

AND TIE BAR EXTRUSIONS

F. DRAWING FILE NAME: MTC14REV6

R0.09 min

12.00

TOP & BOTTOM

0.43 TYP

1.00

D. DIMENSIONING AND TOLERANCES PER ANSI

Y14.5M, 1982

R0.09min

E. LANDPATTERN STANDARD: SOP65P640X110-14M

0.65

6.10

1.65

0.45

A. CONFORMS TO JEDEC REGISTRATION MO-153,

VARIATION AB, REF NOTE 6

B. DIMENSIONS ARE IN MILLIMETERS

1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74LCX125 Rev. 1.7.0 13

TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global

subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

ACEx

Build it Now

CorePLUS

CROSSVOLT

CTL

Current Transfer Logic

EcoSPARK

EZSWITCH *

Fairchild

Fairchild Semiconductor

FACT Quiet Series

FACT

FAST

FastvCore

FlashWriter

*

FPS

FRFET

Global Power Resource

SM

Green FPS

Green FPSe-Series

GTO

i-Lo

IntelliMAX

ISOPLANAR

MegaBuck

MICROCOUPLER

MicroFET

MicroPak

MillerDrive

Motion-SPM

OPTOLOGIC

OPTOPLANAR

PDP-SPM

Power220

POWEREDGE

Power-SPM

PowerTrench

Programmable Active Droop

QFET

QS

QT Optoelectronics

Quiet Series

RapidConfigure

SMART START

SPM

STEALTH

SuperFET

SuperSOT-3

SuperSOT-6

SuperSOT-8

SupreMOS

SyncFET

The Power Franchise

TinyBoost

TinyBuck

TinyLogic

TINYOPTO

TinyPower

TinyPWM

TinyWire

SerDes

UHC

Ultra FRFET

UniFET

VCX

* EZSWITCH and FlashWriter

are trademarks of System General Corporation, used under license by Fairchild Semiconductor.

DISCLAIMER

FAIRCHILDSEMICONDUCTORRESERVESTHERIGHT TOMAKECHANGESWITHOUT FURTHERNOTICETOANYPRODUCTS

HEREINTOIMPROVERELIABILITY, FUNCTION, ORDESIGN. FAIRCHILDDOESNOT ASSUME ANY LIABILITY ARISINGOUT OF THE

APPLICATIONORUSEOF ANYPRODUCT ORCIRCUIT DESCRIBEDHEREIN; NEITHERDOESIT CONVEYANYLICENSEUNDERITS

PATENT RIGHTS, NORTHERIGHTSOF OTHERS. THESESPECIFICATIONSDONOT EXPANDTHETERMSOF FAIRCHILDS

WORLDWIDE TERMS ANDCONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICHCOVERS THESE PRODUCTS.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR

SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the body or

(b) support or sustain life, and (c) whose failure to perform

when properly used in accordance with instructions for use

provided in the labeling, can be reasonably expected to

result in a significant injury of the user.

2. A critical component in any component of a life support,

device, or system whose failure to perform can be

reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Advance Information Formative or In Design

This datasheet contains the design specifications for product

development. Specifications may change in any manner without notice.

Preliminary First Production

This datasheet contains preliminary data; supplementary data will be

published at a later date. Fairchild Semiconductor reserves the right to

make changes at any time without notice to improve design.

No Identification Needed Full Production

This datasheet contains final specifications. Fairchild Semiconductor

reserves the right to make changes at any time without notice to improve

the design.

Obsolete Not In Production

This datasheet contains specifications on a product that has been

discontinued by Fairchild Semiconductor. The datasheet is printed for

reference information only.

Rev. I33

7

4

L

C

X

1

2

5

L

o

w

V

o

l

t

a

g

e

Q

u

a

d

B

u

f

f

e

r

w

i

t

h

5

V

T

o

l

e

r

a

n

t

I

n

p

u

t

s

a

n

d

O

u

t

p

u

t

s

Vous aimerez peut-être aussi

- 74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsDocument11 pages74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsRicardo MercadoPas encore d'évaluation

- DatasheetDocument8 pagesDatasheetMaizatul Hanisah RoziPas encore d'évaluation

- CD4047Document9 pagesCD4047Haryadi VjPas encore d'évaluation

- Nc7Sz373 Tinylogic Uhs D-Type Latch With 3-State Output: General Description FeaturesDocument9 pagesNc7Sz373 Tinylogic Uhs D-Type Latch With 3-State Output: General Description Featuresgreentea601Pas encore d'évaluation

- 74cx16839 U18 PDFDocument7 pages74cx16839 U18 PDFMarcos AurélioPas encore d'évaluation

- 74ALVC00 Low Voltage Quad 2-Input NAND Gate With 3.6V Tolerant Inputs and OutputsDocument6 pages74ALVC00 Low Voltage Quad 2-Input NAND Gate With 3.6V Tolerant Inputs and OutputsraphaelraistPas encore d'évaluation

- 74 LV 00Document10 pages74 LV 00Brzata PticaPas encore d'évaluation

- Single Bilateral Switch: Order CodesDocument11 pagesSingle Bilateral Switch: Order CodesGaryTechPas encore d'évaluation

- Nc7Sbu3157 - Fsau3157 Tinylogic Low Voltage Uhs SPDT Analog Switch With 2V Undershoot ProtectionDocument11 pagesNc7Sbu3157 - Fsau3157 Tinylogic Low Voltage Uhs SPDT Analog Switch With 2V Undershoot ProtectionAgus TabraniPas encore d'évaluation

- 7Z08Document7 pages7Z08André Frota PaivaPas encore d'évaluation

- Octal 3-State Noninverting Transparent Latch: SL74HC573Document5 pagesOctal 3-State Noninverting Transparent Latch: SL74HC573Prayu GarnurmPas encore d'évaluation

- Octal Bus Transceiver With 3-State Outputs: FeaturesDocument24 pagesOctal Bus Transceiver With 3-State Outputs: FeaturesLungoci AdrianPas encore d'évaluation

- Quadruple Bus Buffer Gate With 3-State Outputs: FeaturesDocument20 pagesQuadruple Bus Buffer Gate With 3-State Outputs: FeaturesEngine Tuning UpPas encore d'évaluation

- 74AC74, 74ACT74 Dual D-Type Positive Edge-Triggered Flip-FlopDocument13 pages74AC74, 74ACT74 Dual D-Type Positive Edge-Triggered Flip-FlopMudasir UmarPas encore d'évaluation

- 74LVT2244, 74LVTH2244 Low Voltage Octal Buffer/Line Driver With 3-STATE Outputs and 25 Series Resistors in The OutputsDocument9 pages74LVT2244, 74LVTH2244 Low Voltage Octal Buffer/Line Driver With 3-STATE Outputs and 25 Series Resistors in The Outputsjovares2099Pas encore d'évaluation

- CD4047BC Low Power Monostable/Astable Multivibrator: General DescriptionDocument10 pagesCD4047BC Low Power Monostable/Astable Multivibrator: General DescriptionWillianPas encore d'évaluation

- MC74VHC1GT125 Noninverting Buffer / CMOS Logic Level ShifterDocument6 pagesMC74VHC1GT125 Noninverting Buffer / CMOS Logic Level ShifterCh SamirPas encore d'évaluation

- Octal 3-State Noninverting D Flip-Flop: KK74HC574ADocument6 pagesOctal 3-State Noninverting D Flip-Flop: KK74HC574Ajksb100Pas encore d'évaluation

- MC74HC541A Octal 3-State Non-Inverting Buffer/Line Driver/ Line ReceiverDocument8 pagesMC74HC541A Octal 3-State Non-Inverting Buffer/Line Driver/ Line ReceivernandobnuPas encore d'évaluation

- 74VCX86 Low Voltage Quad 2-Input Exclusive-OR Gate With 3.6V Tolerant Inputs and OutputsDocument7 pages74VCX86 Low Voltage Quad 2-Input Exclusive-OR Gate With 3.6V Tolerant Inputs and Outputsgame___overPas encore d'évaluation

- 74LVC14APWDHDocument11 pages74LVC14APWDHIlie GrecuPas encore d'évaluation

- 74AHC1G86 74AHCT1G86: 1. General DescriptionDocument12 pages74AHC1G86 74AHCT1G86: 1. General DescriptionKushalSwamyPas encore d'évaluation

- MM74HC245A Octal 3-STATE Transceiver: General DescriptionDocument7 pagesMM74HC245A Octal 3-STATE Transceiver: General DescriptionMubarak CePas encore d'évaluation

- Features: Single Bilateral SwitchDocument15 pagesFeatures: Single Bilateral SwitchGaryTechPas encore d'évaluation

- MC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738Document8 pagesMC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738greentea601Pas encore d'évaluation

- Synchronous Presettable 4-Bit Counter: M B Order CodesDocument12 pagesSynchronous Presettable 4-Bit Counter: M B Order CodesMarimuthu RajPas encore d'évaluation

- MC74AC253, MC74ACT253 Dual 4 Input Multiplexer With 3 State OutputsDocument11 pagesMC74AC253, MC74ACT253 Dual 4 Input Multiplexer With 3 State OutputsMateus RossiniPas encore d'évaluation

- Octal Bus Buffer With 3 State Outputs (Non Inverted) : M B Order CodesDocument8 pagesOctal Bus Buffer With 3 State Outputs (Non Inverted) : M B Order CodesStevenPas encore d'évaluation

- 74AHC1G32 74AHCT1G32: 1. General DescriptionDocument12 pages74AHC1G32 74AHCT1G32: 1. General DescriptionnevdullPas encore d'évaluation

- Octal D-Type Latch With 3 State Outputs (Non Inverted) : Order CodesDocument11 pagesOctal D-Type Latch With 3 State Outputs (Non Inverted) : Order CodesIsaacPas encore d'évaluation

- 74LVC2G126: 1. General DescriptionDocument22 pages74LVC2G126: 1. General DescriptiontuansanhPas encore d'évaluation

- C.I 74HC175Document7 pagesC.I 74HC175DOMINGOS ALADIRPas encore d'évaluation

- 74LVC1G11: 1. General DescriptionDocument14 pages74LVC1G11: 1. General DescriptionnevdullPas encore d'évaluation

- 74VHCT245A Octal Buffer/Line Driver With 3-STATE Outputs: Features General DescriptionDocument9 pages74VHCT245A Octal Buffer/Line Driver With 3-STATE Outputs: Features General DescriptionMalik Mian Manzer MithaPas encore d'évaluation

- General Description: Quad Bilateral SwitchDocument23 pagesGeneral Description: Quad Bilateral Switchtotal4321Pas encore d'évaluation

- General Description: Quad Buffer/line Driver 3-StateDocument15 pagesGeneral Description: Quad Buffer/line Driver 3-Statesinner86Pas encore d'évaluation

- Mid Semester 2012 TID203Document17 pagesMid Semester 2012 TID203peas002Pas encore d'évaluation

- 74AC00 - 74ACT00 Quad 2-Input NAND Gate: General Description FeaturesDocument8 pages74AC00 - 74ACT00 Quad 2-Input NAND Gate: General Description FeaturesAini NierisPas encore d'évaluation

- 74 HC 573Document5 pages74 HC 573Yann Van OsselaerPas encore d'évaluation

- 74 Ls 244Document16 pages74 Ls 244Abednego TariganPas encore d'évaluation

- SN54HC573A, SN74HC573A Octal Transparent D-Type Latches With 3-State OutputsDocument7 pagesSN54HC573A, SN74HC573A Octal Transparent D-Type Latches With 3-State OutputsMadhukar PuliPas encore d'évaluation

- Dual D-Type Flip-Flop: Integrated CircuitsDocument8 pagesDual D-Type Flip-Flop: Integrated CircuitsRakesh Kumar DPas encore d'évaluation

- Fan 7316Document21 pagesFan 7316sontuyet82Pas encore d'évaluation

- IDT54/74FCT373T/AT/CT Fast Cmos Octal Transparent Latch: Features: DescriptionDocument7 pagesIDT54/74FCT373T/AT/CT Fast Cmos Octal Transparent Latch: Features: Descriptiongreentea601Pas encore d'évaluation

- Data SheetDocument6 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- 74LVC1G04: 1. General DescriptionDocument20 pages74LVC1G04: 1. General DescriptionnevdullPas encore d'évaluation

- 74LVC00A: 1. General DescriptionDocument14 pages74LVC00A: 1. General DescriptionVlad Cristia-AvramPas encore d'évaluation

- DatasheetDocument9 pagesDatasheetLuis Caba RamirezPas encore d'évaluation

- Dual Intelligent Power Low Side Switch: DescriptionDocument10 pagesDual Intelligent Power Low Side Switch: DescriptionDan EsentherPas encore d'évaluation

- Double Channel High Side Driver: Type R I VDocument19 pagesDouble Channel High Side Driver: Type R I VDan EsentherPas encore d'évaluation

- Data Sheet: 74AHC74 74AHCT74Document20 pagesData Sheet: 74AHC74 74AHCT74Kang JadiJaya OtodidakPas encore d'évaluation

- 74AC74Document9 pages74AC74ciernesPas encore d'évaluation

- 74LVC08A: Low Voltage Cmos Quad 2-Input and Gate High PerformanceDocument11 pages74LVC08A: Low Voltage Cmos Quad 2-Input and Gate High PerformanceFernando QueirozPas encore d'évaluation

- 74AHC1G02 74AHCT1G02: 1. General DescriptionDocument11 pages74AHC1G02 74AHCT1G02: 1. General DescriptionMarcu Andrei StefanPas encore d'évaluation

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsD'EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsPas encore d'évaluation

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Pas encore d'évaluation

- PICDEM 2 Plus Users Guide 51275cDocument26 pagesPICDEM 2 Plus Users Guide 51275cAvais AhmedPas encore d'évaluation

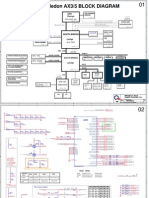

- Quanta Ax3 Winbledon Ax3.5 - Da0ax3mb6c2 Ddr3 - Rev 1aDocument30 pagesQuanta Ax3 Winbledon Ax3.5 - Da0ax3mb6c2 Ddr3 - Rev 1afenixtec1100% (1)

- Quanta Ax3 Winbledon Ax3.5 - Da0ax3mb6c2 Ddr3 - Rev 1aDocument30 pagesQuanta Ax3 Winbledon Ax3.5 - Da0ax3mb6c2 Ddr3 - Rev 1afenixtec1100% (1)

- Academic Program FlyerDocument2 pagesAcademic Program Flyerfenixtec1Pas encore d'évaluation

- FD FDMS9620SDocument9 pagesFD FDMS9620Sfenixtec1Pas encore d'évaluation

- Datasheet 3Document6 pagesDatasheet 3fenixtec1Pas encore d'évaluation

- Ao4468 PDFDocument5 pagesAo4468 PDFAxsoftSoportePas encore d'évaluation

- THAT 2181-Series DatasheetDocument12 pagesTHAT 2181-Series DatasheetSaverioCor100% (1)

- Lab 1 Pulse Code ModulationDocument5 pagesLab 1 Pulse Code ModulationAbbaas AlifPas encore d'évaluation

- 208SE Class Test Jan2019 Rev ADocument10 pages208SE Class Test Jan2019 Rev AMeowPas encore d'évaluation

- Display Electroluminiscent 640x480Document20 pagesDisplay Electroluminiscent 640x480Sveto Sl100% (1)

- Brosur Patient Monitor NSR PM1200Document4 pagesBrosur Patient Monitor NSR PM1200Riska SetyawPas encore d'évaluation

- Introduction To Pic 16F877ADocument37 pagesIntroduction To Pic 16F877AAbdul Muqeet Ahmed KhanPas encore d'évaluation

- Service Manual: ChassisDocument43 pagesService Manual: ChassisSokol Kadare50% (2)

- FS08 - Elec - Tender DrawingDocument5 pagesFS08 - Elec - Tender Drawinglkt_pestechPas encore d'évaluation

- CSC 326 Transformer Protection Ied Technical Application ManualDocument445 pagesCSC 326 Transformer Protection Ied Technical Application ManualAssistant executive engineerPas encore d'évaluation

- AC 800PEC Sales BrochureDocument12 pagesAC 800PEC Sales BrochureMohd Lutfi MahaliPas encore d'évaluation

- 05 - LED BlinkingDocument3 pages05 - LED BlinkingShivaniPas encore d'évaluation

- F0af6 Clevo W830T W840TDocument46 pagesF0af6 Clevo W830T W840TOsvaldo LucianiPas encore d'évaluation

- 15ecl48-VTU-raghudathesh-Instrumentation Amplifier PDFDocument6 pages15ecl48-VTU-raghudathesh-Instrumentation Amplifier PDFraghudatheshgpPas encore d'évaluation

- English Print PDFDocument24 pagesEnglish Print PDFYASSINE EL HAOURIPas encore d'évaluation

- CookbookDocument248 pagesCookbookHalph Macedo FraulobPas encore d'évaluation

- Orthogonal Frequency-Division Multiple AccessDocument10 pagesOrthogonal Frequency-Division Multiple AccessDarwinPas encore d'évaluation

- 11 Physics CompleteDocument15 pages11 Physics Completehana.tahir345Pas encore d'évaluation

- Magnetic Lock CE EMC Test Report E160510426Document36 pagesMagnetic Lock CE EMC Test Report E160510426Moraru PAPas encore d'évaluation

- Tps40057 Data SheetDocument41 pagesTps40057 Data SheetDwp BhaskaranPas encore d'évaluation

- Verilog Interview Questions With Answers!Document42 pagesVerilog Interview Questions With Answers!Vinod Lk95% (56)

- Power Samson Servo 170 - ManualDocument16 pagesPower Samson Servo 170 - ManualKlass DrumsPas encore d'évaluation

- Technical Manual 5050 MAN0005391Document92 pagesTechnical Manual 5050 MAN0005391Lin LinPas encore d'évaluation

- Vivaldi1 5to15Document2 pagesVivaldi1 5to15Concerned CitizenPas encore d'évaluation

- Radio PPT 1Document30 pagesRadio PPT 1ShrayGupta100% (1)

- Laboratory 2 Hall-Effect Sensors: ME 104 Sensors and Actuators Fall 2003Document13 pagesLaboratory 2 Hall-Effect Sensors: ME 104 Sensors and Actuators Fall 2003Jalaj JainPas encore d'évaluation

- OpAmp F10Document32 pagesOpAmp F10Suguna PriyaPas encore d'évaluation

- Double Integral SMCDocument11 pagesDouble Integral SMCrida abbasPas encore d'évaluation

- Adc ProgramDocument3 pagesAdc ProgramMallikarjun DeshmukhPas encore d'évaluation

- Lecture20 Memory PDFDocument37 pagesLecture20 Memory PDFKarl ArschPas encore d'évaluation

- Designing Multi Layer To Balance SI by LeeRitcheyDocument85 pagesDesigning Multi Layer To Balance SI by LeeRitcheyram100% (1)