Académique Documents

Professionnel Documents

Culture Documents

06-Condensadores Integrados

Transféré par

Cesar SaucedoDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

06-Condensadores Integrados

Transféré par

Cesar SaucedoDroits d'auteur :

Formats disponibles

Tecnologa Microelectrnica Pagina Condensadores Integrados Seccin 6

1

6- CONDENSADORES INTEGRADOS

Los condensadores en los circuitos integrados se fabrican empleando la capacitancia de la regin de deplexion de una unin PN con

dolarizacin inversa.

Figura N 6.1(a) CONDENSADOR INTEGRADO TIPO UNIN

Figura N 6.1(b) CIRCUITO EQUIVALENTE (Cortesa de Motorola Inc)

6.1- Condensador de Unin [1]

La figura 6.1(a) representa la seccin transversal de un condensador de unin. El condensador esta formado por la unin con

polarizacin inversa J

2

que separa la capa epitaxial de tipo N de la superior de difusin de tipo P. Aparece una unin adicional J

1

entre el plano epitaxial de tipo N y el sustrato, y una capacidad parsita C

1

relacionada con esta unin polarizada en sentido inverso.

El circuito equivalente de este condensador de unin puede verse en la figura 6.1(b) en el que la capacidad deseada C

2

debe ser tan

grande como sea posible con relacin a C

1

. El valor de C

2

depende de la superficie de la unin y de la concentracin de impurezas.

Esta unin es linealmente gradual. La resistencia R en serie entre 10 y 50 , representa la resistencia de la capa tipo N. Es evidente

que el sustrato debe estar a la tensin ms negativa para minimizar C

1

y aislar el condensador de los dems elementos manteniendo la

unin J

1

con polarizacin inversa. Puntualicemos que el condensador de unin C

2

esta polarizado ya que la unin PN J

2

siempre esta

con polarizacin inversa.

En resumen y visto de otra manera [1], esta claro que el equivalente de capacitores se logra en circuitos integrados, con junturas

polarizadas en inversa. En una juntura PN, la regin P tiene alta densidad de lagunas y la tipo N alta densidad de electrones. En la

juntura misma hay una zona de carga espacial (zona desierta o de transicin) con carga positiva de un lado y negativa del otro. En

equilibrio trmico, el fuerte campo elctrico existente en esa zona de transicin evita que se difundan las lagunas en la zona tipo N y

los electrones en la zona tipo P. La zona de carga espacial en la juntura PN se comporta como un capacitor de placas paralelas. El

ancho de la zona desierta es equivalente a la separacin entre placas, la nica diferencia consiste en que en este caso el dielctrico es

silicio. Un hecho caracterstico de las junturas PN de silicio es que la zona de transicin se extiende mas hacia el lado de la juntura

que tiene menor concentracin de impurezas (mayor resistividad). Debe observarse tambin que el ancho de la zona de transicin es

funcin de la tensin aplicada. Esta tensin en una juntura abrupta varia como la raz cuadrada de la tensin. La capacitancia formada

por la zona desierta para una juntura gradual es:

Tecnologa Microelectrnica Pagina Condensadores Integrados Seccin 6

2

[ ] farads

V

M q

C

r

. 2

. . .

0

=

0

= Permitividad del vaco 8,85 x 10

-14

F / cm.

r

= Constante Dielctrica del Silicio = 12.

V = Tensin inversa aplicada + potencial de contacto de 0,6 volt.

q = Carga del Electrn 1,6 x 10

-19

coulomb.

M = Concentracin de impurezas del lado menor.

Debido a la alta constante dielctrica del silicio, se pueden obtener altos valores de capacitancia por unidad de superficie. La ecuacin

es suficientemente exacta como para dar aproximaciones de primer orden al calcular la capacidad.

La tabla 1 indica valores tpicos de capacidad por unidad de superficie que se obtienen en estructuras integradas monolticas

Ejemplo: Para la juntura base-colector si la superficie real de la juntura es de 1.3 mm

2

y la tensin V

AB

= 0v

cunto vale la capacidad?

Vemos que para la juntura dada la capacidad por mm

2

es 308 luego C= 308 x 1,3 = 400.4 pF

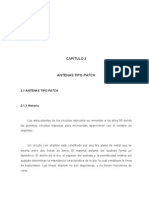

6.2-Condensadores MOS y de Pelcula Delgada

La figura 6.2(a) representa un condensador MOS no polarizado. Esta estructura es la de un condensador plano paralelo con SiO

2

como dielctrico de un espesor de 500 ngstrom. La placa superior es una fina pelcula superficial metlica de aluminio. La placa

inferior es la regin n

+

fuertemente dopada que se forma durante la difusin (implantacin) de emisor en un proceso bipolar o durante

la implantacin de las regiones de drenaje y fuente en los procesos MOS. El circuito equivalente del condensador MOS es el de la

figura 6.2(b) en el que C

1

representa la capacidad parsita de la unin colector-sustrato, y R la pequea resistencia en serie de la

regin n

+

.

Obsrvese que la placa superior no es necesariamente metlica sino que puede ser la capa de polisilicio empleada para formarlas

regiones de puerta del transistor MOS. Algunos procesos industriales de fabricacin MOS emplean dos capas de polisilicio teniendo

as una capa adicional para las interconexiones entre los componentes. Las dos capas de polisilicio estn separadas por una ligera zona

de SiO

2

lo que forma un condensador figura 6.3. A los condensadores construidos de esta forma se les denomina condensadores poli-

poli.

Los condensadores de pelcula delgada PD se fabrican de forma similar a los condensadores MOS. Se vaporiza una pelcula

conductora (placa superior) sobre la capa de SiO

2

el dielctrico, y la placa inferior la forma la regin n

+

fuertemente dopada debajo

del oxido. La capacidad del condensador MOS o de unin es bien pequea, generalmente del orden de 4 x 10

-4

pF / m

2

.

Tecnologa Microelectrnica Pagina Condensadores Integrados Seccin 6

3

Figura N 6.2(a) CONDENSADOR MOS: ESTRUCTURA EN CORTE

Figura N 6.2(b) CONDENSADOR MOS: CIRCUITO EQUIVALENTE

Figura N 6.3 Condensador MOS formado de dos capas de Polisilicio.

Un condensador de 40 pF ocupa un rea de 10

5

m

2

o cubre un rectngulo de 1 x 0,1 mm sobre la superficie del chip. La mayor parte

de los condensadores integrados son de menos de 100 pF. Se han conseguido valores por encima de los 500 pF pero solo a expensas

de ocupar la mayor parte del rea del chip. El empleo de pelculas de tantalio puede aumentar 10 veces la capacidad por unidad de

superficie. Como dielctrico se recrece una capa bien controlada de peroxido de tantalio Ta

2

O

5

, y para la placa superior se deposita

tantalio metlico, pues el aluminio es soluble en el Ta

2

O

5

. El aumento de la capacidad se obtiene a expensas de nuevos pasos en el

proceso.

[1] La fabricacin de capacitores de PD obedece a superar algunas limitaciones impuestas por los capacitores de juntura. Estos

capacitores son no polarizados y la capacidad es independiente de la tensin aplicada. Las caractersticas de ruptura y el factor de

perdidas son mejores que en los de juntura. El capacitor C dela figura 6.2(b) esta formada por aluminio depositado sobre el oxido. El

valor de C esta dado por: el rea del aluminio depositado, el espesor de la capa de oxido y su constante dielctrica. Se puede lograr

una capacidad por unidad de superficie del orden de 308 a 769 pF / mm

2

. Para una capacidad determinada, se trata de usar una capa

de oxido sumamente delgada para reducir el rea de aluminio requerida. La mxima capacidad disponible esta limitada a algunos

cientos de pF debido a microperforaciones en el oxido, con los cortocircuitos asociados y consideraciones de produccin debido al

tamao de las orejas de conexin requeridas. Nuevamente aparece una capacidad C

1

en la figura 6.2(b) debida a la juntura del

sustrato, que debe tomarse en cuenta en el diseo del circuito.

6.3 PROCESO DE DEPOSICIN DIELECTRICO [4]

Los materiales inorgnicos son depositados por medio de uno a tres procesos:

1- Proceso de pelcula gruesa: sopleteado spray, mascara y sedimentacin.

2- Sputtering, Deposicin electrnica.

Tecnologa Microelectrnica Pagina Condensadores Integrados Seccin 6

4

3- Deposicin de vapor qumico.

1- El sopleteado con mascara es un proceso limitado para espesores de 1,5 a 25 m y es similar al proceso de

pelcula gruesa. El proceso de sedimentacin ilustrado en figura 6.4 requiere la formacin y dispersin de

partculas de tamao del orden de micronesimas incluidas en un solvente orgnico seguido de centrifugado para

obtener pelculas finas y compactas.

2- La deposicin de vapor qumico implica la formacin de compuestos voltiles de metales seguido de

oxidacin del metal para formar una cermica. Dos ejemplos de dielctricos inorgnicos son ilustrados en

tabla 2.

El proceso de pelcula delgada de la figura 6.5 implica su formacin con Au otro conductor para lneas por

uno de los dos procesos en este capitulo seguido por impreso con mascara y secado de dielctrico inorgnico

fotosensitivo que luego se lo expone a travs de la mascara por luz UV. Se elimina el dielctrico segn el

diseo. Es razonable pensar que este procedimiento sea aplicado en pelcula gruesa de conductores como se

hace en PD.

Figura N 6.4 Proceso de Sedimentacin para Deposicin de Pelcula de Vidrio

Tecnologa Microelectrnica Pagina Condensadores Integrados Seccin 6

5

Figura N 6.5 Proceso Pelcula Delgada Dielctrico (cortesa NEC Co)

Tabla 2 Procesos de Pelculas Delgadas de Dielctricos Inorgnicos[4]

Aislador Al + Cu BN + Au

Numero de capas 5 5

Material Al N BN

Espesores 0,5 m / capa 0,2 m / capa

Mtodo de formacin Sputtering CVD

Conductor

Material Cu Au

Ancho de la traza 20 m 20 m

Medida de vaciado 20 m 20 m

La estructura planar de mltiples pelculas delgadas inorgnicas implica o supone la planarizacion qumica,

mecnica o la combinacin de procesos de planarizados. Tales procesos desarrollados en la dcada del setenta

empleaban la deposicin de vidrios boro silicato, la expresin por medios trmicos adoptados a sustratos de

alumina, con constante dielctrica reducida. Estos materiales estn procesados en una atmsfera de N

2

(nitrgeno) seguidos de H

2

por encima de 50C, pues por debajo de esa temperatura se ablanda y vaporiza el N

2

.

Este proceso se muestra en el figura 6.6 lo que implica la deposicin por bloques de cromo-cobre-cromo,

seguido de cobreado previo a la deposicin y disparos de vidrio de alrededor de 800C. L estructura se

maquina para aplanar la superficie despus del depositado de vidrio. Un total de cinco capas de vidrio y cinco

Tecnologa Microelectrnica Pagina Condensadores Integrados Seccin 6

6

de cobre metalizado, se llegan a formar de esta forma. La desventaja es que al depositar una nueva capa a alta

temperatura, puede afectar la capa anterior ablandndola y produciendo globos en el material de vidrio y

adems algn desplazamiento de las lneas de conductores. Esto se puede resolver empleando vidrio-cermica

La mejor ventaja es la compatibilidad trmica del conjunto de materiales desde la alumina al vidrio, habiendo

tambin estabilidad trmica permitiendo procesos de juntura estables por encima de los 800C.

Los defectos de la vitrificacin con vidrio son resueltos mediante el uso de virio cristalizado reduciendo costos

en mdulos de multinivel en multichip. La construccin de esta estructura se ve en la figura 6.7 en donde los

conductores de cobre estn formados por medio de mascaras de impresin sobre la que se proyecta el cobre,

seguido por nitrgeno-vidrio cristalizado proyectado como disparos sobre los huecos de la mascara. La

cubierta de vidrio-cermica es suavizada por una delgada cubierta de vidrio. Seguidamente la pelcula delgada

de Ta

2

N / NiCr / Au depositado del cableado, es baada con oro Au.

La figura 6.8 muestra como se cubren los conductores depositados, por una pelcula delgada dielctrica:

poliamida.

Figura N 6.6 Proceso Cobre-Vidrio

Secuencia Multicapa Pelcula Delgada

Tecnologa Microelectrnica Pagina Condensadores Integrados Seccin 6

7

Figura N 6.7 Fabricacin de Pelcula Gruesa y Fina Sustrato Multicapa (Cortesa Fujitsu Ltd)

Figura N 6.8 Deposicin Dielctrica y Plantillado

Tecnologa Microelectrnica Pagina Condensadores Integrados Seccin 6

8

6.4 MARGENES DE FUNCIONAMIENTO SEGN EL PROCESO DE DEPOSITADO[ 11 ]

Pag. 37 Bierman R. Scot, Don W. Brooks, Texas Instruments Inc. Dallas Texas

Generalmente se atribuye la excesiva baja tensin de sustrato entre resistencias o capacitores difundidos y el

sustrato a imperfecciones en la juntura. La ruptura respecto al sustrato en dispositivos difundidos es un

problema de rendimiento que aumenta con la superficie de la juntura difundida y la tensin de trabajo. El

problema se puede eliminar usando componentes pasivos de PD. Sobre la capa de Oxido de Silicio. La tensin

de ruptura de la capa de Si O

2

est en el orden de 200 a 1000 volt.

Se puede elegir una gran cantidad de materiales para resistores de PD. El resistor de Ni-Cr de PD fue

experimentado durante muchos aos y probo ser muy til para su aplicacin en CI. El resistor de Cermet Ta /

Ta

2

O

3

que se muestra en lnea punteada en la figura 6.9.

Figura N 6.9 Mrgenes de resistencia

Laminar para materiales difundidos de PD y Cermet (metal-cermica)

-------------------------------------------

La resistencia laminar til de un resistor difundido esta limitado a 10 - 250 ohm/cuadro para la mayora de las

aplicaciones. Aunque se pueden conseguir mayores resistencias laminares, es difcil mantener la tolerancia y

otras caractersticas como el Coeficiente de Temperatura, quedan severamente degradados. El diseo de

resistores difundidos en la mayora de las aplicaciones esta gobernado por la difusin de base de transistores.

La resistencia laminar es de 80 a 200 ohm/cuadro. Los resistores de Ni-Cr se fabrican entre 1 - 300 ohm /

cuadro, con rendimientos compatibles con el el procesado de CI. Los resistores de Cermet pueden estar

compuestos de Cr-SiO

2

Ta Ta

2

O

5

y su resistencia laminar se aproximan a 1000 - 5000 ohm/cuadro. El

resistor de Cermet tiene un coeficiente de temperatura CT bajo y alta resistencia laminar. El CT de la

resistencia puede ser un factor de rechazo si el circuito debe funcionar en un margen de temperaturas. Un

resistor con un CT de 1000 ppm/C cambia de valor en un 10% dentro de un limite de temperaturas de 100C.

La contraparte de PD con un CTR de 50 ppm/C varia solo un 0,5% en el mismo margen. La figura 6.10

indica que el CTR de resistores difundidos puede llegar a ser de hasta 2000 a 2500 ppm/C positivo o negativo

segn la impurificacin y la resistencia laminar.

Figura N 6.10 El Efecto de la Temperatura

En la resistencia en resistores difundidos esta entre los limites de - 2000 a + 1000 ppm/C dependiendo de la

impurificacin y la resistencia laminar.

----------------------------------------------------------------------------------------

Sin embargo el resistor difundido que se usa en general tiene un CTR de - 2000 a + 1000 ppm/C.

6.4.1 Limites de Frecuencia de resistores Peliculares

En la figura 6.11 se muestra que el limite practico de Alta Frecuencia esta en 1 GHz para el resistor de Ni-Cr

y 20 MHz para el resistor Difundido.

Tecnologa Microelectrnica Pagina Condensadores Integrados Seccin 6

9

Figura N 6.11 El Limite Practico de Alta Frecuencia

En resistores se define como 0,707 del valor en corriente continua.

-------------------------------------------------------------------------------------

El limite de alta frecuencia de un resistor difundido puede variar ya que la frecuencia a la cual la resistencia

comienza a disminuir depende del nivel de impurificacin y de la dolarizacin. Con un diseo optimo del

resistor difundido se podra extender el limite de frecuencia de trabajo, pero esto no es practico en CI porque

compromete el diseo del transistor.

En la figura 6.12 se indica la capacidad por unidad de superficie para los tres tipos de Capacitores

Figura N 6.12 La capacidad por Unidad de Superficie

Del Ta

2

O

5

es altamente promisoria.

------------------------------------------------------------

El capacitor difundido difundido puede llegar a 750 pF/mm2 aunque se fabrican capacitores de 1200 pF/mm

2

.

El capacitor de PD puede dar 900 pF/mm

2

con dielctrico de Ta

2

O

5

se han obtenido valores de 3800 pF/mm

2

.

El capacitor MOS tiene una capacidad inferior al tipo difundido. Esto es cierto para un capacitor MOS de 300

pF/mm

2

insensible a la tensin operando en el margen de 0 a 10 v.

Figura N 6.13 La sensibilidad a la tensin de Capacitores

Hechos por tcnicas de difusin y PD. No se muestran capacitores MOS ya que la relacin depende del proceso

de fabricacin.

----------------------------------------------------------------------------------------

Se puede aumentar la capacidad por unidad de superficie pero a costa de un rpido incremento en la

sensibilidad a la tensin aplicada. En la figura 6.13 puede observarse la sensibilidad a la tensin de los tres

tipos de capacitores a 300 pF/mm

2

. La estructura difundida con una resistividad de 1 ohm.cm tipo n 3

ohm.cm tipo p es la ms sensible. Se muestra la dependencia de la inversa de la raz cbica esperada de la

capacidad con respecto a la tensin. No se muestra la relacin capacidad-tensin del capacitor MOS ya que

Tecnologa Microelectrnica Pagina Condensadores Integrados Seccin 6

10

esta depende mucho del proceso de fabricacin. El capacitor MOS se describe generalmente como un capacitor

serie de capa de oxido y empobrecimiento. Deben tenerse en cuenta sin embargo los efectos de los estados

superficiales ya que a menudo enmascaran la relacin C / V antes mencionada.

6.4.2 Efecto de la Temperatura en Capacitores Difundidos

El coeficiente de temperatura de la capacidad CTC del capacitor difundido se considera generalmente un orden

de magnitud mayor que el de los capacitores de PD. Tal como se ve en la figura 6.14. El CTC de capacitores

MOS depende de cmo se hizo crecer el oxido, del espesor del mismo y de su contenido de humedad. Esta

entre 5 y 300 ppm/C.

Figura N 6.14 El efecto de la temperatura sobre la capacidad

Es menor para el tipo de Si O

2

.

El CTC de capacitores de PD de Si O

2

varia entre 6 y 30 ppm/C. La figura 6.15 muestra la dependencia de

la frecuencia del factor de disipacin. Este factor es del mismo orden de magnitud a baja frecuencia para

capacitores de PD y MOS mientras que el factor de disipacin (fd) del capacitor difundido es mucho mayor.

Este factor limita el uso de capacitores difundidos a frecuencias ms altas ya que su fd es 0,1 apenas por

encima de 1 MHz. En todos los capacitores las perdidas ohmicas en los terminales y en las placas

incrementan el fd.

Figura N 6.15 Un aumento lineal en el Factor de Disipacin

De capacitores difundidos limitan la frecuencia til.

En la figura 6.16 se ilustra esta dependencia respecto de la resistencia serie para un capacitor ideal. El fd

disminuye casi un orden de magnitud con un decrecimiento similar de la resistencia serie. El diseo de

capacitores MOS es critico en lo que respecta al fd. El capacitor debe tener baja resistencia laminar para

disminuir Rs y mantener bajo el fd. El alto fd del capacitor difundido mostrando en la figura 6.16 se debe a

una Rs de 102 ohms.

Este valor es mas de un orden de magnitud mayor que en el capacitor MOS o el de PD. De hecho casi siempre

es alto, ya que la porcin del capacitor que se forma durante la difusin del colector tiene alta resistencia

laminar. Al disear capacitores difundidos para alta frecuencia, deben considerarse tambin la geometra y el

nivel de impurificacin del silicio. La capacidad de un cuerpo de Si O

2

es lineal hasta 25 GHz y se encuentra

que los capacitores de PD son lineales hasta una frecuencia de 2GHz tal como se muestra en la figura 6.17

limitada solo por la inductancia del encapsulado. Los capacitores MOS tipo p de 100 .cm estn limitados en

Tecnologa Microelectrnica Pagina Condensadores Integrados Seccin 6

11

capacidad a una frecuencia menor que 100 KHz. Los capacitores tipo p de 1 ohm.cm exceden ese limite tal

como se observa en la figura 6.17.

Figura 6.16 Efecto de la Resistencia Serie

Sobre las placas del capacitor.

--------------------------------------------------------

Figura N 6.17 El limite practico de Alta Frecuencia

en capacitores de PD esta fijado por la inductancia de los terminales y el encapsulado.

------------------------------------------------------------------------------------------------------

Vous aimerez peut-être aussi

- 04-Fabricacion Del FETDocument8 pages04-Fabricacion Del FETAlex EdUu NúñezPas encore d'évaluation

- Proceso de Fabricación Del BJT y MOSDocument7 pagesProceso de Fabricación Del BJT y MOSAlber Lim GboPas encore d'évaluation

- CAPACITORESDocument11 pagesCAPACITORESAngie León100% (1)

- Caracterización química, morfológica y estructural de materialesD'EverandCaracterización química, morfológica y estructural de materialesPas encore d'évaluation

- Proceso de Fabricacion Del BJTDocument1 pageProceso de Fabricacion Del BJTCristhoper Paucar Huallpa0% (1)

- Proyectos de instalaciones eléctrica de baja tensiónD'EverandProyectos de instalaciones eléctrica de baja tensiónÉvaluation : 5 sur 5 étoiles5/5 (1)

- Fabricación de TransistoresDocument2 pagesFabricación de TransistoresChilo Enrique AntPas encore d'évaluation

- 03-Fabricacion de Transistores BipolaresDocument5 pages03-Fabricacion de Transistores BipolaresManuel Rubin de CelisPas encore d'évaluation

- Interpretación de planos en soldadura. FMEC0210D'EverandInterpretación de planos en soldadura. FMEC0210Évaluation : 4.5 sur 5 étoiles4.5/5 (3)

- Tipos de CapacitoresDocument19 pagesTipos de CapacitoresAlberto SánchezPas encore d'évaluation

- Celdas Solares de Silicio Fundamento y Tendencia IMPORTANTEDocument13 pagesCeldas Solares de Silicio Fundamento y Tendencia IMPORTANTEArob BoraPas encore d'évaluation

- Tipos de CapacitoresDocument17 pagesTipos de CapacitoresYuri Hernandez100% (1)

- Determinacion Del Angulo y Factor de Perdidas de Un CondensadorDocument23 pagesDeterminacion Del Angulo y Factor de Perdidas de Un CondensadorNicholas EvansPas encore d'évaluation

- Tecnicas Fabricacion CIDocument8 pagesTecnicas Fabricacion CILuis Francisco Amores TapiaPas encore d'évaluation

- Parte 2 Detectores de SemiconductoresDocument30 pagesParte 2 Detectores de SemiconductoresYenny EstradaPas encore d'évaluation

- Calculo Resistencia de Puesta A TierraDocument10 pagesCalculo Resistencia de Puesta A TierraDanilo QuevedoPas encore d'évaluation

- Circuito IntegradoDocument16 pagesCircuito Integradord20081587100% (1)

- Tecnica e Fabricacion CMOSDocument6 pagesTecnica e Fabricacion CMOSJuan CandanedoPas encore d'évaluation

- ACTIVIDAD1Document8 pagesACTIVIDAD1Luis Angel CarballoPas encore d'évaluation

- Curvas Características Del MOSFET de VaciamientoDocument12 pagesCurvas Características Del MOSFET de VaciamientoNoe Sanchez HernandezPas encore d'évaluation

- Comsol Software de Simulacion de Corrosion PDFDocument7 pagesComsol Software de Simulacion de Corrosion PDFCarmen MarcanoPas encore d'évaluation

- 2.2 CapacitanciaDocument25 pages2.2 CapacitanciaAlberto Lujan100% (1)

- Data SheetDocument13 pagesData SheetEstebanPas encore d'évaluation

- GUIA de ESTUDIO Respondida YanniDocument16 pagesGUIA de ESTUDIO Respondida Yanniyannifer mercadoPas encore d'évaluation

- 07-Ingenieria de Los Ci y MicroelectronicaDocument16 pages07-Ingenieria de Los Ci y Microelectronicascribd_lostandfoundPas encore d'évaluation

- Cálculo de TransformadorDocument5 pagesCálculo de TransformadorCharles DPas encore d'évaluation

- Clase 22 Circuitos Integrados y Dispositivos Semi ConductoresDocument11 pagesClase 22 Circuitos Integrados y Dispositivos Semi ConductoresnamimddPas encore d'évaluation

- MosfetDocument5 pagesMosfetBob BakerPas encore d'évaluation

- Resumen LibroDocument6 pagesResumen LibroKoki De la CruzPas encore d'évaluation

- Tipos de Capacitores y Sus CaracteristicasDocument8 pagesTipos de Capacitores y Sus CaracteristicasIvan Arevalo0% (1)

- Condensador EléctricoDocument8 pagesCondensador EléctricoYraimaPas encore d'évaluation

- Reporte Celdas Solares de SilicioDocument6 pagesReporte Celdas Solares de SilicioCamilo Andrés PeñaPas encore d'évaluation

- MOSFETDocument21 pagesMOSFETYAMIR SANDOVALPas encore d'évaluation

- Cap 6Document42 pagesCap 6Casas Churqui JessePas encore d'évaluation

- Factores de Perdida ElectricaDocument7 pagesFactores de Perdida ElectricaAngel RojasPas encore d'évaluation

- Informe #5 - Carga de CondensadoresDocument15 pagesInforme #5 - Carga de CondensadoresWilliam's Limonchi SandovalPas encore d'évaluation

- APUNTES MAQUINAS ELECTRICAS - U 1y2 v1.1Document61 pagesAPUNTES MAQUINAS ELECTRICAS - U 1y2 v1.1Darwin GualotoPas encore d'évaluation

- Fabricación de Dispositivos SemiconductoresDocument12 pagesFabricación de Dispositivos SemiconductoresHamilton AmadoPas encore d'évaluation

- Tecnologia Planar Transistor NPNDocument12 pagesTecnologia Planar Transistor NPNNatalia Moral FlorPas encore d'évaluation

- Trabajo #6 Física IIIDocument10 pagesTrabajo #6 Física IIILeonardo Reyes100% (4)

- Fabricacion de Capacitores y Manufactura de Capacitadores de Dimensiones PequeñasDocument21 pagesFabricacion de Capacitores y Manufactura de Capacitadores de Dimensiones Pequeñasreyli9490% (10)

- Condensadores (Resumen)Document8 pagesCondensadores (Resumen)reolokPas encore d'évaluation

- Previo Poteccion CatodicaDocument9 pagesPrevio Poteccion CatodicaAzv FentanesPas encore d'évaluation

- Equipo3. Analizar y Exponer Sobre La Polarización Del BJTDocument12 pagesEquipo3. Analizar y Exponer Sobre La Polarización Del BJTERICK DANIEL DAGIO DIAZPas encore d'évaluation

- Guia No 8 TransformadoresDocument46 pagesGuia No 8 TransformadoresHerney Lopez0% (1)

- ComsolDocument11 pagesComsolkevin100% (1)

- 03ckt13pdf LabDocument8 pages03ckt13pdf LabFernando ArmoaPas encore d'évaluation

- Tipos de CapacitoresDocument10 pagesTipos de CapacitoresGiovanny CifuentesPas encore d'évaluation

- APUNTES MAQUINAS ELECTRICAS - U 1y2 v1.1Document61 pagesAPUNTES MAQUINAS ELECTRICAS - U 1y2 v1.1elmenperu100% (1)

- Electricidad Teórico Práctica V-Leccion22 PDFDocument43 pagesElectricidad Teórico Práctica V-Leccion22 PDFcms124dPas encore d'évaluation

- Ucontrol Revista 0008Document60 pagesUcontrol Revista 0008miguel lazarte chavezPas encore d'évaluation

- MOSFET de PotenciaDocument12 pagesMOSFET de PotenciaWladimir ChillánPas encore d'évaluation

- Antenas Tipo PATCHDocument26 pagesAntenas Tipo PATCHArley Machado BedoyaPas encore d'évaluation

- Condensadores PDFDocument14 pagesCondensadores PDFRolando Choque HuarcayaPas encore d'évaluation

- Portada Manga Vol. 13 Trinity SevenDocument1 pagePortada Manga Vol. 13 Trinity SevenCesar SaucedoPas encore d'évaluation

- Metal Gear Solid 5 - Cap 4Document2 pagesMetal Gear Solid 5 - Cap 4Cesar SaucedoPas encore d'évaluation

- Kv21fa310-29fa310 LaDocument56 pagesKv21fa310-29fa310 LaJames NaitroPas encore d'évaluation

- Fate-Kaleid Liner Prisma IllyaDocument5 pagesFate-Kaleid Liner Prisma IllyaCesar SaucedoPas encore d'évaluation

- Unidad 2-1 Inteligencia ArtificialDocument2 pagesUnidad 2-1 Inteligencia ArtificialCesar SaucedoPas encore d'évaluation

- Manual de Ensamblador-TasmDocument17 pagesManual de Ensamblador-Tasmomarwolf_92100% (1)

- La Muerte MadrinaDocument1 pageLa Muerte MadrinaCesar SaucedoPas encore d'évaluation

- Tarea de Potencial Electrico y Ley de OhmDocument11 pagesTarea de Potencial Electrico y Ley de OhmCesar Saucedo0% (1)

- Presentación Bien de Procesos Ligeros Hilos o HebrasDocument12 pagesPresentación Bien de Procesos Ligeros Hilos o HebrasCesar Saucedo100% (1)

- Em Plea DoDocument6 pagesEm Plea DoCesar SaucedoPas encore d'évaluation

- Con Los Datos Obtenido y Calculados. Ordénelos en Las Tablas DadasDocument8 pagesCon Los Datos Obtenido y Calculados. Ordénelos en Las Tablas DadasAnderszon AndradePas encore d'évaluation

- Momento LinealDocument23 pagesMomento LinealISABELPas encore d'évaluation

- Elasticidad Cinta de GomaDocument3 pagesElasticidad Cinta de GomadfgjPas encore d'évaluation

- Concepto de ANPA y Curva ANPADocument3 pagesConcepto de ANPA y Curva ANPAJorge Fernandez EdelmanPas encore d'évaluation

- Formulas Globalizador ResistenciaDocument9 pagesFormulas Globalizador ResistenciaFrancisco NavarroPas encore d'évaluation

- Examen MaquinasDocument6 pagesExamen MaquinasDana GalvezPas encore d'évaluation

- Problemas Unidad 1 DesarrolloDocument5 pagesProblemas Unidad 1 DesarrolloGabriela ChiffellePas encore d'évaluation

- Vibraciones TextoDocument24 pagesVibraciones TextoLuis VillarroelPas encore d'évaluation

- Carga Eléctrica y Campo Electrico - PlataformaDocument4 pagesCarga Eléctrica y Campo Electrico - PlataformaPool BreakPas encore d'évaluation

- Proceso Tostacio N Molibdeno AltonorteDocument39 pagesProceso Tostacio N Molibdeno AltonorteLuis Felipe SAPas encore d'évaluation

- FISICA II Informe N 05Document7 pagesFISICA II Informe N 05Edu A Pari CondoriPas encore d'évaluation

- Mapa Conceptual Unidad 2Document1 pageMapa Conceptual Unidad 2Fernando MontalvanPas encore d'évaluation

- 6 Carta PsicrometricaDocument42 pages6 Carta Psicrometricaluis0% (1)

- Campos Magneticos - Ley de Biot y SavartDocument38 pagesCampos Magneticos - Ley de Biot y SavartAndres Bautista PPas encore d'évaluation

- Pelandintecno - 2ESO-T6 - Electricidad - 2019v2Document12 pagesPelandintecno - 2ESO-T6 - Electricidad - 2019v2Alan ChávezPas encore d'évaluation

- Educacion Fisica, Debates y Tensiones - Memoria Academica FahceDocument10 pagesEducacion Fisica, Debates y Tensiones - Memoria Academica FahceJuliaPas encore d'évaluation

- Formulación de Preguntas Laboratorio Tensión PuraDocument1 pageFormulación de Preguntas Laboratorio Tensión PuraMauro Alejandro Silva HoyosPas encore d'évaluation

- Laboratorio de Fisica 1-2Document3 pagesLaboratorio de Fisica 1-2Joe OrtizPas encore d'évaluation

- IntroducciónDocument7 pagesIntroducciónNadia HuertasPas encore d'évaluation

- L7 Reactancia PotierDocument6 pagesL7 Reactancia PotierMelissa ZepitaPas encore d'évaluation

- Fisica Guias 10 y 11 (2020)Document20 pagesFisica Guias 10 y 11 (2020)kogui de mulkwakunguiPas encore d'évaluation

- Limite de OperacionDocument8 pagesLimite de OperacionCalixto TorresPas encore d'évaluation

- Péndulo ElectrostaticoDocument4 pagesPéndulo ElectrostaticoSamuelPas encore d'évaluation

- Producción de EnergíaDocument44 pagesProducción de EnergíacuriosityPas encore d'évaluation

- El Enlace CovalenteDocument13 pagesEl Enlace CovalenteSofía DiazPas encore d'évaluation

- Cinematica, Movimiento ParabólicoDocument5 pagesCinematica, Movimiento Parabólicoroberto hsPas encore d'évaluation

- Análisis y Conclusiones Del Funcionamiento Del Dipolo EléctricoDocument6 pagesAnálisis y Conclusiones Del Funcionamiento Del Dipolo EléctricoTaty RodriguezPas encore d'évaluation

- Informe de Péndulo SimpleDocument16 pagesInforme de Péndulo SimpleAndreinä SilväPas encore d'évaluation

- Quimica 1 Conversiones de Unidades - DensidadDocument3 pagesQuimica 1 Conversiones de Unidades - DensidadLUIS FERNANDO VASQUEZ ROMEROPas encore d'évaluation