Académique Documents

Professionnel Documents

Culture Documents

Digital circuit timing analysis and constraints

Transféré par

shrish9999Description originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Digital circuit timing analysis and constraints

Transféré par

shrish9999Droits d'auteur :

Formats disponibles

Jon Turner

Setup and hold time constraints

Input timing constraints

Clock period analysis

Metastability and synchronizer reliability

Timing Issues in

Digital Circuits

2

Edge-Triggered D Flip Flop

D lip lop stores !alue at D input

"hen clock rises

Most "idely used storage element

or se#uential circuits

Propagation time is time rom rising

clock to output change

I input changes "hen clock rises$

ne" !alue is uncertain

output may oscillate or may remain at

intermediate !oltage %metastability)

D Q

Q >C

&

Timing rules to a!oid metastability

' D input must be stable or setup time beore rising clock edge

' must remain stable or hold time ollo"ing rising clock edge

C

D

Q

setup

hold

min, max propagation delay

(

Implications o Setup Time Constraints

D Q

Q >C

D Q

Q >C

clock

source

combinational

circuit path

x

y

clk

y

x

period

flip flop prop delay

comb circuit delay

setup time

! clock ske"

To a!oid setup time !iolations$ re#uire

period ) %ma* FF prop+ delay, - %ma* comb+ circuit delay,

- %FF setup time, - %ma* clock ske",

C.D tools can check all FF-to-FF paths to !eriy

both component delays and "iring delays matter

accurate estimate re#uires component locations and

inormation about routing o "ires

/

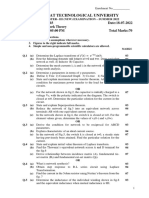

Clock 0eriod .nalysis rom Synthesis

=======================================================================

Timing constraint: Default period analysis for Clock 'clk'

Clock period: 4.227ns (frequency: 2!."!#$%&'

Total num(er of pat)s * destination ports: 4" * "

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

Delay: 4.227ns (,e-els of ,ogic = '

.ource: state/00d1 (00'

Destination: cnt/2 (00'

.ource Clock: clk rising

Destination Clock: clk rising

Data 2at): state/00d1 to cnt/2

3ate 4et

Cell:in+5out fanout Delay Delay ,ogical 4ame (4et 4ame'

++++++++++++++++++++++++++++++++++++++++ ++++++++++++

0D6:C+57 8 #.!2! 1.12" state/00d1 (state/00d1'

,9T2::1+5; 1 #.478 #.74# /mu<###1=252#/.># (412'

,9T4/,::2+5,; 1 #.478 #.12 /mu<###1=2524/.># (4118'

,9T4::+5; 1 #.478 #.### /mu<###1=254 (/mu<###1=25'

0D.:D #.17! cnt/2

++++++++++++++++++++++++++++++++++++++++

Total 4.227ns (2.28ns logic? 1.8@@ns route'

(".#A logic? 47.#A route'

=======================================================================

synthesis estimates only1

placement and routing

inormation needed or

accurate analysis

FF setup

time

2

Implications o 3old Time Constraints

D Q

Q >C

D Q

Q >C

clock

source

combinational

circuit path

x

y

To a!oid hold time !iolations$ re#uire

hold time 4 %min FF prop+ delay,

- %min comb+ circuit delay, 5 %ma* clock ske",

C.D tools can check all FF-to-FF paths to !eriy

In F60.s$ it is oten the case that

hold time 7 %min FF prop+ delay, 5 %ma* clock ske",

so$ hold time !iolations cannot occur

clk

y

x

hold time

ff delay

cc delay

8

Input Timing

Setup and hold times constrain "hen inputs to a

circuit can change

stable period starts at clock 5 %setup - ma* delay,

and lasts until clock - hold 5 %min delay,

Common simpliication is to hold input stable rom

clock 5 %setup - ma* delay, until clock

D Q

>C

D Q

>C

clock

max

delay path

x

y

min

delay path

#

clk

y,# stable

max delay

x stable

min delay

setup hold

9

Input Delay .nalysis rom Synthesis

=========================================================================

Timing constraint: Default ;00.BT :4 CB0;6B for Clock 'clk'

Total num(er of pat)s * destination ports: 17 * 12

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

;ffset: 4."!ns (,e-els of ,ogic = 4'

.ource: d:n (2DD'

Destination: cnt/2 (00'

Destination Clock: clk rising

Data 2at): d:n to cnt/2

3ate 4et

Cell:in+5out fanout Delay Delay ,ogical 4ame (4et 4ame'

++++++++++++++++++++++++++++++++++++++++ ++++++++++++

:C90::+5; 7 #.71" 1.2#1 d:n/:C90 (d:n/:C90'

,9T4::#+5; 1 #.478 #.7#4 /mu<###1=25 (/mu<###1=25/map1

,9T4/,::+5,; 1 #.478 #.12 /mu<###1=2524/.># (4118'

,9T4::+5; 1 #.478 #.### /mu<###1=254 (/mu<###1=25'

0D.:D #.17! cnt/2

++++++++++++++++++++++++++++++++++++++++

Total 4."!ns (2.2@ns logic? 2.#2@ns route'

(".4A logic? 4!.!A route'

=========================================================================

d$n input should be stable$

rom /+(28 ns beore clock

edge$ until clock edge

:

;e!ie" <uestions

=+ Consider a lip lop "ith a setup time o ( ns and a hold time o =

ns+ I the clock input rises at time t$ is it ok or the data input to

change at time t52> ?hat about t5/> ?hat about t-=@2> ?hat

about t-2> E*plain "hy it is not acceptable or the data input to

change at certain times+

2+ Consider the clock period analysis on page /+ 3o" "ould the clock

period change i the lip lop propagation delay "as = ns instead o

+828 and the gate delay or the ABTs "as C+8 ns$ instead o C+/9D>

%Eou may assume that the net delays donFt change+,

(+ Consider a circuit in "hich there is a path rom an input x to a lip

lop that has a ma*imum possible delay o 9 ns$ and there is also a

path rom x to another lip lop "ith a minimum delay o ( ns+ I

the setup and hold times are 2 ns and = ns respecti!ely and the

clock input rises at time t$ is it ok or x to change at time t52> ?hat

about t5=> ?hat about t> ?hat about t5=C>

D

Timing .nalysis 0rocedure

=+ Check or internal hold time !iolations

or e!ery -to- path$ check

%minimum prop+ delay, - %minimum comb+ circuit delay,

) %hold time, - %clock ske",

i* !iolations by adding delay

no !iolations possible i hold-time7%min--prop-delay,5ske"

2+ Determine minimum clock period

ind -to- path "ith largest !alue o

%maximum prop+ delay, - %maximum comb+ circuit delay,

- %setup time, - %clock ske",

(+ Input timing analysis

each input must be stable rom

%clockGedge, %%maximum input-to- delay, - %setup time,,

to %%clockGedge, - %hold time,, %minimum input-to- delay,

/+ Timing analysis or synchronous outputs

synchronous outputs ha!e potential to change any time rom

%clockGedge, - %minimum clock-to-output delay,

to %clockGedge, - %maximum clock-to-output delay,

omit ske" or paths rom

output to input o same

omit ske" or paths rom

output to input o same

=C

Timing .nalysis o Se#uential Comparator

&

Minimum clock period - 2 - 8= - 2 - = H == ns or DC M3z

Input timing re#uirements

'

% and & must be stable rom %clock'edge 5 2, 5 /= until

%clock'edge -=, 5 ( +22$ so rom -8 ns to -+22

Iutput timing - outputs can change +2 to 2 ns ater clock

&

Timing parameters

' gate delayJ C+22 to = ns

' setup timeJ 2 ns

'

hold timeJ = ns

' prop+ delayJ C+2-2 ns

' clock ske"J = ns

Internal hold time !iolation>

' yes - +2 - /%+22, 7 = - =

' add in!erter pair to eedback

paths rom s

==

Combining Circuits

?hen combining t"o components$ check setup

constraints manually

clock period ) %ma* output delay, - %ma* input delay,

- %ma* inter-connect delay, - ske"

Kote$ ske" much larger across dierent

components than "ithin a single component

3old time !iolations unlikely across components

inter-chip delays much larger than %hold time,-ske"

Circuit =

Circuit 2

clk

interconnect

delay

D Q

>C

D Q

>C

ma* input

delay

ma* output

delay

=2

Dealing "ith Timing Failures

To i* hold time errors$ add delay

rarely issue in F06.s$ but can be in .SIC designs

To correct setup time ailures

i you canFt increase clock period$ must reduce delay

ind long delay paths and modiy circuit to reduce

adLust synthesis@implementation properties

ocus on speed optimization$ increase eort le!el

study synthesis report to identiy "orst-case paths

re"rite M3DA to produce aster circuit

e+g+ replace ripple-carry circuits "ith carry lookahead

i need be %and easible,$ insert pipeline registers to di!ide

long combinational paths into smaller parts

=(

Metastability

Most digital systems ha!e asynchronous inputs

keyboard input on a computer$

sensor on a traic light controller$

card insertion on an .TM$ etc+

.synchronous inputs change at unpredictable times

so$ can change during clock transition$ causing

metastability

Iutput o a metastable lip lop can oscillate or remain

at intermediate !alue

leads to unpredictable beha!ior in other lip lops

metastability usually ends #uickly$ but no definite time

limit

so$ circuit ailures due to metastability are una(oidable

ho"e!er$ systems can be designed to make ailures rare

=/

Synchronizers

)ynchroni#ers are used to isolate metastable signals until

they are Nprobably saeO

D Q

>C

D Q

>C

clk

asynchronous

input

potentially

metastable

signal

*probably

safe+ signal

&

I the clock period is long enough$ ailure probability is small

and e*pected time bet"een ailures is large

MTPF H Mean Time Pet"een Failures %T@TC,eT@

"here T is the clock period$ is the a!erage time bet"een

asynchronous input changes$ and TC are parameters o the

lip lop being used

I T H 2C ns$ , = ms$ H = ns$ TC H = ns$ MTPF : trillion

years$ i T H =C ns$ MTPF becomes 22C secondsQ

=2

MTPF Chart

=+E-C2

=+E-C8

=+E-C9

=+E-C:

=+E-CD

=+E-=C

=+E-==

=+E-=2

=C =2 2C 22 (C (2 /C /2 2C 22 8C

T@

M

T

P

F

%

s

e

c

o

n

d

s

,

H= s

= year

= ns = ms =

HT

C

HTC

T@TC

=C years

=8

E*ercises

=+Consider the generic state machine

sho"n belo" "ith the indicated

propagation delays+ I the setup time or

the lip lops is =+2 ns and the ma*imum

clock ske" is +2 ns$ "hat is the smallest

clock period or "hich the circuit is

guaranteed to "ork correctly>

2+ For the state machine sho"n belo"$

assume that the lip lop setup time is 2

ns$ the hold time is C+2 ns and the lip lop

propagation delay is bet"een = and ( ns+

.lso$ that the clock ske" is C+( ns+

Is this circuit subLect to internal hold

time !iolations> Rustiy your ans"er+ ?hat

is the smallest clock period or "hich the

circuit is not subLect to setup time

!iolations> Pe sure to take into account

any modiications rom the pre!ious step+

?hat is the latest time relati!e to the

clock$ "hen it is sae or input & to

change> ?hat is the latest time ater the

clock "hen output - can be changing>

=9

(+Consider a synchronizer used to

synchronize an asynchronous input

signal+ Aet the a!erage time bet"een

changes o the input signal be 2C

microseconds+ Aet the lip lop

parameters be TC H ( ns and H 2 ns+ I

the clock period or the synchronizer is

=C ns$ "hat is the mean time bet"een

synchronizer ailures> ?hat is the

smallest clock period %to the nearest ns,

or "hich the mean time bet"een ailures

is =C years> ?hat is the smallest clock

period or "hich the mean time bet"een

ailures is =C$CCC years>

=:

Solutions

=+ The minimum clock period is

=+2-(-=+2-C+2H8+2 ns+

2+ There are no hold time !iolations

because the minimum lip lop

propagation delay is larger than the hold

time plus the ske"+

The ma*imum delay or the ne*t state

logic is 2 ns+ This gi!es a minimum clock

period o (-2-2-C+(H=C+( ns+

Input & has a ma*imum delay path o 2

ns$ so it must be stable by (-2H2 ns

beore the clock rises+

The latest time ater the clock "hen

output - can be change is (-/H9 ns+

(+ H 2C*=C

-8

$ TC H (*=C

-D

and H

2*=C

-D

$ so or TH=C*=C

-D

$ MTPF H

=89*=C

-8

e

2

H 2/$9(2*=C

-8

seconds or

about 22 milliseconds+ Py trial and

error$ one inds that or TH2( ns the

MTPF is about D+2 years and or TH2/

ns$ it is about =2 years$ so "e need a

target clock period o about 2/ ns to

get a =C year MTPF+ .lso$ by trial and

error$ one inds that or TH88 ns the

MTPF is about 9$8CC years and or

TH89 ns$ it is about =2$:CC years$ so

"e need a target clock period o

about 89 ns to get a =C$CCC year

MTPF+ So$ adding =( ns has impro!ed

the reliability by a actor o =$CCC+

Vous aimerez peut-être aussi

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsD'EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsÉvaluation : 1 sur 5 étoiles1/5 (1)

- Timing Issues in CircuitsDocument15 pagesTiming Issues in CircuitsNiloy RoyPas encore d'évaluation

- 3 Analysis (Easier Awk)Document36 pages3 Analysis (Easier Awk)Dilip GyawaliPas encore d'évaluation

- Simulation PracticalDocument71 pagesSimulation PracticalrntimePas encore d'évaluation

- Static Timing AnalysisDocument100 pagesStatic Timing Analysismrinalmishra100% (2)

- ITC242 Spring Exam QuestionsDocument18 pagesITC242 Spring Exam Questionspriyasingh1682Pas encore d'évaluation

- Ping TCU and NWI 2GDocument9 pagesPing TCU and NWI 2G3GSEROPas encore d'évaluation

- Network Processor Packet Processing RatesDocument12 pagesNetwork Processor Packet Processing RatesBobby BeamanPas encore d'évaluation

- 1 b30 - s08 - 01 s08 - 02 RRC 1Document325 pages1 b30 - s08 - 01 s08 - 02 RRC 1gh1ij1Pas encore d'évaluation

- Minimum Overhead Routing Protocol in MANETDocument8 pagesMinimum Overhead Routing Protocol in MANETIJAFRCPas encore d'évaluation

- CMOS Latches and Flip Flops TutorialDocument52 pagesCMOS Latches and Flip Flops TutorialGuru VelmathiPas encore d'évaluation

- STA-Static Timing AnalysisDocument28 pagesSTA-Static Timing AnalysisNaveen KumarPas encore d'évaluation

- Timing issues in digital ASIC designDocument101 pagesTiming issues in digital ASIC designnsai_vs1513Pas encore d'évaluation

- Channel Configuration: ObjectivesDocument30 pagesChannel Configuration: Objectivestatuchi69Pas encore d'évaluation

- YLD H06 ProtocolDocument8 pagesYLD H06 Protocoldrezao_rnPas encore d'évaluation

- Programing Code PABX Panasonic PDFDocument39 pagesPrograming Code PABX Panasonic PDFPthroeztPas encore d'évaluation

- Imp Vlsi QuesDocument21 pagesImp Vlsi QuesVikasAroraPas encore d'évaluation

- Cyclone V Schematic Review WorksheetDocument111 pagesCyclone V Schematic Review WorksheetTabitha HowardPas encore d'évaluation

- MT8870D/MT8870D-1: ISO - CmosDocument25 pagesMT8870D/MT8870D-1: ISO - CmosetechmduPas encore d'évaluation

- Q10 Invalid Data Type? HEX Q11 Loop Tablename-Fldname 'Accenture' Append Table Endloop Ans - Infinite LoopDocument5 pagesQ10 Invalid Data Type? HEX Q11 Loop Tablename-Fldname 'Accenture' Append Table Endloop Ans - Infinite LoopSiddhartha BaruaPas encore d'évaluation

- NS-3 Simulator BasicsDocument47 pagesNS-3 Simulator BasicsSonali DasPas encore d'évaluation

- NS-3 Network Simulation TutorialDocument46 pagesNS-3 Network Simulation TutorialahmedabdullaPas encore d'évaluation

- Lec 06Document18 pagesLec 06Souptik SenPas encore d'évaluation

- NSN Rno Fi 191007 PartiiiDocument41 pagesNSN Rno Fi 191007 PartiiiZamroniMohammadPas encore d'évaluation

- Timing Analysis of Source Synchronous Interface Using ALTLVDS v1.0Document6 pagesTiming Analysis of Source Synchronous Interface Using ALTLVDS v1.0huangjsmikePas encore d'évaluation

- Memo Commande SysadminDocument7 pagesMemo Commande SysadminhrbrtscribdPas encore d'évaluation

- 93K TrainingDocument21 pages93K TrainingrumralkarPas encore d'évaluation

- Static Timing Analysis in VLSI CircuitsDocument16 pagesStatic Timing Analysis in VLSI CircuitseeshgargPas encore d'évaluation

- Why timing analysis is important in chip designDocument58 pagesWhy timing analysis is important in chip designPooja selvamPas encore d'évaluation

- Chapter 4 Lab 4-2, Mixed Layer 2-3 Connectivity Chapter 4 Lab 4-2, Mixed Layer 2-3 ConnectivityDocument13 pagesChapter 4 Lab 4-2, Mixed Layer 2-3 Connectivity Chapter 4 Lab 4-2, Mixed Layer 2-3 ConnectivityKarina Herrera YzaguirrePas encore d'évaluation

- 2207-2209 Log BookDocument75 pages2207-2209 Log BookCatherineOngPas encore d'évaluation

- Source Code-234Document9 pagesSource Code-234Bryan Joshua SalvidarPas encore d'évaluation

- Test flexible RLC PDU sizes for UM RLC in uplinkDocument5 pagesTest flexible RLC PDU sizes for UM RLC in uplinkpzernikPas encore d'évaluation

- NSN 2G-3G Parameter SettingDocument17 pagesNSN 2G-3G Parameter SettingTOMTOB_123100% (5)

- 4ms Pingable Envelope Generator: Eurorack Module User Manual v2012-06-01 (Rev4.2)Document12 pages4ms Pingable Envelope Generator: Eurorack Module User Manual v2012-06-01 (Rev4.2)MaciasPajasPas encore d'évaluation

- Inertial Delay Returns Boolean Balance BehaviorDocument81 pagesInertial Delay Returns Boolean Balance BehaviorssfofoPas encore d'évaluation

- Negative and Positive Clock SkewDocument27 pagesNegative and Positive Clock SkewSupriya AggarwalPas encore d'évaluation

- FPGA Climatic Control Platform Design and ImplementationDocument39 pagesFPGA Climatic Control Platform Design and ImplementationValy RusuPas encore d'évaluation

- Relay Super Cycle With TimerDocument8 pagesRelay Super Cycle With Timerdon121don121Pas encore d'évaluation

- LM555 NewDocument18 pagesLM555 NewAnye ChikitaPas encore d'évaluation

- Direct Digital Synthesizer: Design of ROMDocument53 pagesDirect Digital Synthesizer: Design of ROMYermakov Vadim IvanovichPas encore d'évaluation

- CCNA Practice Certification Exam QuestionsDocument23 pagesCCNA Practice Certification Exam QuestionsMauricio Rodriguez FigueroaPas encore d'évaluation

- Program MicroDocument7 pagesProgram Microari wiliamPas encore d'évaluation

- STI - FSM - SolutionsDocument6 pagesSTI - FSM - SolutionsAishwarya GajendrulaPas encore d'évaluation

- CCNAS Chp4 PTActC Zone Based Policy Firewall InstructorDocument5 pagesCCNAS Chp4 PTActC Zone Based Policy Firewall InstructorilhamdaniPas encore d'évaluation

- Experiment 1 - Stop and Wait Protocol Implementation and AnalysisDocument18 pagesExperiment 1 - Stop and Wait Protocol Implementation and AnalysisfarukhPas encore d'évaluation

- STA FinalDocument66 pagesSTA FinalgauravkshriPas encore d'évaluation

- Journal: Ethernet Frame Check Sequence: 34349 Integrated Broadband ElectronicsDocument16 pagesJournal: Ethernet Frame Check Sequence: 34349 Integrated Broadband ElectronicsCopenhagen Studies on Asthma in ChildhoodPas encore d'évaluation

- Accelerated Test: Failure Rate at 25 C ???Document41 pagesAccelerated Test: Failure Rate at 25 C ???Dia Putranto HarmayPas encore d'évaluation

- Visual Basic 6 Code Explanation On Yaesu FT-840 CAT ApplicationDocument6 pagesVisual Basic 6 Code Explanation On Yaesu FT-840 CAT ApplicationShree Vishnu ShastriPas encore d'évaluation

- CCNAS - Chp2 - PTActA - Syslog-SSH-NTP - InstructorDocument5 pagesCCNAS - Chp2 - PTActA - Syslog-SSH-NTP - InstructorAziz LondonPas encore d'évaluation

- High Performance ComputingDocument33 pagesHigh Performance ComputingRimsa GopermaPas encore d'évaluation

- StatictimeanalysisDocument75 pagesStatictimeanalysisAgnathavasiPas encore d'évaluation

- Computer Network Lesson PlanDocument3 pagesComputer Network Lesson PlansenthilvlPas encore d'évaluation

- GCR300 DNP3.0 Detail Switch ControlDocument8 pagesGCR300 DNP3.0 Detail Switch ControlJagan VanamaPas encore d'évaluation

- 11timing Concepts and Physical DesignDocument42 pages11timing Concepts and Physical DesignTeja Reddy100% (2)

- Timing Analysis: Elec 326 Sequential Circuit TimingDocument43 pagesTiming Analysis: Elec 326 Sequential Circuit TimingArpit KapoorPas encore d'évaluation

- LOCATION AREA DIMENSIONING GUIDELINE FOR ERICSSON GSM SYSTEMDocument26 pagesLOCATION AREA DIMENSIONING GUIDELINE FOR ERICSSON GSM SYSTEMWaheed Ali Bangash100% (1)

- Numerical Methods for Simulation and Optimization of Piecewise Deterministic Markov Processes: Application to ReliabilityD'EverandNumerical Methods for Simulation and Optimization of Piecewise Deterministic Markov Processes: Application to ReliabilityPas encore d'évaluation

- Engineering Academy: MOCK GATE (2012) - 2Document12 pagesEngineering Academy: MOCK GATE (2012) - 2shrish9999Pas encore d'évaluation

- Eemock6 QueDocument17 pagesEemock6 Queshrish9999Pas encore d'évaluation

- OEGCB OnlineMistakesAnsDocument1 pageOEGCB OnlineMistakesAnsshrish9999Pas encore d'évaluation

- IesDocument4 pagesIesshrish9999Pas encore d'évaluation

- Objective Type QuestionsDocument4 pagesObjective Type Questionssarfzec0381Pas encore d'évaluation

- CD PDFDocument9 pagesCD PDFshrish9999Pas encore d'évaluation

- IES2013 EEE Objective Paper 2Document17 pagesIES2013 EEE Objective Paper 2bigboss0086Pas encore d'évaluation

- IES2013 EEE Objective Paper 1Document20 pagesIES2013 EEE Objective Paper 1Srinivas DalliPas encore d'évaluation

- PowerSystem Analysis HADI SAADAT E-BokDocument130 pagesPowerSystem Analysis HADI SAADAT E-BoksasikalasivakumarPas encore d'évaluation

- AmpiDocument2 pagesAmpishrish9999Pas encore d'évaluation

- r05320402 Vlsi DesignDocument4 pagesr05320402 Vlsi DesignSRINIVASA RAO GANTAPas encore d'évaluation

- HF Transceiver PDFDocument16 pagesHF Transceiver PDFHaggai Ben BaruchPas encore d'évaluation

- BD9479Document29 pagesBD9479Aceng SobanaPas encore d'évaluation

- (CNY) QUOTATION - Module Amplifier (Powavesound)Document8 pages(CNY) QUOTATION - Module Amplifier (Powavesound)angelo gazabonPas encore d'évaluation

- Vlsi Design Test and TestabilityDocument17 pagesVlsi Design Test and TestabilitySuravarapu ArunaPas encore d'évaluation

- ISRO ECE Solved Question PaperDocument3 pagesISRO ECE Solved Question PapermnbvcxzPas encore d'évaluation

- Lab 3Document4 pagesLab 3J SarduaPas encore d'évaluation

- Registers and Counters Design in VerilogDocument65 pagesRegisters and Counters Design in VerilogPurushothama ReddyPas encore d'évaluation

- A Low Power Vernier Time-To-digitalDocument5 pagesA Low Power Vernier Time-To-digitalLaxmi KumrePas encore d'évaluation

- General Description: Dual Retriggerable Precision Monostable MultivibratorDocument17 pagesGeneral Description: Dual Retriggerable Precision Monostable Multivibratorsajad hejaziPas encore d'évaluation

- High Frequency VCO Design OptimizationDocument67 pagesHigh Frequency VCO Design OptimizationEnricoLiaPas encore d'évaluation

- Basic Electrical Engineering Course Outcomes (39Document3 pagesBasic Electrical Engineering Course Outcomes (39Mega rani RPas encore d'évaluation

- NT 2022 Gtu PyqDocument3 pagesNT 2022 Gtu PyqSandeep kumarPas encore d'évaluation

- 74HC4050Document8 pages74HC4050Thai Khang VanPas encore d'évaluation

- Star DeltaDocument19 pagesStar DeltaSUSHMAGUPTAPas encore d'évaluation

- Lecure-4 Biopotential Amplifiers & FiltersDocument87 pagesLecure-4 Biopotential Amplifiers & FiltersNoor Ahmed75% (4)

- Objective:: Study Single Phase Cycloconverter Point Configuration)Document4 pagesObjective:: Study Single Phase Cycloconverter Point Configuration)Mukesh Kumar BeheraPas encore d'évaluation

- A New CMOS Charge Pump For Low Voltage ApplicationsDocument4 pagesA New CMOS Charge Pump For Low Voltage Applicationskhausar1785Pas encore d'évaluation

- OCL Power Amplifier 50watt - Electronic CircuitDocument1 pageOCL Power Amplifier 50watt - Electronic CircuitJosue Rafael BorjasPas encore d'évaluation

- Analysis of Class B Push-Pull Amplifier CircuitDocument24 pagesAnalysis of Class B Push-Pull Amplifier CircuitMbugua DuncanPas encore d'évaluation

- Using Overture Design GuideDocument5 pagesUsing Overture Design Guideeleceng1979Pas encore d'évaluation

- QuestionDocument80 pagesQuestionRodalie Vale CruzPas encore d'évaluation

- EDCDocument28 pagesEDCzuberbashaPas encore d'évaluation

- Power Amplifiers: W6L1 BoylsterdDocument18 pagesPower Amplifiers: W6L1 BoylsterdMuhammad SameerPas encore d'évaluation

- Unit-V Small Signal Low Frequency Transistor Amplifier ModelsDocument40 pagesUnit-V Small Signal Low Frequency Transistor Amplifier ModelsSivakumar PothirajPas encore d'évaluation

- Analog Communication Lab ManualDocument59 pagesAnalog Communication Lab Manualsasa_sag100% (2)

- ANALOG AND DIGITAL ELECTRONICS MCQDocument12 pagesANALOG AND DIGITAL ELECTRONICS MCQNoor AhmedPas encore d'évaluation

- Latch-Up Prevention in CMOS Logics - Team VLSIDocument13 pagesLatch-Up Prevention in CMOS Logics - Team VLSIKaifeng LiuPas encore d'évaluation

- MOSFET Switching WaveformsDocument3 pagesMOSFET Switching WaveformsGagnePas encore d'évaluation

- Chapter 3 - FETDocument24 pagesChapter 3 - FETHoang Dung SonPas encore d'évaluation