Académique Documents

Professionnel Documents

Culture Documents

Sistema PLL

Transféré par

Wisller JeffersonCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Sistema PLL

Transféré par

Wisller JeffersonDroits d'auteur :

Formats disponibles

SISTEMAS PLL

Sistemas PLL

Os sistemas de lao fechado por fase j existem h um bom tempo, mas so ainda

pouco conhecidos pelos prprios profissionais e estudantes de eletrnica. Da a

idia de fazer uma introduo completa a esses dispositivos, mas sem exigir grandes conhecimentos matemticos ou mesmo qualquer familiaridade sobre o assunto.

Aproveitando a oportunidade, sero apresentados tambm os sistemas PLL por realimentao, superiores aos convencionais em muitos aspectos.

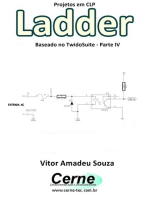

O que chamamos de lao fechado por fase (phase-locked loop ou ainda PLL) um

sistema que permite controlar uma grandeza eltrica mediante uma defasagem entre

dois sinais. Na FIG. 01 podemos ver o diagrama de blocos de um sistema servocontrolado genrico, onde Ax e Ay so grandezas do mesmo tipo (tal como potenciais

de CC ou CA, por exemplo), e que pode servir como ilustrao bsica da operao

dos PLL.

Figura 01 Todo sistema de controle composto de uma fonte de informao (Ax),

um comparador (C), um processador (B) e uma quantidade controlvel

(Ay).

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

Essas duas grandezas podem ser comparadas entre si no bloco C, utilizando-se vrios processos (multiplicao ou subtrao, digamos). O resultado da comparao

ento processada nesse mesmo bloco de modo que a grandeza Ay seja ajustada

em seu valor. A forma como ocorre esse processamento vai determinar algumas caractersticas do sistema, entre elas e constante de tempo de controle.

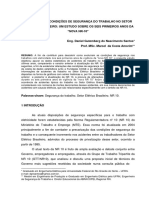

Passando FIG. 02, j temos o diagrama de blocos de um verdadeiro sistema PLL.

Neste caso, o controle se baseia na defasagem entre o sinal de entrada (1) e aquele

proveniente de um VCO ou oscilador controlado por tenso (2), de forma que o bloco seja capaz de reconhecer essa defasagem. O VCO concebido de modo que

exista sempre uma diferena de fase especfica entre sua sada e o sinal de entrada.

A rapidez com que o sistema vai ajustar o VCO, a fim de conseguir qualquer alterao da entrada, depende principalmente das caractersticas do filtro passa-baixas

(FPB).

Figura 02 Os PLL so formados por trs elementos bsicos: um comparador de

fase , um filtro passa-baixa (FPB) e um VCO (ou oscilador controlvel).

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

O PLL em ao

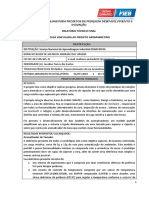

Sempre que dois sinais so multiplicados, seu produto inclui um componente proporcional defasagem entre ambos, que pode ser separado dos demais atravs de

filtragem; essa a funo do bloco . Na prtica, o sinal de entrada multiplicado

por uma onda quadrada vinda do VCO o que significa, portanto, que os semiciclos

dessa onda multiplicam o sinal de entrada alternadamente por +1 ou 1. Os grficos

da FIG. 03 podem ajudar-nos a compreender melhor essa operao.

Em a temos o sinal de entrada (que uma senide) e logo abaixo a onda quadrada

do VCO, com a mesma freqncia; ela repetida vrias vezes, com defasagens que

variam de 0 a 180o , sempre adiantada em relao senide, em b, d, f, h e j.

Observe, ento, que durante os semiciclos positivos dessa onda o sinal de produto

(representado em c, e, g, i e k) idntico senide de entrada. J nos semiciclos negativos, a senide tem sua polaridade invertida o que eqivale, na prtica,

a multiplicar os dois sinais entre si.

No primeiro sinal-produto (c), que aquele associado onda quadrada em fase

(b), percebemos que no existem valores negativos; de fato, ele pode ser considerado uma verso da senide retificada em onda completa. Seu valor CC, uma vez

filtrado, ser indiscutivelmente positivo.

Quando a onda quadrada est adiantada de 45o, porm, como em d, o produto

(e) exibe claramente uma rea maior acima do eixo horizontal; isto quer dizer que

seu nvel CC mdio tambm positivo, porm menor do que em c. Avanando um

pouco mais a onda quadrada at os 90o, como em f -, o produto g apresenta

reas idnticas acima e abaixo do eixo, o que significa um valor mdio nulo.

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

Figura 03 Sada do comparador de fase para vrias defasagens entre o sinal de

entrada e o sinal do VCO.

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

Com defasagens maiores que 90o, o valor CC do produto passa a ser negativo, atingindo em 180o o mximo valor abaixo do eixo (k). Resumindo, ento: o nvel CC do

sinal-produto varia do valor mximo positivo, quando a onda quadrada se encontra

em fase com o sinal de entrada, passando por zero quando este fica atrasado 90o

em relao a ela, at um mximo negativo quando esse atraso de 180

Vamos assumir, agora, que a freqncia de entrada exatamente igual do VCO e

que o PLL j est fechado(ignorando, por enquanto, como ele chegou a esse estado). Nessas condies, a onda do VCO vai estar 90o adiantada em relao ao sinal

de entrada e a sada CC do comparador de fase (ou multiplicador) nula. Suponhamos ento que a freqncia do VCO tende a aumentar, elevando tambm a defasagem. A sada do comparador de fase passa, obviamente, a ser negativa, leva ndo a uma reduo de freqncia do VCO; o lao mantido, com uma ligeira elevao da defasagem (com a onda quadrada sempre frente da senide).

Se, por outro lado, a freqncia do VCO tende a diminuir, a sada do comparador de

fase vai tornar-se positiva, forando um aumento naquela freqncia. possvel

demonstrar, ainda, que o sinal de entrada pode ser travado com certas harmnicas

da onda do VCO ou esta com harmnicas do sinal de entrada (caso a entrada no

seja senoidal, como no exemplo).

Existe tambm a possibilidade de inserir um divisor de freqncia entre o VCO e o

comparador de fase e, combinando esse divisor ao travamento com harmnicas, fazer com que a relao entre as freqncias do VCO e de entrada assuma valores

bastante peculiares tal como 16/3, por exemplo. Esse processo abre enormes

possibilidades na sintetizao de freqncias.

O processo de captura

Consideramos, at aqui, que o sistema PLL estava sempre travado. Precisamos

agora examinar o que acontece quando o circuito ligado e no se encontra ainda

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

com o lao fechado que o caso mais comum na prtica. Em poucas palavras, o

VCO busca at encontrar uma freqncia e uma fase s quais possa ficar travado.

Felizmente, possvel entender o processo de captura, como chamada essa busca, sem que precisaremos recorrer matemtica; basta examinar o comportamento

do circuito em certos pontos do lao e assumir alguns detalhes de antemo.

Para ajudar na explanao, vamos determinar primeiro que a ligao entre a sada

do FPB e a entrada do VCO est interrompida. Este ltimo, privado da tenso de

controle, ir atingir sua freqncia de oscilao livre, que pode ser considerada inferior de entrada. J havamos assumido anteriormente, ao discutir a condio de

lao fechado, que a freqncia do VCO tende a aumentar, quando a tenso de controle torna-se positiva e diminui quando ela passa a ser negativa.

Podemos assumir tambm que o filtro remove totalmente as freqncias equivale ntes soma das freqncias de entrada e do VCO, que ele permite a passagem de

corrente contnua sem atenuao e deixa passar a diferena entre as freqncias do

VCO e de entrada com certa dose de atenuao que diminui com a reduo da

freqncia-diferena (isto , medida que a freqncia do VCO aproxima-se da de

entrada).

Enquanto o VCO se encontra em regime de livre oscilao, devido ligao inte rrompida, na sada do FPB surge um sinal-diferena de amplitude constante. Uma

vez refeita a ligao, preciso seguir cuidadosamente tudo o que acontece j que

nos primeiros momentos continua existindo uma freqncia-diferena, ao mesmo

tempo em que o VCO est recebendo uma tenso de controle.

Considerando agora uma variao ascendente dessa tenso de controle, do vale at

o pico (FIG. 04); como ela tem sentido positivo, a freqncia do VCO tende a aumentar e o sinal-diferena, a diminuir. Devido a essa reduo, a freqncia diferena

tem sua atenuao pelo FPB progressivamente reduzida, o que leva a uma maior

amplitude final da tenso de controle, se comparada ao regime de oscilao livre.

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

A FIG. 04a compara as duas variaes positivas (sob controle e em oscilao livre),

partindo do mesmo instante e mesmo potencial de vale. Observe que o pico da variao controlada mais positiva, alm de ocorrer um pouco mais tarde, devido reduo do sinal-diferena.

J na FIG. 04b podemos ver o que acontece com uma variao descendente. Nesse

caso, a tenso de controle do VCO tem sentido negativo, provocando uma reduo

em sua freqncia e um aumento na freqncia-diferena. No FPB, a atenuao

eleva-se progressivamente, fazendo com que a amplitude final seja menor que a de

oscilao livre e o vale termine mais cedo.

Figura 04 Representao de como a onda de diferena de freqncia varia durante um ciclo do transiente de captura.

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

A prpria FIG. 04a representa uma soma das duas etapas, mostrando assim o que

ocorre durante um ciclo completo do sinal-diferena, vale a vale. Como se v, o semiciclo ascendente exibe um pico mais positivo do que o do sinal-diferena, o que

prejudica o semiciclo descendente, tornando o vale mais positivo do que seria na

condio livre.

Os ciclos posteriores do transiente de captura, como tambm chamado esse processo, no permitem comparao com a forma de onda de oscilao livre, mas seguem o mesmo padro geral, ou seja, as variaes ascendentes tm maior amplitude e as descendentes, menor amplitude. Isso vai resultar em picos e vales sucessivamente mais positivos e em intervalos de tempo cada vez mais longos o que significa que a freqncia do VCO ir aumentar progressivamente, at o ponto em que

uma dessas variaes da tenso de controle iguale as freqncias do VCO e de entrada. Outras passagens podero ocorrer, em seguida, para que o VCO localize a

correta relao de fase, antes que o lao esteja realmente fechado.

Aplicaes dos PLL

Todo sistema PLL fornece, na sada, dois tipos de informao; a freqncia do VCO,

que est sempre relacionada com a freqncia de entrada, e a tenso de controle,

cujo valor depende da defasagem entre o sinal de entrada e a sada do VCO.

Caso a informao que queiramos no sinal de entrada esteja sob a forma de variao de freqncia (isto , modulao em freqncia), o PLL pode ser usado como

detector de FM apresentando vrias vantagens sobre os detectores de relao e

coincidncia, tais como menor distoro, melhor supresso de interferncias e ausncia de circuitos LC.

Mas os circuitos de lao fechado por fase tambm so teis na sintetizao de freqncias, conforme nos mostra a FIG. 05. No exemplo da FIG. 05a, a condio para

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

o fechamento do lao de que fc /nv = fr e que, com um espaamento entre canais de

f, tenhamos f = f. Desse modo, as freqncias entregues pelo VCO so mltiplas

da freqncia de referncia e a prpria sada do VCO determinada pela razo de

diviso nv .

Na maioria dos casos prticos, porm, os divisores de razo varivel no so capazes de receber diretamente uma freqncia elevada do VCO motivo pelo qual esta

normalmente aplicada, antes de mais nada, a um divisor estvel de razo fixa e

deste para o de razo varivel. Com esse artifcio, possvel realizar divises sucessivas a partir de portadoras relativamente elevadas, at uma baixa freqncia de

espaamento entre canais. Processo de grande utilidade em equipamentos VHF

para avies, por exemplo.

Figura 05a Inserindo um divisor de freqncia de razo varivel entre o VCO e o

comparador de fase, pode-se obter vrias freqncias a partir de uma

nica referncia fr.

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

10

Figura 05b Este mtodo mais simples que o da FIG. 05a, mas s custas da estabilidade, que normalmente diminui com o aumento de n.

A FIG. 05b, por sua vez, mostra um caso de sintetizao de freqncias em que pulsos delta, em forma de agulha, so aplicados ao comparador de fase juntamente

com o sinal do VCO. Como esse tipo de pulso contm harmnicas pares e mpares

da freqncia fundamental, o PLL pode ser induzido a fechar com qualquer uma

delas.

Confeco de um PLL

Vejamos separadamente os requisitos prticos para se implementar os trs estgios

bsicos de um sistema de lao fechado por fase.

O VCO As exigncias do VCO dependem, principalmente, da aplicao especfica

do PLL. Se for utilizado como detector de FM deve-se ter a melhor linearidade possvel (isto , variao linear de freqncia com a variao da tenso de controle), ao

passo que para a sintetizao de freqncias mais importante a estabilidade.

Multiplicadores por tenso controlada e osciladores LC sintonizados por varicap,

como os ilustrados nas figuras 6a e 6b, respectivamente, devem normalmente em-

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

11

pregar componentes discretos. Se o oscilador da FIG. 6b for utilizado tambm na

sintonia de receptores (isto , como oscilador local), ser conhecido por oscilador

controlado por tenso sintonizvel (TVCO). Por outro lado, os sistemas PLL integrados, como o tipo 565 da FIG. 07, operam segundo o princpio do disparo.

Figura 06a Circuito VCO de excepcional linearidade, capaz de operar at os 50

MHz.

Figura 06b Circuito VCO composto por um oscilador LC sintonizado e/ou controlado por diodos varicap.

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

12

Figura 07 Circuito simplificado de VCO usado em integrados PLL, tal como o 565.

Toda vez que um PLL deve ser alimentado com uma tenso flutuante, recomendase que a freqncia do VCO seja independente dessa tenso; ou, ento, que a fonte

seja substituda por outra estabilizada.

O comparador de fase A sada desse estgio (tambm chamado de multiplicador)

deve depender somente dos dois sinais aplicados a ele requisito que pode ser

atendido por qualquer componente no linear, desde que os sinais de entrada apaream realmente na sada. importante tambm, que os sinais no afetem o desempenho do sistema. Mas vital mesmo a exigncia de que a sada no contenha

quaisquer componentes CC resultantes da retificao dos sinais de entrada que poderiam atrapalhar o sistema e at faz-lo desmanchar o lao.

Utilizando, porm, um multiplicador balanceado como o da FIG. 08, esses problemas

podem ser facilmente evitados, pois ele suprime os sinais de entrada e no utiliza

retificao. Caso a supresso no seja necessria, podemos adotar um multiplicador

assimtrico como o da FIG. 09; circuitos desse tipo constituem o estgio de entrada

dos amplificadores operacionais de transcondutncia (OTAs), tal como o CA3080

um CI ideal para circuitos PLL.

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

13

Pode-se perceber que, nesse caso, pode ocorrer a retificao dos sinais de entrada;

mesmo assim, possvel obter nveis satisfatrios de supresso de AM. Para alcanar melhor desempenho nesse aspecto, a soluo aplicar a sada do VCO entrada assimtrica e o sinal de entrada na simtrica; as amplitudes no devem exceder,

ento, 0,5 V a 0,05V, respectivamente. Por esse mtodo obtm-se nveis de supresso de AM to elevados quanto os do multiplicador simtrico.

Figura 08 O multiplicador simtrico usado em quase todo os CI PLL e pode ser

tambm encontrado com CI individual. Pode-se obter igualmente bons

resultados montando-o com elementos discretos.

Se houver transformadores de RF disposio, pode-se tentar um mtodo antiquado (mas ainda eficiente), usando-os juntamente com um modulador em anel de quatro diodos, que faz as vezes de multiplicador (FIG. 10). A mais simples (e infeli zmente tambm pior) implementao para o comparador de fase consiste em um nico dispositivo semicondutor, acionado por um sinal de VCO com nvel suficiente

para comut-lo continuamente. Devido inevitvel realimentao do circuito para o

VCO, imprescindvel incluir um estgio isolador, a exemplo do circuito mostrado na

FIG. 11.

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

14

Figura 09 Multiplicadores simtricos tambm podem ser utilizados, desde que o

filtro passa-baixa proporcione uma supresso adequada das freqncias de entrada.

Figura 10 Empregando transformadores de RF, pode-se montar um multiplicador

bastante barato com quatro diodos.

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

15

Figura 11 Circuito que pode ser usado como comparador de fase, mas no como

detector de FM.

Como se v, nessa figura o comparador de fase ficou reduzido a um simples misturador, o que nos leva a concluir que qualquer circuito semelhante poder exercer a

mesma funo. Os problemas introduzidos por esse circuito, porm, impedem que

ele seja usado em detectores de FM e s podem ser eliminados com equipamentos

sofisticados de testes. Os comparadores simtricos, ao contrrio, proporcionam resultados satisfatrios, exigindo apenas os instrumentos convencionais.

O filtro passa-baixa o estgio que determina a largura de faixa do PLL e pode

ser implementado a partir de simples filtros RC. Alguns deles podem ser vistos na

FIG. 12; os modelos b , c e d so adequados para os comparadores simtricos,

enquanto o a mais visto nos assimtricos. Alm disso, normal que o resistor R

faa parte do comparador de fase.

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

16

Figura 12 Entre esses quatro filtros passa-baixa, a verso d a melhor para implementao domstica, por ser menos crtica.

Embora seja tarefa simples o clculo de componentes para o filtro, quando se utiliza

PLL integrados (j que basta recorrer ao manual do fabricante), preciso dispor de

equipamentos sofisticados para avaliar o desempenho do circuito em freqncias

superiores a 10 MHz. Entre os quatro exemplos dados, o d o mais adequado

para montagens domsticas. Nesse caso, a freqncia de corte da malha formada

por C2 e a resistncia de sada do comparador de fase determinada pela menor

freqncia a ser detectada (20 Hz, em FM comercial). O corte da segunda malha

RC, formada por P (em seu valor mximo) e C1, ambos ligados em paralelo com a

resistncia de sada, estabelecido pelo desvio mximo da freqncia de entrada.

Assim, qualquer largura de faixa desejada, at o limite determinado pelo ganho do

lao e pela amplitude do sinal de entrada, pode ser ajustada atravs de P.

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

17

Problemas dos PLL

Teoricamente, os detectores baseados em circuitos de lao fechado por fase tm

grandes vantagens sobre outros detectores de FM, mas elas nem sempre se concretizam. Isto porque existem, basicamente, dois fatores crticos nos sistemas PLL:

estabilidade de freqncia do VCO e relao sinal/rudo.

A boa estabilidade pode ser obtida compensando em temperatura a alimentao do

VCO o que se aplica tambm ao comparador de fase, caso a entrada de controle

do VCO seja assimtrica. Alm disso, os componentes cujos valores afetam a freqncia do VCO devem exibir coeficientes trmicos nulos.

Tais requisitos so difceis de satisfazer plenamente e, na prtica, a freqncia central do VCO costuma sofrer pequenos desvios ao longo da faixa de temperaturas de

operao. Por isso, aconselhvel escolher a menor freqncia de trabalho possvel

que vai depender da largura de banda do sinal de FM. Com os tradicionais 200

kHz de radiodifuso em FM, possvel obter uma operao satisfatria com freqncias de 450 kHz, por exemplo. A deriva de freqncia, com freqncia, com

valores to baixos pode ser considerada desprezvel, entretanto, os receptores que

utilizam esse princpio devem dispor das tcnicas de dupla converso (ou seja, superheterodinos duplos) e fatalmente custam mais caro do que os convencionais.

Tanto o VCO como o comparador de fase geram algum rudo e, portanto, o nvel do

sinal demodulado deve ser o mais elevado possvel em relao a esse rudo. A amplitude da sada do PLL proporcional ao quociente do desvio pela freqncia de

trabalho que nos receptores de FM , obviamente, a freqncia intermediria. Com

uma FI de 10,7 MHz e um desvio de 75 kHz, por exemplo esse quociente gira em

torno de 0,007; j com uma FI de 450 kHz essa diviso d 0,17. A freqncia menor,

portanto, melhora a relao S/R em cerca de 28 dB.

Encerrando esta parte, podemos afirmar que um PLL utilizando apenas componentes discretos, trabalhando em 450 kHz e usando o comparador de fase da FIG. 08 e

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

18

o VCO da FIG. 06a, capaz de atingir 60 dB de relao sinal-rudo em transmisses

estereofnicas.

O PLL por realimentao

Como j vimos, o maior problema ao se utilizar um PLL convencional como detector

de FM provm da padronizao da FI em 10,7 MHz. Isto significa que praticamente

todos os estgios iniciais de FM disponveis no comrcio tm uma FI desse valor.

Alm disso, deve-se prever a incluso de um controle automtico de freqncia, utilizando uma tenso extrada do prprio PLL.

No entanto, se forem removidos alguns componentes do lao do CAF, em um sintonizador convencional, o oscilador local poder servir de VCO. A linearidade desse

VCO ser bastante razovel, j que desvios de 75 kHz so pequenos em comparao com a freqncia de trabalho (cerca de 100 MHz). Quanto freqncia de referncia para o comparador de fase, poder ser fornecida por um oscilador estvel,

onde o elemento determinante seja um cristal de quartzo ou um filtro cermico -a

fim de evitar o rudo provocado no VCO por instabilidade de fase, particularmente

intenso em 10,7 MHz.

Na FIG. 13 temos o diagrama de blocos de um PLL desse tipo. O sinal vindo da antena misturado com o enviado pelo TVCO, dando origem a um sinal de 10,7 MHz

que passa por um filtro de FI e depois vai para o comparador de fase. A outra entrada do comparador recebe uma referncia de 10,7 MHz de alta estabilidade; assim

sendo, sempre que o lao fechado, o TVCO segue os desvios do sinal de entrada.

Na prtica, isto implica em uma reduo considervel na deriva do sinal de 10,7

MHz, da o nome de PLL por realimentao. E, graas reduo dos desvios, a

largura de banda de FI pode ser bem menor do que em receptores comuns. De fato,

no artigo Sistemas de modulao, desta mesma edio, a mnima largura de faixa

de um sinal de FM dada por:

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

19

Bmin = 2(m+1) fLfmax

que uma relao vlida quando m muito maior do que 1. Nos PLL por realimentao, porm, o ndice de modulao do sinal de FI bastante inferior unidade, contribuindo para reduzir a largura de faixa.

Figura 13 O PLL de realimentao difere basicamente do convencional pela incluso de um filtro de FI no lao de controle.

A grande vantagem dos sistemas PLL por realimentao, portanto, reside basicamente na largura de banda de FI, que se torna independente da deriva, passando a

depender apenas da maior freqncia de modulao. Obtm-se, dessa forma, melhores relaes sinal-rudo e menos distoro que nos receptores convencionais

embora o grau de melhora v sempre depender do ndice original de modulao do

sinal vindo da antena.

No caso das transmisses mono de FM, com a mxima freqncia de modulao de

15 kHz e um ndice de modulao de 5, a largura de faixa deve ser de 180 kHz nos

receptores comuns, ao passo que nos modelos que empregam PLL por realimenta-

DIGITADO E FORMATADO POR WANDER RODRIGUES

SISTEMAS PLL

20

o ela no passa de 30 kHz. A relao tambm favorvel para as transmisses

estereofnicas, na qual a freqncia mxima de modulao (53 kHz) implica em

uma faixa de 106 kHz no PLL por realimentao.

Apesar de ser conhecido antes mesmo da introduo das transmisses de FM estreo, o princpio do PLL por realimentao foi incompreensivelmente suplantado pelos sistemas multiplex, e assim perdeu-se a oportunidade de melhorar a recepo de

sinais estereofnicos. O que no nos impede de afirmar que um circuito semelhante

ao da FIG. 13 poderia, ainda hoje, proporcionar uma boa reduo no custo do receptor, se comparado aos sistemas convencionais com desempenho equivalente.

Os circuitos PLL por realimentao devem interessar particularmente aos radioamadores, por permitirem melhorias significativas na relao sinal/rudo, desde que seja

especificada uma baixa freqncia mxima de modulao. As bases esto a para

quem quiser tentar e as faixas de UHF e VHF de radioamadorismo oferecem possibilidades ilimitadas de experimentao.

Referncia Bibliogrfica

Revista Elektor. Sistemas PLL. P. 13 - 19

DIGITADO E FORMATADO POR WANDER RODRIGUES

Vous aimerez peut-être aussi

- PLLDocument24 pagesPLLHenrique Tannús CarvalhoPas encore d'évaluation

- Como funciona o PLLDocument6 pagesComo funciona o PLLMárcio CunhaPas encore d'évaluation

- PLL Ou Phase Locked LoopDocument10 pagesPLL Ou Phase Locked Loopivan bragaPas encore d'évaluation

- Apostila RF Cap7Document8 pagesApostila RF Cap7da3dbbf9c6Pas encore d'évaluation

- Como funciona o PLLDocument6 pagesComo funciona o PLLAllan DennisPas encore d'évaluation

- Fundamentos de OsciladoresDocument62 pagesFundamentos de OsciladoresEmanuel Baldissera100% (1)

- O Temporizador 555 emDocument14 pagesO Temporizador 555 emdevecchiPas encore d'évaluation

- PWMDocument11 pagesPWMErick RoblesPas encore d'évaluation

- Ampl Op: CaracterísticasDocument13 pagesAmpl Op: CaracterísticasStephany Lyra100% (1)

- Gerador de ondas e modulação PWM/FMDocument13 pagesGerador de ondas e modulação PWM/FMRodney RibeiroPas encore d'évaluation

- Experimento #5: IntroduçãoDocument12 pagesExperimento #5: IntroduçãoFiegiPas encore d'évaluation

- Conheça o PLL - Saber Eletrônica OnlineDocument4 pagesConheça o PLL - Saber Eletrônica OnlineGuilherme MariniPas encore d'évaluation

- Circuito Horizontal (Cont)Document5 pagesCircuito Horizontal (Cont)api-3800166100% (1)

- 44-Comparaçao Entre Circuitos RetificadoresDocument19 pages44-Comparaçao Entre Circuitos RetificadoresGhêeysoon ReedPas encore d'évaluation

- Relatório 3 - Amplificador Classe ABDocument25 pagesRelatório 3 - Amplificador Classe ABJader Vinicius Nascimento0% (1)

- Multivibrador AstávelDocument8 pagesMultivibrador AstávelHenrique Tannús CarvalhoPas encore d'évaluation

- F429 - Relatório 2 - RC e RLDocument13 pagesF429 - Relatório 2 - RC e RLJBBARPas encore d'évaluation

- 3.a Aula PAE 04 ChoppersDocument50 pages3.a Aula PAE 04 ChoppersFernando Santana100% (1)

- Retificadores de PrecisaoDocument18 pagesRetificadores de PrecisaoThiago RodriguesPas encore d'évaluation

- Conversores DC/DC: Buck, Boost e Buck-BoostDocument24 pagesConversores DC/DC: Buck, Boost e Buck-BoostEmanoel RibeiroPas encore d'évaluation

- Aula.04 - Transistor TBJ Operação em CADocument19 pagesAula.04 - Transistor TBJ Operação em CAMatheus FiliéPas encore d'évaluation

- Circuitos Não LinearesDocument59 pagesCircuitos Não LinearesThais FaçanhaPas encore d'évaluation

- Capitulo 8 - Conversores e ModuladoresDocument8 pagesCapitulo 8 - Conversores e ModuladoresEmanuel LimaPas encore d'évaluation

- TCM ModelagemDocument9 pagesTCM ModelageminfoteccftvPas encore d'évaluation

- Circuito SG3525 conversor CC-CCDocument7 pagesCircuito SG3525 conversor CC-CCNikolas Augusto100% (1)

- Relatorio LVDT PDFDocument12 pagesRelatorio LVDT PDFjosehenriquemdPas encore d'évaluation

- Relatório - Exp3 - Amplificadores Classe B e AB - Eletrônica Aplicada - Trim4.1Document7 pagesRelatório - Exp3 - Amplificadores Classe B e AB - Eletrônica Aplicada - Trim4.1Fernando Henrique G. ZucatelliPas encore d'évaluation

- Circuitos Multivibradores CMOSDocument13 pagesCircuitos Multivibradores CMOSRodolfo BaltieriPas encore d'évaluation

- Amplificador diferencial: introdução e análiseDocument13 pagesAmplificador diferencial: introdução e análiseadolfoPas encore d'évaluation

- Controlar motores com inversores de frequênciaDocument12 pagesControlar motores com inversores de frequênciaanon_656790980Pas encore d'évaluation

- Oscilador HartleyDocument6 pagesOscilador HartleyJaisom SilveiraPas encore d'évaluation

- GRUPO 3 (Final)Document16 pagesGRUPO 3 (Final)Chande JúniorPas encore d'évaluation

- Relatório 01 - Sistemas Eletronicos - Amplificadores OperacionaisDocument14 pagesRelatório 01 - Sistemas Eletronicos - Amplificadores OperacionaisPedro Lucas Rodrigues SousaPas encore d'évaluation

- Projeto de fonte chaveada com conversor flybackDocument36 pagesProjeto de fonte chaveada com conversor flybackmarcor08Pas encore d'évaluation

- Cicloconversor monofásico com carga resistivaDocument10 pagesCicloconversor monofásico com carga resistivaMaurrizzyWestonLanclacheJotamo0% (1)

- Elo-Lab Exp-11 Amplificador Emissor ComumDocument13 pagesElo-Lab Exp-11 Amplificador Emissor ComumLuciano CamilloPas encore d'évaluation

- OSCILADORESDocument48 pagesOSCILADORESjoaoteixeira25100% (1)

- Choppers CC-CC: introdução aos conversores CC-CCDocument37 pagesChoppers CC-CC: introdução aos conversores CC-CCJoao Carlos CumbanePas encore d'évaluation

- Rectificador de meia-onda e onda completaDocument6 pagesRectificador de meia-onda e onda completaGilmar FerrettiPas encore d'évaluation

- Testar Transformador de Linhas (Flyback)Document6 pagesTestar Transformador de Linhas (Flyback)vilmar konageski jr86% (7)

- Timer 555Document9 pagesTimer 555arthurdasilvapereiraPas encore d'évaluation

- EP - Sub - Aula 8Document19 pagesEP - Sub - Aula 8André BertoniPas encore d'évaluation

- Relatório AmpOpDocument14 pagesRelatório AmpOpeduardohcmendesPas encore d'évaluation

- Amplificadores em CascataDocument24 pagesAmplificadores em CascataMatheus Padilha100% (1)

- Circuito 555 aplicaçõesDocument6 pagesCircuito 555 aplicaçõesEdson Luis FreitasPas encore d'évaluation

- Sistema DigitalDocument20 pagesSistema DigitalEmanuella Carvalho AlmeidaPas encore d'évaluation

- Captulo 5 - Modelagem Do Transistor e Anlise de Pequenos Sinais-Aula1Document62 pagesCaptulo 5 - Modelagem Do Transistor e Anlise de Pequenos Sinais-Aula1Kelvin JordanPas encore d'évaluation

- Testador de BobinaDocument6 pagesTestador de BobinaAlyne Cristina Bernardi JonerPas encore d'évaluation

- BJT - Espelhos e Fontes de CorrenteDocument33 pagesBJT - Espelhos e Fontes de Correntevictorw63Pas encore d'évaluation

- 5 Fundamentos de AmplificadoresDocument10 pages5 Fundamentos de AmplificadoresVasco Joaquim MhulaPas encore d'évaluation

- Amplificador DiferenciadorDocument4 pagesAmplificador DiferenciadorThiago Silveira Olivera100% (1)

- Amplificador não-inversor CA com AOPDocument7 pagesAmplificador não-inversor CA com AOPBarbaraPas encore d'évaluation

- Amplificadores transistor: conceitos e análiseDocument32 pagesAmplificadores transistor: conceitos e análiseThais CarvalhoPas encore d'évaluation

- PROJETO DE UM CONVERSOR BUCK BOOST SIEPE2017 AlexandrePreisslerDocument5 pagesPROJETO DE UM CONVERSOR BUCK BOOST SIEPE2017 AlexandrePreisslerAlexandre Welter PreisslerPas encore d'évaluation

- Projetos Em Clp Ladder Baseado No Twidosuite Parte IvD'EverandProjetos Em Clp Ladder Baseado No Twidosuite Parte IvPas encore d'évaluation

- Catalogo Clamper - Dispositivos de Proteção Contra SurtosDocument22 pagesCatalogo Clamper - Dispositivos de Proteção Contra SurtosWisller Jefferson100% (1)

- Control Adore SpidDocument29 pagesControl Adore SpidLeandro LuzPas encore d'évaluation

- Exercícios de produtos notáveis e fatoraçãoDocument5 pagesExercícios de produtos notáveis e fatoraçãoadriano2fPas encore d'évaluation

- Dicas de Verificação em Instalação ElétricaDocument2 pagesDicas de Verificação em Instalação ElétricaranunksPas encore d'évaluation

- Cap3 DiagramaBlocosDocument13 pagesCap3 DiagramaBlocosGustavo De Souza SatyroPas encore d'évaluation

- Assessoria técnica Serviço SocialDocument19 pagesAssessoria técnica Serviço SocialJanaína BandeiraPas encore d'évaluation

- Lista de Revisão Av03 de Gramática - 4°bimestreDocument2 pagesLista de Revisão Av03 de Gramática - 4°bimestreWisller JeffersonPas encore d'évaluation

- Catalogo Clamper - Dispositivos de Proteção Contra SurtosDocument22 pagesCatalogo Clamper - Dispositivos de Proteção Contra SurtosWisller Jefferson100% (1)

- Artigo Nr10 Marcel AmorimDocument34 pagesArtigo Nr10 Marcel AmorimWisller JeffersonPas encore d'évaluation

- Comandos Pneumáticos e HidráulicosDocument180 pagesComandos Pneumáticos e HidráulicosluizbarbieriPas encore d'évaluation

- Prova Ufam2013 Ns Administrador InfoDocument8 pagesProva Ufam2013 Ns Administrador InfoWisller JeffersonPas encore d'évaluation

- Apostila de Controle Linear IDocument240 pagesApostila de Controle Linear IAntonio Carlos SilvaPas encore d'évaluation

- Lista de Revisão Av03 de Math - 4°bimestreDocument2 pagesLista de Revisão Av03 de Math - 4°bimestreWisller JeffersonPas encore d'évaluation

- Conceitos Básicos de RS-485 e RS-422Document7 pagesConceitos Básicos de RS-485 e RS-422lordmagusbrPas encore d'évaluation

- 14 - ValvulasDocument176 pages14 - ValvulasWanderley Terci EstevesPas encore d'évaluation

- Controlador PIDDocument6 pagesControlador PIDadilsondissoPas encore d'évaluation

- Teorema Da Diverg EnciaDocument13 pagesTeorema Da Diverg Enciabricklayer_vocalPas encore d'évaluation

- (APOSTILA) Resposta No Tempo de Sistemas de Primeira e Segunda OrdemDocument11 pages(APOSTILA) Resposta No Tempo de Sistemas de Primeira e Segunda OrdemAdriano BrandãoPas encore d'évaluation

- Trans LinDocument39 pagesTrans LinJCarlos MatosPas encore d'évaluation

- Operad DiferDocument1 pageOperad DiferWisller JeffersonPas encore d'évaluation

- Redução de diagramas de blocos em 8 regrasDocument3 pagesRedução de diagramas de blocos em 8 regrasWisller JeffersonPas encore d'évaluation

- Controle DinâmicoDocument62 pagesControle DinâmicoRafael Lopes CarneiroPas encore d'évaluation

- Aula EME12 Lugar RaizesDocument12 pagesAula EME12 Lugar RaizesMariana SanchezPas encore d'évaluation

- Máquinas SíncronasDocument91 pagesMáquinas SíncronasAlfredo EscáratePas encore d'évaluation

- 10 - Campos Variantes No TempoDocument19 pages10 - Campos Variantes No TempoWisller JeffersonPas encore d'évaluation

- Força Magnética Sobre Condutores Cap11Document8 pagesForça Magnética Sobre Condutores Cap11Wisller JeffersonPas encore d'évaluation

- 08 - For-As Magnetic As, Materiais e IndutanciaDocument17 pages08 - For-As Magnetic As, Materiais e IndutanciaLuiz Alberto CarbobiachPas encore d'évaluation

- Ondas-Eletromagneticas - Energia Poiting - ExercíciosDocument4 pagesOndas-Eletromagneticas - Energia Poiting - ExercíciosDiego SantosPas encore d'évaluation

- Eletromagnetismo.01.UFMG - Prof Joao Antonio VasconcelosDocument58 pagesEletromagnetismo.01.UFMG - Prof Joao Antonio VasconcelosWilliam Marques100% (1)

- Equações de MaxwellDocument0 pageEquações de MaxwellRoberto MeiraPas encore d'évaluation

- Linhas de TransmissãoDocument40 pagesLinhas de TransmissãoRuan Filipi Putka100% (1)

- Regulamento técnico Mercosul fumaça dieselDocument24 pagesRegulamento técnico Mercosul fumaça dieselRogério Caiado MachadoPas encore d'évaluation

- 3 - Amplificadores Operacionais v2.0Document44 pages3 - Amplificadores Operacionais v2.0carlos augusto do carmo braiaPas encore d'évaluation

- Relatorio Final - AROMARKETINGDocument6 pagesRelatorio Final - AROMARKETINGMatheus AndradePas encore d'évaluation

- Datasheet Painel Solar 550w Elgin ELG550 M72HOD - V1Document2 pagesDatasheet Painel Solar 550w Elgin ELG550 M72HOD - V1Marco TúlioPas encore d'évaluation

- Plano Ensino Eletricidade 2009 PortalDocument4 pagesPlano Ensino Eletricidade 2009 PortalJean César Barbosa PereiraPas encore d'évaluation

- Transistores de PotênciaDocument23 pagesTransistores de PotênciaDilsael MelekPas encore d'évaluation

- Motores Perkins Serie 600Document36 pagesMotores Perkins Serie 600Barra Nova FerreiraPas encore d'évaluation

- WEG CFW 09 Inversor de Frequencia 0899.5180 3.3x Manual Portugues BRDocument328 pagesWEG CFW 09 Inversor de Frequencia 0899.5180 3.3x Manual Portugues BRRubem Soares100% (2)

- Transformador de tensão e corrente para carga trifásicaDocument4 pagesTransformador de tensão e corrente para carga trifásicaHeli CarlosPas encore d'évaluation

- Comportamento Dos Geradores Na Presença de CapacitoresDocument7 pagesComportamento Dos Geradores Na Presença de Capacitoresccprado1Pas encore d'évaluation

- Mini Dicionario de EletrotecnicaDocument17 pagesMini Dicionario de Eletrotecnicarogerio limaPas encore d'évaluation

- Ams Trex Device ComunicadorDocument16 pagesAms Trex Device Comunicadorluiz claudioPas encore d'évaluation

- Simulações de Circuitos Retificadores Trifásicos de Meia E Onda Completa No Software Matlab/Simulink™Document28 pagesSimulações de Circuitos Retificadores Trifásicos de Meia E Onda Completa No Software Matlab/Simulink™Vinicius MartinsPas encore d'évaluation

- Amplificadores TransistorizadosDocument7 pagesAmplificadores TransistorizadosAnderson DutraPas encore d'évaluation

- Sefs 02Document85 pagesSefs 02CesarLimaPas encore d'évaluation

- Construindo gerador senoidal 1kHzDocument4 pagesConstruindo gerador senoidal 1kHzChellton100% (1)

- Partes fixas micrômetroDocument217 pagesPartes fixas micrômetroCarlyson SilvaPas encore d'évaluation

- Amplificadores analógicos: ganhos, potências e filtrosDocument4 pagesAmplificadores analógicos: ganhos, potências e filtrosJoão ValePas encore d'évaluation

- NTCB 42 2020 Inspecao Visual em Instalacoes EletricasDocument7 pagesNTCB 42 2020 Inspecao Visual em Instalacoes EletricasGetulio JuniorPas encore d'évaluation

- Circuitos RLC série - Regime permanente senoidalDocument5 pagesCircuitos RLC série - Regime permanente senoidalRodrigues Antonio NaboPas encore d'évaluation

- O Campo Elétrico e suas PropriedadesDocument5 pagesO Campo Elétrico e suas PropriedadesMaria João PinhoPas encore d'évaluation

- Apostila de Conserto de ImpressorasDocument26 pagesApostila de Conserto de ImpressorasAllan PereiraPas encore d'évaluation

- Fundamentos gerais dos sistemas elétricos de potênciaDocument5 pagesFundamentos gerais dos sistemas elétricos de potênciaRaclenir LopesPas encore d'évaluation

- Manual 2103A 002Document23 pagesManual 2103A 002psmorais51Pas encore d'évaluation

- Cálculo de potência aparente, corrente e fator de potência em circuito elétricoDocument1 pageCálculo de potência aparente, corrente e fator de potência em circuito elétricoKelitonPas encore d'évaluation

- Guia Geral - Códigos de Avaria - Infortronica, Lda - Autodata, Atelio, Haynes, Online EstimateDocument13 pagesGuia Geral - Códigos de Avaria - Infortronica, Lda - Autodata, Atelio, Haynes, Online EstimateRicardinhorickPas encore d'évaluation

- Catalogo Todos Os ProdutosDocument16 pagesCatalogo Todos Os ProdutosLuciano Siqueira OliveiraPas encore d'évaluation

- Circuito Básico Versus Circuito RegenerativoDocument3 pagesCircuito Básico Versus Circuito RegenerativoFelipe Brandão dos ReisPas encore d'évaluation