Académique Documents

Professionnel Documents

Culture Documents

Errata

Transféré par

Predrag PejicCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Errata

Transféré par

Predrag PejicDroits d'auteur :

Formats disponibles

ES_LPC11U1x

Errata sheet LPC11U1x

Rev. 3.1 30 September 2013

Errata sheet

Document information

Info

Content

Keywords

LPC11U12FHN33, LPC11U12FBD48, LPC11U13FBD48,

LPC11U14FHN33, LPC11U14FHI33, LPC11U14FBD48,

LPC11U14FET48, LPC11U1x errata

Abstract

This errata sheet describes both the known functional problems and any

deviations from the electrical specifications known at the release date of

this document.

Each deviation is assigned a number and its history is tracked in a table.

ES_LPC11U1x

NXP Semiconductors

Errata sheet LPC11U1x

Revision history

Rev

Date

3.1

20130930

20130117

2.1

20121002

20120112

1.2

20110901

1.1

20110622

20110601

Description

Added Note.2.

Added I2C.1.

Added Rev A to Note.1.

Added Rev B.

Added ADC.1.

Added Note.1.

Section 3.4: Corrected device name.

Initial version.

Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

ES_LPC11U1X

Errata sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3.1 30 September 2013

NXP B.V. 2013. All rights reserved.

2 of 13

ES_LPC11U1x

NXP Semiconductors

Errata sheet LPC11U1x

1. Product identification

The LPC11U1x devices typically have the following top-side marking:

LPC11U1x

/xxx

xxxxxxx

xxYYWWxR[x]

The last letter in the last line (field R) will identify the device revision. This Errata Sheet

covers the following revisions of the LPC11U1x:

Table 1.

Device revision table

Revision identifier (R)

Revision description

Initial device revision

Second device revision

Field YY states the year the device was manufactured. Field WW states the week the

device was manufactured during that year.

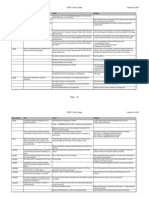

2. Errata overview

Table 2.

Errata summary table

Functional

problems

Short description

ADC.1

A/D Global Data register should not be used with burst A, B

mode or hardware triggering.

Section 3.1

I2C.1

In the slave-transmitter mode, the device set in the

monitor mode must write a dummy value of 0xFF into

the DAT register.

A, B

Section 3.2

IRC.1

Accuracy of the Internal RC oscillator (IRC) frequency

may be outside of the 12 MHz 1 % specification.

Section 3.3

USART.1

False positive break indicator events may occur.

Section 3.4

USART.2

SCI Transmit retry error interrupt not working.

Section 3.5

USB.1

The VBUSDEBOUNCED status bit is not updated

correctly.

Section 3.6

Table 3.

Revision identifier

Detailed description

AC/DC deviations table

AC/DC

deviations

Short description

Revision identifier

Detailed description

n/a

n/a

n/a

n/a

ES_LPC11U1X

Errata sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3.1 30 September 2013

NXP B.V. 2013. All rights reserved.

3 of 13

ES_LPC11U1x

NXP Semiconductors

Errata sheet LPC11U1x

Table 4.

Errata notes table

Errata notes

Short description

Revision identifier

Detailed description

Note.1

During power-up, an unexpected glitch (low pulse)

could occur on the port pins as the VDD supply ramps

up.

A, B

Section 5.1

Note.2

Depending on bootloader version, pin(s) PIO0_1 or

PIO0_1 and PIO0_3 must be pulled LOW to enter

UART ISP mode.

A, B

Section 5.2

ES_LPC11U1X

Errata sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3.1 30 September 2013

NXP B.V. 2013. All rights reserved.

4 of 13

ES_LPC11U1x

NXP Semiconductors

Errata sheet LPC11U1x

3. Functional problems detail

3.1 ADC.1: A/D Global Data register should not be used with burst mode

or hardware triggering

Introduction:

On the LPC11U1x, the START field and the BURST bit in the A/D control register specify

whether A/D conversions are initiated via software command, in response to some

hardware trigger, or continuously in burst ("hardware-scan") mode. Results of the ADC

conversions can be read in one of two ways. One is to use the A/D Global Data Register

to read all data from the ADC. Another is to use the individual A/D Channel Data

Registers.

Problem:

If the burst mode is enabled (BURST bit set to 1) or if hardware triggering is specified,

the A/D conversion results read from the A/D Global Data register could be incorrect. If

conversions are only launched directly by software command (BURST bit = '0' and START

= 001), the results read from the A/D Global Data register will be correct provided the

previous result is read prior to launching a new conversion.

Work-around:

When using either burst mode or hardware triggering, the individual A/D Channel Data

registers should be used instead of the A/D Global Data register to read the A/D

conversion results.

ES_LPC11U1X

Errata sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3.1 30 September 2013

NXP B.V. 2013. All rights reserved.

5 of 13

ES_LPC11U1x

NXP Semiconductors

Errata sheet LPC11U1x

3.2 I2C.1: In the slave-transmitter mode, the device set in the monitor

mode must write a dummy value of 0xFF into the DAT register

Introduction:

The I2C monitor allows the device to monitor the I2C traffic on the I2C bus in a

non-intrusive way.

Problem:

In the slave-transmitter mode, the device set in the monitor mode must write a dummy

value of 0xFF into the DAT register. If this is not done, the received data from the slave

device will be corrupted. To allow the monitor mode to have sufficient time to process the

data on the I2C bus, the device may need to have the ability to stretch the I2C clock.

Under this condition, the I2C monitor mode is not 100% non-intrusive.

Work-around:

When setting the device in monitor mode, enable the ENA_SCL bit in the MMCTRL

register to allow clock stretching.

Software code example to enable the ENA_SCL bit:

LPC_I2C_MMCTRL |= (1<<1); //Enable ENA_SCL bit

In the I2C ISR routine, for the status code related to the slave-transmitter mode, write the

value of 0xFF into the DAT register to prevent data corruption. In order to avoid stretching

the SCL clock, the data byte can be saved in a buffer and processed in the Main loop.

This ensures the SI flag is cleared as fast as possible.

Software code example for the slave-transmitter mode:

case

case

case

case

case

0xA8:

// Own SLA + R has been received, ACK returned

0xB0:

0xB8:

// data byte in DAT transmitted, ACK received

0xC0:

// (last) data byte transmitted, NACK received

0xC8:

// last data byte in DAT transmitted, ACK received

DataByte = LPC_I2C->DATA_BUFFER; //Save data. Data can be process in Main loop

LPC_I2C->DAT = 0xFF;

// Pretend to shift out 0xFF

LPC_I2C->CONCLR = 0x08;

// clear flag SI

break;

ES_LPC11U1X

Errata sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3.1 30 September 2013

NXP B.V. 2013. All rights reserved.

6 of 13

ES_LPC11U1x

NXP Semiconductors

Errata sheet LPC11U1x

3.3 IRC.1: Accuracy of the IRC frequency may be outside of the

12 MHz 1 % specification

Introduction:

The LPC11U1x has three independent oscillators: the system oscillator, the Internal RC

oscillator (IRC), and the Watchdog oscillator. The IRC can be optionally used as a clock

source for the CPU, the system PLL, and the peripherals blocks. The IRC frequency spec

is 12 MHz 1 % accuracy over the entire voltage and temperature range. During

In-System Programming (ISP), the auto-baud routine is expecting the IRC frequency to be

12 MHz 1 % and is used to synchronize with the host via serial port 0.

Problem:

On the LPC11U1x Rev A device(s) only, the IRC frequency could be outside the nominal

frequency of 12 MHz 1 %. The IRC is hence not recommended to be used as a clock

source. This behavior could also affect the auto-baud routine's ability to synchronize with

the host via serial port 0 during ISP.

Work-around:

None. This errata was fixed on the LPC11U1x Rev B device.

ES_LPC11U1X

Errata sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3.1 30 September 2013

NXP B.V. 2013. All rights reserved.

7 of 13

ES_LPC11U1x

NXP Semiconductors

Errata sheet LPC11U1x

3.4 USART.1: False positive break interrupt events may occur

Introduction:

The LPC11U1x device family features an option to operate the UART in synchronous

mode.

Problem:

When using synchronous UART mode (USART) under the following conditions:

CSCEN = 0 (SCK active only during transmission)

CSRC = 0 (Synchronous Slave Mode)

FES = 1 (Falling Edge Sampling)

SSDIS = 0 (Use Start and Stop Bit)

The external transmitting device (Master) sends start and stop bits

The external device transmits 0x00

The Break Interrupt (BI) flag can become set, despite the fact that no break condition on

the bus has occurred. This problem does not manifest when the external master device

uses two stop bits.

Work-around:

None, however in some cases system designers have control over the protocol being

used between devices and can avoid the error condition outlined above in their system

design and/or communication protocol.

ES_LPC11U1X

Errata sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3.1 30 September 2013

NXP B.V. 2013. All rights reserved.

8 of 13

ES_LPC11U1x

NXP Semiconductors

Errata sheet LPC11U1x

3.5 USART.2: SCI Transmit retry error interrupt not working

Introduction:

The USART can be used as a ISO 7816-3 compliant asynchronous smart card interface

(SCI). When used in this mode, data transmissions are automatically retried if a NACK is

received. If the number of retries exceeds the maximum allowed value (set via the

TXRETRY field in the (SCICTRL register) the USART is locked and a transmit error

interrupt is generated.

Problem:

When a transmission error occurs, and the interface does not initiate a deactivation

sequence (e.g. when the TXRETRY register has been set to 0x0) a lock state is entered.

Work-around:

Recovery from this locked state can be achieved as follows:

When the USART external smartcard clock is used:

1. After a transmission error occurs, wait for at minimum half a smartcard clock period

2. Reset the Tx FIFO

When The USART external smartcard clock is not used:

1. Reset the Tx FIFO

2. Toggle the SCIEN bit

ES_LPC11U1X

Errata sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3.1 30 September 2013

NXP B.V. 2013. All rights reserved.

9 of 13

ES_LPC11U1x

NXP Semiconductors

Errata sheet LPC11U1x

3.6 USB.1: The VBUSDEBOUNCED status bit is not updated correctly

Introduction:

The VBUSDEBOUNCED status bit (bit 28 in DEVCMDSTAT register) indicates if Vbus is

detected or not. The bit is set when Vbus becomes high. It gets set to zero if Vbus is low

for at least 3 ms. If this bit is high and the DCon bit (bit 16 in DEVCMDSTAT register) is

set, the pull-up resistor on USB_DP pin will be enabled to signal a connect.

Problem:

When the LPC11U1x USB interface is configured as a self-powered device, occasionally,

the VBUSDEBOUNCED status (bit 28) is not updated correctly in the DEVCMDSTAT

register when the USB connector is disconnected from the host while the USB_NeedClk

is not set to "PLL Always ON" (bit 9 in DEVCMDSTAT register). When the

VBUSDEBOUNCED bit doesn't reflect correct status, the USB_CONNECT signal pin will

drive the pull-up resistor on the USB_DP pin all the time. In turn, the LPC11U1x will fail

the back voltage test which is part of the USB compliance test (USB-IF).

Work-around:

1. Turn "PLL always ON" (bit 9) off by setting the bit to zero in the DEVCMDSTAT

register.

2. Enable the clock to the GPIO Pin interrupts register interface (PINT, bit 19) in the

SYSAHBCLKCTRL register.

3. Configure the PIO0_3 pin as USB_VBUS function (PIO0_3 register) and the PIO0_6

pin as USB_CONNECT function (PIO0_6 register)

4. Select the USB_VBUS (PIO0_3 pin) to be one of the GPIO pin interrupt sources by

setting the PINTSELx register, and configure the interrupt to trigger as a falling edge

sensitive.

5. When the GPIO pin interrupt occurs (VBUS is falling when USB cable is

disconnected), check the VBUSDEBOUNCED status (bit 28) in the DEVCMDSTAT

register. If it is still set, then configure the USB_CONNECT pin as PIO0_6 function,

drive it output high, wait for VBUSDEBOUNCED bit to go low, and then configure the

PIO0_6 function back to USB_CONNECT function.

ES_LPC11U1X

Errata sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3.1 30 September 2013

NXP B.V. 2013. All rights reserved.

10 of 13

ES_LPC11U1x

NXP Semiconductors

Errata sheet LPC11U1x

4. AC/DC deviations detail

4.1 n/a

5. Errata notes detail

5.1 Note.1

The General Purpose I/O (GPIO) pins have configurable pull-up/pull-down resistors where

the pins are pulled up to the VDD level by default. During power-up, an unexpected glitch

(low pulse) could occur on the port pins as the VDD supply ramps up.

5.2 Note.2

For LPC11U1x parts with bootloader version 7.0, pins PIO0_1 and PIO0_3 must be pulled

LOW to enter UART ISP mode.

For LPC11U1x parts with bootloader version 7.1, pin PIO0_1 must be pulled LOW to enter

UART ISP mode.

ES_LPC11U1X

Errata sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3.1 30 September 2013

NXP B.V. 2013. All rights reserved.

11 of 13

ES_LPC11U1x

NXP Semiconductors

Errata sheet LPC11U1x

6. Legal information

6.1

Definitions

Draft The document is a draft version only. The content is still under

internal review and subject to formal approval, which may result in

modifications or additions. NXP Semiconductors does not give any

representations or warranties as to the accuracy or completeness of

information included herein and shall have no liability for the consequences of

use of such information.

6.2

Disclaimers

Limited warranty and liability Information in this document is believed to

be accurate and reliable. However, NXP Semiconductors does not give any

representations or warranties, expressed or implied, as to the accuracy or

completeness of such information and shall have no liability for the

consequences of use of such information. NXP Semiconductors takes no

responsibility for the content in this document if provided by an information

source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental,

punitive, special or consequential damages (including - without limitation - lost

profits, lost savings, business interruption, costs related to the removal or

replacement of any products or rework charges) whether or not such

damages are based on tort (including negligence), warranty, breach of

contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason

whatsoever, NXP Semiconductors aggregate and cumulative liability towards

customer for the products described herein shall be limited in accordance

with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes NXP Semiconductors reserves the right to make

changes to information published in this document, including without

limitation specifications and product descriptions, at any time and without

notice. This document supersedes and replaces all information supplied prior

to the publication hereof.

Suitability for use NXP Semiconductors products are not designed,

authorized or warranted to be suitable for use in life support, life-critical or

safety-critical systems or equipment, nor in applications where failure or

ES_LPC11U1X

Errata sheet

malfunction of an NXP Semiconductors product can reasonably be expected

to result in personal injury, death or severe property or environmental

damage. NXP Semiconductors and its suppliers accept no liability for

inclusion and/or use of NXP Semiconductors products in such equipment or

applications and therefore such inclusion and/or use is at the customers own

risk.

Applications Applications that are described herein for any of these

products are for illustrative purposes only. NXP Semiconductors makes no

representation or warranty that such applications will be suitable for the

specified use without further testing or modification.

Customers are responsible for the design and operation of their applications

and products using NXP Semiconductors products, and NXP Semiconductors

accepts no liability for any assistance with applications or customer product

design. It is customers sole responsibility to determine whether the NXP

Semiconductors product is suitable and fit for the customers applications and

products planned, as well as for the planned application and use of

customers third party customer(s). Customers should provide appropriate

design and operating safeguards to minimize the risks associated with their

applications and products.

NXP Semiconductors does not accept any liability related to any default,

damage, costs or problem which is based on any weakness or default in the

customers applications or products, or the application or use by customers

third party customer(s). Customer is responsible for doing all necessary

testing for the customers applications and products using NXP

Semiconductors products in order to avoid a default of the applications and

the products or of the application or use by customers third party

customer(s). NXP does not accept any liability in this respect.

Export control This document as well as the item(s) described herein

may be subject to export control regulations. Export might require a prior

authorization from competent authorities.

6.3

Trademarks

Notice: All referenced brands, product names, service names and trademarks

are the property of their respective owners.

All information provided in this document is subject to legal disclaimers.

Rev. 3.1 30 September 2013

NXP B.V. 2013. All rights reserved.

12 of 13

ES_LPC11U1x

NXP Semiconductors

Errata sheet LPC11U1x

7. Contents

1

2

3

3.1

3.2

3.3

3.4

3.5

3.6

4

4.1

5

5.1

5.2

6

6.1

6.2

6.3

7

Product identification . . . . . . . . . . . . . . . . . . . . 3

Errata overview . . . . . . . . . . . . . . . . . . . . . . . . . 3

Functional problems detail . . . . . . . . . . . . . . . . 5

ADC.1: A/D Global Data register should not be

used with burst mode or hardware triggering . . 5

I2C.1: In the slave-transmitter mode, the device

set in the monitor mode must write a dummy value

of 0xFF into the DAT register . . . . . . . . . . . . . . 6

IRC.1: Accuracy of the IRC frequency may be

outside of the 12 MHz 1 % specification . . . . 7

USART.1: False positive break interrupt events

may occur . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

USART.2: SCI Transmit retry error interrupt not

working . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

USB.1: The VBUSDEBOUNCED status bit is not

updated correctly . . . . . . . . . . . . . . . . . . . . . . 10

AC/DC deviations detail . . . . . . . . . . . . . . . . . 11

n/a. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Errata notes detail . . . . . . . . . . . . . . . . . . . . . . 11

Note.1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Note.2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Legal information. . . . . . . . . . . . . . . . . . . . . . . 12

Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Disclaimers . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Please be aware that important notices concerning this document and the product(s)

described herein, have been included in section Legal information.

NXP B.V. 2013.

All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 30 September 2013

Document identifier: ES_LPC11U1X

Vous aimerez peut-être aussi

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- !!!! Signal Integrity Considerations For High Speed Digital HardwareDocument12 pages!!!! Signal Integrity Considerations For High Speed Digital HardwarePredrag PejicPas encore d'évaluation

- 3rd, 5th, 7th Course OutlineDocument55 pages3rd, 5th, 7th Course OutlineSamiullah IlyasPas encore d'évaluation

- Types of Memory Allocation SchemesDocument15 pagesTypes of Memory Allocation SchemesMichael John Sabido93% (15)

- ARM7Document36 pagesARM7Yogesh SutharPas encore d'évaluation

- STEP7 ErrorCode EnglDocument37 pagesSTEP7 ErrorCode EnglVinoth RaviPas encore d'évaluation

- EECC0097Document6 pagesEECC0097Predrag PejicPas encore d'évaluation

- Beagle Board XM Reference ManualDocument164 pagesBeagle Board XM Reference Manualmhenryk1Pas encore d'évaluation

- STM32F103C8T6Document105 pagesSTM32F103C8T6Phạm Thế VũPas encore d'évaluation

- An203 - c8051fxxx Printed Circuit Board Design Notes - Silicon - LabsDocument22 pagesAn203 - c8051fxxx Printed Circuit Board Design Notes - Silicon - LabsEdson PaivaPas encore d'évaluation

- A51 1 Jurisic10 Low Sensitivity Active RC Allpole Filters Using Optimized BiquadsDocument16 pagesA51 1 Jurisic10 Low Sensitivity Active RC Allpole Filters Using Optimized BiquadsPredrag PejicPas encore d'évaluation

- An203 - c8051fxxx Printed Circuit Board Design Notes - Silicon - LabsDocument22 pagesAn203 - c8051fxxx Printed Circuit Board Design Notes - Silicon - LabsEdson PaivaPas encore d'évaluation

- WatchdogDocument10 pagesWatchdogxa yPas encore d'évaluation

- Interrupts: RST 7.5 RST 6.5 RST 5.5 1 Non-Vectored Intr 1 Non-Maskable Vectored TrapDocument11 pagesInterrupts: RST 7.5 RST 6.5 RST 5.5 1 Non-Vectored Intr 1 Non-Maskable Vectored TrapHamza Abu AjamiaPas encore d'évaluation

- Kinetix Error Codes-1Document18 pagesKinetix Error Codes-1Renzo DamianPas encore d'évaluation

- Service Monitoring Tool UserDocument88 pagesService Monitoring Tool UserwilliamPas encore d'évaluation

- Laboratory Manual: Department of Mechanical Engineering Faculty of EngineeringDocument24 pagesLaboratory Manual: Department of Mechanical Engineering Faculty of EngineeringwahtoiPas encore d'évaluation

- Cheat Sheet PDFDocument40 pagesCheat Sheet PDFxoureia laPas encore d'évaluation

- IM34M06P15-01E UsDocument708 pagesIM34M06P15-01E UsLovelySinghPas encore d'évaluation

- Embedded C Programming For 8051 Using KeilDocument12 pagesEmbedded C Programming For 8051 Using KeilNishant MittalPas encore d'évaluation

- Organization blocks overview S7-1200/1500Document2 pagesOrganization blocks overview S7-1200/1500Mehtab AhmedPas encore d'évaluation

- Basic Computer Organization and DesignDocument49 pagesBasic Computer Organization and Designsara_loloPas encore d'évaluation

- Intel 8008 Users ManualDocument62 pagesIntel 8008 Users ManualCarlos Eduardo MaidanaPas encore d'évaluation

- DatasheetDocument57 pagesDatasheetKrisiantoPas encore d'évaluation

- Vxworks Case StudyDocument11 pagesVxworks Case StudyPathella SudhakarPas encore d'évaluation

- CCS - View Topic - #Int - RDA and Disable - InterruptsDocument3 pagesCCS - View Topic - #Int - RDA and Disable - Interruptsapi-3755810100% (1)

- Porting The C-OS-II Real Time Operating System To The M16C MicrocontrollersDocument142 pagesPorting The C-OS-II Real Time Operating System To The M16C MicrocontrollersskalydPas encore d'évaluation

- i.MX 7dual Family of Applications Processors DatasheetDocument158 pagesi.MX 7dual Family of Applications Processors DatasheetHosein movahedian attarPas encore d'évaluation

- Microprocessors and Microcontrollers ArchitectureDocument148 pagesMicroprocessors and Microcontrollers ArchitectureMani KumarPas encore d'évaluation

- Pxros User GuideDocument188 pagesPxros User GuideimensassiPas encore d'évaluation

- Os (Unit 4 and 5)Document36 pagesOs (Unit 4 and 5)vikrant sharmaPas encore d'évaluation

- LM75Document12 pagesLM75tebeica2100% (2)

- Curriculum 2012 CSE PDFDocument125 pagesCurriculum 2012 CSE PDFRehan Umer100% (1)

- R5F21255SNFP Renesas PDFDocument525 pagesR5F21255SNFP Renesas PDFBernardo RatiaPas encore d'évaluation

- 6 and c200 Chipset Specification UpdateDocument82 pages6 and c200 Chipset Specification UpdateedyplayPas encore d'évaluation

- St Joseph's College student's term paper on 8086 MicroprocessorDocument37 pagesSt Joseph's College student's term paper on 8086 MicroprocessorWren D'silvaPas encore d'évaluation

- Malp Unit 6 Marks 14Document10 pagesMalp Unit 6 Marks 14Khilan MendaparaPas encore d'évaluation

- Hardware Features of 8051Document52 pagesHardware Features of 8051Manjunath Shimoga100% (1)