Académique Documents

Professionnel Documents

Culture Documents

AVR Programming

Transféré par

Saint TyagiCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

AVR Programming

Transféré par

Saint TyagiDroits d'auteur :

Formats disponibles

AVR

AVR

AVR

AVR

AVR

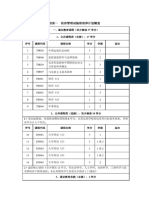

2.2.2

32

Flash

(4KX16

8KX8)

64 I/O

SRAM

(512X8)

SRAM

(0-64KX8)

AVR

AVR

AVR

AVR

AVR

10

2.3.5 I/O

,, AT90S8515

,:

.include"8515def.inc" ; I/O ,

\AVR\asmpack\appnotes\*.inc

AVR

11

(*.inc),,

, I/O !

AVR

12

SREG , ,, 1 ,

, 1,, 1 , 0 , SREG 36

AVR

13

AVR

14

http://WWW.SL.COM.CN

AVR

15

AVR

16

AVR

17

AVR

18

GIFR

AVR

19

TIMSK

TIMSK

AVR

20

1

SREG I OCIE1B( 1 B ) OCF1B 1

1

4 2 0

Res

90 0

3

ICF1 1

ICF1 1 1

ICR1 ICF1 ICF1

1

TOV0 / 0

1

0 TOV0 1 TOV0

TOV0 1 SREG I TOIE0

0

TOV0 1

2.5.2

INT1 INT0 INT0 INT1

MCU

MCUCR

MCU

MCUCR

2 5 3

AVR 4 4

4 2

2 2

4 4

2 2 AVR

SREG AVR

SREG

2 5 4

AVR

21

MCU MCUCR

MCUCR MCU

7

6

5

4

3

2

1

0

SM ISC11 ISC10 ISO01 ISC00

MCUCR

35

55 SRE SRW SE

: R W

: $00

7

SRE SRAM

A8 A15 C

SRE 1 SRAM AD0 AD7 A

RD WR D

SRE

SRAM

2 3 2 SRAM

SRE SRAM

6--SRW SRWM

SRW 1 SRAM SRW

0 SRAM 2 2 12 SRAM

2.1 SRAM

5--SE:

SE 1 SLEEP MCU

MCU SLEEP SE

4 --SM:

SM 0 SE 1

2 6 1

3,2

ISC11 ISC10 1, 1 0

SREG I GIMSK 1

INT1 2 4 INT1

ISC01 ISC00 0, 1 0

1 0

SREG I GIMSK 0

INT0 2 5 INT0

ISC10 ISC00 INT0 GIMSK

AVR

22

AVR

2 6 1

MCUCR SE 1 SLEEP MCU

MCU SLEEP

I O MCU

MCU 16 ms

MCU

2.6.2

SM 0 SLEEP MCU

CPU

CPU

CPU

ACSR ACD

2.6.3

SM 1 SLEEP MCU

MCU MCU

2.7 AVR

AT90S8515 2 8 16

10 2

2.7.1

2

AVR

23

20

CK 8 CK 64 CK 256 CK 1024 CK

CK

2.7.2

2 21 0

8 0 CK

0

TCCR0

TIFR

0

TIMSK

0 CPU

CPU

CPU

8 0

AVR

24

TCCRO

5

1

0

CS02 CS01

CS00

TCCR0

R

R W

R/W

R/W

-----53

:

R

R

R

R

: $00

7 3 Res

90 0

2,1,0

CS02,CS01,CS00: 0 2 1 0

0 2 1 0 0 2 6

33

2.6 0

AVR

25

TCNT0

7

6

5

4

3

2

1

0

MSB

LSB

TCNT0

$32 $52

:

R/W

R/W R/W R/W R/W

R/W

R/W

R/W

: $00

0 0

0

2.7.3

16

2.22 1

16 1 CK

1

TCCR1A TCCR1B

TCCR1A TCCR1B

1

TIMSK

1 CPU

2 CPU

CPU

16 1

1

1 1A 1B

OCR1A OCR1B

1 A

8 9 10 OCR1A

OCR1B PWM

1

ICR1

ICP

1

TCCR1B

ICP 2 23 1

2 24

4

XTAL

AVR

1 A

$2F

$4F

7

COM1A1

:

R/W

: $00

26

TCCR1A

22

COM1A0

COM1B1

R/W

R/W

4

COM1B0

R/W

3

--

--

PWM11

PWM10

R/W

TCCR1A

R/W

7,6

COMM1A1 COM1A0: 1 1 0

COM1A1 COM1A0 1

OC1A A 1 I O

1 2 7

AVR

27

COMM1B1 COM1B0: 1 1 0

5,4

COM1B1 COM1B0 / 1

OC1B B 1 I O

1 2 7

PWM 2 11

COM1X1 COM1X0 1 TIMSK

Res:

3,2

90 0

1,0--PWM11,PWM10:

2 8 1 PWM

AVR

1 B

7

ICNC1

$2E $4E

:

R/W

: $00

28

TCCR1B

6

5

4

3

2

1

0

ICES1 --CTC1 CS12 CS11 CS10

TCCR1B

R/W

R

R

R/W

R/W

R/W

R/W

7

ICNC1 4CKS)

ICNC1 0 ICP

/ ICNC1 1 4 ICP

/ ICES1

XTAL

6

ICES1 1

ICES1 0 / 1

ICR1

ICP ICES1 1 / 1

ICR1 ICP

Res:

5,4

90 0

3

CTC1 / 0

CTC1 1 / 1 $0000

CTC1 / 1

PWM

2,1,0

CS12,CS11,CS10: 1 2 1 0

1 2 1 / 1 2.9

$2D $4D

$2C ($4C)

15

MSB

TCNT1H TCNT1L

14

13

8

TCNT1H

LSB

TCNT1L

5

4

3

2

1

0

R/W R/W R/W

R/W

R/W

R/W

--

12

11

10

--

7

6

:

R/W

R/W

:

R/W

R/W

R/W R/W R/W

R/W

R/W

R/W

: $00 00

16 16 / 1 . CPU

,, 8 (TEMP).

1.TCNT1 / 1

CPU TCNT1H , TEMP ,, CPU

TCNT1L , TEMP , 16

AVR

29

TCNT1 / 1 , TCNT1H 16

2 TCNT1 1

CPU TCNT1L TCNT1L CPU TCNTlH

TEMP CPU TCNT1L CPU TEMP

TCNT1L 16

1 PWM

1

$2B $4B

$2A ($4A)

15

MSB

14

13

12

11

10

R/W

R/W

R/W

R/W

R/W

$29 $49

$28 ($48)

OCR1AH OCR1AL

8

--OCR1AH

LSB

OCR1AL

7

6

5

4

3

2

1

0

R/W

R/W

R/W R/W R/W

R/W

R/W

R/W

:

:

R/W

R/W

: $00 00

15

MSB

14

R/W

OCR1BH OCR1BL

8

--OCR1BH

LSB

OCR1BL

7

6

5

4

3

2

1

0

R/W

R/W

R/W R/W R/W

R/W

R/W

R/W

:

:

R/W

R/W

: $00 00

13

12

11

10

R/W

R/W

R/W

R/W

R/W

R/W

16 1

1 1

OCR1A OCR1B 16 OCR1A/B

TEMP CPU , OCR1AH

OCR1BH TEMP CPU , OCR1AL OCR1BL

TEMP OCR1AH OCR1BH OCR1AH OCR1BH

16

AVR

$25 $45

$24 ($44)

15

MSB

14

R

R

$00 00

12

11

10

30

ICR1H ICR1L

LSB

1

R

7

:

:

:

13

8

ICR1H

ICR1L

0

R

R

16 ICP

ICES1) 1

ICR1

ICF1 1

ICR1 16 ICR1

TEMP CPU ICR1L CPU

ICR1H TEMP CPU ICR1H

CPU TMEP ICR1L

16

PWM 1

PWM 1 OCR1A

OCR1B 8 9 10 PD5 OC1A OC1B

PWM 1 $ 0000

TOP 2 10 0

OCR1A OCR1B 10 PD5 OC1A

OC1B

1 TCCR1A COM1A1 COM1A0 COM1B1 COM1B0

2 11

PWM 10 OCR1A OCR1B

1 TOP OCR1A OCR1B

2 25

PWM

AVR

31

OCR1A $ 0000 TOP OC1A OC1B COM1A1 COM1A0

COM1B1 COM1B0 2.12

PWM 1

TOVI 0000

2.12

PWM OCRIX

0000 TOP

1

TOV1

1

1

2.7.4

1MHz

16 2048

Vcc 5V

Vcc RC

WDR

8

2 WDR

MCU

WDR 90

2.26

$21 $41

:

7

R

WDTCR

6

R

4

3

2

1

0

-WDTOE WDE WDP2 WDP1 WDP0 WDTCR

R

R/W

R/W

R/W

R/W

R/W

AVR

32

: $00

7 5Res:

2 13

AVR

AVR E2PROM

2.8

33

0 E2PROM

2..5 4 ms Vcc

Vcc E2PROM E2PROM

E2PROM CPU

I

E2PROM

$1F $3F

$1E ($3E)

15

-EEAR7

7

:

R

EEAR

14

13

12

-EAR6

6

R

-EEAR5

5

R

-EEAR4

:

R/W

R/W

: $00 00

11

-EEAR3

4

R

R/W

R/W

8

--EEAR9 EEARH

EEAR2 EEAR1 EEAR0 EEARL

3

2

1

0

R

R

R/W

R/W

10

R/W

R/W

R/W

E2PROM

EEARH EEARL 512 E2PROM

511

E2PROM E2PROM 0

E2PROM

$1D $3D

:

:

7

MSB

R/W

$00

EEDR

6

R/W

R/W

3

R/W

R/W

2

R/W

1

0

LSB

EEDR

R/W

R/W

EEDR7~0 E2PROM

7~0

E2PROM EEDR E2PROM EEAR

E2PROM EEDR EEAR E2PROM

E2PROM

EECR

6

3

2

1

0

EEMWE EEWE EERE

EECR

R

R/W

R/W

R/W

-----$3C

:

R

R

R

R

: $00

7~3

Res:

90 0

EEMWE E2PROM

2

EEMWE EEWE EERPOM EEMWE 1 EEWE

E2PROM EEMWE 0 EEWE EEMWE

4 E2PROM EEWE

1

EEWE E2PROM

$1C

E2PROM EEWE E2PROM EEWE

E2PROM EEWE 1 EEMWE 1 E2PROM

(1

2

3

4

AVR

EERPOM

EEWE 0

34

E2PROM EEAR

E2PROM EEDR

EECR EEMWE 1

5 EEMWE 4 EEWE 1

EEWE

5 V 2.5 ms 2.7 V 4 ms

EEWE CPU

2

EERE E2PROM

0

E2PROM EERE E2PROM EEAR

EERE EEAR EEDR E2PROM

1 EERE EERE CPU

2 EEWE E2PROMI

O

AVR

35

9 AVR

2 9 1 SPI

SPI 90 90

2 27 90 SPI

1 3

2

3 5Mb/S

4 LSB MSB

5

6

AVR

36

AVR

37

7

6

5

4

3

2

1

0

SPIE SPE DORD MSTR CPOL CPHA SPR1 SPR0

SPCR

$0D $2D

:

R/W R/W R/W

R/W

R/W

R/W

R/W

R/W

: $00

AVR

38

7

6

SPIF WCOL

$0E $2E

:

R/W

R/W

: $00

5

--

-R

-R

-R

2

-R

1

-R

0

SPSR

R

7

6

5

4

3

2

1

0

MSB

LSB

SPDR

$0E $2E

:

R/W

R/W R/W R/W

R/W

R/W

R/W

R/W

: $00

AVR

39

AVR

40

AVR

41

$0C $2C

:

:

7

MSB

R/W

$00

6

R/W

5

R/W

4

R/W

3

R/W

2

R/W

1

LSB

R/W

0

UDR

R/W

7

6

5

4

3

RXC

TXC

UDR

FE

OR

-$0B $2B

:

R/W

R/W R/W R/W

R/W

: $00

2

-R

1

-R

0

USR

R

AVR

42

7

6

5

4

3

2

1

0

RXCIE TXCIE UDRIE RXEN TXEN CHR9 RXB8 TXB8 UCR

$0A $2A

:

R/W

R/W

R/W

R/W

R/W

R/W

R

W

: $00

AVR

43

AVR

44

AVR

45

AVR

46

AVR

47

AVR

48

AVR

49

AVR

50

AVR

51

AVR

52

AVR

53

AVR

54

AVR

55

AVR

56

AVR

57

AVR

58

AVR

59

AVR

60

AVR

61

AVR

62

AVR

63

AVR

64

AVR

65

AVR

66

AVR

67

AVR

68

Vous aimerez peut-être aussi

- 中菲规范地震动参数确定方法的对比分析 彭殿东Document5 pages中菲规范地震动参数确定方法的对比分析 彭殿东周晓光Pas encore d'évaluation

- Matlab SimulinkDocument363 pagesMatlab SimulinkSaint TyagiPas encore d'évaluation

- AVR ProgrammingDocument27 pagesAVR ProgrammingSaint TyagiPas encore d'évaluation

- AVR BookDocument4 pagesAVR BookSaint TyagiPas encore d'évaluation

- VHGLDocument95 pagesVHGLSaint TyagiPas encore d'évaluation

- ElectronicsDocument49 pagesElectronicsSaint TyagiPas encore d'évaluation

- Excel2019电子表格实例教程(微课版)Document33 pagesExcel2019电子表格实例教程(微课版)f22jian20t50Pas encore d'évaluation

- 指数函数与对数函数Document2 pages指数函数与对数函数Tan Ying ShuangPas encore d'évaluation

- 2 104地特須知 (三四等) 0908 PDFDocument93 pages2 104地特須知 (三四等) 0908 PDF何家銘Pas encore d'évaluation

- 2018级经济管理试验班本科生培养计划Document20 pages2018级经济管理试验班本科生培养计划George DavePas encore d'évaluation

- 13. 计算机网络实践Document22 pages13. 计算机网络实践hongPas encore d'évaluation

- S2700, S3700, S5700, S6700, S7700, S7900, S9700系列交换机 对接替换指导 (V200)Document668 pagesS2700, S3700, S5700, S6700, S7700, S7900, S9700系列交换机 对接替换指导 (V200)KeithPas encore d'évaluation