Académique Documents

Professionnel Documents

Culture Documents

V01I031119

Transféré par

IJARTETCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

V01I031119

Transféré par

IJARTETDroits d'auteur :

Formats disponibles

International Journal of Advanced Research Trends in Engineering and Technology (IJARTET)

Vol. 1, Issue 3, November 2014

Analysis And Implementation Of PI Controller

Fordc Link Single Phase PWM Voltage Source

Inverter

B.Kiruthiga1, S.Senthil Rani2, J.Rajeswari3

Assistant Professor, EEE Dept, Velammal College of Engineering and Technology, Madurai, India. 1

Assistant Professor, EEE Dept, Velammal College of Engineering and Technology, Madurai, India.2

Assistant Professor, EEE Dept, Velammal College of Engineering and Technology, Madurai, India.3

Abstract: The Pulse Width Modulation (PWM) DC-to-AC inverter has been widely used in many applications due to its

circuit simplicity and rugged control scheme. In the inverters, high-frequency (HF) operation reduces the filter size, which

ic claimed to be the biggest advantage. The major limitation in increasing the switching frequency is the switching losses.

Hence, zero voltage switching is used to reduce the switching losses. This work proposes a novel controller for enhancing

the performance of the inverter. A Zero Voltage Switching (ZVS) DC link single-phase Pulse Width Modulated Voltage

Source Inverter (VSI) under open loop and closed loop condition is simulated and presented. Design equations are also

discussed and ZVS is achieved for both forward power flow, without increasing the voltage stress on the inverter devices.

For the performance evaluation of the proposed converter in closed loop, PI controller is incorporated. The parameters such

as output voltage, voltage stress, current through switches and switching losses are obtained and a detailed comparative

analysis is made between open loop, closed loop using PI controller.

Keywords: Zero voltage switching, Inverter, Dc link, PI controller, Modulation strategy, Soft switching

I. INTRODUCTION

Switching mode power supplies are widely used in

many applications such as uninterruptible power systems,

motor drives, induction heating, etc., High-frequency (HF)

operation reduces the filter size. The major limitation to

increase the switching frequency is the switching losses.

Hence, soft switching techniques are used to reduce the

switching losses. In the proposed ZVS dc link technique, the

switch voltage is clamped to the dc link voltage and PWM

schemes can be used to control the inverter output voltage.

Soft switching techniques for power inverters have been

proposed to improve circuit efficiency, increase power

density and reduce voltage and current stresses on the

switching devices. Hence, soft switching techniques are used

to reduce the switching losses in [1]-[8]. The resonant dc

link inverter proposed in [1] has been used to achieve zerovoltage switching (ZVS), but the switch voltage stress is

much higher than the dc-link voltage. The inverter proposed

in [2] reduces the voltage stress. In [3][6] many techniques

were proposed to clamp the voltage stress on the switches to

dc-link voltage. But they suffer from one or another

limitation, like increased complexity due to more number of

auxiliary switches, addition of transformer or coupled

inductor, complex switching algorithms, etc. Soft switching

using auxiliary circuits at the load end has also been

proposed in [7][8].In [9] used the active circuit in [11]to

obtain ZVSof the active switch in a fly back converter. Here

the leakage inductance of the transformer is allowed to

resonate to obtain soft switching.

But the ZVS is load dependent. The energy stored

in the leakage inductance must be sufficient enough to

discharge the snubber capacitor of the switch. In [10], a

transformer is used in the auxiliary circuit to transfer the

energy to the output. It reduces the conduction losses but the

switching stress and the parasitic oscillations still exists. In

[12] the stress across the switch has been reduced. It uses

coupled inductance instead of using auxiliary switch. A

bidirectional switch [13] is used in the auxiliary circuit to

achieve soft switching.

The energy supplied to the split capacitors is not

equal. Hence, the voltage levels of the split capacitors differ

hence cant achieve soft switching. A rugged soft

commutating inverter has been proposed in [13].The inverter

could operate efficiently, without voltage. In [12] a new

variant of inverter has been proposed for AC drives

applications. The presence of resonant capacitor and the

clamp diodes substantially reduces the rectifier diode voltage

overshoot. In [6] the ZVS using auxiliary circuit was used to

obtain soft switching in full bridge dc-dc inverters. And the

output voltage has also been controlled to a reasonable

extent. The voltage stress has been reduced only to the 15%

by using transformer and coupled inductor. But in the

proposed work, without the use of transformer and complex

coupled inductors, the voltage stress has been reduced to

48

International Journal of Advanced Research Trends in Engineering and Technology (IJARTET)

Vol. 1, Issue 3, November 2014

20% of the dc link voltage. It has been achieved using

simple auxiliary switch circuit. Also, the output voltage has

also been controlled to a reasonable extent. And, in order to

enhance the performance of the inverter for suitable

applications and also for increasing versatility, a closed loop

controller has been proposed. Closed loop system results has

been obtained using PI controller.

II. BLOCK DIAGRAM OF PROPOSED INVERTER

The block diagram of the proposed inverter in

closed loop system using controller is shown in Fig.1. There

is a Dc link which acts as the interlink between the Dc input

and H-bridge inverter. Whenever the input is given as Dc it

converts it to Ac as output by means of H-bridge inverter.

DC-Link capacitors must be designed for high DC voltages

which occur permanently and which may be superimposed

with high frequency ripple voltages [2].

Fig.2.Circuit diagram of proposed inverter

Therefore for forward power flow Si/Di represents

S1/D1 or S3/D3 during positive half-cycle. Similarly Sa/Da

represents S4/D4 or S2/D2 during negative half cycle. The

capacitor Cs is the snubber capacitance which can be seen in

the auxiliary circuit.

The circuit diagram of the proposed DC link single

phase PWM voltage source inverter (VSI) is shown in

Fig.2.The Proposed inverter consists of a dc link Sdc switch,

its snubber capacitor Cdc, resonant inductor Lr, resonant

capacitor Cr, and the H-bridge inverter consisting

Fig.3.Detailed block diagram of proposed inverter

CONTROLLE

R

Fig.1.Block diagram of proposed closed loop inverter

of switches S1,S2,,S3,S4 along with their anti-parallel diodes

and snubber capacitors C1-C4[1]-[3]. To simplify the

analysis, all the components (semiconductor switches,

diodes, inductors and capacitors) are assumed ideal [2].

Lagging power factor load is assumed. The load inductance

is large enough that the load current is assumed constant in a

HF switching cycle.

The H-bridge formed by the switches S1,S2,S3, S4

performs forward power transfer where S1-S2 transfers the

power during the positive half-cycle of output and S3-S4

transfers the power during the negative half-cycle of output.

At which switches S1,S3 operates at high frequency (i.e., 50

kHz) and switches S2,S4 operates at low frequency (i.e., 50

Hz). The detailed block diagram of the proposed inverter is

shown in Fig.3.

III.OPERATING PRINCIPLE OF PROPOSED INVERTER

A. Circuit Operation

To illustrate the soft switching characteristics of

the proposed technique, the operation can be divided in to

seven operating intervals. The operating waveforms in

different intervals of operation are shown in Fig.4. At the

start of the switching period, it is assumed that the

equivalent switch Si is off and the switch Sdc is on. The load

current is freewheeling through the diode Da. Let the voltage

across the resonant capacitor Cr be Va. The resonant

capacitor is assumed large enough so that the voltage across

it is assumed approximately constant, however changes

slightly. The inductor current iLr(iLr(0- )= -Ia ) is flowing

through the resonant capacitor Cr and switch Sdc. Initially the

switch Sdc is in ON state. Whenever the supply is given to

the circuit the voltage across Vlink and Vdc starts increasing.

Then a breach occurs, at a particular instant the voltage starts

dropping and reaches zero, at that period the switches Sdc

and S1 starts conducting simultaneously. Whenever the

voltage across Vlink comes to zero the switch Sdc will starts

conduct and whenever the voltage across Vdc comes to zero

the switch S1 will starts conducts which has been stated

below in the waveforms. Related inductor and capacitor

current and voltages have also been shown in Fig.4 and the

49

International Journal of Advanced Research Trends in Engineering and Technology (IJARTET)

Vol. 1, Issue 3, November 2014

equivalent circuits with different operating intervals are

given in Fig.5 (a)-(g). The snubber capacitor, Cs starts

resonating with the resonant inductor Lr which has been

shown in the figure5.a. When the dc bus voltage

(VLink)reaches zero at t1 the diode Dastarts conducting. The

current through Lr(iLr) linearly rarnps up and reaches Io at

ta. The switch Sa and Si are both gated within this interval.

The switch Si turns on with ZVS. The inductor current rises

linearly until it reaches the output current Io.

circuit diagram depicting this interval is shown in Figure5.e.

The dc link switch turns on with zero voltage which is

shown in figure5.g. The resonant inductor current i Lr ramps

down and reaches zero at t7 and goes negative, while the dc

link switch current increases.

Fig.5.Equivalent circuits during different intervals of the proposed

soft-Switched VSI during forward power flow

Fig. 4.Operating waveforms of proposed inverter

The diode ( Da )current ramps down and reach zero.

Then the reverse recovery current of the diode Da starts

flowing. At the end of this interval the diode stops

conducting and enters the blocking mode [4] is shown in

figure5.b. The current through Lr continues to increase due

to resonance between Lr and Cs. The capacitor Cs is charged

until the resonance brings its voltage Vlink toVdc and the

voltage Vm reaches zero is shown in figure5 .c. The blocking

voltage of the diode Da increases and reaches Vdc[5]. The

circuit diagram depicting this interval of operation is shown

in figure5.d. The dc link switch voltage Vm tries to go

negative but is clamped by the anti-parallel body diode Ddc

of the switch, which starts conducting. The switch Sdc should

be gated within this interval at time t5(t4< t5 <t6 ) to obtain

zero-voltage turn-on. The resonant inductor current iLr

reaches the output load current value (I0) at t6[11]. The

B. Modulation Strategy

With sine triangle modulation the switching cycle

is not synchronized to the carrier at turn-on or at turnoff, i.e.,

both rising edge and the falling edge are modulated [11].The

proposed inverter requires a PWM scheme in which the turnon of each cycle is synchronized to the carrier (trailing edge

modulation). Therefore, the triangular carrier is replaced by

a ramp carrier, (Fig.6).

Fig.6. Sine-triangle modulation

With the ramp carrier, the turn-on edge of the

switching signal is synchronized to the falling edge of the

carrier. The harmonic spectrum of the sine-ramp modulation

looks almost same as that of the conventional sine-triangle

modulation scheme. During forward power transfer, the

50

International Journal of Advanced Research Trends in Engineering and Technology (IJARTET)

Vol. 1, Issue 3, November 2014

gating signals are obtained from rising ramp-sine modulator

(Fig.6) and during reverse power flow; the gating signals are

obtained from falling ramp-sine modulator (Fig.7). This can

be realized by sensing the inverter bridge output current and

obtaining the reverse power-flow regions. Therefore, the

triangular carrier is replaced by a ramp carrier (With the

ramp carrier, the turn-on edge of the switching signal is

synchronized to the falling edge of the carrier. The harmonic

spectrum of the sine-ramp modulation looks almost same as

that of the conventional sine-triangle modulation scheme.

Fig.7. Sine-ramp modulation

C. Conventional Unipolar Strategy

The modes of operation in a switching cycle are

given in Table.I. The transition from Mode A to Mode B and

Mode D to Mode C is with natural ZVS [3], [5]. The

transition from Mode B to Mode A and Mode C to Mode D

is hard switched. Hence, soft switching mechanisms are

required for these transitions. Hence, auxiliary assisted soft

switching technique should be applied at Ts for forward

power flow and at DT for reverse power flow. This means

that the control should detect the point of transfer from

Mode C to Mode D so that the auxiliary circuit can be

initiated to obtain soft switching. The modes of operation

varies depends upon the duration ON period of the switches.

The auxiliary switch provides vital role in achieving Zero

voltage switching. Since it has single switch instead of

transformer and coupled inductor it makes the operation

simple. Ts and DT are the parameters which represent the

duration of power transfer in forward power flow and

reverse power flow respectively which has been shown in

Table. I.

TABLE .I. CONVENTIONAL UNIPOLAR SWITCHING SCHEME

Forward Power Flow

0<t<DTs

DTs<t<Ts

MODE A

MODE B

Power transfer

S1-S2 or S3-S4

conduct

Power free wheeling

S2-D4 or S4-D2

conduct

Hence, soft switching mechanisms are required for

these transitions. The control should detect the point of

transfer from Mode C to Mode D so that the auxiliary circuit

can be initiated to obtain soft switching. Moreover, the

auxiliary circuit should reset and get ready as it can be called

at any instant between 0 to Ts (duty cycle D will vary along

the low-frequency output voltage cycle).The PWM inverter

should operate with minimum modulation index so that the

auxiliary circuit can be reset.

D. Modified Unipolar Switching Strategy

In the modified strategy proposed here, the

forward power flow is similar to that of the conventional

method. During reverse power flow, the switching cycle

starts with power freewheeling and ends with power transfer

(different from the conventional control). Table.II presents

the modes of operation in a switching cycle. (At the end of

the switching cycle for transition from Mode B to Mode A

and Mode C to Mode D). The dc link soft switching

auxiliary circuits has been activated and the transition is

made soft. Hence, the auxiliary circuit will be activated at

the end of each switching cycle to obtain ZVS both during

forward power flow and reverse power flow [13]. Therefore,

the auxiliary circuit has been operated in entire switching

period and it must be called for soft transition before getting

reseted. During forward power transfer; the gating signals

are obtained from rising ramp-sine modulator and during

reverse power flow; the gating signals are obtained from

falling ramp-sine modulator.

TABLE.II. MODIFIED UNIPOLAR SWITCHING SCHEME

Forward Power Flow

0<t<DTs

DTs<t<Ts

MODE A

MODE B

Power transfer

Power free wheeling

S1-S2 or S3-S4

conduct

S2-D4 or S4D2conduct

But this paper deals only with the forward power

flow, at which the performance has been improved and their

performance parameters were analyzed. It consists of four

inverter switches at which upper two switches were operated

in higher frequency and lower two switches were operated in

lower frequency [11]. They are synchronized by means of

multiplexing the both frequencies which produces minimum

loss. During forward power transfer, the gating signals are

obtained from rising ramp-sine modulator which produces

minimum loss. This can be realized by sensing the inverter

bridge output current and output voltage.

51

International Journal of Advanced Research Trends in Engineering and Technology (IJARTET)

Vol. 1, Issue 3, November 2014

III. DESIGN SPECIFICATION

A dc-to-ac bridge inverter with the following

specifications has been designed to illustrate the design

procedure. Vdc= 220Vdc; output power, P 0= 300 VA; output

voltage, V0 =120 Vrms; output frequency, f0= 50 Hz;

switching frequency, fs= 50 kHz. The top switches in the full

bridge inverter operate at high frequency, while the bottom

switches operate at low output frequency.

Hence, MOSFETs are used for bottom switches and

for top switches respectively. Moreover, during the forward

power freewheeling, the bottom switch diodes are used.

MOSFETs with fast anti-parallel diodes are available.

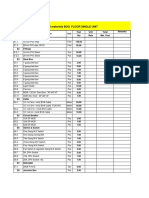

TABLE.III. RESULTS FOR OPEN LOOP SYSTEM

Input voltage

220 V

Input current

2.5 A

Input power

550 W

Output voltage

138 V

Output current

2.45 A

Output power

345 W

Total loss

205 W

Voltage stress

also called a non-feedback controller, is a type of controller

that computes its input into a system using only the current

state and its model of the system. A characteristic of the

open-loop controller is that it does not use feedback to

determine if its output has achieved the desired goal of the

input. This means that the system does not observe the

output of the processes that it is controlling. Consequently, a

true open-loop system can not engage in machine learning

and also cannot correct any errors that it could make. It also

may not compensate for disturbances in the system. A dc-toac bridge inverter with 220V dc input was designed as per

design procedure illustrated. The output frequency, is fo=50

Hz and switching frequency, fs=50 kHz. The top switches

(S1, S3), in the full bridge inverter operate at high frequency,

while the bottom switches (S4, S2) operates at low output

frequency. Lr is selected to be 32 mH to limit the di/ dt of the

anti-parallel diodes and recovery losses is negligible.

Resonant frequency is chosen as fr=50 kHz and resonant

capacitor as Cr=5 H. The output voltage can be varied from

120v to 140v for the required application and hence the

output voltage obtained for open loop system is 138v.

B. Closed Loop System

5V

Fast diodes reduce the circulating energy in the

resonant inductor. During R-load the specifications are

considered to be Resonant inductor, Lr= 32H; Resonant

capacitor, Cr= 5F;Snubber capacitor, Cs= 0.333nf; Supply

voltage Vdc= 220V; Switching frequency, fs = 50HZ; R

load= 60ohm. These specifications can applicable for both R

and RL loads respectively.

PI controller have two components: the first

component, proportional control which generates an output

signal proportional to error and second component is integral

control, takes into account the error history, and generates

output proportional to the integral of error. Proportional

controller (Kp) will have the effect of reducing the rise time

but, never eliminate the steady-state error [10]. An integral

control (Ki) will have the effect of eliminating the steadystate error, but it may make the transient response worse [1].

Effects of each controller parameters kp, and Ki on a closedloop system are summarized in Table.IV shown below. The

PI values are obtained by tuning general inverter transfer

function by using MATLAB tuner block.

IV.RESULTS AND DISCUSSION

A. Open Loop System

The proposed inverter is simulated in MATLAB

environment using SIMULINK. An open-loop controller,

Fig. 8. Simulation circuit with PI controller

52

International Journal of Advanced Research Trends in Engineering and Technology (IJARTET)

Vol. 1, Issue 3, November 2014

TABLE.IV. TUNED PI VALUES

PARAMETERS

VALUES

Kp

1.2

Ki

0.08

The main simulation circuit of the proposed

inverter with PI controller is shown in Fig.8. The following

Fig.9 Shows the gate pulses simulated gate pulses for the

switchesSdc, S1, S2, S3, andS4. The switch Sdcis operated at

the frequency of 50 kHz and the switches S2, S4 are operated

at the frequency of 50HZ. And the switches S1, S3 are

operated at the frequency by adding the frequencies of 50HZ

and 50KHZ respectively.Fig.10 shows the output waveform

obtained for PI controller.

Fig. 10.Simulated output waveforms for forward power flow

V.CONCLUSION

A DC link zero voltage switching single phase

Voltage Source Inverter is proposed. The system

performance is optimized using the unipolar, sine -ramp

modulation scheme. The soft switching for all power factor

conditions is achieved. Only one extra switch is required in

the dc link to obtain ZVS. Simulation is performed for the

proposed inverter for the open loop condition and closed

loop condition with PI controller and comparative study is

presented. The performance is very much improved in the

closed loop system than the open loop system.

REFERENCES

Fig. 9. Simulated output waveforms

[1]. Agelidis.V. G., Ziogas.P.D., and Joos.G.,An optimum

modulation strategy for a

novel notch commutated 3-phase

PWM inverter,IEEE Transactions on industrial applications,

vol. 30, no.1, pp. 5261, Jan. 1994.

[2]. Anui. G., Shireen. W., Enjeti. P.N., "Improved active power

factor Correction circuit using a zero voltage switching Boost

converter"IEEE Transactions on Power Electronics, Vol. 13, No.

2, March 1998, pp. 308- 314.

[3]. Bazinet. J., Connor. J., "Analysis and Design of a Zero Voltage

Transition power factor correction circuit," IEEE transactions on

53

International Journal of Advanced Research Trends in Engineering and Technology (IJARTET)

Vol. 1, Issue 3, November 2014

Applied Power Electronics Conference., 1994, pp.591 600.(Unitrode)

[4]. Canten. B., "Design Techniques for transformer active reset

circuits at high frequencies andpower levels," High Frequency

Power Conversion conference, 1990, pp.235-246.

[5]. Chan. C. C., Chau. K. T, Chan. D. T. W., Yao. J., Lai. J. S., and

Li. Y.,Switching characteristics and efficiency improvement

with auxiliary resonant snubber based soft switching inverters,

Proceedings. IEEE Power electronics specialist conference ,pp.

429435, 1998.

[6]. Cherti. A., Al-haddad. K., Dessaint. L. A., Meynard.T.Aand

Mukhedar. D.," A rugged soft commutated PWM inverter for

ACdrives,"

IEEE

Power

Electronics

Specialists

recommended.,1990, pp. 656-662.

[7]. Da Silva. E. R. C., Cavalcanti. M. C., and Jacobina. C. B.,

Comparative study of

pulsed DC-link voltage converters,

IEEE Transactions on Power Electronics., vol. 18, no. 4,

pp.10281033, Jul. 2003.

[8]. Divan. D.M., The resonant dc link converter A new concept

in static power conversion, IEEE Transactions on industrial

applications., vol. 25, no. 2, pp.317325,Mar./Apr. 1989.

[9]. Dosreis.A.,Vieira.J., Jr., Defreitas.L, and Farias.V, A full

bridge three level single

phase inverter with stressless

commutation

cell

and

special

PWM

technique,

Proceedings.IEEE Applied power electronics conference, pp.

551557, 1998.

[10]. Hua. G., Lee. F.C., 'Novel Zero-voltage transition

PWMconverters,"IEEE

Power

Electronics

Specialists

conference.,1992pp.55-61.

[11]. Jafar.J.J.andFernandes.B.G., A new quasi-resonant dc-link

PWM inverter using

single switch for soft switching, IEEE

Transactions on Power Electronics., vol. 17, no. 6, pp. 1010

1016, Nov. 2002.

[12]. Rui li, zhiyuan ma, and dehongxu, A zvs grid-connected threephase inverter., IEEE transactions on power electronics, vol.

27, no. 8, august 2012.

[13]. Il-oun lee, and gun-woo moon., phase-shifted pwm converter

with a wide zvs range and reduced circulating current.,IEEE

transactions on power electronics, vol. 28, no. 2, february 2013.

54

Vous aimerez peut-être aussi

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Évaluation : 2.5 sur 5 étoiles2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Pas encore d'évaluation

- High Power Factor Soft SwitchedDocument7 pagesHigh Power Factor Soft SwitchedMohan KrishnaPas encore d'évaluation

- Two-Stage H-Bridge Transformer Coupled DC-DC Converter With Zero Voltage SwitchingDocument8 pagesTwo-Stage H-Bridge Transformer Coupled DC-DC Converter With Zero Voltage SwitchingRakeshconclavePas encore d'évaluation

- J'14 - Analysis, Design and Performance of A Soft-Switching Single-Phase InverterDocument12 pagesJ'14 - Analysis, Design and Performance of A Soft-Switching Single-Phase Inverter閒雲野鶴Pas encore d'évaluation

- Implementation of ZVS-ZCS Combined Snubber NetworkDocument6 pagesImplementation of ZVS-ZCS Combined Snubber NetworkYuiophjklPas encore d'évaluation

- A Novel Analysis of ZeroDocument9 pagesA Novel Analysis of ZerodineshpeterPas encore d'évaluation

- A New Soft-Switching Technique For Buck, BoostDocument8 pagesA New Soft-Switching Technique For Buck, BoostVisu TamilPas encore d'évaluation

- A Very High Frequency DC-DC Converter Based On A Class Pfi Resonant InverterDocument10 pagesA Very High Frequency DC-DC Converter Based On A Class Pfi Resonant InvertererdemsecenPas encore d'évaluation

- Wineyard - in Abstract Mtech Electronics BP 14PE3 PDFDocument5 pagesWineyard - in Abstract Mtech Electronics BP 14PE3 PDFbhulakshmideviPas encore d'évaluation

- Family of Soft-Switching PWMDocument7 pagesFamily of Soft-Switching PWMMohan KrishnaPas encore d'évaluation

- ZVS Boost Converter With A Flyback Snubber CircuitDocument8 pagesZVS Boost Converter With A Flyback Snubber Circuitmishranamit2211Pas encore d'évaluation

- ZVSDocument28 pagesZVS12BACAUPas encore d'évaluation

- Implementation of Single Stage Three Level Power Factor Correction AC-DC Converter With Phase Shift ModulationDocument6 pagesImplementation of Single Stage Three Level Power Factor Correction AC-DC Converter With Phase Shift ModulationseventhsensegroupPas encore d'évaluation

- Transformer Based Resonant DC Inverter For Brushless DC Motor Drive SystemDocument7 pagesTransformer Based Resonant DC Inverter For Brushless DC Motor Drive SystemStudents Xerox ChidambaramPas encore d'évaluation

- A Comparison of Voltage-Mode Soft-Switching Methods For PWM ConvertersDocument10 pagesA Comparison of Voltage-Mode Soft-Switching Methods For PWM ConvertersAshish BhardwajPas encore d'évaluation

- DC-DC Converter: Four Switches V V 2, Capacitive Turn-Off Snubbing, ZV Turn-OnDocument10 pagesDC-DC Converter: Four Switches V V 2, Capacitive Turn-Off Snubbing, ZV Turn-OnRomitan AlexandraPas encore d'évaluation

- A Novel Soft-Switching Single-Phase AC-DC-AC Converter Using New ZVS-PWM StrategyDocument2 pagesA Novel Soft-Switching Single-Phase AC-DC-AC Converter Using New ZVS-PWM Strategyskumar_61719Pas encore d'évaluation

- Non Isolated Bidirectional DC DC ConverterDocument6 pagesNon Isolated Bidirectional DC DC ConverterAnuja VarghesePas encore d'évaluation

- Digital Simulation of ZVS DC To DC Converter Using Simulink: AbstractDocument13 pagesDigital Simulation of ZVS DC To DC Converter Using Simulink: AbstractAshok KumarPas encore d'évaluation

- DC-DC Boost Converter Lab ProjectDocument15 pagesDC-DC Boost Converter Lab ProjectAyush MittalPas encore d'évaluation

- High-speed voltage follower designDocument2 pagesHigh-speed voltage follower designfatyfroisPas encore d'évaluation

- Switched Inductor Z-Source Matrix Converter Operation and AnalysisDocument9 pagesSwitched Inductor Z-Source Matrix Converter Operation and AnalysisA'Platinum EngPas encore d'évaluation

- Resonant DC-DC ConvertingDocument21 pagesResonant DC-DC ConvertingSanthoshPas encore d'évaluation

- Design and Application For PV Generation System Using A Soft-Switching Boost Converter With SARCDocument13 pagesDesign and Application For PV Generation System Using A Soft-Switching Boost Converter With SARCIJERDPas encore d'évaluation

- Analysis and Construction of Push Pull Converter - Noor Rulmuna Bt. Mohd Sarmin - TK7872.C8.N66 2006Document27 pagesAnalysis and Construction of Push Pull Converter - Noor Rulmuna Bt. Mohd Sarmin - TK7872.C8.N66 2006Rizwan FaizPas encore d'évaluation

- Generation of Energy Usig MagnetsDocument26 pagesGeneration of Energy Usig MagnetsSridhar PatilPas encore d'évaluation

- Research Article: On The Development of High Power DC-DC Step-Down Converter With Energy Recovery SnubberDocument10 pagesResearch Article: On The Development of High Power DC-DC Step-Down Converter With Energy Recovery SnubberefremofePas encore d'évaluation

- Design and Implementation of Multiple Output Switch Mode Power SupplyDocument6 pagesDesign and Implementation of Multiple Output Switch Mode Power SupplyseventhsensegroupPas encore d'évaluation

- Digital Simulation of ZVS DC To DC Converter Using Simulink: Research Scholar Sathyabama University Chennai, IndiaDocument13 pagesDigital Simulation of ZVS DC To DC Converter Using Simulink: Research Scholar Sathyabama University Chennai, Indiaaamirhussain_001Pas encore d'évaluation

- Analysis, Design and Implementation of Zero-Current-Switching Resonant Converter DC-DC Buck ConverterDocument12 pagesAnalysis, Design and Implementation of Zero-Current-Switching Resonant Converter DC-DC Buck Converterdaber_huny20Pas encore d'évaluation

- 9.eee Ijeee Two Phase Interleaved DC SumalathaDocument16 pages9.eee Ijeee Two Phase Interleaved DC Sumalathaiaset123Pas encore d'évaluation

- Step Down PSIMDocument6 pagesStep Down PSIMAnonymous W44hzJ9roPas encore d'évaluation

- Resonant DC Link InvertersDocument6 pagesResonant DC Link InvertersSanchit AgarwalPas encore d'évaluation

- Zero Voltage Switching Resonant Power Devices by Bill AndrecakDocument28 pagesZero Voltage Switching Resonant Power Devices by Bill AndrecakRekhamtrPas encore d'évaluation

- PWM Rectifier Design Lab ReportDocument12 pagesPWM Rectifier Design Lab ReportSarika ChauhanPas encore d'évaluation

- 6high Power Full-Bridge DC-DC Converter Using A Center-Tapped Transformer and A Full-Wave Type Rectifier PDFDocument12 pages6high Power Full-Bridge DC-DC Converter Using A Center-Tapped Transformer and A Full-Wave Type Rectifier PDFmajidPas encore d'évaluation

- DC-DC Converters Lab ManualDocument32 pagesDC-DC Converters Lab ManualShah SahadPas encore d'évaluation

- Modified Space Vector Pulse Width Modulation For Modified Z-Source InverterDocument4 pagesModified Space Vector Pulse Width Modulation For Modified Z-Source InverterAvinash GpPas encore d'évaluation

- Simulation and Prototype Implementation of Phase Shift Full Bridge DC DC ConverterDocument4 pagesSimulation and Prototype Implementation of Phase Shift Full Bridge DC DC ConverterjimmyPas encore d'évaluation

- Wide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial ApplicationsDocument14 pagesWide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial Applicationsstrngr06Pas encore d'évaluation

- Zero-Voltage Switching Technique in DC/DC Converters: Abstruct-ADocument12 pagesZero-Voltage Switching Technique in DC/DC Converters: Abstruct-ARushikeshKatkarPas encore d'évaluation

- A Seamless Mode Transfer Maximum Power Point Tracking Controller For Thermoelectric Generator ApplicationsDocument10 pagesA Seamless Mode Transfer Maximum Power Point Tracking Controller For Thermoelectric Generator Applicationssumiths32Pas encore d'évaluation

- 1.1 Introduction To Buck ConverterDocument44 pages1.1 Introduction To Buck Converterapi-19810277Pas encore d'évaluation

- Design and Implementation of ZCS BUCK CONVERTERDocument51 pagesDesign and Implementation of ZCS BUCK CONVERTERAriful Haque100% (1)

- High-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniqueDocument9 pagesHigh-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniquekerblaPas encore d'évaluation

- Tugas 6 Kendali Mesin Listrik Industri - Aulia Silfani - 20130072Document8 pagesTugas 6 Kendali Mesin Listrik Industri - Aulia Silfani - 20130072Aulia SilfaniPas encore d'évaluation

- Ijeet: International Journal of Electrical Engineering & Technology (Ijeet)Document13 pagesIjeet: International Journal of Electrical Engineering & Technology (Ijeet)IAEME PublicationPas encore d'évaluation

- Asymmetrical Full-Bridge ConverterDocument9 pagesAsymmetrical Full-Bridge ConverterAthiesh KumarPas encore d'évaluation

- A Simple Structure of Zero-Voltage Switching Zero Current Switching Buck ConverterDocument9 pagesA Simple Structure of Zero-Voltage Switching Zero Current Switching Buck Convertersang young soPas encore d'évaluation

- Analysis and Comparison of DC-DC Boost Converters With High Voltage Conversion RatioDocument10 pagesAnalysis and Comparison of DC-DC Boost Converters With High Voltage Conversion RatioKrishnaveni Subramani SPas encore d'évaluation

- Switched Quasi Z Source Inverters With Extended Boost CapabilityDocument13 pagesSwitched Quasi Z Source Inverters With Extended Boost CapabilityAnoop MathewPas encore d'évaluation

- A Novel Aeronautical Static Inverter With High Frequency Pulse DC Link PDFDocument8 pagesA Novel Aeronautical Static Inverter With High Frequency Pulse DC Link PDFqiwatingPas encore d'évaluation

- EI5007W2Document17 pagesEI5007W2PyiAungPas encore d'évaluation

- مناقشة اولية1Document17 pagesمناقشة اولية1ahmedPas encore d'évaluation

- Analysis and Design of Common-Diode Tapped-Inductor PWM Buck Converter in CCMDocument7 pagesAnalysis and Design of Common-Diode Tapped-Inductor PWM Buck Converter in CCMEfa KhairiPas encore d'évaluation

- Design of Transformer-Less DC To AC Converter Using PWM TechniqueDocument6 pagesDesign of Transformer-Less DC To AC Converter Using PWM TechniqueHariesh WaranPas encore d'évaluation

- Power Electronics Applied to Industrial Systems and Transports, Volume 3: Switching Power SuppliesD'EverandPower Electronics Applied to Industrial Systems and Transports, Volume 3: Switching Power SuppliesPas encore d'évaluation

- Optimized Design and Manufacturing of WasteDocument5 pagesOptimized Design and Manufacturing of WasteIJARTETPas encore d'évaluation

- Wireless Notice Board With Wide RangeDocument5 pagesWireless Notice Board With Wide RangeIJARTETPas encore d'évaluation

- Tech Vivasayi Mobile ApplicationDocument3 pagesTech Vivasayi Mobile ApplicationIJARTETPas encore d'évaluation

- Smart Water Management System Using IoTDocument4 pagesSmart Water Management System Using IoTIJARTETPas encore d'évaluation

- Smart Farm Management System For PrecisionDocument5 pagesSmart Farm Management System For PrecisionIJARTETPas encore d'évaluation

- Object Detection and Alerting System inDocument4 pagesObject Detection and Alerting System inIJARTETPas encore d'évaluation

- Privacy Preservation of Fraud DocumentDocument4 pagesPrivacy Preservation of Fraud DocumentIJARTETPas encore d'évaluation

- Real Time Dynamic Measurements andDocument6 pagesReal Time Dynamic Measurements andIJARTETPas encore d'évaluation

- Ready To Travel ApplicationsDocument4 pagesReady To Travel ApplicationsIJARTETPas encore d'évaluation

- Behaviour of Concrete by Using DifferentDocument3 pagesBehaviour of Concrete by Using DifferentIJARTETPas encore d'évaluation

- Non Invasive Blood Glucose Monitoring ForDocument4 pagesNon Invasive Blood Glucose Monitoring ForIJARTETPas encore d'évaluation

- Makeover Features Base Human IdentificationDocument7 pagesMakeover Features Base Human IdentificationIJARTETPas encore d'évaluation

- Hygienic and Quantity Based WaterDocument10 pagesHygienic and Quantity Based WaterIJARTETPas encore d'évaluation

- Experimental Investigation On Concrete WithDocument18 pagesExperimental Investigation On Concrete WithIJARTETPas encore d'évaluation

- Complaint Box Mobile ApplicationDocument4 pagesComplaint Box Mobile ApplicationIJARTETPas encore d'évaluation

- Exam Seating ArrangementDocument3 pagesExam Seating ArrangementIJARTETPas encore d'évaluation

- Comparative Harmonics Analysis of ThreeDocument8 pagesComparative Harmonics Analysis of ThreeIJARTETPas encore d'évaluation

- Smart Door Using Raspberry PiDocument4 pagesSmart Door Using Raspberry PiIJARTETPas encore d'évaluation

- Application of Computer Vision in HumanDocument6 pagesApplication of Computer Vision in HumanIJARTETPas encore d'évaluation

- A High-Availability Algorithm For HypercubeDocument8 pagesA High-Availability Algorithm For HypercubeIJARTETPas encore d'évaluation

- A Non Threshold Based Cluster Head RotationDocument7 pagesA Non Threshold Based Cluster Head RotationIJARTETPas encore d'évaluation

- A Novel Artificial Neural Network and 2dPCABasedDocument9 pagesA Novel Artificial Neural Network and 2dPCABasedIJARTETPas encore d'évaluation

- Review On Field Testing of Protective RelaysDocument4 pagesReview On Field Testing of Protective RelaysIJARTETPas encore d'évaluation

- Wireless Cardiac Patient Monitoring SystemDocument6 pagesWireless Cardiac Patient Monitoring SystemIJARTETPas encore d'évaluation

- Power Transformer Explained PracticallyDocument4 pagesPower Transformer Explained PracticallyIJARTETPas encore d'évaluation

- Insect Detection Using Image Processing and IoTDocument4 pagesInsect Detection Using Image Processing and IoTIJARTETPas encore d'évaluation

- Study of Hypotenuse Slope of Chandrayaan-2 While Landing On The Moon SurfaceDocument3 pagesStudy of Hypotenuse Slope of Chandrayaan-2 While Landing On The Moon SurfaceIJARTETPas encore d'évaluation

- Fire Detection and Alert System Using Convolutional Neural NetworkDocument6 pagesFire Detection and Alert System Using Convolutional Neural NetworkIJARTETPas encore d'évaluation

- Review On Recycled Aluminium Dross and It's Utility in Hot Weather ConcretingDocument3 pagesReview On Recycled Aluminium Dross and It's Utility in Hot Weather ConcretingIJARTETPas encore d'évaluation

- Face Detection and Recognition Using Eigenvector Approach From Live StreamingDocument5 pagesFace Detection and Recognition Using Eigenvector Approach From Live StreamingIJARTETPas encore d'évaluation

- NCP 1014Document24 pagesNCP 1014rodricaldasPas encore d'évaluation

- Planning Dirty FrameworkDocument62 pagesPlanning Dirty FrameworkHoàng Hoa Dương100% (1)

- CM Group Marketing To Gen Z ReportDocument20 pagesCM Group Marketing To Gen Z Reportroni21Pas encore d'évaluation

- Efficacy of Platelet-Rich Fibrin On Socket Healing After Mandibular Third Molar ExtractionsDocument10 pagesEfficacy of Platelet-Rich Fibrin On Socket Healing After Mandibular Third Molar Extractionsxiaoxin zhangPas encore d'évaluation

- INJSO Answer Key & SolutionDocument5 pagesINJSO Answer Key & SolutionYatish Goyal100% (1)

- Instruction Manual Series 854 XTG Level GaugeDocument60 pagesInstruction Manual Series 854 XTG Level GaugeJandri JacobPas encore d'évaluation

- Ethics in ResearchDocument21 pagesEthics in Researchmukku_raviPas encore d'évaluation

- Hardware Devices Used in Virtual Reality TechnologiesDocument6 pagesHardware Devices Used in Virtual Reality TechnologiesTheMoon LightPas encore d'évaluation

- An Introduction to Heisenberg Groups in Analysis and GeometryDocument7 pagesAn Introduction to Heisenberg Groups in Analysis and Geometrynitrosc16703Pas encore d'évaluation

- Chem 361 Separation Methods IntroDocument8 pagesChem 361 Separation Methods IntroTwum SomoahPas encore d'évaluation

- Đề Minh Họa 2020 Số 23 - GV Trang Anh - Moon.vnDocument22 pagesĐề Minh Họa 2020 Số 23 - GV Trang Anh - Moon.vnLily LeePas encore d'évaluation

- Kevin Chiu - Solving Procrastination v1.1Document2 pagesKevin Chiu - Solving Procrastination v1.1TêteHautePas encore d'évaluation

- Private Void BtnDeleteActionPerformedDocument12 pagesPrivate Void BtnDeleteActionPerformedDDDPas encore d'évaluation

- Assembly Transmission Volvo A40GDocument52 pagesAssembly Transmission Volvo A40GNanang SetiawanPas encore d'évaluation

- Foundation ProblemsDocument71 pagesFoundation Problemsيقين يقين0% (1)

- 2022 Anambra State ITN Mass Campaign Report in Nnewi North LGA by Idongesit EtukudoDocument15 pages2022 Anambra State ITN Mass Campaign Report in Nnewi North LGA by Idongesit EtukudoIdongesit EtukudoPas encore d'évaluation

- Physical Layer:: SwitchingDocument27 pagesPhysical Layer:: SwitchingPKSachanPas encore d'évaluation

- DLP IN ICT 9 1st MeetingDocument2 pagesDLP IN ICT 9 1st MeetingHEDDA FULOPas encore d'évaluation

- The Champion Legal Ads: 11-02-23Document58 pagesThe Champion Legal Ads: 11-02-23Donna S. SeayPas encore d'évaluation

- IIT BOMBAY RESUME by SathyamoorthyDocument1 pageIIT BOMBAY RESUME by SathyamoorthySathyamoorthy VenkateshPas encore d'évaluation

- BOQ Sample of Electrical DesignDocument2 pagesBOQ Sample of Electrical DesignAshik Rahman RifatPas encore d'évaluation

- CS 704 Socio-Emotional and Moral Development in Middle ChildhoodDocument25 pagesCS 704 Socio-Emotional and Moral Development in Middle ChildhoodPatricia PamintuanPas encore d'évaluation

- Revision Module 1,2,3Document129 pagesRevision Module 1,2,3jitamitra88Pas encore d'évaluation

- 102DNDocument2 pages102DNManuel ZavalaPas encore d'évaluation

- DUPLICATE BILL TITLEDocument8 pagesDUPLICATE BILL TITLEMohammed AhmedPas encore d'évaluation

- Risk Assissment 1Document12 pagesRisk Assissment 1Ibrahim BouzinaPas encore d'évaluation

- Atpl Formula MergedDocument74 pagesAtpl Formula Mergeddsw78jm2mxPas encore d'évaluation

- Halo Outdoor slmt1000 - slmt1000wDocument1 pageHalo Outdoor slmt1000 - slmt1000wFrank MoyaPas encore d'évaluation

- Designing of 3 Phase Induction Motor Blackbook DoneDocument30 pagesDesigning of 3 Phase Induction Motor Blackbook Donetryd0% (1)

- TLUD Handbook, Paul Anderson, V.2010Document19 pagesTLUD Handbook, Paul Anderson, V.2010satyakaamsPas encore d'évaluation