Académique Documents

Professionnel Documents

Culture Documents

1995-Transaction-Impact of IGBT Behavior On Design Optimization

Transféré par

Gabriel MejiaTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

1995-Transaction-Impact of IGBT Behavior On Design Optimization

Transféré par

Gabriel MejiaDroits d'auteur :

Formats disponibles

280

IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 31, NO. 2, MARCHJAPRIL 1995

Impact of IGBT Behavior on Design Optimization

of Soft Switching Inverter Topologies

Alexander Kurnia, Member, IEEE, Hassan Cherradi, and Deepakraj M. Divan, Senior Member, IEEE

Abstract- IGBTs operated under a zero voltage switching

scheme exhibit significantly different operating characteristics

from specified parameters in manufacturer data sheets. Important differences include an elevated tail current, dynamic

saturation and resulting snubber dump, and a significantly higher

conduction loss under moderate to high &/at conditions. Soft

switching inverter topologies of various kinds have been reported

in the literature including resonant dc and ac link inverters,

resonant pole inverters and many variations thereof. Loss characterization of soft switching inverter circuits reported to date

is based on manufacturer data sheets, and do not reflect actual

losses incurred in the circuit. Including the actual device behavior

into the circuit loss calculations has a big impact on the total

losses, and more importantly the trade-offs which impact the

viability of a given topology at a specified operating point. This

paper presents a detailed analysis of the losses in soft switching

inverters and the impact on topology choice. A detailed design of

a 50-kVA IGBT-based resonant dc link inverter is used as a design

example, and it is seen that optimal design points and choices are

significantly different from those that have been reported earlier.

I---.

DUT

Fig. 1. Test circuit used for characterizing IGBTs under zero voltage

switching.

and parasitic inductance within the device package and in

the circuit layout. This paper investigates important device

properties and the impact on converter choice and operation.

The approach taken in this paper consists of presenting

measured loss data for IGBTs operating under zero voltage

switching, identifying the various new loss mechanisms and,

subsequently, proposing an approach to include both of them

in the converter design optimization process. Detailed loss

calculations to determine optimal design points and choices

for a 50-kVA actively clamped resonant dc link inverter will

be used as an example.

Paper IPCSD 94-55, approved by the Industrial Power Converter Committee of the IEEE Industry Applications Society for presentation at the 1993

Industry Applications Society Annual Meeting, Toronto, Ontario, Canada,

October 3-8. Manuscript released for publication July 1 , 1994.

A. Kurnia was with the Department of Electrical and Computer Engineering,

University of Wisconsin, Madison, WI 53706-1691 USA. He is now with AC

Delco Systems, Technology Development, Indianapolis, IN 46256 USA.

H. Cherradi was with the Department of Electrical and Computer Engineering, University of Wisconsin, Madison, WI 53706-1691 USA. He is now with

C.L.M.L./O.N.A., Rabat, Morocco.

D. M. Divan is with the Department of Electrical and Computer Engineering, University of Wisconsin, Madison, WI 53706-1691 USA.

IEEE Log Number 940828 1.

The major losses normally considered in power devices

such as IGBTs are the conduction and switching losses.

Reasonably measuring the actual power loss in an in-circuit

operating device is not an easy task. Difficulties due to measurement artifacts limit the resolution obtainable and impact

the accuracy. Further, it is difficult to make direct current

measurements without altering the test circuit. In order to avoid

these problems and reasonably measure the actual power loss,

the test circuit of Fig. 1 was used.

The loss mechanisms identified for IGBTs under zero

voltage switching conditions are depicted in Fig. 2. Ideally,

as per manufacturer data sheets, one would expect to find

conduction loss, switching loss primarily as a result of the

tail current, and to a lesser extent, loss due to dynamic

saturation. A very unexpected loss mechanism is seen to be

an additional conduction loss component in the device which

is dependent on the d i / d t in the device [l]. Resulting voltage

drops of as high as 6-10 V have been consistently observed

and are significantly greater than can be accounted for due to

in situ parasitic inductance. This can be seen from Fig. 3(a)

where the device under test was FUJI 2MBI100L-120 rated

at 100 A and 1200 V. Further, measurement of in-circuit

inductance using resonance confirms our calculated estimate,

I. INTRODUCTION

HE application of soft switching inverters such as the

resonant dc link inverter is being actively considered by

many manufacturers. With the use of IGBTs, link frequencies

of 30 to 90 kHz seem to be practical at power levels of up

to 200 kW. A long held premise for promoting soft switching

converters has involved device specifications, considered to

be as per manufacturers data sheets. Detailed investigation of

device behavior under soft switching conditions, as opposed to

the more conventional hard switching conditions, has shown

that devices do not behave as per data sheets under both

zero voltage and zero current switching conditions. Particularly, under zero voltage switching conditions, IGBTs have

been shown to demonstrate unanticipated loss mechanisms

which dramatically influence frequency capabilities, and also

unexpectedly influence the choice of converter topology. This

is over and above anticipated second order effects such as

diode reverse recovery, dynamic saturation during tum-on

11. IGBT

0093-9994/95$04.00 0 1995 IEEE

Loss MODEL

KURNIA et al.: IMPACT OF IGBT BEHAVIOR ON DESIGN OPTIMIZATION OF SOFT SWITCHING INVERTER TOPOLOGIES

Conduction Los

28 1

in L

I .

Circulating Current (?)

Fig. 2. Major sources of loss in ZVS IGBTs.

and is much less than the observed dildt-dependent voltage

drop. The most probable mechanism for the di/dt dependence

seems to be conductivity modulation lag, a phenomenon

that we have observed in most conductivity modulated devices

including p-i-n diodes [2], [3]. Fig. 3(b) shows data plotting

Vce as a function of di/dt for different values of collector

current at 25OC and clearly points out that Vce is strongly

dependent upon both quantities. V, is seen to be considerably

in excess of values predicted from device internal inductance.

Similar results are obtained at temperature of 125C. This

proposes an equivalent circuit arrangement which is composed

of an equivalent resistance, as suggested by manufacturer

data sheets, in series with an equivalent inductance which

is an inherent characteristic of the device. The relationship

governing V,, is given by

- 5

9

4

_Q_

0

For the device that will be considered later in loss calculations,

Le, = 65 nH within the operating range of interest.

Another interesting property reported for IGBT turn-off is a

tail current bump which occurs under low dv/dt conditions,

particularly at high temperatures (see Fig. 4(a)). This seems to

occur as a result of inadequate charge removal from the drift

region [4]. Fig. 4(b) shows experimentally measured turn-off

losses for a second generation FUJI-IGBT under low dv/dt

conditions at 25OC. As expected, a higher temperature results

in higher turn-off losses. By curve-fitting these measured data,

an expression that gives turn-off energy losses for given device

current and snubber capacitance value can be obtained.

Fig. 3(a) also reveals that the device takes a long time to

reach steady state conduction loss condition, and typically

involves a dynamic saturation bump. Under these conditions,

if a snubber capacitor is used across the device (to obtain zero

voltage switching), one can obtain significant turn-on loss due

to snubber dump. Finally, this snubber dump can also set up

very large circulating currents between the snubber capacitor

and the device package possibly overstressing the device. A

detailed discussion of some of these loss mechanisms has been

presented in [1].

10

20

Vce @ IC=1OOA

Vce@Ic=90A

Vce@Ic=80A

Vce @Ic=75A

Vce@Ic=70A

Vce@Ic=60A

Vce@Ic=SOA

Vce@Ic=40A

30

40

di/dt (Alps)

50

I

60

(b)

Fig. 3. (a) An oscillogram of V,, (2 V/div) at different d i l d t s at 25OC, time

(1 ps/div), IGBT-FUJI 2MBI100L-120. (b) Test results from the \&-Ic measurements at different values of d i / d t at 25OC, IGBT-FUJI2MBI100L-120.

Another loss mechanism encountered is due to the energy

trapped in the device internal inductance, LSt.The corresponding energy (0.5 L&) is dissipated in the device at turn-off.

Although this applies for hard switching inverters, the higher

switching frequencies typical for soft switching inverters can

make those losses important. Such loss data have also been

measured for various IGBTs and are found to be similar.

The second generation FUJI 2MBI100L-120 will be the one

considered in the presented design methodology.

It is clear that the IGBT behaves significantly differently

under zero voltage conditions than under more conventional

hard switching conditions. While much of this behavior is a

result of available devices having been optimized for hard

switching conditions, it nevertheless reflects the fact that

converter topologies must be assessed on the basis of these

device properties.

282

IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 31, NO. 2, MARCHIAPRIL 1995

Fig. 5.

Actively clamped resonant dc link inverter

Operating at higher frequencies only exacerbates the problem. Taken in conjunction with the widely varying switching

frequency, high-VA ratings of the filter components, and highpeak current stress in the device, it is considered that resonant

pole converters tend to be at a substantial disadvantage, and

will not be considered further. The most promising converters

for moderate power applications of 1-200 kW seem to be the

family of resonant dc link circuits, with the ARCP inverter

a distinct possibility at even higher power levels. This paper

examines first the issue of topology selection based on detailed

device characteristics.

111. RESONANTDC LINKINVERTEROPERATION

20

40

60

80

100

120

I, (A)

(b)

Fig. 4. (a) Oscillogram of

(100 V/div) and I , (20 A/div) during turn-off

with C = 100 nF at 25OC, and 125OC time (0.5 ps/div), IGBT-FUJI

2MBI100L-120. (b) Test results of turn-off loss for different values of IGBT

turn-off current and capacitor, at 25OC, IGBT-FUJI 2MBI100L-120.

Examining zero voltage switching converter topologies from

the open literature, two m&jor categories can be defined [ 5 ] .

These include resonant pole inverters and resonant link inverters, along with several variations including quasi-resonant

dc link inverters, parallel resonant dc link inverters and the

auxiliary resonant commutated pole (ARCP) inverter. Basic

resonant pole inverter operation requires that soft switching

conditions be generated by forcing the current in an output

inductor to rapidly ramp up and down so as to follow the

desired average value. This necessitates continuous operation

under high d i l d t , and causes very high conduction loss in

the device as a result of the dildt-dependent voltage drop.

The actively clamped resonant dc link (ACRDCL) inverter

shown in Fig. 5 is the most commonly used of the soft

switching inverter circuits. This topology permits inverter

operation using devices with voltage ratings similar to that of

PWM inverters intended for the same input and output voltage

levels. This does not preclude voltage ringing considerations,

as zero voltage switching eliminates voltage spikes associated

with diode recovery. The clamp and main devices of the

ACRDCL all operate under zero voltage switching, but their

switching characteristics and, thus, the associated switching

loss are quite different.

The clamp device operates at the link frequency ( f i ) and

experiences the highest switching loss [4]. The average maximum link frequency is given by (2) [6].

1

Tl = - = a

K-1

fl

The d i l d t in the clamp, the peak current, and the conduction

time depend on the circuit parameters and are expressed as

( K - 1)K

L,

K ( 2 - K)V?

=

LICr

--

dt

Isp

(3)

(4)

KURNIA et al.: IMPACT OF IGBT BEHAVIOR ON DESIGN OPTIMIZATION OF SOFT SWITCHING INVERTER TOPOLOGIES

and

The diode of the clamp circuit conducts during time t,, from

current -Ispto 0 A. Then the clamp current is transferred

to IGBT which also conducts during time t,, until the current

reaches its peak Is,. For the loss calculation, it is assumed that

the load current I, is not allowed to change instantaneously.

The clamp device has a continuous and high dildt whenever it

is conducting, as it clamps KV, across the resonant capacitor

C,. Under such conditions, it has a high-conduction drop

which is proportional to dildt, and a high-circulating current.

This incurs additional losses which are a significant portion

of total inverter loss.

Inverter loss calculations are based on semiconductor losses.

Losses due to high-circulating current are also neglected. The

inverter is assumed to operate in a way such that the load

current I, is not allowed to change instantaneously. For the

worst case scenario, the inverter is driving a resistive load.

The clamp losses consist of conduction and switching loss.

At a constant link frequency, smaller values of resonant inductance L, are indicated for larger resonant capacitors C,. This

results in lower switching losses in the main devices because

of lower dwldt, but increases the switching losses in the clamp

devices since the peak current Is,,in the clamp increases

dramatically. On the other hand, smaller L , induces higher

dildt, and simultaneously higher conduction loss. The various

loss components in the clamp device can be calculated using

the clamp equations and the experimentally measured loss-data

for the kind of device under use. The clamp conduction loss

of IGBT and diode can be evaluated using

tSP

Pcl(con) = f i

(vce

+ Vdiode)Iadt

= fi(k0

+ h I s p + kZI,2,)

(7)

where ko, k l , k ~are

, constant coefficients of the second order

polynomial curve-fitted equations obtained from the turn-off

loss curve.

Moreover, there are two other loss components related to

dynamic saturation at turn-on and to the energy stored in the

device internal inductance. These are not as substantial as the

previous loss quantities, and are given by

Pcl(on) = O.5fiCTV$

27t

7t

The six main inverter devices, on the other hand, behave

very differently. On turn-on, the current quickly ramps up

to the load current value, where it remains for the rest

of the resonant cycle. These devices consequently do not

experience a continuous and high dildt, and do not have the

additional loss identified above. Further, these devices switch

at a rate much lower than the average link frequency, and

thus have very low average switching loss. The various loss

components in the main devices can also be derived for a

modulation strategy that gives an output time current plot.

Remembering that switch operation is governed by a discrete

pulse modulation strategy, the switching frequency can be

expressed in terms of the average duty factor d and the link

frequency fi in the following manner [7].

< 0.5 + fsw

d > 0.5 + fsw

d

= dfi

(1 - d)fi

(10)

where the duty factor equals the ratio of the instantaneous

sinusoidal output voltage V,, and the corresponding peak

voltage VOpk.

(6)

where Vce is given by (1) and Vdi& is forward bias voltage

of free-wheeling diode. The turn-off energy loss in the clamp

is an experimentally measured quantity that is curve-fitted as

a second order polynomial. This yields the turn-off power loss

in the clamp as

PCl(0ff)

0

Fig. 6 . Load current and voltage.

(8)

For the worst case scenario, the load current IOand output

voltage V, are assumed to be in phase as shown in Fig. 6.

Under this condition, the fraction of time that each IGBT

conducts K , can be expressed as

1

- -(1

"-2

+ dsin8)dB.

(12)

The conduction loss of IGBT's in the six main devices is

found to be

and the conduction loss of the free-wheeling diodes is found

to be

where Vpk is the dynamic saturation voltage spike which is

also a measured quantity, and

is the saturation forward voltage drop of IGBT

(9) where Vce-sat

The total clamp loss is obtained by summing the various loss

components.

and V d is the conduction drop across the main free-wheeling

diodes. For the worst case scenario, the duty factor d is

assumed to be one. Hence, the total conduction loss in the

284

IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 3 I , NO. 2, MARCWAPRIL 1995

six main devices is found to be

Pmain(con) FZ

l.7Ke-sat100,k

0'2vd10pk.

(14)

It can be seen that there is no additional dildt-dependent

conduction loss component as explained above. The turn-off

loss quantity is also derived for this modulation strategy and

is found to be

where ko, k1, and k2 are the same as in (7). The turn-on

loss is negligible as the resonant capacitor is not across every

individual main device. The loss due to the internal inductance

in each device is also small and is expressed as

Once again, total main device losses are found by summing

individual components.

IV. Loss CALCULATION

Design optimization of soft switching inverters, such as

the resonant dc link inverter, has been presented in various

publications [8], [9]. However, most of the optimizations have

been based on device properties given in manufacturer data

sheets. It is found that design optimization is also significantly

influenced by improved understanding of IGBT characteristics.

The actively clamped resonant dc link inverter has been

preferred in the past because of lower voltage stress, although

the passive clamp would be desirable if higher voltage devices

were available without significant cost penalty. It is interesting

to note that the active clamp switch operates under high

dildt conditions whenever it conducts, incurring additional

losses as identified above. In fact, depending on the particular

design, the dildt-dependent loss can be the most dominant loss

component, and thus the limiting factor. This is also the most

likely reason for several early clamp device failures that have

been documented in several laboratories. On the other hand,

the six main inverter devices do not have the additional loss

identified above, have a lower switching rate, and therefore,

have very low average switching loss. This is also one of the

reasons why the passively clamped resonant dc link inverter is

preferred if higher voltage devices are available at reasonable

cost.

With experimentally measured loss data for the IGBT under

use and the analytical approach outlined above, it is possible

to optimize the design of the RDCL inverter. Fig. 6 shows

design optimization curves which have been calculated for

a 50-kVA actively clamped resonant dc link inverter using

the 2nd generation FUJI-IGBT's, where the bus voltage is

600 V and the peak inverter output current is 100 A. Loss

calculations have been made for various scenarios including

constant frequency operation and constant LC tank while the

clamping voltage is varied.

Fig. 7(a) shows clamp device conduction and turn-off losses

at a constant link frequency of 60 kHz, as the resonant

capacitor is varied. As the peak voltage stress ( K )is reduced,

1.0

1.2

1.4

1.6

2.0

1.8

K (Clamp Factor)

(a)

10

I .

'

'

'

' I

' I

'

'

Fig. 7. (a) Clamp conduction and tum-off loss at 25OC using the new loss

mechanisms for three different capacitance values, I., = 600 V, Io,* = 100

A, fl = 60 kHz, IGBT-FUJI 2MBI100L-120. (b) Power loss comparison

of ACRDCL inverter for two different loss models at 25OC, IOpk

= 100 A,

Vs = 600 V, C, = 100 nF, L , = 27.2 pH, IGBT-FUJI 2MBI100L-120.

the conduction and thus the turn-off loss increase. Interestingly

enough, as the resonant capacitor is increased, the losses also

increase. This counter-intuitive result is due to a substantial

increase in circulating current which contributes to turn-off

KURNIA et al.: IMPACT OF IGBT BEHAVIOR ON DESIGN OPTIMIZATION OF SOFT SWITCHING INVERTER TOPOLOGIES

700

285

TABLE I

COMPARATIVE

DATAFOR SO-kVA RDCL-ACTIVELY CLAMPED

(K

= 2.0), WHEREf i = 60 kHz,

= 100 nF, AND L,. = 35

DH, AND HARLISWITCHED

PWM INVERTER

f,w = 10 kHz

FOR V, = 600 V, IGBT-FUJI 2MBI100L120. @i = 25OC.

c,

6004

RDCL RDCL

Clamp Type

2

1.4

Main Devices:

465

61

Zonduction Loss (W)

Tum-off Loss (W)

Tum-on Loss (W)

Stray Inductance Loss 0

MAINDEVICELOSS(W)

0.9 1.0 1.1 1.2 1.3 1.4 1.5 1.6 1.7 1.8 1.9 2.0

K (Clamp Factor)

465

61

0 1 0

530

530

Clamp Switch:

londuction Loss (W)

n/a

15

33

0.3

I

I n/a

49

n/a

TOTAL INVERTER LOSS (W) I 579

530

Tum-off Loss (W)

Tum-on Loss (W)

Stray Inductance Loss 0

CLAMPSWITCHLOSS(W)

n/a

1

n/a

Fig. 8. Power loss for the ACRDCL inverter using the new loss model for

two different temperatures, \% = 600 V, Iopk= 100 A, C,. = 100 nF,fr =

60 kHz, and IGBT-FUJI 2MBI100L-120.

@

loss, and higher d i / d t due to the smaller L,, which in turn

causes higher conduction loss.

Fig. 7(b) shows clamp device and main devices loss besides

the inverter overall loss (per unit device). It in turn examines

the impact of the improved device model on component

ratings, and thus on inverter design. The previous device model

considered is the one referred to in [9]. Including the additional

loss mechanism impacts the clamp device the most, as may

be expected.

Finally, Fig. 8 demonstrates the dramatic effect of considering temperature variations. The turn-off losses increase very

substantially with temperature, as a result of the tail current

bump. This clearly indicates the importance of including

temperature characteristics in the design process.

Unlike conventional load resonant converters, there is the

possibility of optimizing the design of the RDCL inverters.

This can be achieved by reducing device circulating currents.

C, can be sized so as to yield the desired dw/dt and the

switching loss in the main devices, under the worst case

within inverter switching state change. Then, L, can be chosen

as large as possible regarding the desired link frequency.

Table I shows a performance comparison for the actively

clamped, the passively clamped resonant dc link inverters

and the PWM-VSI inverter. It should be mentioned that

loss calculation for the PWM-VSI case has also been done

predicated on experimentally measured data for the same kind

of device (see Fig. 4(b)) and analytical loss expressions that

have been established in a similar fashion to that done for

the ACRDCL. The three inverters are rated at 50 KVA for a

dc bus voltage of 600 V. Table I shows that for the desired

link frequency, L, and C, can be appropriately chosen to

enhance the performance of the ACRDCL. Table I1 displays

the effect of including temperature on the performance of those

converters.

TABLE I1

TI = 12SC

lRDCL

5qm

Clamp Type

Conduction Loss (W)

Tum-off Loss (W)

Tum-on Loss (W)

Stray Inductance Loss (W)

MAIN DEVICE LOSS (W)

658

Clamp Switch:

Ida

465

189

0 1

4 ,

465

314

314

0.75

658

1094

15

Conduction Loss (W)

Turn-off Loss 0

Tum-on Loss (W)

Stray Inductance Loss 0

CLAMP SWITCH LOSS (W)

212

n/a

n/a

n/a

125

n/a

I

~

n/a

n/a

TOTAL INVERTER LOSS (W) [ 783

V. CONCLUSION

This paper has presented a detailed examination of the

factors that affect the design of resonant dc link inverters

using IGBTs.

Measured loss data for IGBTs operating under zero voltage

switching conditions have been provided and various loss

mechanisms have been identified. An approach that includes

measured device characteristics in the converter design optimization process has been proposed.

The paper has also addressed the suitability of the resonant

dc link ( R D C L ) inverter in view of better device understanding. It showed that the performance of this family of

converters can be substantially improved by properly choosing

the resonant components for a desired link frequency. Under

such criteria, loss calculation and comparison with the family

286

IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 31, NO. 2, MARCWAPRIL 1995

of PWM-VSIs have highlighted the fact that the resonant link

inverter can offer a far better performance in terms of device

loss reduction with a moderate peak voltage stress ( K )of 1.3

or 1.4.

REFERENCES

[I] A. Kurnia, 0. H. Stielau, G. Venkataramanan, and D. M. Divan, Loss

mechanisms in IGBTs under zero voltage switching, IEEE-PESC

Con$ Rec., 1992, pp. 1011-1018.

[21 B. J. Baliga, Modern Power Devices. New York: Wiley, 1987.

[3] N. Mohan, T. M. Undeland, and W. P. Robbins, Power ElecrronicsConverters, Applications and Design. New York: Wiley, 1989.

[4] A. Petterteig and T. Rogne, IGBT turn-off losses in hard switching and

with capacitive snubber, EPE-MADEP Con$ Rec., pp. 0:203-0:208,

1991.

[5] G. Venkataramanan and D. M. Divan, Comparative evaluation of soft

switching inverters, EPE Con$ Rec., pp. 2013-2:019, 1991.

[6] D. M. Divan and G. L. Skibinski, Zero-switching loss inverters for

high power applications, IEEE-/AS Con$ Rec. pp. 627-634, 1987.

M. Kheraluwala and D. M. Divan, Delta modulation strategies for

resonant link inverters, IEEE-PESC Con$ Rec., pp. 271-278, 1987.

D. M. Divan, G. Venkataramanan and R. W. De Doncker, Design

methodologies for soft switched inverters, IEEE-IAS Con$ Rec., pp.

758-766, 1988.

[91 A. Mertens and D. M. Divan, A high frequency resonant dc link inverter

using IGBTs, IPEC Con$ Rec., pp. 152-160, 1990.

Alexander Kurnia (M93) received the B.Sc. and

M.Sc. degrees in electrical engineering from the

University of Wisconsin, Madison, in 1990 and

1993, respectively.

From 1991 to 1993, he was a Research Assistant with the Electrical and Computer Engineering

Department, University of Wisconsin, where he

worked in the areas of IGBTs characterization and

design optimization of resonant dc link inverters.

From 1993 to 1994, he was a Design Engineer

with MTI International, Milwaukee, WI, where he

worked in the design of unity input power factor-parallel operations electronic

ballasts and development of single-stage unity power factor ac/ac power

converters for electronic ballasts. He is currently working on applied research

and development of high-performance power converters for electric vehicles at

AC Delco Systems, Technology Development, Indianapolis, IN. His primary

research interests are in power electronic converter circuits. He has three

patents pending in electronic ballasts and intelligent lighting areas.

Mr. Kurnia has published several papers, including a second-prize paper

for the Industrial Power Semiconductor Committee at the 1993 Industry

Applications Society Annual Meeting. He is a member of Eta Kappa Nu.

Hassan Cherradi was bom in May 1966, in Rabat,

Morocco. He graduated from the National School

of Mining and Industry, Rabat, (1984-1990), as a

graduate engineer in electromechanics. He received

the M.Sc. degree in electrical engineering from the

University of Wisconsin, Madison, in 1993.

From 1991 to 1993, he was a Research Assistant with the Electrical and Computer Engineering

Department, University of Wisconsin, where he

worked in the areas of high-power level GTO based

inverters. After graduation, he was in charge of the

production section in Industube, Tangier, Morocco, for five months. He is

presently working for C.L.M.L./O.N.A., Rabat, as Maintenance and New

Special Techniques Engineer. His areas of interest are in power electronics.

Mr. Cherradi has published several papers, including a second-prize paper

for the Industrial Power Semiconductor Committee at the 1993 Industry

Applications Society Annual Meeting.

Deepakraj M. Divan (S78-M78-S82-M83SM91) received the B.Tech. degree in electrical

engineering from the Indian Institute of Technology,

Kanpur, India, in 1975. He received the MSc. and

Ph.D. degrees in electrical engineering from the

University of Calgary, Canada.

He worked for two years as a Development

Engineer with Philips India Ltd. In 1979, he started

his own concern in Pune, India, providing product

development and manufacturing services in the

power electronics and instrumentation areas. In

1983, he joined the Department of Electrical Engineering at the University

of Alberta, Canada, as an Assistant Professor. Since 198.5, he has been with

the Department of Electrical and Computer Engineering at the University

of Wisconsin, Madison, where he is presently a Professor. He is also an

Associate Director of the Wisconsin Electric Machines and Power Electronics

Consortium (WEMPEC), a group of approximately 52 industrial sponsors

supporting research in the area of power electronics and machines. His

primary areas of interest are in power electronic converter circuits and

controls techniques. He is a consultant for various organizations including

the Electric Power Research Institute, Oakridge National Laboratory, and is

also working with several industries. He has over 70 papers in these areas

as well as 12 patents.

Prof. Divan has been a recipient of the Killam Scholarship while in the

Ph.D. program, and has also won various prize papers, including the IEEE-IAS

Best Paper Award for 1988-89, second prize paper at PCC-Yokohama93,

prize papers for the Industrial Drives Committee in 1989 and 1991, the

Industrial Power Converter Committee in 1983, 1989, 1991, and 1993, and

the Power Semiconductor Committee in 1990. He has been the Program

Chairman for the 1988 and 1989 Industrial Power Converter Committee of

the IEEE-IAS, Transactions Review Chair for the committee in 1990 and

1991, and is presently Chairman of the Committee. He was Technical Program

Chairman for PESC 91, and a Treasurer for PESC89. He was Chairman of

the Education Committee in the IEEE Power Electronics Society during 1990

and 1991, an Adcom Member since 1991, and is presently the Technical

Vice President for the society. He is a member of the R&D Committee of

the Power Sources Manufacturers Association and a member of the National

Committee on Power Electronics.

Vous aimerez peut-être aussi

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5795)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1091)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- 4th Generation Control Logic Allison 1000/2000/2400Document1 page4th Generation Control Logic Allison 1000/2000/2400John MichaelPas encore d'évaluation

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- Design of Induction Motors PDFDocument108 pagesDesign of Induction Motors PDFMaverick Naidu100% (3)

- Technology in Action Complete 9th Edition Evans Test BankDocument20 pagesTechnology in Action Complete 9th Edition Evans Test BankMrsKellyHammondqrejw100% (11)

- Static Synchronous Compensators (STATCOM) : A Review: B. Singh R. Saha A. Chandra K. Al-HaddadDocument28 pagesStatic Synchronous Compensators (STATCOM) : A Review: B. Singh R. Saha A. Chandra K. Al-HaddadGabriel MejiaPas encore d'évaluation

- PHEV-EV Charger Technology Tesis BuenaDocument113 pagesPHEV-EV Charger Technology Tesis BuenaGabriel MejiaPas encore d'évaluation

- Semi-Detailed Lesson Plan Tle 6 (Industrial Arts) Fourth QuarterDocument3 pagesSemi-Detailed Lesson Plan Tle 6 (Industrial Arts) Fourth QuarterEiram Williams78% (9)

- Fixed Frequency Sliding Mode (SM) Control Scheme Based On Current Control Manifold For Improved Dynamic Performance of Boost PFC ConverterDocument11 pagesFixed Frequency Sliding Mode (SM) Control Scheme Based On Current Control Manifold For Improved Dynamic Performance of Boost PFC ConverterGabriel MejiaPas encore d'évaluation

- Experimental Study On The in Uence of Dead-Time On IGBT Turn-Off Characteristics in An Inverter Leg at High and Low CurrentsDocument5 pagesExperimental Study On The in Uence of Dead-Time On IGBT Turn-Off Characteristics in An Inverter Leg at High and Low CurrentsGabriel MejiaPas encore d'évaluation

- A High Efficiency Bi-Directional EV ChargerDocument6 pagesA High Efficiency Bi-Directional EV ChargerGabriel MejiaPas encore d'évaluation

- A High-Efficiency 3.3-kW Bidirectional On-Board ChargerDocument5 pagesA High-Efficiency 3.3-kW Bidirectional On-Board ChargerGabriel MejiaPas encore d'évaluation

- Sliding Mode Control HandoutDocument42 pagesSliding Mode Control HandoutGabriel MejiaPas encore d'évaluation

- 1987-Sliding Motions in BilinearDocument15 pages1987-Sliding Motions in BilinearGabriel MejiaPas encore d'évaluation

- 2016 - Dhanasekar - Sliding Mode Control of Electric Drives ReviewDocument7 pages2016 - Dhanasekar - Sliding Mode Control of Electric Drives ReviewGabriel MejiaPas encore d'évaluation

- A G2V-V2G Off-Board Fast Charger For ChargingDocument6 pagesA G2V-V2G Off-Board Fast Charger For ChargingGabriel MejiaPas encore d'évaluation

- A Survey On The Contributions of Power Electronics To SmartDocument18 pagesA Survey On The Contributions of Power Electronics To SmartGabriel MejiaPas encore d'évaluation

- M2mpower Datasheet R1FDocument1 pageM2mpower Datasheet R1FGabriel MejiaPas encore d'évaluation

- Meets Mil-S-19500/291 Collector-Base Voltage 60V Collector Current: 600 Madc Fast Switching 345 NsDocument3 pagesMeets Mil-S-19500/291 Collector-Base Voltage 60V Collector Current: 600 Madc Fast Switching 345 NsGabriel MejiaPas encore d'évaluation

- Part I, Revision 2: Pice Utorial I DC ADocument28 pagesPart I, Revision 2: Pice Utorial I DC AGabriel MejiaPas encore d'évaluation

- 2003-Optimum Design of Snubber Capacitors in 9kW Three-Phase InverterDocument4 pages2003-Optimum Design of Snubber Capacitors in 9kW Three-Phase InverterGabriel MejiaPas encore d'évaluation

- 2011-The Loss Calculation of RCD Snubber With Forward and ReverseDocument8 pages2011-The Loss Calculation of RCD Snubber With Forward and ReverseGabriel MejiaPas encore d'évaluation

- IEEE STD ANSI-IEEE STD 668-1987Document24 pagesIEEE STD ANSI-IEEE STD 668-1987abdou samiPas encore d'évaluation

- TT100 Viscometer: For Inline Systems ApplicationsDocument2 pagesTT100 Viscometer: For Inline Systems ApplicationsPablo Antu Manque RodriguezPas encore d'évaluation

- Catalog Big Capacity AHU DX DuctedDocument28 pagesCatalog Big Capacity AHU DX DuctedBistok ManurungPas encore d'évaluation

- Catálogo Nord Redutores Aluminio SmoothmotorsDocument28 pagesCatálogo Nord Redutores Aluminio Smoothmotorsleonardo silveiraPas encore d'évaluation

- Dynapac CA4000 DCO Dynapac CA4000 DCO: Single Drum Vibratory Rollers Single Drum Vibratory RollersDocument2 pagesDynapac CA4000 DCO Dynapac CA4000 DCO: Single Drum Vibratory Rollers Single Drum Vibratory Rollersabdelrhmangbr86Pas encore d'évaluation

- Frankenstein Laser Engraver: InstructablesDocument38 pagesFrankenstein Laser Engraver: InstructablesKon ArvaPas encore d'évaluation

- PIAGGIO X10 500 Service Station ManualDocument226 pagesPIAGGIO X10 500 Service Station ManualMichaeluiMichaeluiPas encore d'évaluation

- 3241 L028-21-LCV-001 Type 3241-1 Pneumatic Control Valve Globe Valve 001 Raised Face Class 300 3271Document4 pages3241 L028-21-LCV-001 Type 3241-1 Pneumatic Control Valve Globe Valve 001 Raised Face Class 300 3271Nitin ZorePas encore d'évaluation

- Mecanismo de CDDocument57 pagesMecanismo de CDsuperinfPas encore d'évaluation

- Alliance 5w Remote Unit (Mrou) v2.3Document5 pagesAlliance 5w Remote Unit (Mrou) v2.3Diego ZagoPas encore d'évaluation

- MCE513 Lecture 1Document22 pagesMCE513 Lecture 1Atiba JoshuaPas encore d'évaluation

- E Catalogue Airhoists eDocument8 pagesE Catalogue Airhoists eAhmedPas encore d'évaluation

- Checklist For Partners: Complete SystemDocument3 pagesChecklist For Partners: Complete SystemparaboolPas encore d'évaluation

- ServeRAID M5110 SASSATA Controller For IBM System XDocument78 pagesServeRAID M5110 SASSATA Controller For IBM System XSnow DropPas encore d'évaluation

- Plano Electrico 450E EBLDocument4 pagesPlano Electrico 450E EBLDarío Ache EmePas encore d'évaluation

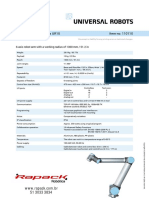

- Ficha T+®cnica UR10 CB3Document1 pageFicha T+®cnica UR10 CB3Isaque OteiroPas encore d'évaluation

- Ground Bounce: (And It's Dual, V Bounce)Document31 pagesGround Bounce: (And It's Dual, V Bounce)9844352836Pas encore d'évaluation

- February '96: 710-19 CARRARO AXLE Ref. 126139 For "J.I. CASE" Spare Parts ListDocument8 pagesFebruary '96: 710-19 CARRARO AXLE Ref. 126139 For "J.I. CASE" Spare Parts ListDmytro PichkurPas encore d'évaluation

- Siemens Polydoros IT X2287: Surve SheetDocument22 pagesSiemens Polydoros IT X2287: Surve SheetVictor ZambranoPas encore d'évaluation

- Book 1Document100 pagesBook 1Devasyruc100% (1)

- LA SpecificationDocument3 pagesLA SpecificationVino VinoPas encore d'évaluation

- Lincoln p203 PumpDocument4 pagesLincoln p203 PumphalimPas encore d'évaluation

- Saudara Kita EnterpriseDocument3 pagesSaudara Kita EnterprisetierachumelPas encore d'évaluation

- Vessel Hand Over Take Over Checklist - TugDocument3 pagesVessel Hand Over Take Over Checklist - Tugroni amiruddinPas encore d'évaluation

- Electrical Design of A Modern Contemporary HouseDocument5 pagesElectrical Design of A Modern Contemporary HouseNoxian TelicPas encore d'évaluation

- Rotary Vial Washing Machine VIALWASH 120RDocument1 pageRotary Vial Washing Machine VIALWASH 120RumangPas encore d'évaluation