Académique Documents

Professionnel Documents

Culture Documents

GC3355 Application NOTE

Transféré par

MarcianoValverdeCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

GC3355 Application NOTE

Transféré par

MarcianoValverdeDroits d'auteur :

Formats disponibles

GC3355 APPLICATION NOTE

GC3355 Application NOTE

Version 1.0

Page 1 of 5

GC3355 APPLICATION NOTE

Version

Date

Description

1.0

2013-11-28

Initial version

Page 2 of 5

GC3355 APPLICATION NOTE

1. General Description

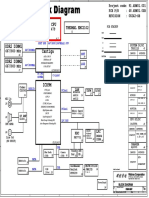

GC3355 supports two configuration mode: PN mode(CFG_P/CFG_N mode) and

UART mode. PN mode is back compatible with previous BTC mining ASIC chips, and

support BTC mining only. UART mode can support BTC and LTC, this Application note

describe UART mode only.

The following is one example of Mining System, with one Host CPU and 4

GC3355 chips. The CPU will run two cgminer programs, one for BTC mining and

another for LTC mining. Each GC3355 chip is assigned with one different ID to be

accessed by the Host CPU. The ID is used as chip address in the Mining System.

The following is the communication command from Host CPU to GC3355:

55, AA, {CLUS_ADDR[3:0], CHIP_ADDR[3:0]}, REG_ADDR[7:0], DATA[7:0],

DATA[15:8], DATA[23:16],DATA[31:24]

The UART mode also supports burst command, the data can be 32*N bits, for

example:

55, AA, {CLUS_ADDR[3:0], CHIP_ADDR[3:0]}, REG_ADDR[7:0], DATA0[7:0],

DATA0[15:8], DATA0[23:16], DATA0[31:24], DATA1[7:0], DATA1[15:8], DATA1[23:16],

DATA1[31:24], ..., DATAN-1[7:0], DATAN-1[15:8], DATAN-1[23:16], DATAN-1[31:24]

The DATA0, DATA1, DATAN-1 will be written to the following register

address: REG_ADDR, REG_ADDR+1, REG_ADDR+N-1.

Page 3 of 5

GC3355 APPLICATION NOTE

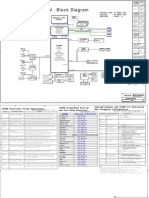

Each GC3355 chip only responses the command with the chip_id == the

CHIP_ADDR, or the CHIP_ADDR is 0xf which denote broadcast. In another words, if

the command is broadcast (the CHIP_ADDR is 0xf), all the chips will response the

command.

The CLUS_ADDR denote the function module in the GC3355: 0 is BTC module,

1 is LTC module; 0xE is CPM module.

The REG_ADDR is the register address in each function module. Please

reference the registers description for detailed information.

2. BTC work Mode

The following code is an example: xclk is 25MHz, core clock is 500MHz, force_start=0,

rpt_cycle = 0x10

cfg_chip_reg(8'hef, 8h00, 32h94e00005);

cfg_chip_reg(8h0f, 8hff, 32h00000010);

cfg_btc_data; //configure the BTCs data, which address is 0x00xb

3. LTC work mode

the following code is an example: xclk is 25MHz, core clock is 500MHz,

configure the UARTs, timeout = 0x10

cfg_chip_reg(8'h1f, 8'h28, ltc_cfg_ctrl); // ltc_cfg_ctrl = 0x00000013

cfg_chip_reg(8'hef, 8'h30, ltc_cfg_reg); //ltc_cfg_reg = 0x00000020

cfg_chip_reg(8'hef, 8h00, 32h 94e00005);// pll config

cfg_chip_reg(8hef, 8h02, 32h0000_0000);//gating BTCs core0- core31 clk

cfg_chip_reg(8hef, 8h03, 32h0000_0000);//gating BTCs core31-core63 clk

cfg_chip_reg(8hef, 8h04, 32h0000_0000);//gating BTCs core64-core95 clk

cfg_chip_reg(8hef, 8h05, 32h0000_0000);//gating BTCs core96-core127 clk

cfg_chip_reg(8hef, 8h06, 32h0000_0000);//gating BTCs core128-core159 clk

Page 4 of 5

GC3355 APPLICATION NOTE

cfg_chip_reg(8'hef, 8'h20, uart_bps); // uart_bps

cfg_chip_reg(8'hef, 8'h21, uart_timeout);//uart_timeout= 0x80000018

cfg_ltc_data;//config the ltcs data, which address are 0x00x22, min/max nonce: 0x23,

0x24

4. BTC+LTC work mode

the following code is an example: xclk is 25MHz, LTC/BTC core clk is 500MHz, configure

the UARTs BPS

cfg_chip_reg(8'hef, 8'h20, uart_bps); // uart_bps

cfg_chip_reg(8'hef, 8'h21, uart_timeout);//uart_timeout= 0x80000018

cfg_chip_reg(8'hef, 8'h30, ltc_cfg_reg); //ltc_cfg_reg = 0x00000020

cfg_chip_reg(8'h1f, 8'h28, ltc_cfg_ctrl); // ltc_cfg_ctrl = 0x00000017

cfg_chip_reg(8h0f, 8hff, 32h80000010);//btcs misc register

cfg_chip_reg(8'hef,8h00, 32h 94e00005);// pll config

fork

cfg_btc_data

cfg_ltc_data

join

Page 5 of 5

Vous aimerez peut-être aussi

- Power Point PresentationDocument17 pagesPower Point PresentationVPas encore d'évaluation

- Cortex A9 Tri-core Processor Specs and Physical DesignDocument7 pagesCortex A9 Tri-core Processor Specs and Physical DesignPramod Reddy RPas encore d'évaluation

- Development Board For Stm8S003F3: by Nitin Chand M S (2018H1400171P), Rohith Krishnan P (2018H1400180P)Document13 pagesDevelopment Board For Stm8S003F3: by Nitin Chand M S (2018H1400171P), Rohith Krishnan P (2018H1400180P)Thông NguyễnPas encore d'évaluation

- Acer Aspire 8730Document51 pagesAcer Aspire 8730Sadun CaymazPas encore d'évaluation

- Rotor-Cuda 1.0.7 TutorialDocument17 pagesRotor-Cuda 1.0.7 TutorialLoïc TernisienPas encore d'évaluation

- Sprs 276 KDocument255 pagesSprs 276 Ktheomen3007Pas encore d'évaluation

- MT48LC64M4A2Document86 pagesMT48LC64M4A2nhv_lhPas encore d'évaluation

- Lenovo 3000 G430 - Quanta LE6 Rev.1ADocument34 pagesLenovo 3000 G430 - Quanta LE6 Rev.1Aaries_2010Pas encore d'évaluation

- CT1 Block Diagram PCB Stack UpDocument38 pagesCT1 Block Diagram PCB Stack UpUno EstePas encore d'évaluation

- Osmeoisis 2022-09-06 15-33-19PIC - Mid - A - 8Document19 pagesOsmeoisis 2022-09-06 15-33-19PIC - Mid - A - 8Tomás BurónPas encore d'évaluation

- DELL Inspiron N4020Document88 pagesDELL Inspiron N4020Deddy SuyantoPas encore d'évaluation

- Serial ComDocument4 pagesSerial ComBanaNiBebangPas encore d'évaluation

- Acer Aspire 5738Document61 pagesAcer Aspire 5738Ariox VitriolPas encore d'évaluation

- RGMIIv1 3Document8 pagesRGMIIv1 3lim_mgPas encore d'évaluation

- DFI DK X38 OC Guideline: (BIOS Version: 2008/2/4) V001 Example of Over-Clock Device OverviewDocument8 pagesDFI DK X38 OC Guideline: (BIOS Version: 2008/2/4) V001 Example of Over-Clock Device OverviewAlloy TarungPas encore d'évaluation

- MC9S08QE128RMDocument346 pagesMC9S08QE128RMSergio ContrerasPas encore d'évaluation

- LC877364ADocument26 pagesLC877364AAlbert GTPas encore d'évaluation

- Dell Inspiron 1545 - Wistron Dr1 Roberts Uma - 48.4aq01.031 08212-3Document59 pagesDell Inspiron 1545 - Wistron Dr1 Roberts Uma - 48.4aq01.031 08212-3_Spiritum_75% (4)

- Spy RobotDocument74 pagesSpy Robotjanakiram473Pas encore d'évaluation

- Microstar (MSI) MS-168X Rev 0ADocument50 pagesMicrostar (MSI) MS-168X Rev 0ALuizLuizPas encore d'évaluation

- GSM Based Home AutomationDocument80 pagesGSM Based Home AutomationShashi Kant SainiPas encore d'évaluation

- Dell Inspiron 1750 - SchematicsDocument59 pagesDell Inspiron 1750 - SchematicsAnonymous i1XrU6jzo0Pas encore d'évaluation

- Timer - counting pulses with STM32 microcontrollerDocument5 pagesTimer - counting pulses with STM32 microcontrollerEdward ConalPas encore d'évaluation

- Acer TravelMate 5730 - WISTRON Homa 3g - SCDocument56 pagesAcer TravelMate 5730 - WISTRON Homa 3g - SCDiego R. NoalPas encore d'évaluation

- Dell Inspiron 1545 Wistron DR1 (Roberts)Document58 pagesDell Inspiron 1545 Wistron DR1 (Roberts)Geoffrey M. Gitau100% (1)

- MG82F6D17 Datasheet: 8051-Based MCUDocument307 pagesMG82F6D17 Datasheet: 8051-Based MCUAnil GayakwadPas encore d'évaluation

- GPU Model: Cedric Nugteren February 2, 2010Document8 pagesGPU Model: Cedric Nugteren February 2, 2010proxymo1Pas encore d'évaluation

- UART SpecDocument24 pagesUART SpecPronadeep BoraPas encore d'évaluation

- UARTDocument24 pagesUARTPronadeep BoraPas encore d'évaluation

- Acer SchematicsDocument48 pagesAcer Schematicsadyxyy1Pas encore d'évaluation

- Acer Emachines d725 - Wistron Hm40-MvDocument51 pagesAcer Emachines d725 - Wistron Hm40-MvNguyễn Công CườngPas encore d'évaluation

- Nexus 9000 Cloud Scale ASIC (Tahoe) NX-OS ELAMDocument7 pagesNexus 9000 Cloud Scale ASIC (Tahoe) NX-OS ELAMIsmail MirzayevPas encore d'évaluation

- Using The MSSP Module To Interface I2CDocument16 pagesUsing The MSSP Module To Interface I2Csoft4gsmPas encore d'évaluation

- DS 2CD2043G0 I20190403aawrd03410072 - 20200522231311Document37 pagesDS 2CD2043G0 I20190403aawrd03410072 - 20200522231311revanth kumarPas encore d'évaluation

- WinfoilDocument6 pagesWinfoilAshwini Kumar SinghPas encore d'évaluation

- Acer Aspire 7336 7336g 7336gz 7336z 7736 7736g 7736gz 7736z jv71-mv (09242-1 4fx01)Document60 pagesAcer Aspire 7336 7336g 7336gz 7336z 7736 7736g 7736gz 7736z jv71-mv (09242-1 4fx01)smooky1980Pas encore d'évaluation

- CODEDocument6 pagesCODEGuillaume ChopinPas encore d'évaluation

- Acer Aspire 6530 ZK3Document43 pagesAcer Aspire 6530 ZK3Jose A LachiondoPas encore d'évaluation

- Pertandingan Myskills Ke-7 Electronics CompetitionDocument11 pagesPertandingan Myskills Ke-7 Electronics Competitionnabilo20Pas encore d'évaluation

- 8051-Based MCU MG82F6D64/32 Data SheetDocument416 pages8051-Based MCU MG82F6D64/32 Data SheetSuper ManPas encore d'évaluation

- Block Diagram LayoutDocument73 pagesBlock Diagram LayoutPedro LuizPas encore d'évaluation

- PIC 16F877 CCP Modules for PWM, Capture & Compare ModesDocument8 pagesPIC 16F877 CCP Modules for PWM, Capture & Compare ModesPrabhu Parames100% (1)

- Watchdog Timer PIC18F4525Document6 pagesWatchdog Timer PIC18F4525Carlos LMPas encore d'évaluation

- Acer Extensa 5235 5635 5635z Quanta Zr6 Rev 1a SCHDocument42 pagesAcer Extensa 5235 5635 5635z Quanta Zr6 Rev 1a SCHvideosonPas encore d'évaluation

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationD'EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationPas encore d'évaluation

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkD'EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkPas encore d'évaluation

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.D'EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Pas encore d'évaluation

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960D'EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Pas encore d'évaluation

- Multicore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCD'EverandMulticore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCPas encore d'évaluation

- Mega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3D'EverandMega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3Pas encore d'évaluation

- From GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandD'EverandFrom GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandPas encore d'évaluation

- Definitive Guide to Arm Cortex-M23 and Cortex-M33 ProcessorsD'EverandDefinitive Guide to Arm Cortex-M23 and Cortex-M33 ProcessorsÉvaluation : 5 sur 5 étoiles5/5 (1)

- Master System Architecture: Architecture of Consoles: A Practical Analysis, #15D'EverandMaster System Architecture: Architecture of Consoles: A Practical Analysis, #15Pas encore d'évaluation

- ARM Microcontrollers Programming for Embedded SystemsD'EverandARM Microcontrollers Programming for Embedded SystemsÉvaluation : 5 sur 5 étoiles5/5 (1)

- Microprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureD'EverandMicroprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureÉvaluation : 1 sur 5 étoiles1/5 (1)

- 3-Sistem Kontrol PTL - 3Document97 pages3-Sistem Kontrol PTL - 3Usman FadillahPas encore d'évaluation

- +5 Volt, Serial Input, Dual 12-Bit DAC AD8522Document8 pages+5 Volt, Serial Input, Dual 12-Bit DAC AD8522Zoran ConstantinescuPas encore d'évaluation

- HT2300 Satellite Router Installation GuideDocument64 pagesHT2300 Satellite Router Installation GuideT Bag100% (1)

- AN4326Document14 pagesAN4326hnooriPas encore d'évaluation

- Catalogue Cap FLSDocument53 pagesCatalogue Cap FLSTrần Văn PhúcPas encore d'évaluation

- 2-HOLE LUGS FOR 300 SQ - MM CABLE - PDF (TDS)Document2 pages2-HOLE LUGS FOR 300 SQ - MM CABLE - PDF (TDS)mohamed1303Pas encore d'évaluation

- STCE/RTU Communication ProtocolsDocument24 pagesSTCE/RTU Communication ProtocolsJung Boo JangPas encore d'évaluation

- Crydom DC60 DataSheetDocument6 pagesCrydom DC60 DataSheetJose Carlos SoaresPas encore d'évaluation

- Helical Worm: Quick Selection GuideDocument24 pagesHelical Worm: Quick Selection GuideMohammad Ali TaghdiriPas encore d'évaluation

- RE 1 (BAB 8 DAN BAB 9) - Halaman-1,3-8Document7 pagesRE 1 (BAB 8 DAN BAB 9) - Halaman-1,3-8Yesi Indri HeryaniPas encore d'évaluation

- Model Yia Absorption Chillers: Renewal PartsDocument12 pagesModel Yia Absorption Chillers: Renewal PartsArshad MahmoodPas encore d'évaluation

- XPRO Manual Complete PDFDocument2 pagesXPRO Manual Complete PDFGibran Medina CardosoPas encore d'évaluation

- A Circularly Polarized Patch Antenna Array For Ku-Band Data-LinkDocument2 pagesA Circularly Polarized Patch Antenna Array For Ku-Band Data-LinkTolgahan TÜYLÜPas encore d'évaluation

- ToledoDocument123 pagesToledoNabyLamPas encore d'évaluation

- NotesDocument176 pagesNoteskalyanPas encore d'évaluation

- CIGRE-115 Switchgear Condition MonitoringDocument8 pagesCIGRE-115 Switchgear Condition Monitoringkamuik100% (1)

- VR-500 BrochureDocument2 pagesVR-500 Brochuresdelpi5146Pas encore d'évaluation

- Multiple Choice Exam on Telecom Installation FundamentalsDocument10 pagesMultiple Choice Exam on Telecom Installation Fundamentalsbanigx0xPas encore d'évaluation

- Versamate Cleanroom Receptacle PR19Document1 pageVersamate Cleanroom Receptacle PR19Anonymous llBSa7Pas encore d'évaluation

- Activity Module 1 (LED)Document39 pagesActivity Module 1 (LED)naughty dela cruzPas encore d'évaluation

- Microwave and Radar Engineering-Pcec 4101Document2 pagesMicrowave and Radar Engineering-Pcec 4101Dr-Harish Chandra Mohanta0% (1)

- IC Layout Using L-EDITDocument16 pagesIC Layout Using L-EDITEliasA.TiongkiaoPas encore d'évaluation

- Didactic Katalog 09 en Monitor 1Document348 pagesDidactic Katalog 09 en Monitor 1leofocerPas encore d'évaluation

- Chapter 3 MethodologyDocument3 pagesChapter 3 MethodologydanPas encore d'évaluation

- LG lrm-519 (ET)Document158 pagesLG lrm-519 (ET)joeblow44Pas encore d'évaluation

- CIGRE Curso HVDC - Perdas - Canelhas PDFDocument10 pagesCIGRE Curso HVDC - Perdas - Canelhas PDFcarlosrenatorcPas encore d'évaluation

- Assemble Electrical Circuit ComponentsDocument9 pagesAssemble Electrical Circuit ComponentsAnvi MantriPas encore d'évaluation

- An Example Project ReportDocument113 pagesAn Example Project ReportCaner KılıçalpPas encore d'évaluation

- M-Series Electromagnetic Flow Meter Converter: Installation, Operation and Maintenance ManualDocument45 pagesM-Series Electromagnetic Flow Meter Converter: Installation, Operation and Maintenance ManualRodrigo CiezaPas encore d'évaluation

- Equipment Cross Reference GuideDocument22 pagesEquipment Cross Reference GuideizmitlimonPas encore d'évaluation