Académique Documents

Professionnel Documents

Culture Documents

Ad9731 H

Transféré par

thanhtung_151987Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Ad9731 H

Transféré par

thanhtung_151987Droits d'auteur :

Formats disponibles

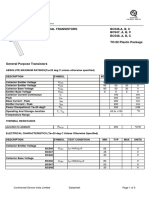

10-Bit, 170 MSPS, DAC

AD9731

1.0

S

COPE

This specification documents the detail requirements for space qualified product manufactured on

Analog Devices, Inc.'s QML certified line per MIL-PRF-38535 Level V except as modified herein.

The manufacturing flow described in the STANDARD SPACE LEVEL PRODUCTS PROGRAM

brochure is to be considered a part of this specification. http://www.analog.com/aerospace

This data sheet specifically details the space grade version of this product. A more detailed

operational description and a complete data sheet for commercial product grades can be found at

www.analog.com/AD9731

2.0

2.1

Part Number. The complete part numbers per Table I of this specification follow:

Part Number

Description

AD9731-703D

10-bit, 170 MSPS, DAC

AD9731-713D

Radiation tested, 10-bit, 170 MSPS, DAC

AD9731-703F

10-bit, 170 MSPS, DAC

AD9731-713F

Radiation tested, 10-bit, 170 MSPS, DAC

Case Outline.

1

Letter

D

F

Descriptive designator

CDIP2-T28

CDFP3-F28

Case Outline (Lead Finish per MIL-PRF-38535)

28-Lead Ceramic Side Brazed DIP package

28-Lead Ceramic Bottom Brazed Flatpack

See MIL-STD-1835

3.0

Absolute Maximum Ratings. (TA = 25C, unless otherwise noted)

+VS ................................................................................................................................. +6V

-VS ................................................................................................................................... -7V

Analog Output...................................................................................................... -VS to +VS

Digital Inputs ....................................................................................................-0.7V to +VS

Analog Output Current ...............................................................................................30 mA

Control Amplifier Input Voltage Range ............................................................... 0V to -4V

Control Amplifier Output Current .......................................................................... 2.5 mA

Reference Input Voltage Range .............................................................................0V to -VS

Operating Temperature Range................................................................... -55C to +125C

Storage Temperature Range....................................................................... -65C to +150C

Lead Temperature (Soldering, 10 sec.)..................................................................... +300C

Maximum Junction Temperature (TJ)....................................................................... +150C

ASD0011259

Rev. I

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its use,

nor for any infringements of patents or other rights of third parties that may

result from its use. Specifications subject to change without notice. No license

is granted by implication or otherwise under any patent or patent rights of

Analog Devices. Trademarks and registered trademarks are the property of

their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106,

U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.326.8703 2009 Analog Devices, Inc. All rights reserved.

AD9731

3.1

Thermal Characteristics:

Thermal Resistance, SIDEBRAZED (D) Package

Junction-to-Case (JC) = 12 C/W Max

Junction-to-Ambient (JA) = 40 C/W Max

Thermal Resistance, BOTTOMBRAZED (F) Package

Junction-to-Case (JC) = 22 C/W Max

Junction-to-Ambient (JA) = 66 C/W Max

4.0

Electrical Table:

TABLE I

Parameter

See notes at end of table

Differential Nonlinearity

Integral Nonlinearity

Zero Scale Offset Error

Symbol

Conditions

Note 1

DNL

INL

IOS

Full Scale Gain Error (Note 2)

Ae

Internal Reference Voltage

VREF

IREF = -50 A to 500 A

Sub

group

1

Limit

Min

Limit

Max

1

1.5

2, 3

1.5

70

2, 3

100

1, 2, 3

% FS

V

-1.35

-1.15

2, 3

-1.37

-1.13

VIH

1, 2, 3

Input Logic 0 Voltage

VIL

1, 2, 3

0.8

Input Logic 1 Current

IIH

1, 2, 3

50

Input Logic 0 Current

IIL

1, 2, 3

100

Positive Digital Supply Current

+IDIG

20

2, 3

22

42

2, 3

47

53

2, 3

66

Negative Analog Supply Current

-IDIG

-IANA

LSB

2, 3

Input Logic 1 Voltage

Negative Digital Supply Current

Units

LSB

A

V

A

mA

mA

mA

NOTES:

1 +VS = +5V, -VS = -5.2V, Clock = 125 MHz, RSET = 1.96 K for 20.4 mA IOUT, VREF =

-1.25V, unless otherwise specified.

2 Measured as an error in ratio of full-scale current to current through RSET (640 A nominal); ratio

is nominally 32. DAC load is virtual ground.

ASD0011259 Rev. I | Page 2 of 5

AD9731

4.1

Electrical Test Requirements:

Table II

Test Requirements

1/

2/

4.2

Subgroups (in accordance

with MIL-PRF-38535,

Table III)

Interim Electrical Parameters

Final Electrical Parameters

1, 2, 3 1/ 2/

Group A Test Requirements

1, 2, 3

Group C end-point electrical parameters

1 2/

Group D end-point electrical parameters

Group E end-point electrical parameters

PDA applies to Subgroup 1. Deltas excluded from PDA

See table III for delta parameters and limits.

Table III. Burn-in test delta limits.

TEST

TITLE

Table III

ENDPOINT

DELTA

LIMIT

LIMIT

UNITS

-IDIG

42

4.2

mA

IANA

53

5.3

mA

+IDIG

20

2.0

mA

IOS

70

35

Ae

5.0

2.0

%FS

ASD0011259 Rev. I | Page 3 of 5

AD9731

5.0

Package Pin-out:

6.0

Microcircuit Technology Group: The microcircuit is covered by technology group 80.

7.0

Life Test/Burn-In Circuit: Steady state life test is per MIL-STD-883 Method 1005. Burn-in is per

MIL-STD-883 Method 1015 test condition B.

8.0

MIL-STD-38535 QMLV exceptions:

8.1 Full WLA per MIL-STD-883 TM 5007 is not available for this product fabricated in a QMLQ wafer

process facility. SEM Inspection only is available per MIL-STD-883, TM2018.

ASD0011259 Rev. I | Page 4 of 5

AD9731

Rev

A

B

C

D

E

F

G

H

I

Description of Change

Initiate

Delete output compliance from Table I - guaranteed by design

Update paragraph 1.0, added web address

Update web address.

Delete Burn-In circuit.

Add AD9731-703F & AD9731-713F (flatpack version)

Clarify SEM vs. WLA availability for QMLQ fab process

Update header/footer & add to 1.0 Scope description

Add descriptive designator to 2.1- Case Outline

2009 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective

companies.

Printed in the U.S.A.

08/09

ASD0011259 Rev. I | Page 5 of 5

Date

June 30, 2000

Nov. 28, 2000

Feb. 7, 2002

Mar. 18, 2003

Aug. 5, 2003

Oct. 27, 2003

Sep. 21, 2007

Feb. 22,2008

Aug. 18, 2009

Vous aimerez peut-être aussi

- DRV 8801Document27 pagesDRV 8801Rian PermanaPas encore d'évaluation

- AMIS-39101 Octal High Side Driver With Protection: General DescriptionDocument12 pagesAMIS-39101 Octal High Side Driver With Protection: General Descriptionblackmesa82Pas encore d'évaluation

- PHILIPS LCD Ch-10.1L LLA-32PFL3605D-40PFL3605D PDFDocument71 pagesPHILIPS LCD Ch-10.1L LLA-32PFL3605D-40PFL3605D PDFAlecsandro BatistaPas encore d'évaluation

- DISCRETE SEMICONDUCTORS DATA SHEET: BB130 AM VARIABLE CAPACITANCE DIODEDocument4 pagesDISCRETE SEMICONDUCTORS DATA SHEET: BB130 AM VARIABLE CAPACITANCE DIODEAnonymous CdUZMZJq73Pas encore d'évaluation

- CDR 27038 RS485 JBus-ModBusDocument78 pagesCDR 27038 RS485 JBus-ModBusSmandy DanielPas encore d'évaluation

- BB809Document5 pagesBB809scribahoyosPas encore d'évaluation

- Ads 7870Document43 pagesAds 7870Moorthy VenkatachalamPas encore d'évaluation

- AirspeedDocument9 pagesAirspeednabawi24Pas encore d'évaluation

- Philips Chassis Tpm5.2e-LaDocument59 pagesPhilips Chassis Tpm5.2e-Larolandas1970Pas encore d'évaluation

- Pacusbd USB Downstream Port Terminator: Product DescriptionDocument8 pagesPacusbd USB Downstream Port Terminator: Product DescriptionnemonbPas encore d'évaluation

- Tpm4.1ela 689Document64 pagesTpm4.1ela 689fvictor1Pas encore d'évaluation

- Philips Ds9800w-10!37!93 Ver.1.1 Docking Speaker SystemDocument36 pagesPhilips Ds9800w-10!37!93 Ver.1.1 Docking Speaker Systemsupermax900100% (2)

- ACPL C87B ACPL C87A ACPL C870 Precision Optically Isolated Voltage SensorDocument14 pagesACPL C87B ACPL C87A ACPL C870 Precision Optically Isolated Voltage SensorlavaPas encore d'évaluation

- 2 N 3820Document3 pages2 N 3820Ariel NavarretePas encore d'évaluation

- LG 32PC5R Service ManualDocument16 pagesLG 32PC5R Service ManualThomas OldburyPas encore d'évaluation

- Strato 35 Series and 70 Series :: ROAL Living EnergyDocument5 pagesStrato 35 Series and 70 Series :: ROAL Living EnergyroalscribdPas encore d'évaluation

- Ads 4249Document67 pagesAds 4249gigimangiaterra15576Pas encore d'évaluation

- NPN RF Transistor: Symbol Parameter Value UnitsDocument4 pagesNPN RF Transistor: Symbol Parameter Value UnitsAdnanDeğerliyurtPas encore d'évaluation

- Obsolete: Omnidirectional Microphone With Bottom Port and Analog OutputDocument12 pagesObsolete: Omnidirectional Microphone With Bottom Port and Analog OutputngoctuongPas encore d'évaluation

- Manual Servico TV LCD Philips 42pfl3604Document67 pagesManual Servico TV LCD Philips 42pfl3604abe_1962100% (1)

- 42PFL3604Document67 pages42PFL3604Robert Van SchijndelPas encore d'évaluation

- 2 N 5952Document3 pages2 N 5952bahimetPas encore d'évaluation

- Analog I/o ModuleDocument20 pagesAnalog I/o Modulecamus1125Pas encore d'évaluation

- Product Description: Low Noise Phemt Gaas FetDocument4 pagesProduct Description: Low Noise Phemt Gaas FetGisela Fernandez ChavezPas encore d'évaluation

- TCM3.1L LA Colour TV Manual SectionsDocument67 pagesTCM3.1L LA Colour TV Manual SectionsAnonymous Gj5yPUC2JPas encore d'évaluation

- Philips 32pfl5404 Chassis Tpm3.1e La (ET)Document84 pagesPhilips 32pfl5404 Chassis Tpm3.1e La (ET)varimasPas encore d'évaluation

- SIMATIC S7 S7-1200 Programmable Controller - SM 1231 RTDDocument4 pagesSIMATIC S7 S7-1200 Programmable Controller - SM 1231 RTDLeon S. KennedyPas encore d'évaluation

- drv8805 PDFDocument19 pagesdrv8805 PDFAdithya ChandrasekaranPas encore d'évaluation

- Mc7447/Mc7457 Microprocessor Mos-13 Hip7Soi Qualification ReportDocument9 pagesMc7447/Mc7457 Microprocessor Mos-13 Hip7Soi Qualification ReportStrawichDanielPas encore d'évaluation

- FX2N 4AD TC - UserGuide - JY992D65501 G PDFDocument8 pagesFX2N 4AD TC - UserGuide - JY992D65501 G PDFTam DangPas encore d'évaluation

- D D D D D D D D D D D D D: CD74HC08-Q1 Quadruple 2-Input Positive-And GatesDocument8 pagesD D D D D D D D D D D D D: CD74HC08-Q1 Quadruple 2-Input Positive-And Gatesmalirezazadeh5549Pas encore d'évaluation

- Low Noise, Low Gain Drift, G 2000 Instrumentation AmplifierDocument20 pagesLow Noise, Low Gain Drift, G 2000 Instrumentation AmplifiervabecompPas encore d'évaluation

- NPN Silicon: Semiconductor Technical DataDocument4 pagesNPN Silicon: Semiconductor Technical DataMiloud ChouguiPas encore d'évaluation

- Dioda 1N4148Document6 pagesDioda 1N4148Dwie YuliantoPas encore d'évaluation

- Pioneer MJD508 MinidiskDocument72 pagesPioneer MJD508 MinidiskjjelectraPas encore d'évaluation

- Figure 1 - Terminal ConnectionsDocument6 pagesFigure 1 - Terminal ConnectionsNarendra BholePas encore d'évaluation

- RAUP-IOM (Rev.D)Document48 pagesRAUP-IOM (Rev.D)Thiraviam AyyappanPas encore d'évaluation

- lmp7721 PDFDocument32 pageslmp7721 PDFSatish ReddyPas encore d'évaluation

- Wide Bandwidth Dual Bipolar Operational Amplifier: DescriptionDocument10 pagesWide Bandwidth Dual Bipolar Operational Amplifier: DescriptionAlexander MasiasPas encore d'évaluation

- Analog Servo Drive: Description Power RangeDocument7 pagesAnalog Servo Drive: Description Power RangeElectromatePas encore d'évaluation

- ISO 9002 Certified NPN Transistors DatasheetDocument6 pagesISO 9002 Certified NPN Transistors Datasheettabassam7801Pas encore d'évaluation

- Catalog: General Purpose Plug-In RelaysDocument12 pagesCatalog: General Purpose Plug-In Relaysmicaziv4786Pas encore d'évaluation

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsD'EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsÉvaluation : 3.5 sur 5 étoiles3.5/5 (6)

- Offshore Electrical Engineering ManualD'EverandOffshore Electrical Engineering ManualÉvaluation : 4 sur 5 étoiles4/5 (9)

- High-Performance D/A-Converters: Application to Digital TransceiversD'EverandHigh-Performance D/A-Converters: Application to Digital TransceiversPas encore d'évaluation

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142D'EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142Pas encore d'évaluation

- On-Chip Electro-Static Discharge (ESD) Protection for Radio-Frequency Integrated CircuitsD'EverandOn-Chip Electro-Static Discharge (ESD) Protection for Radio-Frequency Integrated CircuitsPas encore d'évaluation

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsD'EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsPas encore d'évaluation

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysD'EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysPas encore d'évaluation

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionD'EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionPas encore d'évaluation

- Instrumentation and Test Gear Circuits ManualD'EverandInstrumentation and Test Gear Circuits ManualÉvaluation : 5 sur 5 étoiles5/5 (1)

- Marine Electrical Practice: Marine Engineering SeriesD'EverandMarine Electrical Practice: Marine Engineering SeriesÉvaluation : 4 sur 5 étoiles4/5 (8)

- Substation Automation Systems: Design and ImplementationD'EverandSubstation Automation Systems: Design and ImplementationÉvaluation : 4.5 sur 5 étoiles4.5/5 (3)

- Quizz 4Document34 pagesQuizz 4diegogasca275Pas encore d'évaluation

- Ltc-Li-R2-020 (Procedure For Losystem - Final - TKG)Document4 pagesLtc-Li-R2-020 (Procedure For Losystem - Final - TKG)ratheeshPas encore d'évaluation

- How To Remove Nickel Oxide: Flow Cell - To Increase The Fluid DynamicsDocument2 pagesHow To Remove Nickel Oxide: Flow Cell - To Increase The Fluid DynamicsGeetha ThiruvengadamPas encore d'évaluation

- Vda de REcinto V InciongDocument5 pagesVda de REcinto V InciongEnma KozatoPas encore d'évaluation

- Revue Technique Hyndai I10Document147 pagesRevue Technique Hyndai I10ossoski100% (5)

- Gathering Information and Scanning The Environment: Marketing Management, 13 EdDocument23 pagesGathering Information and Scanning The Environment: Marketing Management, 13 EdSaket JanglePas encore d'évaluation

- Process Safety KPIsDocument2 pagesProcess Safety KPIssheerazali100% (1)

- Opencv: Object Classification - in The Object Classification, We Train A Model On A Dataset ofDocument9 pagesOpencv: Object Classification - in The Object Classification, We Train A Model On A Dataset ofSrinadh ShaikPas encore d'évaluation

- MW3 HT vs. PowerDocument5 pagesMW3 HT vs. Powergerencia procesos especialesPas encore d'évaluation

- Field Modules: Specifications DescriptionDocument2 pagesField Modules: Specifications DescriptionjorgemalagaPas encore d'évaluation

- Portea Home Health CareDocument17 pagesPortea Home Health CareAbhai Pratap SinghPas encore d'évaluation

- Heating curve graph for benzeneDocument2 pagesHeating curve graph for benzeneBluematwo TwoPas encore d'évaluation

- Cplus Steepds CPPDocument3 pagesCplus Steepds CPPshyamPas encore d'évaluation

- UTSA 15-17 GraduateCatalogDocument336 pagesUTSA 15-17 GraduateCatalogSandeep AyyagariPas encore d'évaluation

- DD311 40Document154 pagesDD311 40luis naupari100% (1)

- Passage PlanDocument4 pagesPassage Plan16 - Aniruth100% (1)

- Van Ginneken Laurenz - CVDocument1 pageVan Ginneken Laurenz - CVDanica VihinenPas encore d'évaluation

- Manage Multiple Businesses with Nimble AccountingDocument16 pagesManage Multiple Businesses with Nimble AccountingWalter De la CruzPas encore d'évaluation

- Ecommerce Opportunity Tracking SheetDocument6 pagesEcommerce Opportunity Tracking SheetdeepakPas encore d'évaluation

- R7210501 Probability & StatisticsDocument2 pagesR7210501 Probability & StatisticssivabharathamurthyPas encore d'évaluation

- List of Premier Green Building ConsultantsDocument4 pagesList of Premier Green Building ConsultantsJahanvi ModiPas encore d'évaluation

- Competency Statement NEO PUFF - ANSWERS-1Document2 pagesCompetency Statement NEO PUFF - ANSWERS-1madimadi11Pas encore d'évaluation

- 01-NAC-Introduction To Ship Stability (160419)Document40 pages01-NAC-Introduction To Ship Stability (160419)MuhammadIlhamNugroho100% (1)

- Shield Type S A-RB Realizes Further Spool-Free!Document36 pagesShield Type S A-RB Realizes Further Spool-Free!Masauso Lungu100% (1)

- CIMPMALAYSIADocument10 pagesCIMPMALAYSIAEpahPas encore d'évaluation

- Elliott Wave Guide to Pattern Recognition and Fibonacci ApplicationsDocument55 pagesElliott Wave Guide to Pattern Recognition and Fibonacci ApplicationsAM PM100% (1)

- The Elliott Wave PrincipleDocument4 pagesThe Elliott Wave PrincipledewanibipinPas encore d'évaluation

- Symmetry: SIAT: A Distributed Video Analytics Framework For Intelligent Video SurveillanceDocument20 pagesSymmetry: SIAT: A Distributed Video Analytics Framework For Intelligent Video SurveillanceData LOG NGUYENPas encore d'évaluation

- Kinetika Kimia: Bambang WidionoDocument77 pagesKinetika Kimia: Bambang WidionoFardaawPas encore d'évaluation

- Kolsterising (Bodycote)Document4 pagesKolsterising (Bodycote)Scott KramerPas encore d'évaluation