Académique Documents

Professionnel Documents

Culture Documents

Gujarat Technological University: Instructions

Transféré par

Pritesh SaxenaTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Gujarat Technological University: Instructions

Transféré par

Pritesh SaxenaDroits d'auteur :

Formats disponibles

Seat No.

: ________

Enrolment No.______________

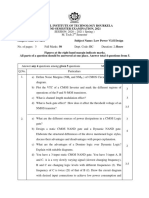

GUJARAT TECHNOLOGICAL UNIVERSITY

M. E. - SEMESTER II EXAMINATION SUMMER 2014

Subject code: 1710412

Subject Name: Digital VLSI Design

Time: 02:30 pm - 05:00 pm

Date: 23-06-2014

Total Marks: 70

Instructions:

1. Attempt all questions.

2. Make suitable assumptions wherever necessary.

3. Figures to the right indicate full marks.

Q.1

(a)

(b)

(c)

(d)

(e)

(f)

(g)

Q.2

(a)

(b)

(b)

Q.3

(a)

(b)

Q.3

(a)

Answer the following questions (Two marks each)

Discuss crosstalk and its implications.

Compare static and dynamic circuit for size, power dissipation and speed of

operation.

Write equation for CMOS channel charge.

Why CMOS is preferred compared to BJT in Digital VLSI design?

Why CMOS flip-flops prefer non-overlapping clocks?

What do you mean by Pseudo gate?

For Circuit shown in figure below, find path logical effort and Path Electrical

effort.

14

Show internal diagram of MOS transistor and explain calculation of gate

capacitance. With diagram show variation of the gate capacitances as functions

of gate-to-source voltage VGS

Derive the drain current equation for MOSFET using Gradual Channel

Approximation (GCA).

OR

State importance of Power-Delay Product and explain with necessary

equations.

07

With appropriate diagram discuss types of photoresists and their usage in

lithography process.

Consider 5mm long, 0.32m wide metal2 wire in 180nm process. The sheet

resistance is 0.05W/ and the capacitance is 0.2fF/m. Estimate resistance and

capacitance of the wire and construct a 3-segment p-model for the wire. A 10x

unit-sized inverter drives a 2x inverter at the end of the 5mm wire. The gate

capacitance is C = 2fF/m and the effective resistance is R = 2.5KW m for

NMOS transistors. Neglect diffusion capacitance. Estimate the propagation

delay using Elmore delay model.

OR

With appropriate diagram explain how CMOS inverter is fabricated on plain

substrate.

07

07

07

07

07

Q.4

(b)

Sketch 2 input NOR gate with transistor widths chosen to achieve effective rise

and fall resistance equal to a unit inverter. Compute the rising and falling

propagation delays in terms of R and C of the NOR gate driving h identical

NOR gates using Elmore delay model. If C = 2fF/m and R = 2.5KW m in a

180nm process, what is the delay of fanout-of-4 NOR gate?

07

(a)

Derive critical voltages for CMOS inverter and find ratio of W/L for

symmetrical inverter.

Draw and compare 1-bit full adder circuit using CMOS compound gate and

CMOS transmission gate. Illustrate which mechanism will use less number of

transistors.

07

(b)

07

OR

Q.4

(a)

(b)

Q.5

(a)

(b)

Q.5

(a)

(b)

For depletion load inverter circuit, discuss noise margin with transfer

characteristic.

Draw MOS transistor level schematic and explain operation of D Latch as well

D Flip-flop with waveforms.

07

Explain concept of precharge and evaluate for dynamic logic circuit.

What is feature size and l? Explain Layout design rules in terms of l.

OR

Write short note on NORA CMOS logic.

Draw Circuit diagram and stick diagram for following boolean function

07

07

07

07

07

(i) Y = AB + C

(ii) Y = ABC

*************

Vous aimerez peut-être aussi

- Power Systems-On-Chip: Practical Aspects of DesignD'EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardPas encore d'évaluation

- r05410207 Vlsi DesignDocument7 pagesr05410207 Vlsi Design9010469071Pas encore d'évaluation

- Gujarat Technological University: InstructionsDocument2 pagesGujarat Technological University: InstructionsArchana TrivediPas encore d'évaluation

- Question Bank Fundamentals of CMOS VLSI-10EC56 15-16Document10 pagesQuestion Bank Fundamentals of CMOS VLSI-10EC56 15-16Pranav KpPas encore d'évaluation

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityPalak AriwalaPas encore d'évaluation

- EC2354 - Nov 2011 - AU QP Anna University Exams - VLSIDocument3 pagesEC2354 - Nov 2011 - AU QP Anna University Exams - VLSISHARANYAPas encore d'évaluation

- Unit 5 QBDocument11 pagesUnit 5 QBAMAN SRIVASTAVA (RA2011030010057)Pas encore d'évaluation

- 18EC42 First IA Test Q-PaperDocument2 pages18EC42 First IA Test Q-PapersharanbasappaPas encore d'évaluation

- Previous PapersDocument12 pagesPrevious PapersKaran SanaPas encore d'évaluation

- VLSIDesignDocument5 pagesVLSIDesignVenkatesh KolatiPas encore d'évaluation

- VHDL MCQDocument18 pagesVHDL MCQtoshit jain100% (1)

- SANDISKDocument3 pagesSANDISKrAM100% (3)

- Previous Question PapersDocument4 pagesPrevious Question Papersshaker423Pas encore d'évaluation

- Use The Process Data Given at The End of The Exam Sheet For All ProblemsDocument4 pagesUse The Process Data Given at The End of The Exam Sheet For All ProblemsBasem Abd ElazizPas encore d'évaluation

- EE 577A Spring 2022 - VLSI System Design Homework 1: TH TH THDocument4 pagesEE 577A Spring 2022 - VLSI System Design Homework 1: TH TH THvedeshPas encore d'évaluation

- General Digital Design Questions: How Do You Size NMOS and PMOS Transistors To Increase The Threshold Voltage?Document22 pagesGeneral Digital Design Questions: How Do You Size NMOS and PMOS Transistors To Increase The Threshold Voltage?Rahul VaddelliPas encore d'évaluation

- EVL562 ECL523 Digital IC Design Dec2020Document3 pagesEVL562 ECL523 Digital IC Design Dec2020akash rawatPas encore d'évaluation

- Design of Folded Cascode OTA in Different Regions of Operation Through gmID Methodology PDFDocument6 pagesDesign of Folded Cascode OTA in Different Regions of Operation Through gmID Methodology PDFAyush MalhotraPas encore d'évaluation

- Assignment Questions ECE VLSI NITTDocument6 pagesAssignment Questions ECE VLSI NITTAkhilGovindPas encore d'évaluation

- Jntu MDocument3 pagesJntu MVijay SagarPas encore d'évaluation

- R09-Cmos Analog and Mixed Signal DesignDocument2 pagesR09-Cmos Analog and Mixed Signal DesignbalashyamuPas encore d'évaluation

- Q Paper 09ec61 May June 2012Document2 pagesQ Paper 09ec61 May June 2012Bhaskar MishraPas encore d'évaluation

- Two Stage OpampDocument17 pagesTwo Stage OpampMac YuPas encore d'évaluation

- AnalogDocument8 pagesAnalogAhmed F RahimPas encore d'évaluation

- Linear Integrated Circuit Ques PaperDocument2 pagesLinear Integrated Circuit Ques PaperABHISHEK JHAPas encore d'évaluation

- MJ12 PDFDocument6 pagesMJ12 PDFSarika VadivelanPas encore d'évaluation

- Vlsi Design: III B. Tech II Semester Regular Examinations, April/May - 2019Document4 pagesVlsi Design: III B. Tech II Semester Regular Examinations, April/May - 2019pawan100% (1)

- Homework 1 EE 240b Advanced Analog CircuitsDocument2 pagesHomework 1 EE 240b Advanced Analog Circuitsb98154Pas encore d'évaluation

- Design of Folded Cascode OTA in Different Regions of Operation Through G /I MethodologyDocument6 pagesDesign of Folded Cascode OTA in Different Regions of Operation Through G /I MethodologyPramod SrinivasanPas encore d'évaluation

- 2023 Midterm PapersDocument5 pages2023 Midterm Papers40 XII-B Satyam SinhaPas encore d'évaluation

- Ae Paper GtuDocument9 pagesAe Paper GtuMehta HarshPas encore d'évaluation

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityPalak AriwalaPas encore d'évaluation

- VLSI Design 2010 Sept CUSATDocument1 pageVLSI Design 2010 Sept CUSATvineethvrr5948Pas encore d'évaluation

- National Institute of Technology Rourkela End Semester Examination, 2021Document3 pagesNational Institute of Technology Rourkela End Semester Examination, 2021ajay vermaPas encore d'évaluation

- Vlsi Design April 2019Document4 pagesVlsi Design April 2019RakeshPas encore d'évaluation

- SEPTEMBERDocument3 pagesSEPTEMBERRocky BobeePas encore d'évaluation

- Vlsi Design: Time: 3 Hours Total Marks: 100Document4 pagesVlsi Design: Time: 3 Hours Total Marks: 100Shivani VarshneyPas encore d'évaluation

- VLSI Design Overview ProblemsDocument4 pagesVLSI Design Overview ProblemsJorge Ivan Canales VerdialPas encore d'évaluation

- Ec 303Document2 pagesEc 303jeetendrasidhiPas encore d'évaluation

- Pulse and Digital CircuitsDocument8 pagesPulse and Digital CircuitsKota divyasreePas encore d'évaluation

- Cmos Comparator ThesisDocument5 pagesCmos Comparator Thesisannemarieolathe100% (1)

- Exercise 2Document3 pagesExercise 2momolololilo4Pas encore d'évaluation

- Dec 2009Document8 pagesDec 2009Viswa ChaitanyaPas encore d'évaluation

- Jntu Vlsi Systems DesignDocument5 pagesJntu Vlsi Systems Design9010469071Pas encore d'évaluation

- A1429 VlsiDocument8 pagesA1429 VlsiratnamsPas encore d'évaluation

- Design of High Performance Dynamic CMOS Circuits in Deep Submicron TechnologyDocument15 pagesDesign of High Performance Dynamic CMOS Circuits in Deep Submicron TechnologyEeshwar Ram JPas encore d'évaluation

- Vlsi Mod3 QnADocument24 pagesVlsi Mod3 QnAsri krishnaPas encore d'évaluation

- h3 f06 PDFDocument5 pagesh3 f06 PDFDevaraj SubrmanayamPas encore d'évaluation

- R7220203 Linear Digital IC ApplicationsDocument2 pagesR7220203 Linear Digital IC ApplicationssivabharathamurthyPas encore d'évaluation

- VLSI RamDocument18 pagesVLSI RamrAM100% (4)

- Op Amp PaperDocument6 pagesOp Amp PaperSrinivasu IrlapatiPas encore d'évaluation

- VLSI DESIGN Question Bank: Unit 1Document12 pagesVLSI DESIGN Question Bank: Unit 1Babu GundlapallyPas encore d'évaluation

- Btech Ee 6 Sem Conventional and Cad of Electrical Machines Nee 023 2016 17Document2 pagesBtech Ee 6 Sem Conventional and Cad of Electrical Machines Nee 023 2016 17Tanisha ShahPas encore d'évaluation

- PVT-Invariant Single-to-Differential Data ConverterDocument4 pagesPVT-Invariant Single-to-Differential Data ConverteryvarshneyPas encore d'évaluation

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionD'EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionPas encore d'évaluation

- High-Performance D/A-Converters: Application to Digital TransceiversD'EverandHigh-Performance D/A-Converters: Application to Digital TransceiversPas encore d'évaluation

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyD'EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyPas encore d'évaluation

- Heterojunction Bipolar Transistors for Circuit Design: Microwave Modeling and Parameter ExtractionD'EverandHeterojunction Bipolar Transistors for Circuit Design: Microwave Modeling and Parameter ExtractionPas encore d'évaluation

- Enabling Technologies for High Spectral-efficiency Coherent Optical Communication NetworksD'EverandEnabling Technologies for High Spectral-efficiency Coherent Optical Communication NetworksPas encore d'évaluation

- AGC-4 Operator's Manual DU-2Document24 pagesAGC-4 Operator's Manual DU-2Delio DuranPas encore d'évaluation

- LPG For Heavy Duty Engines 2017Document116 pagesLPG For Heavy Duty Engines 2017Neagoie SergiuPas encore d'évaluation

- A New Three-Phase Power-Factor Correction (PFC)Document8 pagesA New Three-Phase Power-Factor Correction (PFC)Satya NVPas encore d'évaluation

- Control Properties: Visual ControlsDocument4 pagesControl Properties: Visual Controlssterik alertPas encore d'évaluation

- Catalog Motoare NavaleDocument164 pagesCatalog Motoare NavaleOvidiu Papuc100% (1)

- Detection of Hidden ObjectsDocument23 pagesDetection of Hidden ObjectsJeeva JeevaPas encore d'évaluation

- 00 Cockpit DoorDocument18 pages00 Cockpit DoorKıvanc Terzioglu100% (1)

- Vss Cheat SheetDocument1 pageVss Cheat SheetPiyush BhateePas encore d'évaluation

- How Does A MOOG Servo Valve OperatesDocument5 pagesHow Does A MOOG Servo Valve OperatesMikoto Rifky100% (1)

- AV100 Service Manual EnglishDocument18 pagesAV100 Service Manual EnglishvovchickPas encore d'évaluation

- Data Structure Unit 3 PPT Cs 3rd WKDocument22 pagesData Structure Unit 3 PPT Cs 3rd WKHirut GetachewPas encore d'évaluation

- Brewery Automation: BREE 495 Ian Burelle 260 472 128Document41 pagesBrewery Automation: BREE 495 Ian Burelle 260 472 128Fotonika ITSPas encore d'évaluation

- Alcatel 3G ModemDocument15 pagesAlcatel 3G ModembunaciunePas encore d'évaluation

- EC8652 - Wireless Communication (Ripped From Amazon Kindle Ebooks by Sai Seena)Document466 pagesEC8652 - Wireless Communication (Ripped From Amazon Kindle Ebooks by Sai Seena)Iniyan VenkatesanPas encore d'évaluation

- Practical Java Machine LearningDocument46 pagesPractical Java Machine Learningeazpil01Pas encore d'évaluation

- DCS400 Service Manual PDFDocument70 pagesDCS400 Service Manual PDFDoDuyBacPas encore d'évaluation

- Sri Krishna Arts and Science College Coimbatore - 641 008 PG - II Semester - End Semester Examinations - Time Table (June 2021) CE 07Document5 pagesSri Krishna Arts and Science College Coimbatore - 641 008 PG - II Semester - End Semester Examinations - Time Table (June 2021) CE 07VishwakPas encore d'évaluation

- Harnessing The Power of IoTDocument50 pagesHarnessing The Power of IoTMazlan AbbasPas encore d'évaluation

- Automotive Quality High-Power: Stanley Electric's Latest High-Power IR LEDDocument1 pageAutomotive Quality High-Power: Stanley Electric's Latest High-Power IR LEDbobbbPas encore d'évaluation

- Acura CD Changer PinoutDocument10 pagesAcura CD Changer PinoutcenjibaPas encore d'évaluation

- Gatic Slotdrain PDFDocument35 pagesGatic Slotdrain PDFshugd310850% (1)

- 9.1.1.6 Lab - Encrypting and Decrypting Data Using OpenSSL - ILM EstudantesDocument3 pages9.1.1.6 Lab - Encrypting and Decrypting Data Using OpenSSL - ILM EstudantesJosé Silvestre da Silva GalvãoPas encore d'évaluation

- Windows Defender ATP - Ransomware Response PlaybookDocument19 pagesWindows Defender ATP - Ransomware Response PlaybookVicente ArellanoPas encore d'évaluation

- Kota Krishna Chaitanya - ResumeDocument4 pagesKota Krishna Chaitanya - Resumexiaomi giaPas encore d'évaluation

- Imagerunner Advance 8205Document264 pagesImagerunner Advance 8205Gerardo SaucedaPas encore d'évaluation

- Wollensak T-1500 PDFDocument33 pagesWollensak T-1500 PDFFRANK NIELE DE OLIVEIRAPas encore d'évaluation

- Control S Lec 1-11Document11 pagesControl S Lec 1-11Aloysious Aries GonzagaPas encore d'évaluation

- LM1815 Adaptive Variable Reluctance Sensor Amplifier: Features DescriptionDocument18 pagesLM1815 Adaptive Variable Reluctance Sensor Amplifier: Features DescriptiondangthutqmPas encore d'évaluation

- Datasheet - HK Pcf7991at 450658Document1 pageDatasheet - HK Pcf7991at 450658Adrian FernandezPas encore d'évaluation

- Data Science EssayDocument2 pagesData Science EssayAbdelhak100% (1)