Académique Documents

Professionnel Documents

Culture Documents

Linear and Digital Ic Lab 2011-12 (KTM & NS)

Transféré par

sureshTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Linear and Digital Ic Lab 2011-12 (KTM & NS)

Transféré par

sureshDroits d'auteur :

Formats disponibles

Department of Electrical and Electronics Engineering

LABORATORY MANUAL

LINEAR AND DIGITAL INTEGRATED CIRCUITS

LABORATORY

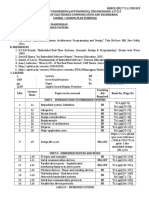

LINEAR AND DIGITAL IC LABORATORY

S. NO.

NAME OF THE EXPERIMENT

Page No.

1.a

STUDY OF LOGIC GATES

03

1.b

STUDY OF FLIP FLOPS

07

2.

ADDERS, SUBTRACTORS AND REDUCTION OF A BOOLEAN

EXPRESSION USING KARNAUGH MAP

12

3.a

CODE CONVERTERS, ODD PARITY GENERATOR AND ODD

PARITY CHECKER

18

3.b

STUDY OF ENCODERS AND DECODERS

23

DESIGN AND IMPLENTATION OF 4-BIT MODULO

4.

5.

COUNTERS

DESIGN AND IMPLEMENTATION OF 4-BIT SHIFT

REGISTERS

27

34

STUDY AND DESIGN OF 4 :1 & 8 :1 MULTIPLEXER AND

6.

DEMULTIPLEXER

54

7.

MONOSTABLE AND ASTABLE MULTIVIBRATOR USING 555

TIMER

59

8.

APPLICATIONS OF OPERATIONAL AMPLIFIERS

68

9.a

DIGITAL TO ANALOG CONVERTER

82

9.b

ANALOG TO DIGITAL CONVERTER

88

VOLTAGE TO FREQUENCY CHARACTERISTICS OF

10.a

10.b

NE/SE 566 IC

FREQUENCY MULTIPLICATION USING NE/SE 565 PLL IC

http://annauniversitystudymaterials.blogspot.in/

94

100

Page 2

LINEAR AND DIGITAL IC LABORATORY

Experiment: 1.a

STUDY OF LOGIC GATES

Aim:

To study the truth tables of various logic gates and verify them experimentally

using appropriate integrated circuits.

Apparatus Required:

S.No

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12

Component Name

AND Gate

OR Gate

NOT Gate

NAND Gate

NOR Gate

EXOR Gate

EXNOR Gate

Bread Board

Light Emitting Diodes

Connecting wires

Regulated Power supply

Current Limiting Resistor

Part No/Range

IC 7408

IC 7432

IC 7404

IC 7400

IC 7402

IC 7486

IC 4077

(0-30V)

330 ohm

Quantity in Nos

1

1

1

1

1

1

1

1

As Req.

As Req.

1

As Req.

Theory:

The logic gates are the basic building blocks of digital systems. A logic gate

produces an output level depending upon the input levels present at that instant. The

functionality of any logic gate can be explained by the corresponding truth table and

logical expression. Both NAND and NOR gates can perform all the three basic logic

functions (AND, OR and NOT), so they are called as Universal gates.

AND Gate Truth Table

http://annauniversitystudymaterials.blogspot.in/

IC7408 AND Gate

Page 3

LINEAR AND DIGITAL IC LABORATORY

OR Gate Truth Table

IC7432 OR Gate

NOR Gate Truth Table

IC7402 NOR Gate

NAND Gate Truth Table

IC7400 NAND Gate

http://annauniversitystudymaterials.blogspot.in/

Page 4

LINEAR AND DIGITAL IC LABORATORY

XOR Gate Truth Table

IC7486 XOR Gate

XNOR Gate Truth Table

IC4077 XNOR Gate

NOT Gate Truth Table

IC7404 NOT Gate

http://annauniversitystudymaterials.blogspot.in/

Page 5

LINEAR AND DIGITAL IC LABORATORY

Procedure:

1. Connections are made as shown in the wiring diagram.

2. The input logic levels are applied from D.C. power supply and the corresponding

output logic level is checked through an LED.

3. All possible input combinations and their corresponding outputs as per the truth

table, are verified.

http://annauniversitystudymaterials.blogspot.in/

Page 6

LINEAR AND DIGITAL IC LABORATORY

Experiment: 1.b

STUDY OF FLIP FLOPS

Aim:

To study the truth tables of various flip flops and verify them experimentally

using appropriate integrated circuits.

Apparatus Required:

S.No

1.

2.

3.

4.

5.

6.

7.

8.

9.

Component Name

OR Gate

NOT Gate

NAND Gate

NOR Gate

Bread Board

Light Emitting Diodes

Connecting wires

Regulated Power supply

Current Limiting Resistor

Part No/Range

IC 7432

IC 7404

IC 7400

IC 7402

(0-30V)

330 ohm

Quantity in Nos

1

1

1

1

1

As Req.

As Req.

1

As Req.

Theory:

S-R Flip-flop:

The output Q is called the state of the flip-flop

S=1, R=0 Sets the state to 1

S=0, R=1 Resets (or Clears) the state to 0

S=0, R=0 is the Hold state

S=1, R=1 is not allowed

SR Flip-Flop- Excitation Table

http://annauniversitystudymaterials.blogspot.in/

Truth Table

Page 7

LINEAR AND DIGITAL IC LABORATORY

Because the 11 input will not be allowed, the result is a dont care, and Q = S + Rq. This

is the characteristic equation for an S-R flip-flop.

D Flip-flop:

When CLK = 0, the flip-flop holds

When CLK = 1

D q

0 0

1 0

0 1

1 1

Characteristic Equation: Q = D

D Flip-Flop-Excitation Table

D Flip-Flop-Truth Table

http://annauniversitystudymaterials.blogspot.in/

Page 8

LINEAR AND DIGITAL IC LABORATORY

J-K Flip-flop

If J and K are different then the output Q takes the value of J at the next clock

edge.

If J and K are both low then no change occurs. If J and K are both high at the

clock edge then the output will toggle from one state to the other.

Characteristic Equation

Q = Jq + Kq

http://annauniversitystudymaterials.blogspot.in/

Page 9

LINEAR AND DIGITAL IC LABORATORY

JK Flip-Flop Excitation Table

Truth Table:

T Flip-flop:

The T or "toggle" flip-flop changes its output on each clock edge, giving an

output which is half the frequency of the signal to the T input.

http://annauniversitystudymaterials.blogspot.in/

Page 10

LINEAR AND DIGITAL IC LABORATORY

T Flip-Flop Excitation Table

Truth Table

Characteristic Equation

Q = Tq + Tq

Procedure:

1. Connections are made as shown in the logic diagram.

2. The input clock pulse are applied from digital trainer and the corresponding output

logic levels are checked through LEDs.

3. The workings of flip-flops are verified using truth table.

Inference:

Result:

Viva Questions:

1. What is mean by flip flop?

2. What is the difference between flip flops and latches?

http://annauniversitystudymaterials.blogspot.in/

Page 11

LINEAR AND DIGITAL IC LABORATORY

3.

4.

5.

6.

7.

8.

What is mean by edge triggered and level triggered flipflop?

What is the characteristic equation for JKFF?

What is mean by setup time and hold time?

What are the applications of flip flops?

What is the 1's and 2's complement of the decimal number 25?

What types of flip-flops can be used to implement the memory elements of a

counter?

9. How is a J-K flip-flop made to toggle?

10. The term hold always means ________.

Experiment: 2

ADDERS, SUBTRACTORS AND REDUCTION OF A BOOLEAN EXPRESSION

USING KARNAUGH MAP

Aim:

To design, construct and test the following digital circuits;

1. Half-adder

2. Full-adder

3. Half-subtractor

4. Full-subtractor and to reduce the given Boolean expression using a Karnaugh

map, implement the reduced expression and test the same.

Apparatus Required:

S.No

1.

2.

3.

4.

5.

6.

7.

8.

9.

Component Name

AND Gate

OR Gate

NOT Gate

EXOR Gate

Bread Board

Light Emitting Diodes

Connecting wires

Regulated Power supply

Current Limiting Resistor

Part No/Range

IC 7408

IC 7432

IC 7404

IC 7486

(0-30V)

330 ohm

Quantity in Nos

1

1

1

1

1

As Req.

As Req.

1

As Req.

Theory:

http://annauniversitystudymaterials.blogspot.in/

Page 12

LINEAR AND DIGITAL IC LABORATORY

Adders and subtractors are part of digital arithmetic circuits that perform

arithmetic operations. An adder is a digital circuit that adds two bits and a carry and

outputs a sum bit and carry bit. A subtractor, subtracts the subtrahend bit from the

minuend bit, considering the borrow due to previous subtraction and outputs difference

bit and borrow bit. A Half-adder will not consider the carry obtained from preceding

addition and can be used only for LSB addition. Similarly a half-subtractor can be used

only for LSB subtraction, since the borrow obtained from preceding subtraction is not

considered.

Design Methodology:

The required circuits are designed using appropriate truth tables. Each output is

expressed as a Boolean algebraic function of all the inputs. The obtained logical

expressions for each of the outputs are reduced using either Karnaugh maps or Boolean

laws.

Karnaugh map:

Karnaugh map is a chart, composed of an arrangement of adjacent cells, each

representing a particular combination of variables in sum or product form. K-map

provides a simple, systematic method of simplifying a Boolean expression, without

changing the functionality of the expression. The simplification leads to reduction in

number of gate inputs during implementation.

Half Adder:

S(X, Y) = (1, 2)

S=X'Y+XY'

S= X Y

CARRY(X, Y) = (3)

CARRY=XY

Circuit

http://annauniversitystudymaterials.blogspot.in/

Truth Table

Page 13

LINEAR AND DIGITAL IC LABORATORY

K MAP

Full Adder:

S(X, Y, Z) = (1, 2, 3)

SUM(X,Y,Z) = X'Y'Z + XY'Z' + X'YZ' + XYZ

S= X Y Z

CARRY(X, Y, Z) = (7)

CARRY= XY + XZ + YZ

Circuit:

Truth Table

X

0

0

0

0

1

Y

0

0

1

1

0

Z

0

1

0

1

0

SUM

0

1

1

0

1

http://annauniversitystudymaterials.blogspot.in/

CARRY

0

0

0

1

0

Page 14

LINEAR AND DIGITAL IC LABORATORY

1

1

1

0

1

1

1

0

1

0

0

1

1

1

1

K MAP

Half Subtractor:

K MAP

Full Subtractor

Circuit

http://annauniversitystudymaterials.blogspot.in/

Page 15

LINEAR AND DIGITAL IC LABORATORY

Truth Table

X

0

0

0

0

1

1

1

1

Y

0

0

1

1

0

0

1

1

Z

0

1

0

1

0

1

0

1

Difference

0

1

1

0

1

0

0

1

Borrow

0

1

1

1

0

0

0

1

K MAP

http://annauniversitystudymaterials.blogspot.in/

Page 16

LINEAR AND DIGITAL IC LABORATORY

Procedure:

1. Connections are made as shown in the logic diagram.

2. The input logic levels are applied from D.C. power supply and the corresponding

output logic levels are checked through LEDs.

3. For adders and subtractors, all possible input combinations and their corresponding

outputs as per their truth tables are verified.

4. The given Boolean expression is entered in an appropriate K-map. Groups are formed

such that all the entries are covered. Equivalent terms representing each group is written

to obtain the simplified expression.

5. Step 4 operations are repeated for the canonical form representation of the given

expression and the simplified expression is obtained.

6. The simplified expressions obtained from step4 and steps 5 are compared for total

number of gate inputs. The expression with minimum number of gate inputs is

implemented using AND, OR and NOT gates and the truth table is verified.

http://annauniversitystudymaterials.blogspot.in/

Page 17

LINEAR AND DIGITAL IC LABORATORY

Inference:

Result:

Viva Questions:

1.

2.

3.

4.

5.

6.

7.

8.

What is mean by half adder?

What is mean by full adder?

What is mean by parallel adder?

What is mean by carry lookahead adder?

What is mean by ripple carry adder?

What is mean by parallel binary adder?

What are the different types of adder implementation?

Realize the functions of NOT, AND, OR and NAND gates only with NOR

gates.

9. Reduce the following using tabulation method.

F = m2 + m3 + m4 + m6 + m7 +m9 + m11 + m13.

10. List out the differences between half adder and full adder.

Experiment: 3(a)

CODE CONVERTERS, ODD PARITY GENERATOR AND ODD PARITY

CHECKER

Aim:

To design, construct and test the following digital circuits;

1.

Gray to Binary code converter

2.

Binary to gray code converter

3.

4-Bit Odd Parity Generator and

4.

4-Bit Odd Parity Checker

Apparatus Required

S.No

1.

2.

3.

4.

Component Name

Not Gate

EXOR Gate

Bread Board

Light Emitting Diodes

Part No/Range

IC 7404

IC 7486

-

http://annauniversitystudymaterials.blogspot.in/

Quantity in Nos

1

2

1

As Req.

Page 18

LINEAR AND DIGITAL IC LABORATORY

5.

6.

7.

Connecting wires

Regulated Power supply

Current Limiting Resister

(0-30V)

330 ohm

As Req.

1

As Req.

Theory:

Code Converter:

Code converters are logic circuits whose inputs are bit patterns representing

numbers or characters in one code and whose outputs are their corresponding

representations in a different code.

Gray Code:

It is a non-weighted code used in instrumentation and data acquisition systems,

where linear or angular displacement is measured and converted into equivalent digital

values. Gray code is an unit-distance code because successive code words in this code

differ by only one bit position.

Parity Generator and Parity Checker:

When binary data is transmitted, it is susceptible to noise that can alter or distort

its contents. The simplest technique for detecting single-bit errors is that of adding an

extra bit, known as the parity bit, to each word being transmitted. There are two types of

parity odd parity and even parity. For odd parity, the parity bit is set to a 1 at the

transmitter such that the total number of 1 bits in the word including the parity bit is an

odd number. When the digital data is received, the parity checking circuit generates an

error signal if the total number of 1 bits is even in an odd-parity system.

Design Methodology:

The required circuits are designed using appropriate truth tables. Each output is

expressed as a Boolean algebraic function of all the inputs. The obtained logical

expressions for each of the outputs are reduced using either Karnaugh maps or Boolean

laws.

Binary to Gray Converter:

http://annauniversitystudymaterials.blogspot.in/

Page 19

LINEAR AND DIGITAL IC LABORATORY

Gray to Binary Converter:

Four Bit Odd Parity Generator:

http://annauniversitystudymaterials.blogspot.in/

Page 20

LINEAR AND DIGITAL IC LABORATORY

Four Bit Odd Parity Checker:

Gray to Binary Code Conversion Table:

http://annauniversitystudymaterials.blogspot.in/

Page 21

LINEAR AND DIGITAL IC LABORATORY

Procedure

http://annauniversitystudymaterials.blogspot.in/

Page 22

LINEAR AND DIGITAL IC LABORATORY

1. Connections are made as shown in the logic diagram.

2. The input logic levels are applied from D.C. power supply and the corresponding

output logic levels are checked through LEDs.

3. For the first three circuits all possible input combinations and their corresponding

outputs as per their truth tables are verified.

4. For a 4-bit odd parity checker, the error conditions are simulated and appropriate

observations are made for three different cases.

Experiment: 3(b)

http://annauniversitystudymaterials.blogspot.in/

Page 23

LINEAR AND DIGITAL IC LABORATORY

STUDY OF ENCODERS AND DECODERS

Aim:

To design

1. 8:3 Encoder

2. 3:8 Decoder

Apparatus Required:

S.No

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

Component Name

AND Gate

OR Gate

Not Gate

NAND Gate

NOR Gate

Bread Board

Light Emitting Diodes

Connecting wires

Regulated Power supply

Current Limiting Resister

Part No/Range

IC 7408

IC 7432

IC 7404

IC 7400

IC 7402

(0-30V)

330 ohm

Quantity in Nos

1

1

1

1

1

1

As Req.

As Req.

1

As Req.

Theory:

Encoder:

An encoder is a digital circuit that performs the inverse operation of a decoder.

An encoder has 2n input lines and n output lines. The output lines generate the binary

equivalent of the input line whose value is 1.At any one time, only one input line has a

value of 1. The figure below shows the truth table of an 8:3 encoder. It has got 8 inputs

and 3 outputs.

http://annauniversitystudymaterials.blogspot.in/

Page 24

LINEAR AND DIGITAL IC LABORATORY

Circuit Diagram:

Truth Table of 8:3 Encoder

Decoder:

It is a logic circuit that converts an n bit binary input code into m bit output

line activated such that any one is selected for each one of possible combination of

inputs.

http://annauniversitystudymaterials.blogspot.in/

Page 25

LINEAR AND DIGITAL IC LABORATORY

http://annauniversitystudymaterials.blogspot.in/

Page 26

LINEAR AND DIGITAL IC LABORATORY

Procedure

1. Connections are made as shown in the logic diagram.

2. The input clock pulse are applied from digital trainer and the corresponding output

logic levels are checked through LEDs.

3. The working of decoding and encoding are verified for proper operation.

Inference:

Result:

Viva Questions:

1. What is mean by encoder?

2. What is mean by decoder?

3. How does an encoder differ from decoder?

4. What is mean by odd and even parity? Is mean by counter?

5. What are the applications of decoder?

6. What is mean by priority encoder?

7. Convert the decimal 65 to BCD, Excess-3 and Gray code.

8. What are codes? List the different codes with examples.

9. Which digital system translates coded characters into a more useful form?

10. A BCD decoder will have how many rows in its truth table?

http://annauniversitystudymaterials.blogspot.in/

Page 27

LINEAR AND DIGITAL IC LABORATORY

Experiment: 4

DESIGN AND IMPLENTATION OF 4-BIT MODULO COUNTERS

Aim:

To design, construct and test the following types of counters

1.

Synchronous counter Mod 6

2.

Synchronous 4-Bit Binary Counter

3.

Asynchronous 4 Bit Binary Counter

4.

Asynchronous Decade Counters

Apparatus Required:

S.No

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

Component Name

AND Gate

OR Gate

Not Gate

NAND Gate

NOR Gate

Flip Flop

Trainer kit

Bread Board

Light Emitting Diodes

Connecting wires

Regulated Power supply

Current Limiting Resister

Part No/Range

IC 7408

IC 7432

IC 7404

IC 7400

IC 7402

IC74LS73

(0-30V)

330 ohm

Quantity in Nos

1

1

1

1

1

2

1

1

As Req.

As Req.

1

As Req.

Theory:

A counter is a sequential machine that produces a specified count sequence. The

count changes whenever the input clock is asserted. There is a great variety of counter

based on its construction.

1. Clock: Synchronous or Asynchronous

2. Clock Trigger: Positive edged or Negative edged

3. Counts: Binary, Decade

4. Count Direction: Up, Down, or Up/Down

5. Flip-flops: JK or T or D

A counter can be constructed by a synchronous circuit or by an asynchronous

circuit. With a synchronous circuit, all the bits in the count change synchronously with

http://annauniversitystudymaterials.blogspot.in/

Page 28

LINEAR AND DIGITAL IC LABORATORY

the assertion of the clock. With an asynchronous circuit, all the bits in the count do not all

change at the same time.

A counter may count up or count down or count up and down depending on the

input control. Because of limited word length, the count sequence is limited. For an n-bit

counter, the range of the count is [0, 2n-1]. The complement of the count sequence counts

in reverse direction. If the uncomplemented output counts up, the complemented output

counts down. If the uncomplemented output counts down, the complemented output

counts up. The natural count sequence is to run through all possible combinations of the

bit patterns before repeating itself. External logic can be used to arbitrary cause the

counter to start at any count and terminate at any count. A binary counter produces a

count sequence similar to the binary numbers. A decade counter counts from 0 to 9, thus

making it suitable for human interface. Other counters count to 12 making them suitable

for clocks.

Two Classes of Counters

Asynchronous Counters (Ripple counters)

Synchronous Counters

Asynchronous: The events do not have a fixed time relationship with each other and do

not occur at the same time.

Synchronous: The events have a fixed time relationship with each other and do occur at

the same time.

Counters are classified according to the way they are clocked. In asynchronous

counters, the first flip-flop is clocked by the external clock pulse and then each

successive flip-flop is by clocked the output of the preceding flip-flop. In synchronous

counters, the clock input is connected to all of the flip-flop so that they are clocked

simultaneously. It is used to count how many clock pulses just have entered. Number of

flip-flops are combined together in order to count the input clock pulses. The count exists

in the form of binary and it is called the state of the counter. If the counter has n flipflops, it can have a maximum of 2n states or unique states; it is called the modulus of the

counter. The number of unique states passed by the counter before coming back to its

initial state is called the module of a counter. If a counter does not utilize all possible

unique states as valid states, it is to be called as shortened modulus counter.

http://annauniversitystudymaterials.blogspot.in/

Page 29

LINEAR AND DIGITAL IC LABORATORY

The change in state of flip-flop will ripple from LSB to MSB which represents

flip-flop and hence called as ripple counter.

For designing a shortened modulus counter, an appropriate reset signal to clear

inputs of all the flip-flops present is given.

Synchronous Counters:

In synchronous counters, the clock inputs of all the flip-flops are connected

together and are triggered by the input pulses. Thus, all the flip-flops change state

simultaneously (in parallel).

Logic diagram of a synchronous mod-6 counter:

http://annauniversitystudymaterials.blogspot.in/

Page 30

LINEAR AND DIGITAL IC LABORATORY

Determination of the minimal-sum expressions for a synchronous mod-6 counter

using clocked JK flip-flops.

Synchronous 4-Bit Binary Counter:

http://annauniversitystudymaterials.blogspot.in/

Page 31

LINEAR AND DIGITAL IC LABORATORY

Asynchronous Counters:

An asynchronous counter is one in which the flip-flop within the counter do not

change states at exactly the same time because they do not have a common clock pulse.

The main characteristic of an asynchronous counter is each flip-flop derives its

own clock from other flip-flops and is therefore independent of the input clock.

Consequently, the output of each flip-flop may change at different time, hence the term

asynchronous. From the asynchronous counter diagram above, we observed that the

output of the first flip-flop becomes the clock input for the second flip-flop, and the

output of the second flip-flop becomes the clock input for the third flip-flop etc. For the

first flip-flop, the output changes whenever there is a negative transition in the clock

input. This means that the output of the first flip-flop produces a series of square waves

that is half the frequency of the clock input. Since the output of the first flip-flop becomes

the clock of the second flip-flop, the output of the second flip-flop is half the frequency

of its clock, i.e. the output of the first flip-flop that in turn is half the frequency of the

clock input. This behavior, in essence is captured by the binary bit pattern in the counting

sequence

Asynchronous 4 Bit Binary Counter:

http://annauniversitystudymaterials.blogspot.in/

Page 32

LINEAR AND DIGITAL IC LABORATORY

Asynchronous Decade Counters:

The binary counters previously introduced have two to the power n states. But

counters with states less than this number are also possible. They are designed to have the

number of states in their sequences, which are called truncated sequences. These

sequences are achieved by forcing the counter to recycle before going through all of its

normal states. A common modulus for counters with truncated sequences is ten. A

counter with ten states in its sequence is called a decade counter.

Once the counter counts to ten (1010), all the flip-flops are being cleared. Notice

that only Q1 and Q3 are used to decode the count of ten. This is called partial decoding,

as none of the other states (zero to nine) have both Q1 and Q3 HIGH at the same time.

http://annauniversitystudymaterials.blogspot.in/

Page 33

LINEAR AND DIGITAL IC LABORATORY

Truth Table:

Procedure:

1. Connections are made as shown in the logic diagram.

2. The input clock pulse is applied from digital trainer and the corresponding output is

checked through LEDs.

Inference:

Result:

Viva Questions:

1.

2.

3.

4.

5.

6.

What is mean by counter?

What is mean by synchronous and asynchronous counter?

What is mean by decade counter?

What is mean by binary counter?

What is the difference between the counting sequences of up and down counter?

Give the advantages and disadvantages of a synchronous counter over an

asynchronous counter?

7. What is the difference between combinational logic and sequential logic?

8. How many flip-flops are required to construct a decade counter?

9. The terminal count of a typical modulus-10 binary counter is ________.

10. To operate correctly, starting a ring counter requires ______________.

http://annauniversitystudymaterials.blogspot.in/

Page 34

LINEAR AND DIGITAL IC LABORATORY

Experiment: 5

DESIGN AND IMPLEMENTATION OF 4-BIT SHIFT REGISTERS

Aim:

To design, construct and test the following types of shift registers

1. 4 bit Serial in Serial out Shift Register

2. 4 bit Serial in Parallel out Shift Register

3. 4 bit Parallel in Parallel out Shift Register

4. 4 bit Parallel in Serial out Shift Register

Apparatus Required:

S.No

1.

2.

3.

4.

6.

7.

8.

9.

10.

11.

12.

Component Name

AND Gate

OR Gate

Not Gate

NAND Gate

Flip Flop

Trainer kit

Bread Board

Light Emitting Diodes

Connecting wires

Regulated Power supply

Current Limiting Resister

Part No/Range

IC 7408

IC 7432

IC 7404

IC 7400

IC 7474

(0-30V)

330 ohm

Quantity in Nos

1

1

1

1

2

1

1

As Req.

As Req.

1

As Req.

Theory:

Shift registers, like counters, are a form of sequential logic. Sequential logic,

unlike combinational logic is not only affected by the present inputs, but also, by the

prior history. In other words, sequential logic remembers past events. Shift registers

produce a discrete delay of a digital signal or waveform. A waveform synchronized to a

clock, a repeating square wave, is delayed by "n" discrete clock times, where "n" is the

number of shift register stages. Thus, a four stage shift register delays "data in" by four

clocks to "data out". The stages in a shift register are delay stages, typically type "D"

Flip-Flops or type "JK" Flip-flops.

http://annauniversitystudymaterials.blogspot.in/

Page 35

LINEAR AND DIGITAL IC LABORATORY

Formerly, very long (several hundred stages) shift registers served as digital

memory. This obsolete application is reminiscent of the acoustic mercury delay lines

used as early computer memory. Serial data transmission, over a distance of meters to

kilometers, uses shift registers to convert parallel data to serial form. Serial data

communications replaces many slow parallel data wires with a single serial high speed

circuit.

Serial data over shorter distances of tens of centimeters, uses shift registers to get

data into and out of microprocessors. Numerous peripherals, including analog to digital

converters, digital to analog converters, display drivers, and memory, use shift registers

to reduce the amount of wiring in circuit boards. Some specialized counter circuits

actually use shift registers to generate repeating waveforms. Longer shift registers, with

the help of feedback generate patterns so long that they look like random noise, pseudonoise.

Basic shift registers are classified by structure according to the following types:

Serial-in/serial-out

Parallel-in/serial-out

Serial-in/parallel-out

Universal parallel-in/parallel-out

Above we show a block diagram of a serial-in/serial-out shift register, which is 4stages long. Data at the input will be delayed by four clock periods from the input to the

output of the shift register. Data at "data in", above, will be present at the Stage A output

after the first clock pulse. After the second pulse stage A data is transfered to stage B

http://annauniversitystudymaterials.blogspot.in/

Page 36

LINEAR AND DIGITAL IC LABORATORY

output, and "data in" is transfered to stage A output. After the third clock, stage C is

replaced by stage B; stage B is replaced by stage A; and stage A is replaced by "data in".

After the fourth clock, the data originally present at "data in" is at stage D, "output". The

"first in" data is "first out" as it is shifted from "data in" to "data out".

Data is loaded into all stages at once of a parallel-in/serial-out shift register. The

data is then shifted out via "data out" by clock pulses. Since a 4- stage shift register is

shown above, four clock pulses are required to shift out all of the data. In the diagram

above, stage D data will be present at the "data out" up until the first clock pulse; stage C

data will be present at "data out" between the first clock and the second clock pulse; stage

B data will be present between the second clock and the third clock; and stage A data will

be present between the third and the fourth clock. After the fourth clock pulse and

thereafter, successive bits of "data in" should appear at "data out" of the shift register

after a delay of four clock pulses.

If four switches were connected to DA through DD, the status could be read into a

microprocessor using only one data pin and a clock pin. Since adding more switches

would require no additional pins, this approach looks attractive for many inputs.

http://annauniversitystudymaterials.blogspot.in/

Page 37

LINEAR AND DIGITAL IC LABORATORY

Above, four data bits will be shifted in from "data in" by four clock pulses and be

available at QA through QD for driving external circuitry such as LEDs, lamps, relay

drivers, and horns. After the first clock, the data at "data in" appears at QA. After the

second clock, The old QA data appears at QB; QA receives next data from "data in". After

the third clock, QB data is at QC. After the fourth clock, QC data is at QD. This stage

contains the data first present at "data in". The shift register should now contain four data

bits.

A parallel-in/parallel-out shift register combines the function of the parallel-in,

serial-out shift register with the function of the serial-in, parallel-out shift register to

yields the universal shift register. The "do anything" shifter comes at a price the

increased number of I/O (Input/Output) pins may reduce the number of stages which can

be packaged. Data presented at DA through DD is parallel loaded into the registers. This

data at QA through QD may be shifted by the number of pulses presented at the clock

input. The shifted data is available at QA through QD. The "mode" input, which may be

more than one input, controls parallel loading of data from D A through DD, shifting of

data, and the direction of shifting. There are shift registers which will shift data either left

or right.

http://annauniversitystudymaterials.blogspot.in/

Page 38

LINEAR AND DIGITAL IC LABORATORY

Serial-in/serial-out shift register:

Serial-in, serial-out shift registers delay data by one clock time for each stage.

They will store a bit of data for each register. A serial-in, serial-out shift register may be

one to 64 bits in length, longer if registers or packages are cascaded. Below is a single

stage shift register receiving data which is not synchronized to the register clock. The

"data in" at the D pin of the type D FF (Flip-Flop) does not change levels when the clock

changes for low to high. We may want to synchronize the data to a system wide clock in

a circuit board to improve the reliability of a digital logic circuit.

The obvious point (as compared to the figure below) illustrated above is that

whatever "data in" is present at the D pin of a type D FF is transfered from D to output Q

at clock time. Since our example shift register uses positive edge sensitive storage

elements, the output Q follows the D input when the clock transitions from low to high as

shown by the up arrows on the diagram above. There is no doubt what logic level is

present at clock time because the data is stable well before and after the clock edge. This

is seldom the case in multi-stage shift registers. But, this was an easy example to start

with. We are only concerned with the positive, low to high, clock edge. The falling edge

can be ignored. It is very easy to see Q follow D at clock time above. Compare this to the

diagram below where the "data in" appears to change with the positive clock edge.

http://annauniversitystudymaterials.blogspot.in/

Page 39

LINEAR AND DIGITAL IC LABORATORY

Since "data in" appears to changes at clock time t 1 above, what does the type D

FF see at clock time? The short over simplified answer is that it sees the data that was

present at D prior to the clock. That is what transfered to Q at clock time t1 is. The

correct waveform is QC. At t1 Q goes to a zero if it is not already zero. The D register

does not see a one until time t2, at which time Q goes high.

Since data, above, present at D is clocked to Q at clock time, and Q cannot

change until the next clock time, the D FF delays data by one clock period, provided that

the data is already synchronized to the clock. The Q A waveform is the same as "data in"

with a one clock period delay. A more detailed look at what the input of the type D FlipFlop sees at clock time follows. Refer to the figure below. Since "data in" appears to

changes at clock time (above), we need further information to determine what the D FF

sees. If the "data in" is from another shift register stage, another same type D FF, we can

draw some conclusions based on data sheet information. Manufacturers of digital logic

make available information about their parts in data sheets, formerly only available in a

collection called a data book. Data books are still available; though, the manufacturer's

web site is the modern source.

http://annauniversitystudymaterials.blogspot.in/

Page 40

LINEAR AND DIGITAL IC LABORATORY

Three type D Flip-Flops are cascaded Q to D and the clocks paralleled to form a

three stage shift register above.

Type JK FFs cascaded Q to J, Q' to K with clocks in parallel to yield an alternate

form of the shift register above. A serial-in/serial-out shift register has a clock input, a

data input, and a data output from the last stage. In general, the other stage outputs are not

available otherwise; it would be a serial-in, parallel-out shift register. The waveforms

below are applicable to either one of the preceding two versions of the serial-in, serial-out

shift register. The three pairs of arrows show that a three stage shift register temporarily

stores 3-bits of data and delays it by three clock periods from input to output.

http://annauniversitystudymaterials.blogspot.in/

Page 41

LINEAR AND DIGITAL IC LABORATORY

At clock time t1 a "data in" of 0 is clocked from D to Q of all three stages. In

particular, D of stage A sees a logic 0, which is clocked to QA where it remains until time

t2. At clock time t2 a "data in" of 1 is clocked from D to QA. At stages B and C, a 0, fed

from preceding stages is clocked to QB and QC. At clock time t3 a "data in" of 0 is

clocked from D to QA. QA goes low and stays low for the remaining clocks due to "data

in" being 0. QB goes high at t3 due to a 1 from the previous stage. QC is still low after t3

due to a low from the previous stage. QC finally goes high at clock t 4 due to the high fed

to D from the previous stage QB. All earlier stages have 0s shifted into them. And, after

the next clock pulse at t5, all logic 1s will have been shifted out, replaced by 0s

Parallel-in, Serial-out Shift Register:

Parallel-in/ serial-out shift registers do everything that the previous serial-in/

serial-out shift registers do plus input data to all stages simultaneously. The parallel-in/

serial-out shift register stores data, shifts it on a clock by clock basis, and delays it by the

number of stages times the clock period. In addition, parallel-in/ serial-out really means

that we can load data in parallel into all stages before any shifting ever begins. This is a

way to convert data from a parallel format to a serial format. By parallel format we mean

that the data bits are present simultaneously on individual wires, one for each data bit as

shown below. By serial format we mean that the data bits are presented sequentially in

time on a single wire or circuit as in the case of the "data out" on the block diagram

below.

Below we take a close look at the internal details of a 3-stage parallel-in/ serialout shift register. A stage consists of a type D Flip-Flop for storage, and an AND-OR

http://annauniversitystudymaterials.blogspot.in/

Page 42

LINEAR AND DIGITAL IC LABORATORY

selector to determine whether data will load in parallel, or shift stored data to the right. In

general, these elements will be replicated for the number of stages required. We show

three stages due to space limitations. Four, eight or sixteen bits is normal for real parts.

Above we show the parallel load path when SHIFT/LD' is logic low. The upper

NAND gates serving DA DB DC are enabled, passing data to the D inputs of type D FlipFlops QA QB DC respectively. At the next positive going clock edge, the data will be

clocked from D to Q of the three FFs. Three bits of data will load into QA QB DC at the

same time. The type of parallel load just described, where the data loads on a clock pulse

is known as synchronous load because the loading of data is synchronized to the clock.

This needs to be differentiated from asynchronous load where loading is controlled by

the preset and clear pins of the Flip-Flops which does not require the clock. Only one of

these load methods is used within an individual device, the synchronous load being more

common in newer devices.

http://annauniversitystudymaterials.blogspot.in/

Page 43

LINEAR AND DIGITAL IC LABORATORY

The shift path is shown above when SHIFT/LD' is logic high. The lower AND

gates of the pairs feeding the OR gate are enabled giving us a shift register connection of

SI to DA , QA to DB , QB to DC , QC to SO. Clock pulses will cause data to be right shifted

out to So on successive pulses. The waveforms below show both parallel loading of three

bits of data and serial shifting of this data. Parallel data at DA DB DC is converted to serial

data at SO.

What we previously described with words for parallel loading and shifting is now

set down as waveforms above. As an example we present 101 to the parallel inputs DAA

DBB DCC. Next, the SHIFT/LD' goes low enabling loading of data as opposed to shifting

of data. It needs to be low a short time before and after the clock pulse due to setup and

hold requirements. It is considerably wider than it has to be. Though, with synchronous

logic it is convenient to make it wide. We could have made the active low SHIFT/LD'

almost two clocks wide, low almost a clock before t 1 and back high just before t3. The

important factor is that it needs to be low around clock time t 1 to enable parallel loading

of the data by the clock. Note that at t 1 the data 101 at DA DB DC is clocked from D to Q

of the Flip-Flops as shown at QA QB QC at time t1. This is the parallel loading of the data

synchronous with the clock.

http://annauniversitystudymaterials.blogspot.in/

Page 44

LINEAR AND DIGITAL IC LABORATORY

Now that the data is loaded, we may shift it provided that SHIFT/LD' is high to

enable shifting, which it is prior to t 2. At t2 the data 0 at QC is shifted out of SO which is

the same as the QC waveform. It is either shifted into another integrated circuit, or lost if

there is nothing connected to SO. The data at QB, a 0 is shifted to QC. The 1 at QA is

shifted into QB. With "data in" a 0, QA becomes 0. After t2, QA QB QC = 010. After t3, QA

QB QC = 001. This 1, which was originally present at QA after t1, is now present at SO

and QC. The last data bit is shifted out to an external integrated circuit if it exists. After t 4

all data from the parallel load is gone. At clock t 5 we show the shifting in of a data 1

present on the SI, serial input. Why provide SI and SO pins on a shift register? These

connections allow us to cascade shift register stages to provide large shifters than

available in a single IC (Integrated Circuit) package. They also allow serial connections

to and from other ICs like microprocessors.

Serial-in, Parallel-out Shift Register:

A serial-in/parallel-out shift register is similar to the serial-in/ serial-out shift

register in that it shifts data into internal storage elements and shifts data out at the serialout, data-out, pin. It is different in that it makes all the internal stages available as

outputs. Therefore, a serial-in/parallel-out shift register converts data from serial format

to parallel format. If four data bits are shifted in by four clock pulses via a single wire at

data-in, below, the data becomes available simultaneously on the four Outputs QA to QD

after the fourth clock pulse.

http://annauniversitystudymaterials.blogspot.in/

Page 45

LINEAR AND DIGITAL IC LABORATORY

The practical application of the serial-in/parallel-out shift register is to convert data from

serial format on a single wire to parallel format on multiple wires. Perhaps, we will

illuminate four LEDs (Light Emitting Diodes) with the four outputs (QA QB QC QD ).

The above details of the serial-in/parallel-out shift register are fairly simple. It

looks like a serial-in/ serial-out shift register with taps added to each stage output. Serial

data shifts in at SI (Serial Input). After a number of clocks equal to the number of stages,

the first data bit in appears at SO (QD) in the above figure. In general, there is no SO pin.

The last stage (QD above) serves as SO and is cascaded to the next package if it exists.

If a serial-in/parallel-out shift register is so similar to a serial-in/ serial-out shift

register, why do manufacturers bother to offer both types? Why not just offer the serialin/parallel-out shift register? They actually only offer the serial-in/parallel-out shift

register, as long as it has no more than 8-bits. Note that serial-in/ serial-out shift registers

come in gigger than 8-bit lengths of 18 to to 64-bits. It is not practical to offer a 64-bit

http://annauniversitystudymaterials.blogspot.in/

Page 46

LINEAR AND DIGITAL IC LABORATORY

serial-in/parallel-out shift register requiring that many output pins. See waveforms below

for above shift register.

The shift register has been cleared prior to any data by CLR', an active low

signal, which clears all type D Flip-Flops within the shift register. Note the serial data

1011 pattern presented at the SI input. This data is synchronized with the clock CLK.

This would be the case if it is being shifted in from something like another shift register,

for example, a parallel-in/ serial-out shift register (not shown here). On the first clock at

t1, the data 1 at SI is shifted from D to Q of the first shift register stage. After t2 this first

data bit is at QB. After t3 it is at QC. After t4 it is at QD. Four clock pulses have shifted

the first data bit all the way to the last stage QD. The second data bit a 0 is at QC after the

4th clock. The third data bit a 1 is at QB. The fourth data bit another 1 is at QA. Thus, the

serial data input pattern 1011 is contained in (QD QC QB QA). It is now available on the

http://annauniversitystudymaterials.blogspot.in/

Page 47

LINEAR AND DIGITAL IC LABORATORY

four outputs. It will available on the four outputs from just after clock t4 to just before t5.

This parallel data must be used or stored between these two times, or it will be lost due to

shifting out the QD stage on following clocks t5 to t8 as shown above.

Parallel-in, Parallel-out or Universal Shift Register:

The purpose of the parallel-in/ parallel-out shift register is to take in parallel data,

shift it, then output it as shown below. A universal shift register is a do-everything device

in addition to the parallel-in/ parallel-out function.

Above we apply four bit of data to a parallel-in/ parallel-out shift register at DA

DB DC DD. The mode control, which may be multiple inputs, controls parallel loading vs.

shifting. The mode control may also control the direction of shifting in some real devices.

The data will be shifted one bit position for each clock pulse. The shifted data is available

at the outputs QA QB QC QD . The "data in" and "data out" are provided for cascading of

multiple stages. Though, above, we can only cascade data for right shifting. We could

accommodate cascading of left-shift data by adding a pair of left pointing signals, "data

in" and "data out", above. The internal details of a right shifting parallel-in/ parallel-out

shift register are shown below. The tri-state buffers are not strictly necessary to the

parallel-in/ parallel-out shift register, but are part of the real-world device shown below.

http://annauniversitystudymaterials.blogspot.in/

Page 48

LINEAR AND DIGITAL IC LABORATORY

The 74LS395 so closely matches our concept of a hypothetical right shifting

parallel-in/ parallel-out shift register that we use an overly simplified version of the data

sheet details above. See the link to the full data sheet more more details, later in this

chapter. LD/SH' controls the AND-OR multiplexer at the data input to the FF's. If

LD/SH'=1, the upper four AND gates are enabled allowing application of parallel inputs

DA DB DC DD to the four FF data inputs. Note the inverter bubble at the clock input of the

four FFs. This indicates that the 74LS395 clocks data on the negative going clock, which

is the high to low transition. The four bits of data will be clocked in parallel from DA DB

DC DD to QA QB QC QD at the next negative going clock. In this "real part", OC' must be

low if the data needs to be available at the actual output pins as opposed to only on the

internal FFs.The previously loaded data may be shifted right by one bit position if

LD/SH'=0 for the succeeding negative going clock edges. Four clocks would shift the

data entirely out of our 4-bit shift register. The data would be lost unless our device was

cascaded from QD' to SER of another device.

http://annauniversitystudymaterials.blogspot.in/

Page 49

LINEAR AND DIGITAL IC LABORATORY

Above, a data pattern is presented to inputs DA DB DC DD. The pattern is loaded to

QA QB QC QD . Then it is shifted one bit to the right. The incoming data is indicated by

X, meaning the we do no know what it is. If the input (SER) were grounded, for

example, we would know what data (0) was shifted in. Also shown, is right shifting by

two positions, requiring two clocks.

The above figure serves as a reference for the hardware involved in right shifting of data.

It is too simple to even bother with this figure, except for comparison to more complex

figures to follow.

Right shifting of data is provided above for reference to the previous right shifter.

If we need to shift left, the FFs need to be rewired. Compare to the previous right

shifter. Also, SI and SO have been reversed. SI shifts to QC. QC shifts to QB. QB shifts to

QA. QA leaves on the SO connection, where it could cascade to another shifter SI. This

left shift sequence is backwards from the right shift sequence.

http://annauniversitystudymaterials.blogspot.in/

Page 50

LINEAR AND DIGITAL IC LABORATORY

Above we shift the same data pattern left by one bit. There is one problem with the "shift

left" figure above. There is no market for it. Nobody manufactures a shift-left part. A

"real device" which shifts one direction can be wired externally to shift the other

direction. Or, should we say there is no left or right in the context of a device which shifts

in only one direction. However, there is a market for a device which will shift left or right

on command by a control line. Of course, left and right are valid in that context.

What we have above is a hypothetical shift register capable of shifting either

direction under the control of L'/R. It is setup with L'/R=1 to shift the normal direction,

right. L'/R=1 enables the multiplexer AND gates labeled R. This allows data to follow

the path illustrated by the arrows, when a clock is applied. The connection path is the

same as the too simple" "shift right" figure above. Data shifts in at SR, to QA, to QB, to

QC, where it leaves at SR cascade. This pin could drive SR of another device to the right.

What if we change L'/R to L'/R=0?

http://annauniversitystudymaterials.blogspot.in/

Page 51

LINEAR AND DIGITAL IC LABORATORY

With L'/R=0, the multiplexer AND gates labeled L are enabled, yielding a path, shown

by the arrows, the same as the above "shift left" figure. Data shifts in at SL, to QC, to QB,

to QA, where it leaves at SL cascade. This pin could drive SL of another device to the

left. The prime virtue of the above two figures illustrating the "shift left/ right register" is

simplicity. The operation of the left right control L'/R=0 is easy to follow. A commercial

part needs the parallel data loading implied by the section title. This appears in the figure

below.

Now that we can shift both left and right via L'/R, let us add SH/LD', shift/ load,

and the AND gates labeled "load" to provide for parallel loading of data from inputs D A

DB DC. When SH/LD'=0, AND gates R and L are disabled, AND gates "load" are

http://annauniversitystudymaterials.blogspot.in/

Page 52

LINEAR AND DIGITAL IC LABORATORY

enabled to pass data DA DB DC to the FF data inputs. the next clock CLK will clock the

data to QA QB QC. As long as the same data is present it will be re-loaded on succeeding

clocks. However, data present for only one clock will be lost from the outputs when it is

no longer present on the data inputs. One solution is to load the data on one clock, then

proceed to shift on the next four clocks. This problem is remedied in the 74ALS299 by

the addition of another AND gate to the multiplexer. If SH/LD' is changed to SH/LD'=1,

the AND gates labeled "load" are disabled, allowing the left/ right control L'/R to set the

direction of shift on the L or R AND gates. Shifting is as in the previous figures.

The only thing needed to produce a viable integrated device is to add the fourth AND

gate to the multiplexer as alluded for the 74ALS299. This is shown in the next section for

that part.

PIN Diagram

http://annauniversitystudymaterials.blogspot.in/

Page 53

LINEAR AND DIGITAL IC LABORATORY

Procedure:

1. Connections are made as shown in the logic diagram.

2. The input clock pulses are applied from digital trainer and the corresponding output is

checked through LEDs.

Inference:

Result:

Viva Questions:

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

What is mean by shift register?

What are the qualitative differences between parallel loading and serial

loading shift register?

How can a serial in / parallel out register be used as a serial in/ serial out

register?

What is mean by parallel in/ parallel out register?

What is mean by serial in /serial out register?

What is mean by parallel data transfer?

What is a shift register that will accept a parallel input, or a bidirectional

serial load and internal shift features, called?

What is meant by parallel load of a shift register?

What is the difference between a ring shift counter and a Johnson shift

counter?

What is the difference between a shift-right register and a shift-left

register?

http://annauniversitystudymaterials.blogspot.in/

Page 54

LINEAR AND DIGITAL IC LABORATORY

Experiment: 6

STUDY AND DESIGN OF 4 :1 & 8 :1 MULTIPLEXER AND DEMULTIPLEXER

Aim:

To design

1. 4:1 and 8:1 Multiplexer

2. 1:4 and 1:8 Demultiplexer

Apparatus Required:

S.No

1.

2.

3.

4.

5.

6.

7.

8.

9.

Component Name

AND Gate

OR Gate

Not Gate

NAND Gate

Bread Board

Light Emitting Diodes

Connecting wires

Regulated Power supply

Current Limiting Resister

Part No/Range

IC 7408

IC 7432

IC 7404

IC 7400

(0-30V)

330 ohm

Quantity in Nos

1

1

1

1

1

As Req.

As Req.

1

As Req.

Theory:

Multiplexer:

Multiplexing is defined as the process of feeding several independent signals to a

common load, one at a time. The device or switching circuitry used to select and connect

one of these several signals to the load at any one time is known as a multiplexer.

A multiplexer is a combinatorial circuit that is given a certain number (usually a

power of two) data inputs, let us say 2n, and n address inputs used as a binary number to

select one of the data inputs. The multiplexer has a single output, which has the same

value as the selected data input. The multiplexer works like the input selector of a home

music system. Only one input is selected at a time, and the selected input is transmitted to

the single output. Here is such an abbreviated truth table for n = 3. The full truth table

would have 2(3 + 23) = 2048 rows.

http://annauniversitystudymaterials.blogspot.in/

Page 55

LINEAR AND DIGITAL IC LABORATORY

4:1 Multiplexer

http://annauniversitystudymaterials.blogspot.in/

Page 56

LINEAR AND DIGITAL IC LABORATORY

8:1 Multiplexer

De Multiplexer:

The process of feeding several independent loads with signals coming

from a common signal source, one at a time. A device used for de-multiplexing is known

as a de-multiplexer the de-multiplexer circuit takes a single data input and one or more

address inputs, and selects which of multiple outputs will receive the input signal. The

address input determine which data output is going to have the same value as the data

input. The other data outputs will have the value 0.

http://annauniversitystudymaterials.blogspot.in/

Page 57

LINEAR AND DIGITAL IC LABORATORY

1:4 Demultiplexer

1:8 Demultiplexer

http://annauniversitystudymaterials.blogspot.in/

Page 58

LINEAR AND DIGITAL IC LABORATORY

Procedure:

1. Connections are made as shown in the logic diagram.

2. The input clock pulses are applied from digital trainer and the corresponding output is

checked through LEDs.

Inference:

Result:

Viva Questions:

1. What is mean by multiplexer?

2. What is the another name of multiplexer and why we are calling it as like that?

3. What are the applications of multiplexer?

4. Write the truth table for 4 input multiplexer

5. What is meant by multiplexing?

6. What is meant by demultiplexer?

7. What is the another name of demultiplexer?

8. What are the applications of Demultiplexer?

9. What is mean by clock demultiplexer?

10. How can we construct 2n to 1 multiplexer from an n to 2n decoder?

http://annauniversitystudymaterials.blogspot.in/

Page 59

LINEAR AND DIGITAL IC LABORATORY

Experiment: 7

MONOSTABLE AND ASTABLE MULTIVIBRATOR USING 555 TIMER

Aim:

1.To study and testing of Astable Multivibrator operation using NE/SE 555 Timer

2.To study and testing of Monostable Multivibrator operation using NE/SE 555 Timer

Apparatus Required:

S.No

1.

2.

3.

4.

5.

6.

7.

8.

9.

Component Name

Timer IC

Regulated Power supply

Bread Board

Light Emitting Diodes

DRB

DCB

Connecting wires

Current Limiting Resister

Function Generator

Part No/Range

NE/SE 555

(0-30V)

-

330 ohm

-

Quantity in Nos

1

1

1

As Req.

1

1

As Req.

As Req.

1

Theory:

555 Timer IC

The 555 timer IC was first introduced around 1971 by the Signetics Corporation

as the SE555/NE555 and was called "The IC Time Machine" and was also the very first

and only commercial timer IC available. It provided circuit designers with a relatively

cheap, stable, and user-friendly integrated circuit for both monostable and astable

applications. The 555 contains more than 28 transistors and it is basically a chip

containing a number of building blocks that end up very similar to an oscillator without

the TIMING COMPONENTS. It needs two or three external components to produce an

oscillator capable of operating at a frequency from 1Hz to 500 kHz. When it oscillates at

a frequency less than 1Hz, the circuit is called a Timer or Delay. . It can be used with any

power supply in the range 5-18 volts, thus it is useful in many analog circuits. When

connected to a 5-volt supply, the circuit is directly compatible with TTL or CMOS digital

devices.

http://annauniversitystudymaterials.blogspot.in/

Page 60

LINEAR AND DIGITAL IC LABORATORY

Description of Functional Block Diagram:

Referring to the functional diagram (Fig. 2.2), three 5k resistors act as a voltage

divider, providing bias voltage of 2/3 V cc to the upper comparator and 1/3 V cc to the

lower comparator, where Vcc is the activation supply voltage to the 555 timer. These two

voltages are used to fix the threshold voltage for the two comparators and aid to

determine time interval. The time interval can be varied by giving voltage to control

voltage terminal (pin 5). In actual application, where no such input voltage is given to

http://annauniversitystudymaterials.blogspot.in/

Page 61

LINEAR AND DIGITAL IC LABORATORY

control voltage terminal, a capacitor (0.01F) will be connected between control

voltage terminal (pin 5) and ground to bypass noise or ripple from the supply.

In standby (stable state), the output Q of the control flip flop (FF) is at logic one

(HIGH). This makes the output (pin 3) logic zero (LOW) because the power

amplifier is basically an inverting amplifier.

Triggering is accomplished by taking the pin 2 from above to below a voltage

level of 1/3 Vcc. The action of the trigger input is level-sensitive, allowing slow

rate-of-change waveforms, as well as pulses, to be used as trigger sources. The

trigger pulse must be of shorter duration than the time interval determined by the

external R and C.

When the trigger input is slightly lower than 1/3 Vcc, the lower comparator

output goes to positive saturation which in turn it sets the control flip flop. The

flip flop will be in set state i.e. Q= logic one (HIGH) and Q =logic zero (LOW).

Then the output of timer will be at logic one(HIGH)

Applying a positive trigger at the Threshold terminal (pin 6), when the voltage is

slightly higher than 2/3 Vcc, the upper comparator goes to positive saturation

which in turn resets the control flip flop. The flip flop goes to reset state i.e. Q=

logic zero (LOW) and Q = logic one (HIGH). Then the output of timer will be

logic zero (LOW)

The reset input (pin 4) provides a mechanism to reset the Control flip flop in a

manner which overrides the effect of any instruction coming to control flip flop from

lower comparator. This overriding reset is effective when the reset input is less than

about 0.4V. When this reset is not used, it is returned to Vcc. the transistor T2 serves as a

buffer to isolate the reset input from the control flip flop and transistor T1. The transistor

T2 is driven by an internal voltage Vref obtained from supply voltage Vcc.

http://annauniversitystudymaterials.blogspot.in/

Page 62

LINEAR AND DIGITAL IC LABORATORY

Monostable Operation:

In the standby (stable) state, control flip flop holds transistor T1 ON, thus

clamping the external timing capacitor C to ground.

The output remains at

ground potential, i.e., LOW.

As the trigger in Fig. 2.3(a) passes through Vcc/3(i.e. trigger input is slightly

lesser than 1/3 Vcc), the lower comparator is triggered to positive saturation and

the control flip flop is set, i.e. Q= logic one (HIGH) and Q =logic zero (LOW).

This makes the transistor T1 OFF and the short circuit across the timing capacitor

C is released.

As Q is LOW, output (pin 3) goes HIGH (=Vcc). The timing cycle now begins.

Since C is unclamped, voltage across it rises exponentially through R towards

Vcc with a time constant RC as in Fig. 2.3(b)

After a time period T, the capacitor voltage is just greater than 2/3V cc (which is

applied in pin 6) and the upper comparator is triggered to positive saturation,

and resets the control flip flop(R=1, S=0) that is, Q= logic zero (LOW) and Q =

http://annauniversitystudymaterials.blogspot.in/

Page 63

LINEAR AND DIGITAL IC LABORATORY

logic one (HIGH)(assuming very small trigger pulse width).

This makes

transistor T1 go ON (i.e. saturates), thereby discharging the capacitor C rapidly to

ground potential. The output returns to the standby state or ground potential as

shown in Fig. 2.3(c) .

The voltage across the capacitor as in Fig is given by

vc Vcc (1 e

t

RC

At t =T,

2

vc Vcc

3

Therefore,

2

Vcc Vcc (1 e RC )

3

0.66 1 e

T

RC

ln( 0.33) ln( e

T

RC

) (

Or,

T = RC ln(0.33)

Or,

T = 1.09 RC (seconds)

T

T

)

RC

RC

http://annauniversitystudymaterials.blogspot.in/

Page 64

LINEAR AND DIGITAL IC LABORATORY

From the above equation it is evident that timing interval is independent of the

supply voltage. It may also be noted that once triggered, the output remains in the HIGH

state until time T elapses, which depends only upon R and C. Any additional trigger pulse

coming during this time will not change the output state.

However, if a negative going reset pulse as in Fig. 2.4(d) is applied to the reset terminal

(pin-4) during the timing cycle, transistor T2 goes OFF, T1 becomes ON and the external

timing capacitor C is immediately discharged. The output now will be as in Fig. 2.4(c)

with doted lines. It may be seen that the output of T2 is connected directly to the input of

T1 so as to turn ON T1 immediately and thereby avoid the propagation delay through the

FF. Now, even if the reset is released, the output will still remain LOW until a negative

going trigger pulse is again applied at pin2.

Astable Operation:

The timing resistor is split into two sections Ra and Rb. Pin 7 of discharging

transistor T1 is connected to the junction of Ra and Rb.

When the power supply Vcc is connected, the external timing capacitor C charges

towards Vcc with a time constant (Ra + Rb)C.

During this time, the lower

comparator will be in positive saturation which in tern sets the control flip flop

(i.e. Reset R=0, Set S=1), this makes Q =0 Output (pin 3) goes high (equals Vcc),

which has unclamped the timing capacitor C.

http://annauniversitystudymaterials.blogspot.in/

Page 65

LINEAR AND DIGITAL IC LABORATORY

When the capacitor voltage is just greater than (2/3)Vcc the upper comparator

triggers to positive saturation and resets the control flip flop(i.e. Reset R=1, Set

S=0) so that Q =1. This in turn, makes transistor T1 on and capacitor C starts

discharging towards ground through Rb and transistor T1 with a time constant RbC

(neglecting the forward resistance of T1).

Current also flows into transistor T1 through Ra. Resistors Ra and Rb must be

large enough to limit this current and prevent damage to the discharge transistor

T1.

The minimum value of Ra is approximately equal to Vcc/0.2 where 0.2A is the

maximum current through the on transistor T1.

During the discharge of the timing capacitor C, as it reaches just less than) Vcc/3,

the lower comparator is triggered and sets the control flip flop (i.e. Reset R=0,

Set S=1), which turns Q =0.

Now Q =0 unclamps the external timing capacitor C.

The capacitor C is thus periodically charged and discharged between (2/3) Vcc and

(1/3) Vcc respectively.

Fig. 2.6 shows the timing sequence and capacitor voltage waveform. The time duration

for which the output remains HIGH is the time taken by the capacitor to charge from

(1/3) Vcc to (2/3) Vcc. This may be calculated as follows:

Let Ra+Rb=R

The capacitor voltage for a low pass RC circuit subjected to a step input of V cc volts is

given by

vc Vcc (1 e

t

RC

The time ta taken by the circuit to charge from 0 to 2/3 Vcc is

2

V cc V cc ( 1 e

3

0 . 66

(1

t a

RC

ln( 0 . 33 ) ln( e

ta

RC

ta

RC

http://annauniversitystudymaterials.blogspot.in/

ta

RC

Page 66

LINEAR AND DIGITAL IC LABORATORY

t a 1.09 RC

and time tb is to change from 0 to 1/3Vcc is,

1

V cc V cc ( 1 e

3

tb

RC

tb=0.405RC.

Or,

So the time to change from 1/3 Vcc to 2/3 Vcc is

t1 = ta-tb

t 1 1.09RC - 0.405RC 0.69RC 0.69(R a Rb )C

The output is low while capacitor is discharging from (2/3)Vcc to (1/3)Vcc through the

resistor Rb and the voltage across the capacitor is given by

1

V

3

cc

V

3

cc

(1 e

t

R

2

b

By solving we get t 2 0.69Rb C

The charging path of the capacitor is through Ra and Rb and discharging is only through

Rb. Therefore total time,

T = t1+t2

T = 0.69(Ra+2Rb)C

1.45

( Ra 2Rb )C

The duty cycle defined here as the ratio of the time the output is low as compared to the

total time period

Duty cycle =

t2

Rb

T R a 2R b

Duty cycle %=

Rb

100

R a 2R b

The duty cycle is always less than 50% in other words, the off time t2 is always

less than the ON time t1. Thus the output of the 555 astable circuit is asymmetric. By

making Rb large compared to Ra,(i.e. Ra=minimum) the waveform becomes more

symmetric and the 555 output approaches a square wave. If Ra is very small, the pin 7 will

be connected to Vcc through a very low resistance and extra current flows through T1

http://annauniversitystudymaterials.blogspot.in/

Page 67

LINEAR AND DIGITAL IC LABORATORY

when it is ON. This may damage the transistor T1 and hence the timer. To avoid this, a

diode can be connected across the resistance Rb in forward bias.

Procedure:

1. The connections are given as per the given circuit diagrams (Fig. 2.3 and Fig 2.5)

drawn as per the design values.

2. The values of Vcc = 5V, R =5k (use decade resistance box) and C=0.1F (use

decade capacitance box) are set.

3. Appropriate Trigger input (400 Hz, 5V p-p, square wave) is applied from the

signal generator for monostable operation.

4. The output signals from Pin no.3 and pin no.6 (voltage across the capacitor) are

observed using a CRO and the frequency and amplitude (p-p) of the output

waveforms are recorded.

5. The output waveforms are plotted under same scale.

Inference:

Result:

Viva Questions:

1.

2.

3.

4.

5.

6.

7.

What is mean by astable multivibrator?

What is mean by duty cycle?

What are the types of astable multivibrator?

Write the equation for time intervals present in an astable multivibrator.

What is the another name of astable multivibrator?

What is mean by monostable multivibrator?

What is the difference between an astable multivibrator and a monostable

multivibrator?

8. What is the another name of monostable multivibrator?

9. What are the types of monostable multivibrator?

10. What is mean by quasi-stable state?

http://annauniversitystudymaterials.blogspot.in/

Page 68

LINEAR AND DIGITAL IC LABORATORY

Experiment No: 8

APPLICATION OF OPERATIONAL AMPLIFIERS

Aim:

To design, construct and test the following Op-Amp applications.

(a) Inverting Amplifier

(b) Non-inverting Amplifier

(c) Adder

(d) Comparator

(e) Integrator

(f) Differentiator.

Apparatus required:

S.No

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

Component Name

Op amp IC

Regulated Power supply

Connecting wires

Bread Board

Cathode Ray Tube

Resister

Resister

Resister

Capacitor

Function Generator

Part No/Range

IC 741

(0-30V)

(0-20MHz)

10K

1K

10K,1.5K159

0.1uf,0.01uf

1-1MHz

Quantity in Nos

1

2

As Req.

1

1

3

2

Each one

Each one

1

Theory:

Ideal op-amp characteristics

Infinite open-loop voltage gain

Infinite input impedance

Zero output impedance

Zero noise contribution

Zero DC output offset

Infinite bandwidth

Differential inputs that stick together

http://annauniversitystudymaterials.blogspot.in/

Page 69

LINEAR AND DIGITAL IC LABORATORY

Inverting Amplifier:

The op-amp is connected using two resistors R1 and Rf such that the input signal

is applied in series with R1 and the output is connected back to the inverting input

through Rf. The non-inverting input is connected to the ground or the center tap of the

dual polarity power supply. In operation, as the input signal moves positive, the output

will move negative and vice versa. The amount of voltage change at the output relative to

the input depends on the ratio of the two resistors R1 and Rf.

Since the input resistance is infinite, current through R1 will be equal to the current

through Rf. Assuming that the op-amp is an ideal one, then Vd = 0 and node a is at

ground potential.

Current through R1 and Rf is given by

Output voltage, Vout i1 R f Vin

i1

vin

R1

Rf

R1

Hence the closed loop gain of the inverting amplifier is, Acl

Alternatively, the node equation at node a is

Rf

Vout

Vin

R1

Va Vin Va Vout

0

R1

Rf

Where Va is the voltage at node a. Since node a is at virtual ground, Va=0. Therefore

by rearranging the above equation the closed loop gain can be written as

Acl

Rf

Rf

Vout

. The output voltage is Vout Vin

Vin

R1

R1

http://annauniversitystudymaterials.blogspot.in/

Page 70

LINEAR AND DIGITAL IC LABORATORY

The negative sign indicates a Phase shift of 180 between Vin and Vout. Also inverting

input is at virtual ground, the effective input impedance is R1.

Non-inverting Amplifier:

The non-inverting amplifier is connected so that the input signal goes directly to

the non-inverting input (+) and the input resistor R1 is grounded. In this configuration, the

input impedance as seen by the signal is much greater since the input will be following

the applied signal and not held constant by the feedback current. As the signal moves in

either direction, the output will follow in phase to maintain the inverting input at the same

voltage as the input (+). The voltage gain is always more than unity.

Analysis:

As the difference voltage Vd is zero, the voltage at node A is Vin, same as the iput

voltage applied to non-inverting terminal. Now, Rf and R1 forms a potential divider.

Hence Vin

Vout

R1 , as no current flow through the op-amp,

R1 R f

Rf

Vout R1 R f

1

Acl . Where Acl is closed loop voltage gain of the non-inverting

Vin

R1

R1

Rf

Vin .

operational amplifier. Hence output voltage Vout 1

R

1

http://annauniversitystudymaterials.blogspot.in/

Page 71

LINEAR AND DIGITAL IC LABORATORY

Summing Amplifier or Adder Circuit:

Inverting Summing Amplifier: