Académique Documents

Professionnel Documents

Culture Documents

Memoria Ee Prom

Transféré par

Cristian ChimboCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Memoria Ee Prom

Transféré par

Cristian ChimboDroits d'auteur :

Formats disponibles

CONTADORES TIPO ANILLO Y TIPO JOHNSON

Diego Gabriel Chano Tomarima

diegoga_1001@hotmail.com.

Cristian David Chimbo Tamami

cdchimbo@espe.edu.ec

Ingeniera Mecatrnica. 6 nivel, Universidad de las Fuerzas Armadas ESPE-Extensin

Latacunga, Mrquez de Maenza S/N Latacunga. Ecuador

Jueves, 28 de enero del 2015

RESUMEN: En el siguiente escrito se presenta

sobre la utilizacin del mapa de Karnaugh ya que

esto que permitir simplificar una expresin

booleana, tambin nos enfocaremos a cmo generar

y simplificar un mapa de Karnaugh de 5 y 6 variables

para ello se realizara ejemplos para una mejor

comprensin del mismo.

PALABRAS CLAVE:

Mapa de Karnaugh: similar a una tabla de

verdad su propsito es simplificar una expresin

booleana.

Simplificar: reducir una expresin o cantidad a

su forma menos compleja o ms breve.

Expresin booleana: sucesin que incluye el 0,

1, algunas variables y operaciones booleanas.

1. INTRODUCCIN.

Actualmente el almacenamiento de datos es un

proceso fundamental de toda mquina como la

computadora o dispositivos inteligentes siempre

hay la necesidad de guardar datos debido a

otros procesos del dispositivo requieren de

datos almacenados para su

comenzar a

ejecutar ya sea que los datos estn

almacenados temporal o permanentemente.

Para el almacenamiento de datos se requiere de

un medio de almacenamiento que pueda

guardar temporalmente o permanentemente los

datos deseados, estos dispositivos son

conocidos como memorias las cuales tiene la

capacidad de albergar datos por un tiempo

determinado segn sea su fabricacin y

configuracin.

En trminos informticos la palabra memoria

hace referencia a las memorias RAM y ROM y

el termino almacenamiento hace referencia al

disco duro, a los discos flexibles y al CD-ROM.

(Floyd, 2006)

2. MAPA DE

VARIABLES.

KARNAUGH

DE

El mapa de Karnaugh de 5 variables se

obtiene de dos mapas con 4 variables lo que

permite a este mapa tener 32 celdas con 5

entradas, cabe recalcar que se cuenta con una

entrada A para uno de los mapas y su

complemento A, para realizar el otro mapa.

2.1 OBTENCIN Y SIMPLIFICACIN.

Un mapa de Karnaugh de cinco variables

(ABCDE) se puede crear utilizando dos mapas

de 4 variables para lo cual ya estamos

familiarizados. Cada uno de estos mapas

contienen 16 celdas con todas las posibles

combinaciones de la variables B, C, D y E. Un

mapa es de A=0 y el otro es para A=1.

Cabe recalcar que ahora una casilla adems de

ser adyacente en forma vertical u horizontal es

adyacente a la casilla que ocupa la misma

posicin en el cuadrado cercano

Figura 1: Mapa de Karnaugh de 5 variables

Para su respectiva simplificacin y agrupacin

de una funcin de cinco variables de entrada

mostrada en la Figura 2 podemos notar que en

la agrupacin de grupo II los trminos escogido

de cada tabla son adyacentes ya que ocupan

las mismas posiciones en la respectiva tabla.

Figura 2: Simplificacin de un mapa de Karnaugh de

5 variables.

Para realizar la simplificacin del mapa de

Karnaugh de 5 variables se bebe realizar de la

misma manera que se la resuelve con un mapa

de Karnaugh de 2, 3 y 4 variables.

Y as obtenemos la simplificacin del mapa de

Karnaugh de 5 variables de la Figura 2 la cual

queda expresada de la siguiente manera:

C

D

E+BDE

C D E+

AC D(1)

f =A

+B

2.2 EJEMPLO DE MAPA DE KARNAUGH

DE

5

VARIABLES

APLICANDO

CONDICIONES NO IMPORTA.

El sistema nervioso humano, incluyendo al

cerebro, est hecho de billones de clulas

especializadas llamadas neuronas. Cada

neurona posee sinapsis (nodos, puntos de

conexin con otras neuronas) que pueden ser

de dos tipos: (1) excitatorias e (2) inhibitorias.

Cada neurona tiene una sola terminal de salida,

(la cual se denomina axn), y transmite por ella

una seal [1] cuando el nmero de sinapsis

excitatorias con entradas [1], excede al nmero

de sinapsis inhibitorias con entrada [1] por al

menos el nmero N (umbral de la neurona).

Determine la funcin de la salida F(A, B, C, D,

E) en el axn de la neurona, dadas las

siguientes condiciones:

N=1.

No se presenta nunca el caso en el cual

el nmero de unos en las sinapsis de

excitacin es igual al nmero de unos

en la sinapsis de inhibicin.

Minimizar F mediante mapas de Karnaugh

haciendo uso de las condiciones irrelevantes o

No Importa.

Figura 3: Detalle de la neurona con las variables

A, B, C Sinapsis de excitacin.

A, D, E Sinapsis de inhibicin.

Resolucin:

Lo primero que vamos hacer es realizar una

tabla de verdad en donde se considera todas las

condiciones mencionadas.

Tabla 1: Tabla de verdad con las 5 variables

Ahora la Tabla 1 pasamos a un mapa de

Karnaugh de 5 variables.

Figura 4: Mapa de Karnaugh de 5 variables

Como podemos observar el mapa anterior de la

Figura 4 difiere usando hasta ahora, esto es con

el fin de mostrar que existen muchas formas de

expresar el mapa de Karnaugh, para la que solo

podemos recomendar se use la que ms nos

facilite.

La funcin reducida obtenida del mapa de

Karnaugh de la Figura 4 queda expresada de la

siguiente manera:

F REDUCIDA =A E +BC + B D+C

D(2)

alrededor de cada puerta flotante puesto a que

es ms delgada y no fotosensible.

En cuanto a la programacin de estas memorias

se realiza de una forma similar a las EPROM,

aplicando una tensin de 21 Voltios a la

compuerta aislada MOSFET de cada transistor,

dejando de esta manera una carga elctrica,

que es suficiente para encender los transistores

y poder almacenar la informacin.

De forma contraa el borrado de esta memoria

se efecta aplicando tensiones negativas sobre

las compuertas de tal manera que se libere la

carga elctrica almacenada entre ellas.

3.1 Ventajas de la EEPROM.

Se puede borrar de forma individual las

palabras almacenadas en la memoria.

No se requiere de luz ultravioleta para

borrar la informacin.

No requieren programador.

Para reescribir no es necesario un

borrado previo.

Se pueden escribir aproximadamente

unas 1000 veces sin que se observen

problemas.

El tiempo de almacenamiento es similar

a las EPROM, aproximadamente de 10

aos.

3. MEMORIAS EEPROM

Las EEPROM cuyas siglas en ingles son

Electrical Erasable Programmable Read Only

Memory son memorias programables y

borrable elctricamente mediante impulsos

elctricos. Son conocidas tambin como nonvolatile memory o memoria no voltil y es

debido a que cuando se desconecta la energa,

los datos almacenados en la EEPROM no sern

eliminados quedando intactos

Existas memorias EEPROM pueden construir

con transistores de tecnologa MOS (Metal

Oxide Silice) de puerta flotante y MNOS (Metal

Nitride-Oxide Silicon). La aplicacin de una

tensin en la puerta de control de la estructura

de puerta flotante permite la eliminacin y el

almacenamiento de la carga en la puerta

flotante. (Floyd, 2006)

Las EEPROM tiene celdas de memoria

similares a las celdas EPROM, la nica

diferencia se encuentra en la capa aislante

3.2 Integrado EEPROM 28C64A.

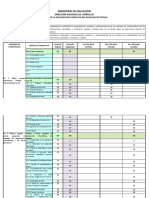

3.2.1. Distribucin de pines.

Figure 1: Distribucin de pines Memoria

EEPROM 28C64A

3.2.2. Caractersticas tcnicas.

Tabla 1: Caractersticas Tecnicas del integrado

28C64A

Caracterstica

Referencia

Tipo

Descripcin

28C64A

EEPROM CMOS

Capacidad (bits)

8192 X 8

Tipo de salida

5V

Tiempos de Acceso

120/150/200 ns

Encapsulado

DIL-28 y PLCC-32

write_eeprom (address, value): Esta

funcin escribe un dato (entero de 8 bit)

en la direccin especificada en address

en la memoria interna del PIC. Al igual

que read_eeprom address puede ser un

entero de 8 16 bit. (Beto, 2011)

5. CONCLUSIONES

La memoria 28c64a puede conectarse

fcilmente con microprocesadores o

micro controladores, puesto a que

posee pines para realizar esta accin.

La transferencia de datos en la memoria

28c641 es de manera serial, lo que

permite ahorro del micro para dedicarlo

a otras funciones.

6. RECOMENDACIONES

3.2.3. Interfaz Serial.

(1 2 pines), habilitacin.

(1 pin), reloj de sincronismo.

(1 pin), direccionamiento de dispositivo.

(3 pines) que no existen en la interfaz

paralela.

(2 pines) los pines de alimentacin del

circuito.

Los datos y la direccin de las

posiciones de memoria utilizarn

nicamente

uno

o

dos

pines,

dependiendo del tipo de comunicacin

utilizada (dos o tres hilos).

La velocidad de transferencia de datos

puede variar desde los 100 KHz hasta

los 600 MHz, dependiendo del tipo de

memoria y del sistema de comunicacin

utilizada. (Beto, 2011)

3.2.3. Funciones Basicas.

value = read_eeprom (address):

Funcin bsica para leer el valor de la

EEPROM interna . Devuelve un valor

entero (int8) de un byte. "address"

puede ser un entero de 8 16 bit. (Beto,

2011)

Se recomienda revisar el datasheet de

las memorias con la finalidad de

conocer

los

parmetros

de

funcionamiento de los mismos.

Se

recomienda

utilizar

fuentes

bibliogrficas

confiables,

con

el

propsito de obtener informacin

verdica de los temas que se trate.

7. REFERENCIAS

[1] Beto. (15 de Noviembre de 2011).

slideshare. Obtenido de

es.slideshare:

http://es.slideshare.net/be77oca

s/eeprom-10170780

[2] Floyd, T. L. (2006). Memorias y

Almacenamiento. Madrid:

Impreso en Espaa.

Vous aimerez peut-être aussi

- Linea de Tiempo UCEDocument1 pageLinea de Tiempo UCECristian ChimboPas encore d'évaluation

- Fotos LibroDocument19 pagesFotos LibroCristian ChimboPas encore d'évaluation

- Preguntas VerbalDocument2 pagesPreguntas VerbalCristian ChimboPas encore d'évaluation

- Preguntas VerbalDocument2 pagesPreguntas VerbalCristian ChimboPas encore d'évaluation

- Preguntas VerbalDocument2 pagesPreguntas VerbalCristian ChimboPas encore d'évaluation

- Preguntas VerbalDocument2 pagesPreguntas VerbalCristian ChimboPas encore d'évaluation

- G2.Chimbo - Tamami.cristian - Apreciacion de La PinturaDocument9 pagesG2.Chimbo - Tamami.cristian - Apreciacion de La PinturaCristian ChimboPas encore d'évaluation

- ProbabilidadDocument2 pagesProbabilidadCristian ChimboPas encore d'évaluation

- Progresiones Aritméticas y GeometricasDocument2 pagesProgresiones Aritméticas y GeometricasCristian Chimbo50% (2)

- Desviacion EstandarDocument2 pagesDesviacion EstandarCristian ChimboPas encore d'évaluation

- Bombas HidraulicasDocument11 pagesBombas HidraulicasCristian ChimboPas encore d'évaluation

- Combinatoria EjerciciosDocument2 pagesCombinatoria EjerciciosCristian ChimboPas encore d'évaluation

- Combinatoria EjerciciosDocument2 pagesCombinatoria EjerciciosCristian ChimboPas encore d'évaluation

- G1.Chimbo - Tamami.cristian - Apreciacion MusicalDocument10 pagesG1.Chimbo - Tamami.cristian - Apreciacion MusicalCristian ChimboPas encore d'évaluation

- Tecnologia de Prototipado Rapido EstereolitografiaDocument8 pagesTecnologia de Prototipado Rapido EstereolitografiaCristian ChimboPas encore d'évaluation

- G1.Chimbo - Tamami.cristian - Apreciacion de La PinturaDocument7 pagesG1.Chimbo - Tamami.cristian - Apreciacion de La PinturaCristian ChimboPas encore d'évaluation

- EstereolitografiaDocument13 pagesEstereolitografiaCristian ChimboPas encore d'évaluation

- Transmision y Sensores PropioceptivosDocument5 pagesTransmision y Sensores PropioceptivosCristian ChimboPas encore d'évaluation

- Maquina Semiautomatica para Pegado de BloquesDocument26 pagesMaquina Semiautomatica para Pegado de BloquesCristian ChimboPas encore d'évaluation

- Seguridad y ControlDocument1 pageSeguridad y ControlCristian ChimboPas encore d'évaluation

- Practica No.1 PDFDocument42 pagesPractica No.1 PDFAdrian AlayPas encore d'évaluation

- Camacho, Chimbo Paper 1Document5 pagesCamacho, Chimbo Paper 1Cristian ChimboPas encore d'évaluation

- Transmision y Sensores PropioceptivosDocument5 pagesTransmision y Sensores PropioceptivosCristian ChimboPas encore d'évaluation

- Evolucion Del Robot IndustrialDocument7 pagesEvolucion Del Robot IndustrialCristian ChimboPas encore d'évaluation

- Ejercicio N°6 Seguridad Con Dos ManosDocument5 pagesEjercicio N°6 Seguridad Con Dos ManosCristian ChimboPas encore d'évaluation

- Preguntas InstrumentacionDocument17 pagesPreguntas InstrumentacionCristian ChimboPas encore d'évaluation

- Informe 1 Micros LEDDocument6 pagesInforme 1 Micros LEDCristian ChimboPas encore d'évaluation

- Compensacion en RadioDocument1 pageCompensacion en RadioCristian ChimboPas encore d'évaluation

- Control ComputarizadoDocument4 pagesControl ComputarizadoCristian ChimboPas encore d'évaluation

- CajeroDocument6 pagesCajeroDavid NúñezPas encore d'évaluation

- Tema5 Actividad0 MiguelMolinaAndrea PDFDocument5 pagesTema5 Actividad0 MiguelMolinaAndrea PDFFoxspring AckermanPas encore d'évaluation

- HV FTTH Lima EneDocument8 pagesHV FTTH Lima EneShermely Araujo mendozaPas encore d'évaluation

- Extracto Dale 9 9 2022Document2 pagesExtracto Dale 9 9 2022blanca rivasPas encore d'évaluation

- Crucigrama ProgramaciónDocument1 pageCrucigrama ProgramaciónEdgar Daniel HernándezPas encore d'évaluation

- Practica 6 SemaforoDocument3 pagesPractica 6 SemaforoAyoriskarPas encore d'évaluation

- Carga de Version y Configuración ZXCTN 6150 - v1.0Document27 pagesCarga de Version y Configuración ZXCTN 6150 - v1.0julio marquez0% (1)

- El Entorno Windows. FundamentosDocument5 pagesEl Entorno Windows. Fundamentossergio darioPas encore d'évaluation

- Guia de Inventario - BelenDocument10 pagesGuia de Inventario - BelenJuan Pedro Rimachi DavilaPas encore d'évaluation

- Jig SawDocument43 pagesJig SawmerungaPas encore d'évaluation

- Laboratorio 1 y 2Document32 pagesLaboratorio 1 y 2AlbertoVega0% (1)

- Todos Los Test Sin CorreguirDocument19 pagesTodos Los Test Sin CorreguirPol SanchzPas encore d'évaluation

- Linea de Tiempo InformaticaDocument9 pagesLinea de Tiempo Informaticamildrey gonzalezPas encore d'évaluation

- Glab S10 Wmoncada 2022 01Document21 pagesGlab S10 Wmoncada 2022 01Nayely Yahuara MeraPas encore d'évaluation

- Paradigmas de La Programacion, Investigacion Unidad IDocument10 pagesParadigmas de La Programacion, Investigacion Unidad ISaysLopszPas encore d'évaluation

- Cuadro Sinoptico 1Document1 pageCuadro Sinoptico 1Moises MartinezPas encore d'évaluation

- C++ - STL, Plantillas, Excepciones, Roles y Objetos (Ricardo Devis)Document241 pagesC++ - STL, Plantillas, Excepciones, Roles y Objetos (Ricardo Devis)Leydwan Zareth D Gonzalez P100% (1)

- 001 - Sistemas de ControlDocument33 pages001 - Sistemas de ControlAdrian AguilarPas encore d'évaluation

- Comunicación Serial Arduino-Scilab PDFDocument1 pageComunicación Serial Arduino-Scilab PDFArmando Salvador de la CerdaPas encore d'évaluation

- Plan. - Mod. I - Sub. II - Sistemas OperativosDocument5 pagesPlan. - Mod. I - Sub. II - Sistemas OperativosFernadoPas encore d'évaluation

- Analisis y Modelos A Pequea Seal Del TransistorDocument22 pagesAnalisis y Modelos A Pequea Seal Del TransistorFERDINADPas encore d'évaluation

- 96508-0c8b9-Procedimiento de Actualizacion Konka kdg32mb542cDocument4 pages96508-0c8b9-Procedimiento de Actualizacion Konka kdg32mb542cMaikol Dominguez100% (1)

- ¿Qué Es El Android?Document12 pages¿Qué Es El Android?Shirley Meléndez TuestaPas encore d'évaluation

- Aplicaciones - Informaticas Malla Curricular PDFDocument5 pagesAplicaciones - Informaticas Malla Curricular PDFDiego Rene Dominguez FreirePas encore d'évaluation

- Taller Prog Ta3 Jshell Conceptos Testing Jshell en Consola Jshell in An IdeDocument13 pagesTaller Prog Ta3 Jshell Conceptos Testing Jshell en Consola Jshell in An IdeFffPas encore d'évaluation

- Cap 3Document15 pagesCap 3Mario BoetaPas encore d'évaluation

- Oracle Buckets Con C SharpDocument4 pagesOracle Buckets Con C SharpIlya RockiticoPas encore d'évaluation

- Qué Es y para Qué Sirve La ProtoboardDocument3 pagesQué Es y para Qué Sirve La ProtoboardLILIANA ANDREA CASTRO MORENOPas encore d'évaluation

- Planificación CelularesDocument2 pagesPlanificación CelularesCarolina CassaguePas encore d'évaluation

- Sistemas Operativos en Dispositivos MovilesDocument16 pagesSistemas Operativos en Dispositivos MovilesLuis VrgsPas encore d'évaluation