Académique Documents

Professionnel Documents

Culture Documents

Instructor:: Systems Design and Programming

Transféré par

MöhâmmãdŠâłãhDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Instructor:: Systems Design and Programming

Transféré par

MöhâmmãdŠâłãhDroits d'auteur :

Formats disponibles

Systems Design & Programming

Introduction

CMPE 310

Systems Design and Programming

Instructor:

Chintan Patel

Text:

Barry B. Brey, 'The Intel Microprocessors, 8086/8088, 80186/80188, 80286, 80386,

80486, Pentium and Pentium Pro Processor, Pentium II, Pentium III and Pentium 4,

Architecture, Programming and Interfacing' Sixth Edition, Prentice Hall (2003).

Supplementary text:

Muhammad Ali Mazidi and Janice Gillispie Mazidi, 'The 80x86 IBM PC and Compatible Computers (Volumes I&II), Assembly Language, Design, and Interfacing', Third

Edition, Prentice Hall (2000).

Lab Text:

Bob Neveln, 'Linux Assembly Language Programming', Prentice Hall PTR.

Web:

http://www.cs.umbc.edu/~cpatel2

Systems Design & Programming

Introduction

CMPE 310

Course Description

This course covers:

Q Intel 80x86 assembly language.

Q Architecture of the Intel microprocessors.

Q Hardware configuration and control of:

Common microprocessor support chips, e.g. Interrupt controller.

Popular I/O devices, e.g. UART, sound card.

Prerequisites:

Q Experience with the C programming language.

Q Some familiarity with Operating Systems, such as Windows.

Q Experience with the Linux operating system.

Projects:

Q Assembly Language Programming

Q Hardware Project

2

Systems Design & Programming

Introduction

CMPE 310

80x86 Evolution

4004:

Q 4-bit microprocessor.

Q 4KB main memory.

Q 45 instructions.

Q PMOS technology.

Q 50 KIPS

8008: (1971)

Q 8-bit version of 4004.

Q 16KB main memory.

Q 48 instructions.

Q NMOS technology.

8080: (1973)

Q 8-bit microprocessor.

Q 64KB main memory.

Q 2 microseconds clock cycle time; 500,000 instructions/sec.

Q 10X faster than 8008.

Systems Design & Programming

Introduction

CMPE 310

80x86 Evolution

8085: (1977)

Q 8-bit microprocessor - upgraded version of the 8080.

Q 64KB main memory.

Q 1.3 microseconds clock cycle time; 769,230 instructions/sec.

Q 246 instructions.

Q Intel sold 100 million copies of this 8-bit microprocessor.

8086: (1978) 8088 (1979)

Q 16-bit microprocessor.

Q 1MB main memory.

Q 2.5 MIPS (400 ns).

Q 4- or 6-byte instruction cache.

Q Other improvements included more registers and additional instructions.

80286: (1983)

Q 16-bit microprocessor very similar in instruction set to the 8086.

Q 16MB main memory.

Q 4.0 MIPS (250 ns/8MHz).

Systems Design & Programming

Introduction

CMPE 310

80x86 Evolution

80386: (1986)

Q 32-bit microprocessor.

Q 4GB main memory.

Q 12-33MHz.

Q Memory management unit added.

Q Variations: DX, EX, SL, SLC (cache) and SX.

80386SX: 16MB through a 16-bit data bus and 24 bit address bus.

80486: (1989)

Q 32-bit microprocessor, 32-bit data bus and 32-bit address bus.

Q 4GB main memory.

Q 20-50MHz. Later at 66 and 100MHz

Q Incorporated an 80386-like microprocessor, 80387-like floating point coprocessor

and an 8K byte cache on one package.

Q About half of the instructions executed in 1 clock instead of 2 on the 386.

Q Variations: SX, DX2, DX4.

DX2: Double clocked version:

66MHz clock cycle time with memory transfers at 33MHz.

5

Introduction

Systems Design & Programming

CMPE 310

80x86 Evolution

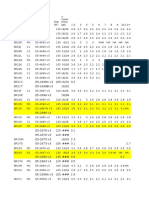

CPU

33

MHz

Co-Processor

memory

Int CPU1

Int CPU2

16K L1 cache

Co-Processor

8K L1 cache

Pentium: (1993)

Q 32-bit microprocessor, 64-bit data bus and 32-bit address bus.

Q 4GB main memory.

Q 60, 66, 90MHz.

1-and-1/2 100MHz version.

Double clocked 120 and 133MHz versions.

Fastest version is the 233MHz (3-and-1/2 clocked version).

Q 16KB L1 cache (split instruction/data: 8KB each).

Q Memory transfers at 66MHz (instead of 33MHz).

Q Dual integer processors.

Pentium

80486DX

66

MHz

memory

Introduction

Systems Design & Programming

CMPE 310

80x86 Evolution

Pentium Pro: (1995)

Q 32-bit microprocessor, 64-bit data bus and 36-bit address bus.

Q 64GB main memory.

Q Starts at 150MHz.

Q 16KB L1 cache (split instruction/data: 8KB each).

Q 256KB L2 cache.

Q Memory transfers at 66MHz.

Q 3 integer processors.

Pentium Pro

Int CPU2

256K L2 cache

Int CPU1

16K L1 cache

Co-Processor

66MHz

memory

Int CPU3

Introduction

Systems Design & Programming

CMPE 310

80x86 Evolution

Pentium II: (1997)

Q 32-bit microprocessor, 64-bit data bus and 36-bit address bus.

Q 64GB main memory.

Q Starts at 266MHz.

Q 32KB split instruction/data L1 caches (16KB each).

Q Module integrated 512KB L2 cache (133MHz).

Q Memory transfers at 66MHz to 100MHz (1998).

Pentium II

Int CPU1

Co-Processor

133MHz

Int CPU3

512K L2 cache

Int CPU2

32K L1 cache

Module

(small PCB)

100MHz

memory

Introduction

Systems Design & Programming

CMPE 310

80x86 Evolution

Pentium III: (1999)

Q 32-bit microprocessor, 64-bit data bus and 36-bit address bus.

Q 64GB main memory.

Q 800MHz and above.

Q 32KB split instruction/data L1 caches (16KB each).

Q On-chip 256KB L2 cache (at-speed).

Q Memory transfers 100MHz to 133MHz.

Q Dual Independent Bus (simultaneous L2 and system memory access).

Pentium III

Int CPU2

256K L2 cache

Int CPU1

16K L1 cache

Co-Processor

133MHz

memory

Int CPU3

9

Systems Design & Programming

Introduction

CMPE 310

80x86 Evolution

Pentium IV: (2002)

Q 1.4 to 1.9GHz and the latest at 3.20 GHz and 3.46GHz (Hyper-Threading)!

Q 1MB/512KB/256KB L2 cache.

Q 800 MHz (about 6.4GB/s)/533 MHz (4.3 GB/s)/ 400MHz (3.2 GB/s) system bus.

Q1066 MHz front side bus just available.

QSpecialized for streaming video, game and DVD applications (144 new SIMD 128-bit

instructions).

Q 0.13um, more than 55 million transistors, 60nm transistors.

QNewer ones are in 90nm transistors, more than 125 million possible.

Refer to the following URL for more details:

http://www.intel.com/design/pentium4/documentation.htm

10

Vous aimerez peut-être aussi

- Instructor:: Systems Design and ProgrammingDocument10 pagesInstructor:: Systems Design and ProgrammingMujeeb AhmadPas encore d'évaluation

- Architecture and Programming of x86 Processors: Microprocessor Techniques and Embedded SystemsDocument24 pagesArchitecture and Programming of x86 Processors: Microprocessor Techniques and Embedded SystemslimbusPas encore d'évaluation

- Intel Microprocessor Chapter 01Document86 pagesIntel Microprocessor Chapter 01Muhammad AwaisPas encore d'évaluation

- Microprocessor Assignment: Priyank Mandal 285/C0/07Document11 pagesMicroprocessor Assignment: Priyank Mandal 285/C0/07Priyank MandalPas encore d'évaluation

- 4thsem Microprocessor Notes PDFDocument148 pages4thsem Microprocessor Notes PDFVishal SharmaPas encore d'évaluation

- MicroprocessorDocument12 pagesMicroprocessorMishalPas encore d'évaluation

- INTEL MicroprocessorDocument75 pagesINTEL MicroprocessorFrank MosesPas encore d'évaluation

- Organization of The IBM Personal Computer: Evolution of Microprocessors Lecture#05Document16 pagesOrganization of The IBM Personal Computer: Evolution of Microprocessors Lecture#05Asadullah KhanPas encore d'évaluation

- Practical No. - 1Document55 pagesPractical No. - 1Rashi SharmaPas encore d'évaluation

- PROCESSOR FAMILIESDocument25 pagesPROCESSOR FAMILIESAnupam Kumar Sinha100% (1)

- Processor Families: by Prabhanshu Tripathi Ankit GuptaDocument25 pagesProcessor Families: by Prabhanshu Tripathi Ankit GuptaAnasPas encore d'évaluation

- 8086 ArchiDocument6 pages8086 ArchiMAHENDRA ZALAPas encore d'évaluation

- Generations of Computer MicroprocessorsDocument68 pagesGenerations of Computer MicroprocessorsMKPas encore d'évaluation

- Case StudyDocument73 pagesCase StudyMisha WaseemPas encore d'évaluation

- The Intel Microprocessors: Architecture, Programming, and Interfacing - 6 Ed.Document75 pagesThe Intel Microprocessors: Architecture, Programming, and Interfacing - 6 Ed.Suhas GhantaPas encore d'évaluation

- Advanced Computer Architecture (ACA) /lecture: LV64-446, Module MV5.1Document101 pagesAdvanced Computer Architecture (ACA) /lecture: LV64-446, Module MV5.1fahadned5717Pas encore d'évaluation

- The 8086 Microprocessor: 1.1 Introduction To Microprocessors and InterfacingDocument31 pagesThe 8086 Microprocessor: 1.1 Introduction To Microprocessors and Interfacingbabil_88Pas encore d'évaluation

- Module 4 - CODocument10 pagesModule 4 - COAnnabellePas encore d'évaluation

- Microprocessors EvolutionDocument56 pagesMicroprocessors EvolutionPrajwal S MPas encore d'évaluation

- The X86 Microprocessor: ObjectivesDocument32 pagesThe X86 Microprocessor: Objectivespapikhu36100% (4)

- Computer Architecture: The Pentium ProcessorDocument43 pagesComputer Architecture: The Pentium ProcessorHussain JehlPas encore d'évaluation

- Mpi Chapter1Document57 pagesMpi Chapter1zinabuhaile26Pas encore d'évaluation

- Intel IA32 (80x86) Microprocessors: Dr. Doug L. Hoffman Computer Science 330 Spring 2002Document28 pagesIntel IA32 (80x86) Microprocessors: Dr. Doug L. Hoffman Computer Science 330 Spring 2002amdevaPas encore d'évaluation

- Introduction To Microprocessors: SubtopicsDocument4 pagesIntroduction To Microprocessors: SubtopicsJimboy RengelPas encore d'évaluation

- Evolution of MicroProcessorDocument28 pagesEvolution of MicroProcessorRafat Touqir RafsunPas encore d'évaluation

- Computer Architecture: The 80x86 MicroprocessorsDocument18 pagesComputer Architecture: The 80x86 Microprocessorsاحمد عاصم عواجهPas encore d'évaluation

- My Architecture Term PaperDocument15 pagesMy Architecture Term PaperJaganmoy DewasyPas encore d'évaluation

- The X86 Microprocessor & Alp: Microprocessors and MicrocontrollersDocument56 pagesThe X86 Microprocessor & Alp: Microprocessors and MicrocontrollersNaveen NPas encore d'évaluation

- Intel P5 (Microarchitecture) : Navigation SearchDocument13 pagesIntel P5 (Microarchitecture) : Navigation SearchLudwig McwillsPas encore d'évaluation

- Evolution of Intel MicroprocessorDocument18 pagesEvolution of Intel MicroprocessorThesisRequirement100% (1)

- Assignment (Chapter1 To Chapter4)Document15 pagesAssignment (Chapter1 To Chapter4)Jac ChanchalPas encore d'évaluation

- Chapter1 - The 80x86 MicroprocessorsDocument77 pagesChapter1 - The 80x86 MicroprocessorsAliaa TarekPas encore d'évaluation

- Evolution of MicroprocessorDocument28 pagesEvolution of MicroprocessorAbhinavPas encore d'évaluation

- Intel 80186 Microprocessor HistoryDocument18 pagesIntel 80186 Microprocessor HistoryAnasPas encore d'évaluation

- COMPARE-386-486-PI-PII-PIII-MOTHERBOARDSDocument13 pagesCOMPARE-386-486-PI-PII-PIII-MOTHERBOARDSManuBhatiaPas encore d'évaluation

- Historical Evolution of Intel MicroprocessorsDocument28 pagesHistorical Evolution of Intel MicroprocessorsDhealine JusayanPas encore d'évaluation

- Rchitecture: Computer Organization and Assembly Language Lec#6Document16 pagesRchitecture: Computer Organization and Assembly Language Lec#6Hasaan AliPas encore d'évaluation

- X86 ArchitetureDocument17 pagesX86 Architetureseety2Pas encore d'évaluation

- Intel Microprocessor EvolutionDocument5 pagesIntel Microprocessor EvolutionRobert Jason RamosPas encore d'évaluation

- 80386Document4 pages80386Peejay OllabracPas encore d'évaluation

- Evolution of Microprocessors: From 4004 to Pentium 4Document10 pagesEvolution of Microprocessors: From 4004 to Pentium 4Sharmila83Pas encore d'évaluation

- Introduction To Microprocessors and ComputersDocument24 pagesIntroduction To Microprocessors and ComputershrrameshhrPas encore d'évaluation

- Microprocessor Engineering PDFDocument68 pagesMicroprocessor Engineering PDFumairPas encore d'évaluation

- ECE391 - Ch1 - Basics of Computer SystemsDocument21 pagesECE391 - Ch1 - Basics of Computer SystemsAnh Hào NguyễnPas encore d'évaluation

- Intel I3 ProcessorDocument8 pagesIntel I3 ProcessorArpit Upadhyay100% (1)

- MP QabankDocument81 pagesMP QabankPreethamkumarms PreethamPas encore d'évaluation

- x-86 FamilyDocument14 pagesx-86 FamilyPrince VegetaPas encore d'évaluation

- Comparison of Pentium Processor With 80386 and 80486Document23 pagesComparison of Pentium Processor With 80386 and 80486Tech_MX60% (5)

- Intel 8086Document4 pagesIntel 8086Shishir YalburgiPas encore d'évaluation

- IntelDocument6 pagesInteljinmenchiePas encore d'évaluation

- Chapter 1Document58 pagesChapter 1vipanaroraPas encore d'évaluation

- Experiment-1: Aim of The ExperimentDocument27 pagesExperiment-1: Aim of The ExperimentsoniaPas encore d'évaluation

- Microprocessor and Assembly Language: LECTURE-3-THE 80X86 MicroprocessorDocument47 pagesMicroprocessor and Assembly Language: LECTURE-3-THE 80X86 MicroprocessorIqraPas encore d'évaluation

- MPMC Mod-1Document32 pagesMPMC Mod-1Syeda AfreenPas encore d'évaluation

- History of Intel Processors from the 8086 to the Pentium IVDocument10 pagesHistory of Intel Processors from the 8086 to the Pentium IVjazibPas encore d'évaluation

- Advanced Microprocessors: The Pentium ProcessorsDocument4 pagesAdvanced Microprocessors: The Pentium ProcessorsSankari SoniPas encore d'évaluation

- Intel Architecture: 2.1. Brief History of The Ia-32 ArchitectureDocument19 pagesIntel Architecture: 2.1. Brief History of The Ia-32 ArchitectureBalu RajanPas encore d'évaluation

- Microprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureD'EverandMicroprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureÉvaluation : 1 sur 5 étoiles1/5 (1)

- Mega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3D'EverandMega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3Pas encore d'évaluation

- DHCP 2008Document8 pagesDHCP 2008MöhâmmãdŠâłãhPas encore d'évaluation

- Actions, Goals, and Environment, and For The Environment (Fully/partially ObservableDocument1 pageActions, Goals, and Environment, and For The Environment (Fully/partially ObservableMöhâmmãdŠâłãhPas encore d'évaluation

- Mda Winide8086 ManualDocument107 pagesMda Winide8086 ManualUmair IslamPas encore d'évaluation

- AdsDocument1 pageAdsMöhâmmãdŠâłãhPas encore d'évaluation

- Classical Mechanics I ILOs Spring 2014-15 - AdliDocument2 pagesClassical Mechanics I ILOs Spring 2014-15 - AdliMöhâmmãdŠâłãhPas encore d'évaluation

- DDDocument1 pageDDMöhâmmãdŠâłãhPas encore d'évaluation

- DDDocument1 pageDDMöhâmmãdŠâłãhPas encore d'évaluation

- AbedDocument1 pageAbedMöhâmmãdŠâłãhPas encore d'évaluation

- AsdDocument1 pageAsdMöhâmmãdŠâłãhPas encore d'évaluation

- AdsDocument1 pageAdsMöhâmmãdŠâłãhPas encore d'évaluation

- Exp# 7Document4 pagesExp# 7MöhâmmãdŠâłãhPas encore d'évaluation

- HWDocument2 pagesHWMöhâmmãdŠâłãhPas encore d'évaluation

- RF Spectrum Ch2Document4 pagesRF Spectrum Ch2MöhâmmãdŠâłãhPas encore d'évaluation

- Lecture L3 - Vectors, Matrices and Coordinate TransformationsDocument16 pagesLecture L3 - Vectors, Matrices and Coordinate TransformationsSquakx BescilPas encore d'évaluation

- HWDocument2 pagesHWMöhâmmãdŠâłãhPas encore d'évaluation

- RF Spectrum Ch2Document4 pagesRF Spectrum Ch2MöhâmmãdŠâłãhPas encore d'évaluation

- Projectile PracticeDocument9 pagesProjectile PracticeMöhâmmãdŠâłãhPas encore d'évaluation

- Projectile Motion Practice Questions (With Answers) * 40-character TitleDocument6 pagesProjectile Motion Practice Questions (With Answers) * 40-character TitleRajat Mehra75% (4)

- Fundamental Concepts: Vectors: AB I J JK I JKDocument11 pagesFundamental Concepts: Vectors: AB I J JK I JKmrmodanoPas encore d'évaluation

- Data and Computer Network ILO - Spring2015Document2 pagesData and Computer Network ILO - Spring2015MöhâmmãdŠâłãhPas encore d'évaluation

- Projectile PracticeDocument9 pagesProjectile PracticeMöhâmmãdŠâłãhPas encore d'évaluation

- Control Systems Engineering Chapter 1 ConceptsDocument18 pagesControl Systems Engineering Chapter 1 ConceptsJseophPas encore d'évaluation

- Instructor:: Systems Design and ProgrammingDocument10 pagesInstructor:: Systems Design and ProgrammingMöhâmmãdŠâłãhPas encore d'évaluation

- 21.11.2012 - Stock InfoComputerDocument494 pages21.11.2012 - Stock InfoComputermedina5031Pas encore d'évaluation

- Compatibility CPUxBoardDocument20 pagesCompatibility CPUxBoardsasa68Pas encore d'évaluation

- CPU-Upgrade: Intel Core I7-3770 CPUDocument3 pagesCPU-Upgrade: Intel Core I7-3770 CPUAli HisamPas encore d'évaluation

- Cisco Unified Communications Manager: Virtualization For Older / End of Sale HardwareDocument43 pagesCisco Unified Communications Manager: Virtualization For Older / End of Sale HardwareOussama AymenPas encore d'évaluation

- List of Intel MicroprocessorsDocument46 pagesList of Intel MicroprocessorsnirajbluelotusPas encore d'évaluation

- Segmentation Targeting PositioningDocument2 pagesSegmentation Targeting PositioningAhmet Babayev50% (2)

- Microprocessors and Interfacing (ITCC 3301) : HomeworkDocument1 pageMicroprocessors and Interfacing (ITCC 3301) : HomeworkAhmad Ali KhaderPas encore d'évaluation

- Intel Server CPU Tray by Bizgram Whatsapp 87776955 PDFDocument3 pagesIntel Server CPU Tray by Bizgram Whatsapp 87776955 PDFBizgram AsiaPas encore d'évaluation

- Intel Xeon E5 v3 SpecificationsDocument6 pagesIntel Xeon E5 v3 SpecificationseuphurPas encore d'évaluation

- Intel Core i7 Processors GuideDocument5 pagesIntel Core i7 Processors GuideKing 79Pas encore d'évaluation

- Accepted ProcessorDocument28 pagesAccepted ProcessorGeo Limpoco LargoPas encore d'évaluation

- CPU Gold ContentDocument9 pagesCPU Gold Contenternestomrodrigues2933100% (1)

- List of Intel ChipsetDocument55 pagesList of Intel ChipsetHiệp MartinPas encore d'évaluation

- Computer processor history: From silicon discovery to modern CPUsDocument8 pagesComputer processor history: From silicon discovery to modern CPUscoep05Pas encore d'évaluation

- Transistor Counts: 1 Billion TransistorsDocument15 pagesTransistor Counts: 1 Billion TransistorsNeeraj KalraPas encore d'évaluation

- CPU Sockets ChartDocument18 pagesCPU Sockets Chartthesingh_0Pas encore d'évaluation

- 1.2 Evolution of MicroprocessorDocument33 pages1.2 Evolution of MicroprocessorJames AlphaPas encore d'évaluation

- Lec # 05Document28 pagesLec # 05eshaPas encore d'évaluation

- WWW Intel ComDocument1 pageWWW Intel Commr.documentPas encore d'évaluation

- Processor Number Feature Table: Desktop - Page 1Document4 pagesProcessor Number Feature Table: Desktop - Page 1Jose luis FernandezPas encore d'évaluation

- Somali Software BookDocument142 pagesSomali Software BookAbdirahman Jamal90% (10)

- 2014 Memory PC Ddr3Document6 pages2014 Memory PC Ddr3Lingga KunPas encore d'évaluation

- CPU-Upgrade - MSI P4M900M2-L (MS-7255 v2.0) Processor Support and SpecificationsDocument15 pagesCPU-Upgrade - MSI P4M900M2-L (MS-7255 v2.0) Processor Support and SpecificationsAlexandro HotnandoPas encore d'évaluation

- TIS1641ADocument28 pagesTIS1641AMonica OramasPas encore d'évaluation

- Dell Carry-In Service Center LocationsDocument2 pagesDell Carry-In Service Center LocationsRajat GuptaPas encore d'évaluation

- DG Promo Q2 FY2223 10082022Document12 pagesDG Promo Q2 FY2223 10082022evan schultzPas encore d'évaluation

- History Intel Chips Timeline PosterDocument1 pageHistory Intel Chips Timeline PosterKellie WarnerPas encore d'évaluation

- Cisco IM & Presence Virtualization GuideDocument33 pagesCisco IM & Presence Virtualization GuideCarlos RiveraPas encore d'évaluation

- Cs ViDocument3 pagesCs ViAnmol RastogiPas encore d'évaluation

- Ranking Prosessor KompDocument39 pagesRanking Prosessor Kompfaj252Pas encore d'évaluation