Académique Documents

Professionnel Documents

Culture Documents

Raiz 4

Transféré par

Hector Polanco AlvarezTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Raiz 4

Transféré par

Hector Polanco AlvarezDroits d'auteur :

Formats disponibles

INFORME PROYECTO SISTEMAS DIGITALES

DATAPATH Y UNIDA DE CONTROL

RAIZ CUARTA

Polanco Hctor (0810058) Estudiante de Pregrado

Ingeniera Electrnica

Universidad Del Valle.

AbstractEn este documento se muestra el funcionamiento de una unidad de control y el datapath especfico para realizar la

operacin de la raz cuarta, se parte del datapath especifico de la raz cuadrada el cual se modifica para poder realizar la operacin

en mencin (raz cuarta).

ndex Termsdatapath, raz cuarta, unidad de control,

I. DATAPATH ESPECIFICO

veces debe iterar para obtener el resultado en el registro

Q debe cargarse con el valor del tamao de palabra del

reistro Q (6 en ente caso) recordando que en el datapath

de la raz cuadrada este valor esta en n/2.

III. ALGORITMO DE CONTROL

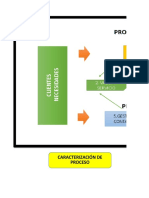

Figura No 1 (Datapath Especifico)

En la figura anterior se muestra el dapath especifico

implementado en quartus para realizar la operacin.

II. DESCRIPCIN DE FUNCIONAMIENTO

la unidad de control es similar a la unidad para realizar

la raz cuadrada pero solo teniendo en cuenta que el

contador que le indica a la unidad de control cuantas

Figura No 2 (Algoritmo de Control)

INFORME PROYECTO SISTEMAS DIGITALES

Se puede observar en el algoritmo de control que los

cambios que se hacen con respecto a la unidad de

clculo de la raz cuadrada radica bsicamente en iterar

n veces el algoritmo para despus cargar el dato

calculado en el registro D e iterar de nuevo hasta

conseguir la segunda raz, de este modo se est

calculando la raz cuadrada de la raz cuadrada.

En el siguiente ejemplo se describe como se llega al

resultado siguiendo el algoritmo.

bit para la parte entera y 5 bits para la parte decimal.

Este comportamiento es razonable ya que al calcular la

raz cuarta la parte entera del numero se hace mas

pequea mientras que para la parte decimal se debe

tener un mayor numero de cifras significativas para

tener una mayor precisin.

A continuacin se muestran los registros de

desplazamiento que se implementaron con ayuda de la

mega funcin de altera.

Se quiere calcular la raz cuarta de 10:

Primero se calcula la raz cuadrada de 10, siguiendo el

algoritmo se obtiene

= .

Despues se carga este valor calculado de nuevo en el

registro D y se limpian A y Q para volver a iterar el

algoritmo.

Figura No 3 (Registros A,D)

De este modo se tiene entonces:

= .

Se puede ver que se pierde el ultimo dato que dara mas

precisin en el resultado, si los registros de la unidad de

ejecucin fueran de mayor cantidad de bits entonces el

resultado seria:

= .

Entonces el resultado esta truncado en precisin por el

echo de no contar con la suficiente cantidad de bits en

la unidad de ejecucin, de este modo el resultado es

4

= .

= .

Se llega entonces a la conclusin que se puede mejorar

la precisin del algoritmo para calcular la raz cuarta

teniendo utilizando una mayor cantidad de bits para la

unidad de ejecucin asi como tambin tener un mayor

rango de valores a los cuales le podemos aplicar el

algoritmo para calcular su raiz4.

Vale la pena aclarar que con la unidad de control que

se utiliz donde n=6, solo se puede calcular la raz de

los nmeros en el rango de 0000 a 1111 ya que el

algoritmo al iterar la primera vez para calcular la

primera raz queda restringido a 3 bits para la parte

entera y tres bits para la parte decimal, ya en el segundo

calculo de la raz la parte entera queda restringida a 1

Figura No 4 (Registro Q y ALU)

En la figura No 3 se puede observar que el registro D

siempre desplaza a la izquierda con cero y que el bit

mas significativo se desplaza hacia A para hacer la

operacin shl(A,D),0 (2)

INFORME PROYECTO SISTEMAS DIGITALES

Vale la pena mencionar que la nica forma que se da desplazamiento en los registros es cuando llega un flanco de reloj

y esta activado el Enable de cada registro para el caso en que se deben cargar datos en los registros de deben activar

las seales Load y Enable de cada registro, y en el caso que se necesita limpiar los registros, estos se configuraron de

tal forma que el clear sea asncrono de esta forma deben haber tres seales activas en el registro para limpiar un registro

Enable,Clear y Load.

De esta forma entonces se colocan las seales de control en cada estado para que realice la operacin que se requiere,

a contincuacion se muestra parte del cdigo VHDL que da un buen entendimiento al desarrollo del algoritmo mediante

la maquina de estados.

Figura No 5 (cdigo VHDL de la FSM)

De esta forma se obtuvo una buena aproximacin del calculo de la raz cuarta de un numero comprendido en el rango

de 0 a 15. Esta condicin en el rango de los datos de entrada es dada por la limitacin en el tamao de palabra de los

registros de la unidad de ejecucin.

Por ultimo a continuacin se puede ver todas la seales de control que tiene la FSM para gobernar sobre la unidad de

ejecucin.

Vous aimerez peut-être aussi

- 115 Ejercicios resueltos de programación C++D'Everand115 Ejercicios resueltos de programación C++Évaluation : 3.5 sur 5 étoiles3.5/5 (7)

- Diseño y construcción de algoritmosD'EverandDiseño y construcción de algoritmosÉvaluation : 4 sur 5 étoiles4/5 (6)

- Motor Paso A Paso LabVIEWDocument14 pagesMotor Paso A Paso LabVIEWLeonardoCamposVazquezPas encore d'évaluation

- Triptico Evolucion de La ComputadoraDocument2 pagesTriptico Evolucion de La ComputadoraLuis Rodriguez79% (14)

- Oracle Application ExpressDocument39 pagesOracle Application Expressjaviergg777Pas encore d'évaluation

- Aspectos Avanzados Simulink y MatlabDocument13 pagesAspectos Avanzados Simulink y MatlabCarlos Oporto AñacatoPas encore d'évaluation

- Simulacion Motoreductor SimulinkDocument4 pagesSimulacion Motoreductor SimulinkRonaldEspana100% (1)

- Digitales Multiplicador y Control de CerraduraDocument31 pagesDigitales Multiplicador y Control de CerraduraCamilo Arcos GomezPas encore d'évaluation

- DatapathDocument33 pagesDatapathArlyn BatistaPas encore d'évaluation

- Reporte 6Document15 pagesReporte 6Miguel Aguilar GonzalezPas encore d'évaluation

- Algoritmo de BoothDocument11 pagesAlgoritmo de BoothSandara ParkPas encore d'évaluation

- PROGRAMACIONDocument22 pagesPROGRAMACIONDiana Peralta RodriguezPas encore d'évaluation

- Algoritmos y Estructuras de DatosDocument8 pagesAlgoritmos y Estructuras de DatosLara ZabalaPas encore d'évaluation

- Resumen de ArquiDocument9 pagesResumen de ArquiAnahi SalinasPas encore d'évaluation

- Mips Ejemplos v1Document19 pagesMips Ejemplos v1Andres DuquePas encore d'évaluation

- 5.2 Diseño Utilizando Memorias.Document7 pages5.2 Diseño Utilizando Memorias.SukiCafePas encore d'évaluation

- Ejercicios LabView PDFDocument13 pagesEjercicios LabView PDFJosho SandovalPas encore d'évaluation

- Informe CalculadoraDocument8 pagesInforme CalculadoraEdwin Gonzalez MedinaPas encore d'évaluation

- Diseño de Lógica de ControlDocument10 pagesDiseño de Lógica de Controlomer primera100% (1)

- 11 - Custom Components IntegrationDocument22 pages11 - Custom Components IntegrationDaniel FajardoPas encore d'évaluation

- Prob 11 Algoritmos para La Multiplicación de 2 NúmerosDocument16 pagesProb 11 Algoritmos para La Multiplicación de 2 NúmerosDaniel Root0% (1)

- P3y4 CiLo MexilogicsDocument25 pagesP3y4 CiLo MexilogicsVaru MataPas encore d'évaluation

- Data PathDocument9 pagesData PathmartinPas encore d'évaluation

- Pràctica 3 FIDocument4 pagesPràctica 3 FInilrosas11Pas encore d'évaluation

- Woped Tutorial Trad.Document12 pagesWoped Tutorial Trad.Alam GomezPas encore d'évaluation

- EjerciciosDocument4 pagesEjerciciosMatias RusichPas encore d'évaluation

- DISEÑO LOGICO DEL CONTROL-unidad 3 - ARQUITECTURA - YsaDocument11 pagesDISEÑO LOGICO DEL CONTROL-unidad 3 - ARQUITECTURA - YsaMichelle Ysa ValeraPas encore d'évaluation

- Unidad 2.0Document12 pagesUnidad 2.0Lisseth RiveraPas encore d'évaluation

- Diseño de SistemasDocument13 pagesDiseño de SistemasMaria EstangaPas encore d'évaluation

- Programacion de Sistemas de Tiempo RealDocument59 pagesProgramacion de Sistemas de Tiempo Realallanzr73Pas encore d'évaluation

- Registro de DesplazamientoDocument6 pagesRegistro de DesplazamientoHoshdenk Romo RamírezPas encore d'évaluation

- Examen Final U3 - p1 (Micromaster en Red Profibus)Document8 pagesExamen Final U3 - p1 (Micromaster en Red Profibus)Antonio LizarragaPas encore d'évaluation

- Organización MIPSDocument13 pagesOrganización MIPSFabiola SanchezPas encore d'évaluation

- El Coprocesador MatemáticoDocument14 pagesEl Coprocesador MatemáticoJuan Francisco HerreraPas encore d'évaluation

- ProgramacionDocument5 pagesProgramacionNixia GittensPas encore d'évaluation

- Material para Convo DecimoDocument12 pagesMaterial para Convo DecimoCa Seg GasecaPas encore d'évaluation

- Componentes TalentDocument11 pagesComponentes Talenterik apontePas encore d'évaluation

- Cap 3Document19 pagesCap 3AngelorasoUTNPas encore d'évaluation

- Sensor de Temperatura Atmel Studio - Atmega2560Document5 pagesSensor de Temperatura Atmel Studio - Atmega2560andrePas encore d'évaluation

- Funcionamiento de Las Instrucciones Aritméticas, Lógicas y de Comparación Que Maneja El PLCDocument14 pagesFuncionamiento de Las Instrucciones Aritméticas, Lógicas y de Comparación Que Maneja El PLCYohani Teodoro50% (2)

- Lab15 Modelamiento Dinamico MatlabDocument35 pagesLab15 Modelamiento Dinamico MatlabSteven Dave QRPas encore d'évaluation

- Practica 17: Funcion STD en PLCDocument19 pagesPractica 17: Funcion STD en PLCEvan AVPas encore d'évaluation

- Diseño Controlador de Velocidad Mediante LGR para Un Motor DC1Document12 pagesDiseño Controlador de Velocidad Mediante LGR para Un Motor DC1johnpiryuk100% (1)

- AT89C52 TablasDocument6 pagesAT89C52 TablasEdgar Mollinedo EscaleraPas encore d'évaluation

- Práctica 8 PipelineDocument14 pagesPráctica 8 PipelineJobQuirozPas encore d'évaluation

- Capitulo 1 - MatLabDocument15 pagesCapitulo 1 - MatLabLuis Cajusol YupanquiPas encore d'évaluation

- 5.modelado Por PRBS A Espacio de EstadosDocument11 pages5.modelado Por PRBS A Espacio de EstadosArmando Vázquez RamírezPas encore d'évaluation

- Tutorial (Algoritmos)Document39 pagesTutorial (Algoritmos)FlorPas encore d'évaluation

- Tarea 5Document5 pagesTarea 5juan mezaPas encore d'évaluation

- Practica 2b GuionDocument13 pagesPractica 2b GuionAmine ZémmouriPas encore d'évaluation

- 3 Matriz de LedsDocument8 pages3 Matriz de LedsChucho ToñoPas encore d'évaluation

- TA1 - Jesús TorresDocument8 pagesTA1 - Jesús TorresJesúsTorresPas encore d'évaluation

- Aritmetica en Punto FlotanteDocument6 pagesAritmetica en Punto Flotantejesusantolin225Pas encore d'évaluation

- TPR5B U2Document16 pagesTPR5B U2Gino FabrizioPas encore d'évaluation

- Presentación de Unidad 3Document51 pagesPresentación de Unidad 3José Armando Cruz VillaPas encore d'évaluation

- Subrutinas PDFDocument11 pagesSubrutinas PDFCristian Olmedo FerreroPas encore d'évaluation

- PEDICIDocument4 pagesPEDICIDon LimonPas encore d'évaluation

- Informe PLC N°7 USACHDocument11 pagesInforme PLC N°7 USACHFelipe VilchesPas encore d'évaluation

- Baez Cruz 11Document11 pagesBaez Cruz 11DaniloPilacuánPas encore d'évaluation

- Forma de Registro de DefectosDocument2 pagesForma de Registro de DefectosAlejandroPas encore d'évaluation

- Sentencias de ControlDocument31 pagesSentencias de ControlJordy AnchundiaPas encore d'évaluation

- Microbyte 01Document44 pagesMicrobyte 01willifoxPas encore d'évaluation

- VMware Workstation Es Un Emulador de ComputadorasDocument19 pagesVMware Workstation Es Un Emulador de ComputadorasdanielrojasPas encore d'évaluation

- Discos Duros Internos y Externos PDFDocument8 pagesDiscos Duros Internos y Externos PDFArnol Jhamil Carmen AtochePas encore d'évaluation

- Modelo ClarissaDocument5 pagesModelo ClarissaRoberto Carlos Obando ValenciaPas encore d'évaluation

- Examen Final Visual Basic BásicoDocument2 pagesExamen Final Visual Basic BásicoJaime Orlando Huarachi NuñezPas encore d'évaluation

- MU SGIS IDENTIFICA v3 PDFDocument44 pagesMU SGIS IDENTIFICA v3 PDFanon_961624585Pas encore d'évaluation

- Prolog ProyectDocument8 pagesProlog ProyectIvan Monts de OcaPas encore d'évaluation

- Tipos de Computadora RESUMEN E IMAGENDocument4 pagesTipos de Computadora RESUMEN E IMAGENUsac PatululPas encore d'évaluation

- AP01 AA1 EV04 Levantamiento Mapa Procesos XDocument11 pagesAP01 AA1 EV04 Levantamiento Mapa Procesos XCristian Camilo Delgado100% (1)

- Informe de Algoritmia y Diagrama de FlujoDocument13 pagesInforme de Algoritmia y Diagrama de FlujoDavid PantevisPas encore d'évaluation

- Taller Del TecladoDocument4 pagesTaller Del TecladojavicamiloPas encore d'évaluation

- Instalacion de La Base de Datos Oracle y Restauracion de BackupDocument9 pagesInstalacion de La Base de Datos Oracle y Restauracion de BackupPedroPas encore d'évaluation

- Mantenimiento Del PC y Resolución de Problemas - Clase 4Document27 pagesMantenimiento Del PC y Resolución de Problemas - Clase 4Alvaro Thomas EduardoPas encore d'évaluation

- Manual Teórico Práctico de Visual FoxPro 6Document36 pagesManual Teórico Práctico de Visual FoxPro 6panjuseidok100% (1)

- ComputadoraDocument1 pageComputadoraAlan CarrascoPas encore d'évaluation

- Ejercicios Resueltos de Calculo de Limites de FuncionesDocument27 pagesEjercicios Resueltos de Calculo de Limites de FuncionesWenDy ChamoChumbi ApaesTiguePas encore d'évaluation

- Vizzio - Pix4D (2) .PPSXDocument12 pagesVizzio - Pix4D (2) .PPSXFlor SegundoPas encore d'évaluation

- Modelo de Ingenieria WebDocument58 pagesModelo de Ingenieria WebMayBalderasGonzálezPas encore d'évaluation

- Libreria FstreamDocument5 pagesLibreria FstreamJunior Alache50% (2)

- Componentes de La Placa BaseDocument60 pagesComponentes de La Placa Basethesky36Pas encore d'évaluation

- Módulo 3 - Ejercicios Programación Orientada A ObjetosDocument4 pagesMódulo 3 - Ejercicios Programación Orientada A Objetosluis mauricio ardila vargasPas encore d'évaluation

- Guia Grado - 10 - Periodo2 PDFDocument5 pagesGuia Grado - 10 - Periodo2 PDFDaniela PradaPas encore d'évaluation

- Maquina de Von NewmannDocument3 pagesMaquina de Von NewmannM.casaPas encore d'évaluation

- ManualDocument74 pagesManualacaneloPas encore d'évaluation

- Usando Linux para Arreglar Un USB RotoDocument20 pagesUsando Linux para Arreglar Un USB RotoBladimir MancíaPas encore d'évaluation

- Significado de Los Símbolos de Diagrama de Flujo de ProcesosDocument6 pagesSignificado de Los Símbolos de Diagrama de Flujo de ProcesosFrank Sanchez SeguraPas encore d'évaluation