Académique Documents

Professionnel Documents

Culture Documents

JUNE 2012: Amiete - Et (New Scheme)

Transféré par

MahadevTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

JUNE 2012: Amiete - Et (New Scheme)

Transféré par

MahadevDroits d'auteur :

Formats disponibles

ROLL NO.

___________________

Code: AE74

Subject: VLSI DESIGN

AMIETE ET (NEW SCHEME)

Time: 3 Hours

JUNE 2012

Max. Marks: 100

PLEASE WRITE YOUR ROLL NO. AT THE SPACE PROVIDED ON EACH PAGE

IMMEDIATELY AFTER RECEIVING THE QUESTION PAPER.

NOTE: There are 9 Questions in all.

Question 1 is compulsory and carries 20 marks. Answer to Q.1 must be written in

the space provided for it in the answer book supplied and nowhere else.

The answer sheet for the Q.1 will be collected by the invigilator after 45 minutes of

the commencement of the examination.

Out of the remaining EIGHT Questions answer any FIVE Questions. Each question

carries 16 marks.

Any required data not explicitly given, may be suitably assumed and stated.

Q.1

Choose the correct or the best alternative in the following:

(2 10)

a. Channel exists between source and drain without gate voltage is

(A) Enhancement type MOS

(C) BiCMOS

(B) Depletion type MOS

(D) CMOS

b. Limitation of MOS Technology is

(A) High power dissipation

(C) Load driving capability

(B) Compactness

(D) High Noise margin.

c. Electron Transit time Tsd is inversely proportional to

(A) Vgs

(B) Vds

(C) L

(D) E ds

d. The constant term K in I ds expression is determined by

ins 0

D

ins 0

(D)

ins 0 WL

D

W

(C) ins 0

L

(A)

(B)

e. Figure of merit 0 is directly proportional to

(A) Width of channel

(C) Mobility of electron/hole

AE74 / JUNE 2012

(B) Length of channel

(D) Electron Transit term

AMIETE ET (NEW SCHEME)

ROLL NO. ___________________

Code: AE74

Subject: VLSI DESIGN

f. Pull-up to pull-down ratio for an nMOS inverter driven by another nMOS

inverter is

(A) 6:1

(C) 16:1

(B) 8:1

(D) 4:1

g. Latch-up in CMOS can be reduced by

(A) Increasing substrate doping level (B) Decreasing substrate doping level

(C) Increasing the value of R s

(D) Increasing the value of R p

h. Minimum spacing between two diffusion layer is

(A) 1

(C) 3

(B) 2

(D) 4

i. nMOS inverter with 4:1 Z pu / Z pd ratio has VDD to G ND ON resistance

_______

(A) 10K

(C) 50K

(B) 40K

(D) 90K

j. Total delay of cascaded CMOS inverter for N even is

(A) 3.5 Ne

(C) 5 Ne

(B) 2.5 Ne

(D) 7 Ne

Answer any FIVE Questions out of EIGHT Questions.

Each question carries 16 marks.

Q.2

a. With neat diagram explain Three modes of operation of nMOS enhancement

mode Transistor

(8)

b. With neat sketch explain the CMOS N-well Fabrication process.

Q.3

(8)

a. Derive an expression for Pull-up to Pull-down ratio for an n-MOS inverter driven

by another n-MOS inverter.

(8)

b. Draw CMOS inverter circuit. Also compare CMOS & Bipolar transistor

parameter.

(8)

Q.4

a. Write circuit and Stick diagram for

(i) 2 I\P CMOS NOR gate

(ii) 2 I\P EXOR gate using CMOS

(8)

b. Briefly explain based design rules for

(i) Transistor

(ii) Wire

(8)

AE74 / JUNE 2012

AMIETE ET (NEW SCHEME)

ROLL NO. ___________________

Code: AE74

Q.5

Subject: VLSI DESIGN

a. Define sheet resistance and standard unit of capacitance

(4)

b. Calculate R on and C g of a n-MOS inverter interms of R s and C g respectively.

Z pu

Assume

(4)

= 4 :1 .

Z pd

c. Write a short note on driving large capacitive loads.

Q.6

Q.7

Q.8

Q.9

a. Obtain Scaling factor for

(i) Gate capacitance

(iii) Power dissipation

(8)

(10)

(ii) Frequency

(iv) Current diversity

b. Design 4:1 MUX using Transmission gate.

(6)

a. Design 44 crossbar switch using MOS switch.

(8)

b. Implement adder element logic circuit using n-Switch based Multiplexer.

(8)

a. Draw the structure of Six- transistor static CMOS memory-cell and explain its

Read and Write operations.

(10)

b. Discuss about Ground rules for successful design of VLSI chip.

(6)

a. Explain briefly various design styles used in VLSI design.

(6)

b. Define Controllability and observability.

(4)

c. Write Sequential logic circuit containing scan path for testing and explain its

operation briefly.

(6)

AE74 / JUNE 2012

AMIETE ET (NEW SCHEME)

Vous aimerez peut-être aussi

- JUNE 2013: Code: AE74 Subject: VLSI DESIGNDocument3 pagesJUNE 2013: Code: AE74 Subject: VLSI DESIGNMahadevPas encore d'évaluation

- December 2011: Amiete - Et (Old Scheme)Document4 pagesDecember 2011: Amiete - Et (Old Scheme)Anurag RanaPas encore d'évaluation

- Ac03 At03Document4 pagesAc03 At03Navaneeth NairPas encore d'évaluation

- Analog CommunicationDocument3 pagesAnalog CommunicationZahid YousufPas encore d'évaluation

- 6th Microelectronic Olympiad in Armenia (2011) - TestsDocument12 pages6th Microelectronic Olympiad in Armenia (2011) - TestsMohammadAmin-DPas encore d'évaluation

- SAMPLEQUESTIONS COMPREXAM (ObjType)Document19 pagesSAMPLEQUESTIONS COMPREXAM (ObjType)ഹരി നീലാംബരിPas encore d'évaluation

- DE57J12Document4 pagesDE57J12tutulkarPas encore d'évaluation

- Test Booklet Electrical Engineering Paper Ii: IES-2011 UPSC (ESE)Document20 pagesTest Booklet Electrical Engineering Paper Ii: IES-2011 UPSC (ESE)kota_265Pas encore d'évaluation

- Acseh0304 (DLD) 2Document5 pagesAcseh0304 (DLD) 2yt608118Pas encore d'évaluation

- SANDISKDocument3 pagesSANDISKrAM100% (3)

- Vlsi Design: Time: 3 Hours Total Marks: 100Document4 pagesVlsi Design: Time: 3 Hours Total Marks: 100Shivani VarshneyPas encore d'évaluation

- AE20Document3 pagesAE20Navaneeth NairPas encore d'évaluation

- TECHNICAL QUIZ EceDocument7 pagesTECHNICAL QUIZ EceAnonymous eWMnRr70qPas encore d'évaluation

- PDC Sdec09Document8 pagesPDC Sdec09Lavanya_123Pas encore d'évaluation

- JUNE 2017: AMIETE - ET (Current & New Scheme)Document3 pagesJUNE 2017: AMIETE - ET (Current & New Scheme)mraavulaPas encore d'évaluation

- DE57D10Document4 pagesDE57D10tutulkarPas encore d'évaluation

- Btech 1 Sem Basic Electronics 15be2101 2018Document2 pagesBtech 1 Sem Basic Electronics 15be2101 2018abinash pujariPas encore d'évaluation

- Electronics June 2012Document4 pagesElectronics June 2012bkvuvce8170Pas encore d'évaluation

- GATE Electronics and Communication 2013 Set CDocument24 pagesGATE Electronics and Communication 2013 Set Cravindra_kirarPas encore d'évaluation

- Digital CommunicationMCQDocument3 pagesDigital CommunicationMCQZahid Yousuf0% (1)

- VLSI Quiz QuestionsDocument17 pagesVLSI Quiz Questionsjitu_40% (1)

- Media Communications: Test Booklet Electrical Engineering Paper IiDocument20 pagesMedia Communications: Test Booklet Electrical Engineering Paper IiRaghuPas encore d'évaluation

- Gujarat Technological University: Seat No.: - Enrolment No.Document2 pagesGujarat Technological University: Seat No.: - Enrolment No.NickPas encore d'évaluation

- JUNE 2016: AMIETE - ET (Current & New Scheme)Document3 pagesJUNE 2016: AMIETE - ET (Current & New Scheme)mraavulaPas encore d'évaluation

- Deld McqsDocument25 pagesDeld McqsAniman XanderPas encore d'évaluation

- Ec: Electronics and Communication Engineering: - Download FromDocument24 pagesEc: Electronics and Communication Engineering: - Download FromKrishna GPas encore d'évaluation

- r05410207 Vlsi DesignDocument7 pagesr05410207 Vlsi Design9010469071Pas encore d'évaluation

- OCTOBER 2012: Amiete - Et (Old Scheme)Document3 pagesOCTOBER 2012: Amiete - Et (Old Scheme)Suneetha AsPas encore d'évaluation

- University of Edinburgh College of Science and Engineering School of Engineering and ElectronicsDocument15 pagesUniversity of Edinburgh College of Science and Engineering School of Engineering and ElectronicsSyed Fasih Ur RehmanPas encore d'évaluation

- Gujarat Technological University: InstructionsDocument2 pagesGujarat Technological University: InstructionsPritesh SaxenaPas encore d'évaluation

- Guessing Papers 1-2-12th Electronics Sub Code C2Document6 pagesGuessing Papers 1-2-12th Electronics Sub Code C2snigdhagulhane0922Pas encore d'évaluation

- Es - 101Document8 pagesEs - 101Subrata PaulPas encore d'évaluation

- VLSI& Embedded - MCQ's - 21 - 30Document5 pagesVLSI& Embedded - MCQ's - 21 - 30rohi89Pas encore d'évaluation

- Gate Papr Set BDocument16 pagesGate Papr Set BD Avi Na ShPas encore d'évaluation

- Question Bank Unit - V: Registers & Counters Part - A (Each Question Carries 1 Mark)Document9 pagesQuestion Bank Unit - V: Registers & Counters Part - A (Each Question Carries 1 Mark)Nithya SPas encore d'évaluation

- Ae53 Ac53 At53Document4 pagesAe53 Ac53 At53M Taher BamyaniPas encore d'évaluation

- Unit 5 QBDocument11 pagesUnit 5 QBAMAN SRIVASTAVA (RA2011030010057)Pas encore d'évaluation

- NEET Ka Feel (04-05-2023) FNLDocument42 pagesNEET Ka Feel (04-05-2023) FNLVaradPas encore d'évaluation

- EC-C.pdf V Gate 2013Document24 pagesEC-C.pdf V Gate 2013Vikas SpPas encore d'évaluation

- FreshersworldDocument45 pagesFreshersworldManish SahuPas encore d'évaluation

- Gujarat Technological University: InstructionsDocument2 pagesGujarat Technological University: InstructionsArchana TrivediPas encore d'évaluation

- BHEL Model Question Paper (Answers Updated) Senthil4u's WeblogDocument81 pagesBHEL Model Question Paper (Answers Updated) Senthil4u's Webloganjanikuma100% (1)

- December 2015: AMIETE - ET (Current Scheme)Document3 pagesDecember 2015: AMIETE - ET (Current Scheme)mraavulaPas encore d'évaluation

- 231 - Sample Placement Papers - Question Bank, Selection Procedures, Interview Tips)Document45 pages231 - Sample Placement Papers - Question Bank, Selection Procedures, Interview Tips)Achiket SinghPas encore d'évaluation

- Model Question Paper: Basic ElectronicsDocument3 pagesModel Question Paper: Basic Electronicsravishpy100% (2)

- Basic Electronics June 2012 NewDocument4 pagesBasic Electronics June 2012 NewPrasad C MPas encore d'évaluation

- WB Set ElectronicsDocument11 pagesWB Set ElectronicsNaveen BhatPas encore d'évaluation

- Area CapacitanceDocument7 pagesArea CapacitancesivanagendraPas encore d'évaluation

- Assignment-1 Sub: Basic Electronics SUB CODE: 2110016Document15 pagesAssignment-1 Sub: Basic Electronics SUB CODE: 2110016khyatichavdaPas encore d'évaluation

- VLSIDocument21 pagesVLSIDinesh PalavalasaPas encore d'évaluation

- TCE ComprehensionDocument142 pagesTCE ComprehensionJaydithya KumarPas encore d'évaluation

- 08ab303 - Digital Logic CircuitsDocument3 pages08ab303 - Digital Logic CircuitsChandru RamaswamyPas encore d'évaluation

- Civil Service Common Examination (Csce) 2008 Examination Category: TechnicalDocument10 pagesCivil Service Common Examination (Csce) 2008 Examination Category: Technicalrohith87nairPas encore d'évaluation

- December 2016: AMIETE - ET (Current & New Scheme)Document3 pagesDecember 2016: AMIETE - ET (Current & New Scheme)mraavulaPas encore d'évaluation

- CS 801D PDFDocument4 pagesCS 801D PDFarnab paulPas encore d'évaluation

- Media Communications: Test Booklet Electronics & Telecommunication Engineering Paper - IiDocument22 pagesMedia Communications: Test Booklet Electronics & Telecommunication Engineering Paper - IiRaghuPas encore d'évaluation

- VLSI (6th) May2019Document2 pagesVLSI (6th) May2019N.RAMAKUMARPas encore d'évaluation

- MOS Integrated Circuit DesignD'EverandMOS Integrated Circuit DesignE. WolfendalePas encore d'évaluation

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysD'EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysPas encore d'évaluation

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyD'EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyPas encore d'évaluation

- Wall Mounting: A Solution To LCD/LED TV Viewing Angle IssuesDocument4 pagesWall Mounting: A Solution To LCD/LED TV Viewing Angle IssuesMahadevPas encore d'évaluation

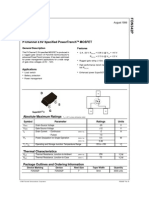

- Fdn342P: P-Channel 2.5V Specified Powertrench MosfetDocument5 pagesFdn342P: P-Channel 2.5V Specified Powertrench MosfetMahadevPas encore d'évaluation

- 0 I ADocument5 pages0 I AMahadevPas encore d'évaluation

- Maintenance 5Document17 pagesMaintenance 5KetanPas encore d'évaluation

- Recondition BatteryDocument46 pagesRecondition Batteryafic219473100% (1)

- Maintenance 5Document17 pagesMaintenance 5KetanPas encore d'évaluation

- Understanding The TV Horizontal Output Stage: Key ComponentsDocument4 pagesUnderstanding The TV Horizontal Output Stage: Key ComponentsakulimePas encore d'évaluation

- MPDFDocument6 pagesMPDFMahadevPas encore d'évaluation

- MPDFDocument6 pagesMPDFMahadevPas encore d'évaluation

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Ae51 102 8 D11Document4 pagesAe51 102 8 D11MahadevPas encore d'évaluation

- An 5273Document7 pagesAn 5273MahadevPas encore d'évaluation

- ExcerptDocument10 pagesExcerptMahadevPas encore d'évaluation

- Ae56 9 J12Document4 pagesAe56 9 J12MahadevPas encore d'évaluation

- AE68 3 d09Document3 pagesAE68 3 d09MahadevPas encore d'évaluation

- Ae68 4Document3 pagesAe68 4MahadevPas encore d'évaluation

- Ae56 D10Document4 pagesAe56 D10MahadevPas encore d'évaluation

- AE68Document4 pagesAE68MahadevPas encore d'évaluation

- Ae68 2Document4 pagesAe68 2MahadevPas encore d'évaluation

- AE56Document4 pagesAE56Gulzar AhamdPas encore d'évaluation

- Ae51 Ac51 At51Document4 pagesAe51 Ac51 At51MahadevPas encore d'évaluation

- Ae56 Ac56 At56Document3 pagesAe56 Ac56 At56MahadevPas encore d'évaluation

- Ae68 D10Document3 pagesAe68 D10MahadevPas encore d'évaluation

- Maths j11Document4 pagesMaths j11jayantsingh13Pas encore d'évaluation

- Ae01 Ac01 At01Document4 pagesAe01 Ac01 At01MahadevPas encore d'évaluation

- Ae51 D10Document4 pagesAe51 D10MahadevPas encore d'évaluation

- Basic ElectronicsDocument53 pagesBasic ElectronicsNikola Petkovic80% (5)

- TheTransistorAmplifier P2 PDFDocument144 pagesTheTransistorAmplifier P2 PDFTihomir AngelovPas encore d'évaluation

- Electrical Engineering Questions-3Document1 pageElectrical Engineering Questions-3tutulkarPas encore d'évaluation

- Radc TR 90 72Document584 pagesRadc TR 90 72Shandy Canester100% (1)

- Dennard - Design of Ion-Implanted MOSFETs With Very Small Physical Dimensions (IEEE 1974)Document13 pagesDennard - Design of Ion-Implanted MOSFETs With Very Small Physical Dimensions (IEEE 1974)Avinash GuptaPas encore d'évaluation

- Seminar ReportDocument12 pagesSeminar ReportAnamika YadavPas encore d'évaluation

- Integrated Circuits Lecture NotesDocument9 pagesIntegrated Circuits Lecture NotesJoanna Fabricante100% (1)

- SM3257ENBA Test Program and ISP Release NoteDocument8 pagesSM3257ENBA Test Program and ISP Release NoteessemirPas encore d'évaluation

- 00989961Document3 pages00989961Satyabrata MahapatraPas encore d'évaluation

- 2020 TSMC Cybershuttle Service PlanDocument2 pages2020 TSMC Cybershuttle Service PlanDal BarPas encore d'évaluation

- Ram TimelineDocument8 pagesRam TimelineCarmen Rosa Amau QuispePas encore d'évaluation

- VLSI Micro-Project Report Group A PDFDocument14 pagesVLSI Micro-Project Report Group A PDFganesh SawantPas encore d'évaluation

- Aic Lec 04 Mosfet DC v01Document55 pagesAic Lec 04 Mosfet DC v01Mustafa NasserPas encore d'évaluation

- Chapter 2 Modern CMOS Technology - IDocument20 pagesChapter 2 Modern CMOS Technology - Ifadwa badiPas encore d'évaluation

- Vlsi LP& SyllabusDocument2 pagesVlsi LP& SyllabusanittadevadasPas encore d'évaluation

- Insulated Gate Bipolar Transistors (Igbts) : Lecture NotesDocument17 pagesInsulated Gate Bipolar Transistors (Igbts) : Lecture NotesTe NgPas encore d'évaluation

- Asic Library DesignDocument12 pagesAsic Library DesignS RAVIPas encore d'évaluation

- Mos Two Input Nor and Nand GateDocument12 pagesMos Two Input Nor and Nand GateSimran SPas encore d'évaluation

- Datasheet RFD16 N05Document8 pagesDatasheet RFD16 N05Nicolau FrançaPas encore d'évaluation

- GTO (Gate Turn - OFF Thyristor)Document3 pagesGTO (Gate Turn - OFF Thyristor)Devarshi GaurPas encore d'évaluation

- CMOS Process Enhancements: Layer Rule Description 65 NM Rule (M) TABLE 3.1Document1 pageCMOS Process Enhancements: Layer Rule Description 65 NM Rule (M) TABLE 3.1Carlos SaavedraPas encore d'évaluation

- Sirena Policial AmericanaDocument9 pagesSirena Policial AmericanaromarioPas encore d'évaluation

- CMOS TechnologiesDocument27 pagesCMOS TechnologiesDebela TesfayePas encore d'évaluation

- Beginning FPGA Programming - Partie24Document5 pagesBeginning FPGA Programming - Partie24ali alilouPas encore d'évaluation

- Mosfet FinalDocument85 pagesMosfet Finaljitendra kumar gurjarPas encore d'évaluation

- FETDocument75 pagesFETVenkateswara ReddyPas encore d'évaluation

- 99 Digital Electronics Chap10 Lecture 1 BJTDocument32 pages99 Digital Electronics Chap10 Lecture 1 BJTRajesh NelavalaPas encore d'évaluation

- JFET and MOSFET PDFDocument21 pagesJFET and MOSFET PDFAkhil BabuPas encore d'évaluation

- 7.scaling and Geometry AffectsDocument3 pages7.scaling and Geometry Affects87krishna331Pas encore d'évaluation

- Fundamentals of CMOS VLSI (Complete Notes) PDFDocument214 pagesFundamentals of CMOS VLSI (Complete Notes) PDFENG18EC0062-MD TANVEERPas encore d'évaluation

- VLSI Design ManualDocument45 pagesVLSI Design ManualRafeyPas encore d'évaluation

- SyllabusDocument1 pageSyllabusRajalingam BossPas encore d'évaluation