Académique Documents

Professionnel Documents

Culture Documents

Cryp 6

Transféré par

JallaRk0 évaluation0% ont trouvé ce document utile (0 vote)

8 vues2 pagessstry

Titre original

cryp6

Copyright

© © All Rights Reserved

Formats disponibles

TXT, PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentsstry

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme TXT, PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

8 vues2 pagesCryp 6

Transféré par

JallaRksstry

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme TXT, PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 2

which matches the two important properties

mentioned above; dual-rail encoding and clockfree operation. It is intended to a

chieve low

power consumption for mobile applications and

considerable resistance against side-channel

attacks such as DPA.

II. AES S BOX AND NCL S BOX

The AES algorithm consists of a number of

rounds that are dependent on the key size. For

both cipher and inverse cipher of the AES

algorithm, each round consists of linear

operation (i.e., ADDROUNDKEY,

SHIFTROWS, and MIXCOLUMNS steps) and

nonlinear operation (i.e., SUBBYTES step).

SUBBYTES step is the first step of AES round.

Each byte in the array is updated by an 8-bit SBox, which is derived from the mu

ltiplicative

inverse over GF(28). The AES S-Box is

constructed by combining the inverse function

with an invertible affine transformation in order

to avoid attacks based on mathematics. The SBox is one the of most critical impl

ementation of

AES hardware. It consumes the majority of

power and is also the most vulnerable

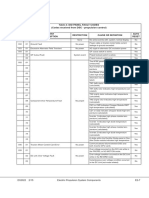

component to SCAs. A block diagram of the

AES S-Box is shown in Fig. 1(a). Asynchronous

clock less circuits require less power, generate

less noise and produce less electro-magnetic

interference compared to their synchronous

counterparts. Null Convention Logic (NCL) is a

delay-insensitive logic which belongs to the

asynchronous circuit s categories. NCL circuit

utilizes dual-rail and quad-rail logic to achieve

this delay insensitivity [9]. A dual-rail signal can

Represent [one of available three states, DATA0,

DATA1 and NULL, which corresponds to

Boolean logic 0 (i.e., DATA0), Boolean logic

1(i.e., DATA1) and control signal NULL for

asynchronous handshaking, respectively. In

order to achieve clock-free operation, two delayinsensitive registers on both si

des of the

combinational NCL circuit with local

handshaking signals are needed.

Fig. 1. (a) Combinational S-Box architecture with

encryption and decryption datapaths. (b) Block

diagram of multiplicative inversion over the GF(28)

component, where MM is modular multiplication and

XOR is EXCLUSIVEOR operation

In this research, dual-rail signals substitutes for

corresponding conventional Binary signals in the

NCL AES S-Box. The AES S-Box algorithm

adapted in this research follows the

combinational logic circuit architecture.The

affine transformation and inverse affine

transformation Components follow a series of

Boolean equations given in Table 1. As shown in

the table, the affine transformation and inverse

affine transformation components require 16 and

12 XOR gates, respectively. The multiplicative

inversion in GF(28) follows the procedure

shown in Figure 1(b). Map, square,

multiplication operations also require significant

amount of XOR gates of which the sum is 95. To

convert

Vous aimerez peut-être aussi

- New Text DocumentDocument6 pagesNew Text DocumentJallaRkPas encore d'évaluation

- New Text DocumentDocument9 pagesNew Text DocumentJallaRkPas encore d'évaluation

- New Text DocumentDocument14 pagesNew Text DocumentJallaRkPas encore d'évaluation

- New Text DocumentDocument9 pagesNew Text DocumentJallaRkPas encore d'évaluation

- Da 7Document1 pageDa 7JallaRkPas encore d'évaluation

- New Text DocumentDocument20 pagesNew Text DocumentJallaRkPas encore d'évaluation

- New Text DocumentDocument5 pagesNew Text DocumentJallaRkPas encore d'évaluation

- New Text DocumentDocument31 pagesNew Text DocumentJallaRkPas encore d'évaluation

- New Text DocumentDocument9 pagesNew Text DocumentJallaRkPas encore d'évaluation

- New Text DocumentDocument15 pagesNew Text DocumentJallaRkPas encore d'évaluation

- RSD 1Document11 pagesRSD 1JallaRkPas encore d'évaluation

- New Text DocumentDocument5 pagesNew Text DocumentJallaRkPas encore d'évaluation

- New Text DocumentDocument16 pagesNew Text DocumentJallaRkPas encore d'évaluation

- New Text DocumentDocument46 pagesNew Text DocumentJallaRkPas encore d'évaluation

- New Text DocumentDocument14 pagesNew Text DocumentJallaRkPas encore d'évaluation

- New Text DocumentDocument14 pagesNew Text DocumentJallaRkPas encore d'évaluation

- Fgs 4Document8 pagesFgs 4JallaRkPas encore d'évaluation

- New Text DocumentDocument90 pagesNew Text DocumentJallaRkPas encore d'évaluation

- New Text DocumentDocument2 pagesNew Text DocumentJallaRkPas encore d'évaluation

- GdhsDocument7 pagesGdhsJallaRkPas encore d'évaluation

- FGZ1Document8 pagesFGZ1JallaRkPas encore d'évaluation

- Fgs 1Document6 pagesFgs 1JallaRkPas encore d'évaluation

- DgtaDocument6 pagesDgtaJallaRkPas encore d'évaluation

- FGZ3Document8 pagesFGZ3JallaRkPas encore d'évaluation

- Ss 56Document3 pagesSs 56JallaRkPas encore d'évaluation

- Ss 17Document4 pagesSs 17JallaRkPas encore d'évaluation

- FGFGDocument6 pagesFGFGJallaRkPas encore d'évaluation

- Ss 18Document4 pagesSs 18JallaRkPas encore d'évaluation

- Ss 18Document4 pagesSs 18JallaRkPas encore d'évaluation

- Ss 56Document3 pagesSs 56JallaRkPas encore d'évaluation

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5782)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (72)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Konica Bizhub Press C7000-C7000p-C70hc-C6000 PDFDocument2 026 pagesKonica Bizhub Press C7000-C7000p-C70hc-C6000 PDFZoran100% (1)

- Skoda Octavia Mk1 - 01 - Running GearDocument605 pagesSkoda Octavia Mk1 - 01 - Running GearTamás Alföldi100% (1)

- Palm OS OverviewDocument20 pagesPalm OS OverviewRecycle BebEnPas encore d'évaluation

- Linear TransformerDocument44 pagesLinear TransformerRonmark AbinoPas encore d'évaluation

- Linear and Digital Appilications LabDocument66 pagesLinear and Digital Appilications LabThomaselvaPas encore d'évaluation

- SCE-Startup Logo! 0ba8 (2016)Document41 pagesSCE-Startup Logo! 0ba8 (2016)Jorge_Andril_5370100% (2)

- Drive SiemensDocument368 pagesDrive SiemensFabio PioPas encore d'évaluation

- High-contrast 6Document2 pagesHigh-contrast 6Naomi GlassPas encore d'évaluation

- NMOS Fabrication StepsDocument3 pagesNMOS Fabrication StepsRose Beth AndayaPas encore d'évaluation

- Shaanxi Electronic Control Unit PDF Wiring Diagrams PinecuDocument7 pagesShaanxi Electronic Control Unit PDF Wiring Diagrams PinecuJefferson Elbrey0% (1)

- Samsung DVD-H1080 Region Co..Document5 pagesSamsung DVD-H1080 Region Co..ppalaiPas encore d'évaluation

- Huawei RNC Parameter Reference PDFDocument1 783 pagesHuawei RNC Parameter Reference PDFcarlosandres8425Pas encore d'évaluation

- DCC-CCU-90 CCTV 3+1 Copper CableDocument2 pagesDCC-CCU-90 CCTV 3+1 Copper CableShiva ShankarPas encore d'évaluation

- CPM1A-AD041 Datasheet EnglishDocument2 pagesCPM1A-AD041 Datasheet EnglishtupitxPas encore d'évaluation

- Virgin Led Smart & Emergency Light: The Tradition of Innovation ContinuesDocument5 pagesVirgin Led Smart & Emergency Light: The Tradition of Innovation ContinuesVirginArt Tech India Pvt LtdPas encore d'évaluation

- Ads1293 UcDocument75 pagesAds1293 UcAnonymous EDt70JASWPas encore d'évaluation

- Decode potentiometer source codes to date vintage guitarsDocument18 pagesDecode potentiometer source codes to date vintage guitarsLeith Marshall100% (1)

- ATV61EXA5C71N4 product data sheetDocument7 pagesATV61EXA5C71N4 product data sheetAmirmasoudPas encore d'évaluation

- Code Fault DSCDocument27 pagesCode Fault DSCCristopher Oliver SalazarPas encore d'évaluation

- Generator Protection CoordinationDocument6 pagesGenerator Protection Coordinationb33lawPas encore d'évaluation

- Feedback Control Homework Drawings and SensorsDocument7 pagesFeedback Control Homework Drawings and SensorsAlexis DelgadoPas encore d'évaluation

- How To Add Hard Disk As CacheDocument6 pagesHow To Add Hard Disk As CacheGary John Managbanag YuPas encore d'évaluation

- SEC - 400-230 Volts LV Distribution PanelDocument24 pagesSEC - 400-230 Volts LV Distribution PanelArafat BauntoPas encore d'évaluation

- Regius 110 Service ManualDocument312 pagesRegius 110 Service ManualWellington Trajano75% (8)

- Manual de Power SuplyDocument6 pagesManual de Power SuplyCesar CelestinoPas encore d'évaluation

- Nec Pasolink NeoDocument57 pagesNec Pasolink NeohheinsPas encore d'évaluation

- Manual FR 18 Diatonic Manual RolandDocument72 pagesManual FR 18 Diatonic Manual RolandLuisDavidHernandezBonillaPas encore d'évaluation

- Yasser Auda CCIEv5 EPC OverviewDocument5 pagesYasser Auda CCIEv5 EPC OverviewQuang AnhPas encore d'évaluation

- AvK Industrial Ratings Book 2Document52 pagesAvK Industrial Ratings Book 2Herbert IrahetaPas encore d'évaluation

- Electric Power Transmission System Engineering Analysis and DesignDocument10 pagesElectric Power Transmission System Engineering Analysis and DesignJyothsna VayyalaPas encore d'évaluation