Académique Documents

Professionnel Documents

Culture Documents

Sram 2nd Phase

Transféré par

Sanjay ChCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Sram 2nd Phase

Transféré par

Sanjay ChDroits d'auteur :

Formats disponibles

Implementation of High Density And Low Leakage Power SRAM

CHAPTER 1

1. 1 INTRODUCTION

For the most recent CMOS feature sizes (e.g., 90nm and 65nm),

leakage power dissipation has become an overriding concern for VLSI circuit designers.

International technology roadmap for semiconductors (ITRS) reports that leakage power

dissipation may come to dominate total power consumption. Power consumption of CMOS

consists of dynamic and static components. Dynamic power is consumed when transistors are

switching, and static power is consumed regardless of transistor switching. Dynamic power

consumption was previously (at 0.18 technology and above) the single largest concern for

low-power chip designers since dynamic power accounted for 90% or more of the total chip

power. Therefore, many previously proposed techniques, such as voltage and frequency

scaling, focused on dynamic power reduction. However, as the feature size shrinks static

power has become a great challenge for current and future technologies.

SRAMs are used extensively in modern processors as on chip memories due to their large

Static storage density and small access latency. Low power on-chip memories have become

the topic of substantial research as they can account for almost half of total CPU dissipation,

even for extremely Power dissipation which was previously considered an issue only in

portable devices is rapidly becoming a significant design constraint in many system designs.

Dynamic power has been a predominant source of power dissipation till recently. However

static power dissipation is becoming an significant fraction of the total power. Static power is

the power dissipated in a design in the absence of any switching activity and is defined as the

product of supply voltage and leakage current. The absolute and the relative contribution of

leakage power to the total system power is expected to further increase in future technologies

because of the exponential increase in leakage currents with technology scaling. The

International Technology Roadmap for Semiconductors (ITRS) predicts that leakage power

would contribute to 50% of the total power in the next generation processors. Therefore, it is

important for system designers to get an early estimate of leakage power to meet the

challenging power constraints. There are several VLSI techniques to reduce,

Department of ECE, LVS (MTECH), NCET Page 1

Implementation of High Density And Low Leakage Power SRAM

There are several VLSI techniques to reduce leakage power. Each technique provides an

efficient way to reduce leakage power, but disadvantages of each technique limit the

application of each technique. We implement a new approach, thus providing a new choice to

low-leakage power VLSI designers. Previous techniques are summarized and compared with

our new approach.

1.2 PROBLEM STATEMENT

This research work is titled new low power approaches for VLSI logic and memory.

While designing a VLSI system power dissipation is one of the major concerns. Up to a

certain 3 time dynamic power was the single largest concern; however as the technology

feature size shrinks static power has become an important issue as dynamic power. A wellknown previous technique called the sleep transistor technique cuts off Vdd and/or Gnd

connections of transistors to save leakage power consumption. However, when transistors are

allowed to float, a system may have to wait a long time to reliably restore lost state and thus

may experience seriously degraded performance. Therefore, retaining state is crucial for a

system that requires fast response even while in an inactive state. The two common

approaches are sleepy stack and sleepy keeper. Both methods are excellent in this regard. The

static and dynamic power of sleepy stack is considerably low. But it has a delay penalty and

its area requirement is maximum compared with other processes. Again the sleepy keeper

process possesses excellent speed criteria but it requires more static and dynamic power than

sleepy stack. Our goal is to trade-off between these limitations and thus proposes new

methods which reduce both leakage and dynamic power with minimum possible area and

delay trade off.

Department of ECE, LVS (MTECH), NCET Page 2

Implementation of High Density And Low Leakage Power SRAM

CHAPTER 2

2 LITERATURE SURVEY

2.1 BASE APPROACH

It is a traditional approach. Base approach is generally indicates conventional

CMOS transistor. In the base approach pull-up network and pull down network are used

using few transistors. The pull-up network is called a P-MOS transistor and pull-down

network is called as N-MOS transistor.

Figure2.1: Base Approach

2.2 SRAM CELL LEAKAGE PATH

Department of ECE, LVS (MTECH), NCET Page 3

Implementation of High Density And Low Leakage Power SRAM

Figure 2.2: SRAM Cell Leakage Path

The sub-threshold leakage current in an SRAM cell is typically categorized into

twokinds as shown in Figure (i) cell leakage current that flows from Vdd to gnd internal

the cell and (ii) bitline leakage current that flows from bitline (or bitline) to Gnd.Although

an SRAM cell has two bitline (BL) leakage paths, the bitline leakage current and bitline

(BL) leakage current differs according to the value stored in the SRAM bit.

If an SRAM cell holds 1 as shown in Figure the bitline leakage current passing through

N3 and N2 is effectively suppressed due to two reasons. First, after precharging bitline and

bitline both to 1, the source voltage and drain voitage of N3 are the same and thus

potentially no current flows through N3. Second, two stacked and turned off transistors

(N2and N3) induce the stack effect. Meanwhile, for this case leakage where the SRAM bit

holds value 1, a large bitline leakage current flows passing through N4 and N1.If on the

other hand , the sram cell holds 0 , a large bitline leakage current is suppressed.

Mean while, for this case where the bit holds value , a large bitline leakage current

flows passing through N4 and N1. If, on the other hand , the SRAM cell holds 0. A large bit

line leakage current flows while bit line leakage current is suppressed.

2.3STACK APPROACH

Department of ECE, LVS (MTECH), NCET Page 4

Implementation of High Density And Low Leakage Power SRAM

Another technique to reduce leakage power is to stack the transistors. Figure 3.3

shows a forced stack inverter. The effect of stacking the transistor results in the reduction of

subthershold leakage current when two or more transistors are turned off together.

Figure 2.3: Stack Approach

The stacking effect can be understood from the forced stack inverter shown in

figure2.3.In the generic inverter there are only two transistors. But here in case of forced

stack inverter two pull up transistors and two pull down transistors are used. All inputs share

the same input in the forced stack circuit. If the input is 0, then both transistor M1 and M2

are turned off. Here Vx is the intermediate node voltage. Transistor M2 has its internal

resistance due to this resistance Vx is greater than the ground potential. This positive Vx

results in a negative gate-source (Vgs) for the M1 transistor and the negative source-base

voltage (Vsb) for M1. Here M1 also has a reduced drain-source voltage (Vds), which lower the

drain induced barrier lowering (DIBL) effect. These three effects together reduced the factor

Department of ECE, LVS (MTECH), NCET Page 5

Implementation of High Density And Low Leakage Power SRAM

X and hence the leakage power. All transistors are getting the same input. So this forced stack

technique is a state saving technique. That means when the circuit is in OFF mode it saves

the current state.

2.4PROPOSED APPROCH

Figure 2.4: proposed Approach

In the proposed approach where the sub thershold leakage is exponentially related to the

threshold voltage of the device and threshold voltage changes due to body effect. The source

of the nMOS device N1 is connected to ground. Transistor N2 source is connected to drain of

N1. The source of N2 is not grounded and it can acquire voltages close to Vdd while its

substrate is connected to ground. Therefore the condition Vsb=0will not hold in bias cases for

transistor N2. The device N1 will experience higher Vth due to the difference in the voltage

between the source and body. The voltage between drain and source also decreased since the

intermediate node has a voltage above the ground resulting reduction in Drain

Barrier Lowering affect and hence effective saving of leakage power.

CHAPTER 3

Department of ECE, LVS (MTECH), NCET Page 6

Induced

Implementation of High Density And Low Leakage Power SRAM

WORK CARRIED

Figure3: SRAM Cell Design

A design of as shown in the Fig 3. In order to design a memory cell there are number of

peripheral circuits connected to SRAM cell such as write driver circuit, sense amplifier

circuit and pre-charge circuit. The peripheral circuits are connected in parallel to each other

as shown in Fig 3. A memory cell can store 1bit of data. The data consists of either of the

two stable states i.e., 0 or 1. The design and description of each peripheral circuit is

explained below.

SRAM Cell:

Department of ECE, LVS (MTECH), NCET Page 7

Implementation of High Density And Low Leakage Power SRAM

An SRAM cell has three different states they are:

1. Standby (the circuit is idle)

2. Write Operation (updating the contents) and

3. Read Operation (the data has been requested).

Here we design conventional 6T SRAM, 5T SRAM, and design of SRAM by using

stacked approach and proposed one .we make power compression of this designs.

Pre-Charge Circuit: Pre-charge circuit is also called as the bit line initialization unit of

the memory bit cell, thus it is used to charge the bitlinesBL and BLbar to the supply

voltage before a read or write operation .

Write Driver Circuit:The write driver circuit is used during the write operation in order

to discharge one of the bit lines. In the SRAM write drivers typically discharge the bit

line to 0V to ensure successful write operation in all process and mismatch corners. When

write driver is enabled, the pre-charge circuit is usually deactivated to avoid any

contention. Based on the application, a write driver circuitry can be implemented in

different ways .

Sense Amplifier Circuit: The sense amplifier is used to facilitate the read operation. The

read operation in the conventional 6T SRAM cell is differential. During a read operation

the stored data inside the SRAM cell appears on the bitlines of the stored data. However,

the data is not directly read from the bit lines. If the data is directly read from the bit

lines, then one of the bit lines has to be discharged to 0V. Since the bit lines are highly

capacitive, discharging a bit line to 0V would make the subsequent pre-charging consume

a significant amount of power. In addition, SRAM cells are made as small as possible in

order to maximize the memory capacity in a given silicon area. The current driving

capability of the SRAM cells read discharge path is very low. If such a low current drive

is used to discharge the highly capacitive bit lines, it would take a large amount of time.

Sense amplifier is used to avoid these problems. The sense amplifier works as a buffer

between the bit lines and the node from where ultimately the data is read, which is

comparatively less capacitive than the bit lines. Instead of being completely discharged,

the bit lines are typically discharged by 10%-15% of V DD. By this way both the

subsequent pre-charge power and the discharge delay is reduced.

3.1 6T SRAM

Department of ECE, LVS (MTECH), NCET Page 8

Implementation of High Density And Low Leakage Power SRAM

6T SRAM cell uses a single wordline and both true and complementary bitlines. The

complementary bitline is often called bit_b.The contain a pair of cross-coupled inverters and

an acess transistors for each bitline. True and complementary versions of the data are stored

on the cross-coupled inverters. If the data is disturbed slightly, positive feedback around the

loop will restore it to VDD or GND. The wordline is asserted to read or write the cell.

.Fig 3.1.1: SCHEMATIC 6T SRAM

The basic working and operation of 6T SRAM cell is that in the design of a single bit

SRAM cell as shown in Fig 1, BL and BLbar are the inputs, V1 and V2 are the outputs,

wordline (WL) is the enable input. When the enable input WL is on, the transistors M5 and

M6 are on, now inputs BL and BLbar are given to the nodes v1 and V2 respectively. Due to

the positive feedback between the two cross coupled inverters the output data is stored at V1

Department of ECE, LVS (MTECH), NCET Page 9

Implementation of High Density And Low Leakage Power SRAM

and V2. When the enable signal WL is turned off, then the SRAM cell will be in standby

mode by holding the previous data. Now the stored data is passed to the sense amplifier

circuit through precharge circuit for read operation.

When wordline is enable WL=1 the inputs are BL=0,BLbar=1 the output will be

V1=0,V2=1 is stored when wordline is disables the same data is retained at V1 and V2 node.

When wordline is enable WL=1 the inputs are BL=1,BLbar=0 the output will be V1=1,

V2=0 is stored if wordline is disables then same data is retained at V1 and V2 node.

Figure 3.1.2:Waveform of 6T SRAM

3.2 5T SRAM MEMORY CELL

Department of ECE, LVS (MTECH), NCETPage 10

Implementation of High Density And Low Leakage Power SRAM

Figure 3.2.1: 5T SRAM Schematic

Figur 3.2.1 shows the schmatic of 5T SRAM cell which contain a single wordline and

Bitline .During idle mode of cell (when read and write operations dont perform on

cell).during write operation the bitline driving for write data drove on bit line and then word

line asserted to vdd.At the end of write operation ,cell will go to idle mode , wordline and bit

line asserted to vdle and Gnd respectively .during read operation bit line discharge to Gnd

and then floated .transistor is off and thus read line maintained at vdd.

The inputs WL=0,BL=0 or 1, output at node V1=X;When the wordline is enabled

high WL=1 and input BL=0 ,output at node V1=0 After disable of wordline the same data

will be retained at the output.WL=0,and BL=1 output will be V1=1.

Department of ECE, LVS (MTECH), NCETPage 11

Implementation of High Density And Low Leakage Power SRAM

Figure 3.2.3:Waveform of 5T SRAM

3.3 SRAM DESGIN USING STACK APPROCH

The design of SRAM by using stack approach is shown in fig. Here transistors M1 to

M6 constitute the standard 6T SRAM cell. Stacking is applied to this cell both in the pull

down and pull up section. Transistors M7 and M8 are connected as Nmos stacking transistors

to pull down transistors M1 and M3.Pmos stacking transistors M9 and M10 are connected to

pull up load transistors M2 and M4.During cell inactive state, the node at 0value is

connected to ground through two series connected off transistors. This reduces leakage

current due to stack effect. Similarly the leakage current flowing through off transistors in the

pull up path also gets reduced due to stacking. The node storing 1gets charged by larger

resistance which reduces active current and active power consumption. The power can be

further lowered by using high Vt transistors.

In this cell both high-Vt and normal-Vt transistors are used. So that optimized delay and

power can be observed. Transistor sizing for SRAM can be approached in two ways. For the

function of SRAM cell, read & write stability needs to be guaranteed. In read stability, M1

Department of ECE, LVS (MTECH), NCETPage 12

Implementation of High Density And Low Leakage Power SRAM

transistor is required to be much larger than M5 transistor to make sure that node between

M1 and M5 transistors must not flip. When in write mode, bit lines (Bl or Blb) over

powercell with new value. However, high bit lines must not overpower inverters during read

operation. That results in the determination of sizing M2 transistor weaker than M5 transistor.

The stacking transistors are taken as minimum size transistors.

Figure 3.3.1: Stacked SRAM Schematic

The design of SRAM by using stack approach is shown in fig here it as wordline BL and

BLbar as input and V1 and V2 as output. when wordline is enabled then the data with be

evaluated at the internal node of the memory as show in fig .

WL=1, BL=0, BLbar=1 outputs will be V1=O, V2=1 when the wordline disabled then

same data will be retained at the output until we make WL as high irrespective of input.

WL=1, BL=1, BLbar=0 output will be V1=1, V2=O. when the wordline disabled then

same data will be retained at the output until we make WL as high irrespective of input.

Department of ECE, LVS (MTECH), NCETPage 13

Implementation of High Density And Low Leakage Power SRAM

Figure 3.3.3:Waveform of Stacked SRAM

3.4 PROPOSED SRAM

Figure 3.4.1: Schematic of proposed SRAM

The design of Proposed SRAM is shown in fig. Here transistors M0 to M5 constitute the

standard 5T SRAM cell proposed. Here an NMOS transistor is applied to this cell in the pull

down section. Transistors M5 are connected as NMOS transistors to pull down transistors M0

and M4. During cell inactive state, the pull down transistor is been isolated with the ground

Department of ECE, LVS (MTECH), NCETPage 14

Implementation of High Density And Low Leakage Power SRAM

terminal and thus by creating virtual ground and back to back inverters connected. This

reduces leakage current due to the NMOS transistor is in cut off region and similarly the

leakage current flowing through off transistors in the pull up path also gets reduced due to

series connected NMOS.

Transistor sizing for SRAM can be approached in two ways. For the function of

proposed SRAM cell requires minimum sizing depending on the Switching value of back to

back inverter connected. PM0 transistor is required to be much larger than NM0 transistor to

make sure that node between NM4 and NM0 transistors must not flip. When in write mode,

bit lines (Bl) is updated with new value and during this operation the NMOS at pull-down is

turned on and turned off when data is written that is when WL is made inactive.

Department of ECE, LVS (MTECH), NCETPage 15

Implementation of High Density And Low Leakage Power SRAM

Figure 3.4.3: Waveform Of Proposed SRAM

POWER COMPARISSION TABLE

MEMORY CELL

6T SRAM

5T SRAM

Stack Approach

STATIC POWER

Department of ECE, LVS (MTECH), NCETPage 16

TOTAL POWER

Implementation of High Density And Low Leakage Power SRAM

Proposed SRAM

3.5 WRITE DRIVER

The write driver is used during the write operation of the SRAM cell . The

function of the SRAM write driver is to quickly discharge one of the bit lines from the

precharge level to below the write margin of the SRAM cell . Normally, the write driver is

enabled by the Write Enable (WE) signal and drives the bit line using full-swing discharge

from the precharge level to ground .

Figure3.5.1: 6T write driver Schematic

The write driver circuit design is as shown in Fig , it consists of data and its

complementary databar inputs, write enable input, outputs BL and BLbar , and transmission

Department of ECE, LVS (MTECH), NCETPage 17

Implementation of High Density And Low Leakage Power SRAM

gates. The design is based on transmission gate. Transmission gate is used to improve the

noise margin .The above Fig shows the write drive circuit for conventional 6T SRAM and

stacked SRAM. From Fig when Data=0,WE=1 means write enabled the output will be

BL=0,BLbar=1.WE=0 same data will be retained at BL and BLbar .when Data=1,WE=1 the

output will be BL=1,BLbar=0 if write is disabled same data is retained.

Figure3.5.2: wave form of write driver circuit

The design of write driver circuit for conventional 5T SRAM and proposed SRAM is shown

in Fig3.5.3 .where Data , write enable are inputs BL is output.when WE is enabled then the

input data will appear at output. Initially WE=0,DATA=1 or 0 ,BL= X;When the write

enable is made high and DATA=1 the output BL=1 If WE=0 then same data will retained at

output. input WE=1 ,DATA=0 and output will be BL=0.

Department of ECE, LVS (MTECH), NCETPage 18

Implementation of High Density And Low Leakage Power SRAM

Figure 3.5.3: 5T write driver schematic

Figure 3.5.4.: waveform of write driver circuit for 5T SRAM

Department of ECE, LVS (MTECH), NCETPage 19

Implementation of High Density And Low Leakage Power SRAM

3.6 PRECHARGE CIRCUIT

Various read and write operations are performed on memory bit cell,

so before any operation is to be performed we have to set the bitlines at a

particular level, so precharge circuit is used to pull up the bitlines.

Precharge circuit is also used to equalize the potential at bitlines . The

precharge circuit design is shown in Fig 3.6, it consists of inputs (bitlines)

BL and BLbar, enable (Pre) signal, the design is composed of transistors

P1, P2 and P3.

Figure3.6: pre-charge circuit schematic

The precharge circuit is used to charge the BL and BLbar to the supply voltage before

a read or write operation . The design of precharge circuit consists of three PMOS transistors.

Two of the transistors P1 and P2 are used to connect the bitlines to VDD, and the third

transistor P3 is connected between the two bitlines to ensure that the bit lines end up being

the same voltage. To precharge the bitlines, the enable signal Pre is given to a logic 0, this

turns on all three transistors which are charged and equalize bitlines BL and BLbar to V DD

[26]. In the design of 6T SRAM cell as shown in Fig 3.1.1, the bitlines BL and BLbar which

are connected to each peripheral circuits will be charged to logic high when precharged

circuit is on. Pre = 0, BL = 1, BLbar = 1. Pre = 1, BL = X , BLbar = X .

Department of ECE, LVS (MTECH), NCETPage 20

Implementation of High Density And Low Leakage Power SRAM

3.7 SENSE AMIPLIFR

The basic working and operation of sense amplifier circuit for conventional

6TSRAM and stacked SRAM is shown in figure3.7.1. The sense amplifier circuit is used

during the read operation in order to sense the data stored in the SRAM cell and display that

data at the output. In the design of a sense amplifier circuit as BL and BLbar are the inputs,

RD and RD bar are the outputs, Ysel is the bitlines isolation enable signal, SAen is the sense

amplifier circuit enable signal.

In the design of a 6T or Stacked SRAM cell as shown in Fig 3.1.1 and Fig 3.3.1, the

bitlines are precharged to logic high through precharged circuit before read operation. The

stored data at nodes V1 and V2 in the SRAM cell are transferred to the bitlines, during this

phase due to charge sharing between the access transistors of the SRAM cell and the bitlines

the voltage will be differential, the sense amplifier will sense this small analog differential

voltage and amplify to a full swing voltage by discharging one of the bitlines to ground from

the precharged value. The read output will be displayed at the RD and RDbar nodes. The

sense amplifier circuit is enabled only when the sense amplifier enable (SAen) signal is

turned on. The precharge circuit and the sense amplifier circuit are isolated from the SRAM

cell during write phase by enabling Ysel input through logic high as shown in Fig 3.7.1. The

isolation circuit consists of two PMOS transistors M6 and M7.

Department of ECE, LVS (MTECH), NCETPage 21

Implementation of High Density And Low Leakage Power SRAM

Figure3.7.1: 6T SRAM Sense Amplifier Schematic

Department of ECE, LVS (MTECH), NCETPage 22

Implementation of High Density And Low Leakage Power SRAM

Figure3.7.2: waveform of 6T SRAM Sense Amplifier

Figure3.7.3 shows the design of sense amplifier for conventional 5T SRAM and proposed

SRAM .The use of sense Amplifier is to read the contents of data from the memory cell and

also to produce a amplified voltage at the output.

Figure3.7.3: 5T SRAM Sense Amplifier Schematic

Sense Amplifier magnify the small differential input voltage to the large differential

output voltage.Figure 3.7.3 shows the design of sense amplifier for 5T and proposed SRAM.

Where sense and BL are inputs RD is output .SENSE =0,BL=0, output RD=0.SENSE=1,

BL=1, output RD=1.

Department of ECE, LVS (MTECH), NCETPage 23

Implementation of High Density And Low Leakage Power SRAM

Figure3.7.4: waveform of 5T SRAM Sense Amplifier

4 Tools Utilized

Cadence IC 6.1.0 Virtuoso Schematic Editor

Analog Design Environment Spectra Simulator for Simulation.

Department of ECE, LVS (MTECH), NCETPage 24

Implementation of High Density And Low Leakage Power SRAM

REFERENCES

1. M. Powell, S.-H. Yang, B. Falsafi, K. Roy and T. N. Vijaykumar, Gated-Vdd: A

Circuit Technique to Reduce Leakage in Deep submicron Cache Memories, Proc. Of

International Symposium on Low Power Electronics and Design, pp. 90-95, July

2000.

2. J.C. Park, V. J. Mooney III and P. Pfeiffenberger, Stack Reduction of Leakage

Power, Proc. of the International Workshop on Power and Timing Modeling,

Optimization and Simulation, pp. 148-158, September 2004.

3. J. Park, Stack: a New Approach to Low Power VLSI and Memory,

Ph.D.Dissertation, School of Electrical and Computer Engineering, Georgia Institute

of Technology, 2005.

4. N. Kim, T. Austin, D. Baauw, T. Mudge, K. Flautner, J. Hu, M. Irwin, M. Kandemir

and V. Narayanan, Leakage Current: Moores Law Meets Static Power, IEEE

Computer, vol. 36, pp. 6875, December 2003.

5.

[2] Shyam Akashe, Sushi I Bhushan, High Density and Low Leakage Current Based

5T, 2011 IEEE

6. SajithAhamed and Palatham-Veedu, Design and Analysis of Sense Amplifier

Circuits used in High-Performance and Low-Power SRAMs, The University of

Texas, Austin , 2011.

Department of ECE, LVS (MTECH), NCETPage 25

Implementation of High Density And Low Leakage Power SRAM

7. Gaurav Kumar and Rajpal Sharma,Analytical Study of Sense Amplifier,

International Journal of Advanced Research in Computer Science and Software

Engineering, Vol. 4, Issue 5, p. 431-435, 2014.

Department of ECE, LVS (MTECH), NCETPage 26

Vous aimerez peut-être aussi

- High-Performance D/A-Converters: Application to Digital TransceiversD'EverandHigh-Performance D/A-Converters: Application to Digital TransceiversPas encore d'évaluation

- PXC 3873796Document6 pagesPXC 3873796Sai PraveenPas encore d'évaluation

- Performance of Low Power SRAM Cells On SNM and Power DissipationDocument5 pagesPerformance of Low Power SRAM Cells On SNM and Power DissipationInternational Journal of Application or Innovation in Engineering & ManagementPas encore d'évaluation

- Low Power SramDocument5 pagesLow Power SramPromit MandalPas encore d'évaluation

- Characterization of 6T CMOS SRAM in 65nm and 120nm Technology Using Low Power TechniquesDocument5 pagesCharacterization of 6T CMOS SRAM in 65nm and 120nm Technology Using Low Power TechniquesAnonymous kw8Yrp0R5rPas encore d'évaluation

- Bicta2012 Submission 94Document23 pagesBicta2012 Submission 94Gurinder Pal SinghPas encore d'évaluation

- Analysis of Leakage Reduction Technique On Different SRAM CellsDocument6 pagesAnalysis of Leakage Reduction Technique On Different SRAM Cellssurendiran123Pas encore d'évaluation

- Leakage Current Reduction 6TDocument3 pagesLeakage Current Reduction 6Tshoaib nadeemPas encore d'évaluation

- Dual-Threshold Voltage Techniques For Low-Power Digital CircuitsDocument10 pagesDual-Threshold Voltage Techniques For Low-Power Digital CircuitsSeizalal SingsonPas encore d'évaluation

- A Novel Power Efficient 8T SRAM Cell: Ankush Sindwani Suman SainiDocument5 pagesA Novel Power Efficient 8T SRAM Cell: Ankush Sindwani Suman SainiBanu KiranPas encore d'évaluation

- Nanometer MOSFETDocument12 pagesNanometer MOSFETSibi ManojPas encore d'évaluation

- Surecore Low-Power SRAM Technology IntroductionDocument7 pagesSurecore Low-Power SRAM Technology IntroductionJohn StewardPas encore d'évaluation

- A 256 KB 65 NM 8T Subthreshold SRAM Employing Sense-Amplifier RedundancyDocument9 pagesA 256 KB 65 NM 8T Subthreshold SRAM Employing Sense-Amplifier RedundancyVishva BPas encore d'évaluation

- Improved Stability SRAM Design For Low Power ApplicationsDocument5 pagesImproved Stability SRAM Design For Low Power ApplicationsInternational Journal of Application or Innovation in Engineering & ManagementPas encore d'évaluation

- A Novel Approach To Design SRAM Cells For Low LeakDocument13 pagesA Novel Approach To Design SRAM Cells For Low LeakАндрей ГрозинPas encore d'évaluation

- Ultra-Low Leakage Static Random Access Memory DesignDocument10 pagesUltra-Low Leakage Static Random Access Memory DesignIJRES teamPas encore d'évaluation

- SurajpaperDocument79 pagesSurajpaperSooraj SattirajuPas encore d'évaluation

- WARM SRAM - A Novel Scheme To Reduce Static Leakage Energy in SRAMDocument8 pagesWARM SRAM - A Novel Scheme To Reduce Static Leakage Energy in SRAMapi-19668941Pas encore d'évaluation

- Sram StudyDocument5 pagesSram StudyAjitaSPPas encore d'évaluation

- 05682957Document4 pages05682957Praveenkumar ViswanathanPas encore d'évaluation

- An Ultra-Low-Power 12T Cam Cell Based On Threshold Voltage TechniquesDocument6 pagesAn Ultra-Low-Power 12T Cam Cell Based On Threshold Voltage TechniquesTJPRC PublicationsPas encore d'évaluation

- Design of Low Power Sram: Presentation OnDocument31 pagesDesign of Low Power Sram: Presentation Ondhanaji pawarPas encore d'évaluation

- Designand Analysisof Low Power MTCMOSDocument10 pagesDesignand Analysisof Low Power MTCMOSseshu bradyPas encore d'évaluation

- A 20-Gb/s 1: 2 demultiplexer in 0.18-Μm Cmos: Zhang Changchun , Wang Zhigong , Shi Si , and Li WeiDocument5 pagesA 20-Gb/s 1: 2 demultiplexer in 0.18-Μm Cmos: Zhang Changchun , Wang Zhigong , Shi Si , and Li WeiDuc DucPas encore d'évaluation

- Analysis of Power Efficient Sram Cell For Portable Devices: Swaroop Kumar K, Shabirahmed B J, Narendra K, Asha G HDocument9 pagesAnalysis of Power Efficient Sram Cell For Portable Devices: Swaroop Kumar K, Shabirahmed B J, Narendra K, Asha G HerpublicationPas encore d'évaluation

- IJETR032745Document3 pagesIJETR032745erpublicationPas encore d'évaluation

- Memrisotor Baishaki CSSP 2017Document13 pagesMemrisotor Baishaki CSSP 2017ABM Harun-ur RashidPas encore d'évaluation

- Sub-Threshold Adiabatic Logic For Low Power ApplicationsDocument7 pagesSub-Threshold Adiabatic Logic For Low Power ApplicationsarcherselevatorsPas encore d'évaluation

- Low-Power VLSI Design Using Dynamic-Threshold LogicDocument6 pagesLow-Power VLSI Design Using Dynamic-Threshold LogicravindarsinghPas encore d'évaluation

- Low Power ThesisDocument6 pagesLow Power Thesistiffanybarbermobile100% (2)

- 1 Low-Voltage Current-Mode Analog Cells Mohit Kumar Iit Bomb Ay 2002Document16 pages1 Low-Voltage Current-Mode Analog Cells Mohit Kumar Iit Bomb Ay 2002jaigodaraPas encore d'évaluation

- Gate Level LeakageDocument4 pagesGate Level LeakageMadu KumarPas encore d'évaluation

- SRAM Circuit Design and Operation: Prepared By: Mr. B. H. NagparaDocument49 pagesSRAM Circuit Design and Operation: Prepared By: Mr. B. H. NagparaBharatPas encore d'évaluation

- A Low-Power 8-Read 4-Write Register File DesignDocument4 pagesA Low-Power 8-Read 4-Write Register File DesignEdmund LeongPas encore d'évaluation

- FinFET-Based SRAM DesignDocument6 pagesFinFET-Based SRAM DesignAnil KulshresthaPas encore d'évaluation

- Gated VDD PDFDocument5 pagesGated VDD PDFkruthikah apPas encore d'évaluation

- Low Voltage and Low Power in Sram Read and Write Assist TechniquesDocument9 pagesLow Voltage and Low Power in Sram Read and Write Assist TechniquesIJSTEPas encore d'évaluation

- Sharifkhani 2007Document10 pagesSharifkhani 2007chirag gargPas encore d'évaluation

- Low Voltage and Low Power in SRAM Read and Write Assist TechniquesDocument6 pagesLow Voltage and Low Power in SRAM Read and Write Assist TechniquesIJSTEPas encore d'évaluation

- DFT For SRAMDocument9 pagesDFT For SRAMsuneeldvPas encore d'évaluation

- Low Power SramDocument6 pagesLow Power SramSuresh BharathPas encore d'évaluation

- Pardazeshgar Digital Project English TextDocument10 pagesPardazeshgar Digital Project English Textkazem.khaari77Pas encore d'évaluation

- A Highly Stable 8T SRAM Cell: P.Rama Koteswara Rao and D.Vijaya KumarDocument6 pagesA Highly Stable 8T SRAM Cell: P.Rama Koteswara Rao and D.Vijaya KumarRakeshconclavePas encore d'évaluation

- Low Power Vlsi Design: Assignment-1 G Abhishek Kumar Reddy, M Manoj VarmaDocument17 pagesLow Power Vlsi Design: Assignment-1 G Abhishek Kumar Reddy, M Manoj VarmamanojPas encore d'évaluation

- 9 PDFDocument10 pages9 PDFrajPas encore d'évaluation

- Leakage Compensation Design For SRAM: Keerthi Sagar 180942008Document24 pagesLeakage Compensation Design For SRAM: Keerthi Sagar 180942008Keerthi SagarPas encore d'évaluation

- A Double Regulated Footer and Header Voltage Technique For Ultra-Low Power Iot SramDocument5 pagesA Double Regulated Footer and Header Voltage Technique For Ultra-Low Power Iot SramChaeyoung YooPas encore d'évaluation

- LOW Power ReportDocument16 pagesLOW Power ReportAMIT VERMAPas encore d'évaluation

- Ultra-Low Power 90nm 6T SRAM Cell For Wireless Sensor Network ApplicationsDocument4 pagesUltra-Low Power 90nm 6T SRAM Cell For Wireless Sensor Network Applicationsapi-19668941Pas encore d'évaluation

- Maximum Leakage Power Estimation For CMOS CircuitsDocument9 pagesMaximum Leakage Power Estimation For CMOS Circuitsowais74Pas encore d'évaluation

- Techniques For Low Power VLSI Design: A Novel Analysis of Leakage Power ReductionDocument4 pagesTechniques For Low Power VLSI Design: A Novel Analysis of Leakage Power ReductionSaranya RamaswamyPas encore d'évaluation

- A Novel Four-Transistor SRAM Cell With Low Dynamic Power ConsumptionDocument5 pagesA Novel Four-Transistor SRAM Cell With Low Dynamic Power ConsumptionDinesh SinghPas encore d'évaluation

- 10T SRAM Using Half-V Precharge and Row-Wise Dynamically Powered Read Port For Low Switching Power and Ultralow RBL LeakageDocument11 pages10T SRAM Using Half-V Precharge and Row-Wise Dynamically Powered Read Port For Low Switching Power and Ultralow RBL LeakageDr. Pullareddy AvulaPas encore d'évaluation

- Mesin Mesin ListrikDocument7 pagesMesin Mesin ListrikMerah Mirza YoshiokaPas encore d'évaluation

- 2007 07 A Multi-Mode Power Gating Structure For Low-Voltage Deep-Submicron CMOS ICsDocument5 pages2007 07 A Multi-Mode Power Gating Structure For Low-Voltage Deep-Submicron CMOS ICsKuldeep SinghPas encore d'évaluation

- Design of ALU Circuits Using Pass Transistor LogicDocument71 pagesDesign of ALU Circuits Using Pass Transistor LogicVivek GuntumuduguPas encore d'évaluation

- FORTRAN Based ApproachDocument22 pagesFORTRAN Based ApproachGS EKTAPas encore d'évaluation

- Lo 2011Document10 pagesLo 2011chirag gargPas encore d'évaluation

- LPVLSIDocument21 pagesLPVLSIagarwaltanujta879Pas encore d'évaluation

- Low Power SramDocument7 pagesLow Power SramRohit TiwariPas encore d'évaluation

- HowtousethebookDocument2 pagesHowtousethebookSanjay ChPas encore d'évaluation

- Seminar 1Document8 pagesSeminar 1Ndive Tino OPas encore d'évaluation

- Lowering Power Dissipation and Energy ConsumptionDocument5 pagesLowering Power Dissipation and Energy ConsumptionSanjay ChPas encore d'évaluation

- SQuare Wave Design Using 8051 in C ProgramDocument1 pageSQuare Wave Design Using 8051 in C ProgramSanjay ChPas encore d'évaluation

- Booth MultiplierDocument8 pagesBooth MultipliervikramkolanuPas encore d'évaluation

- Methods and MethodologyDocument1 pageMethods and MethodologySanjay ChPas encore d'évaluation

- Main PaperDocument6 pagesMain PaperSanjay ChPas encore d'évaluation

- Accident MoniotringDocument2 pagesAccident MoniotringSanjay ChPas encore d'évaluation

- AIDocument8 pagesAISanjay ChPas encore d'évaluation

- 145866Document3 pages145866Sanjay ChPas encore d'évaluation

- Sweatha Swamy - Advance Home Automation Using FpgaDocument3 pagesSweatha Swamy - Advance Home Automation Using FpgaSanjay ChPas encore d'évaluation

- Cordic 123Document20 pagesCordic 123Sanjay ChPas encore d'évaluation

- 2Document82 pages2Sanjay ChPas encore d'évaluation

- Double Edge Triggered Feedback Flip-Flop: S. H. Rasouli, A. Amirabadi, A. S. Seyedi and A. Afzali-KushaDocument31 pagesDouble Edge Triggered Feedback Flip-Flop: S. H. Rasouli, A. Amirabadi, A. S. Seyedi and A. Afzali-KushaSanjay ChPas encore d'évaluation

- Low Power ALU Project Phase2Document84 pagesLow Power ALU Project Phase2Sanjay ChPas encore d'évaluation

- Topics For DiplomaDocument3 pagesTopics For DiplomaSanjay ChPas encore d'évaluation

- Chapters Conclusionp2Document8 pagesChapters Conclusionp2Sanjay ChPas encore d'évaluation

- 32 - BitDocument32 pages32 - BitSanjay ChPas encore d'évaluation

- SynopsisDocument4 pagesSynopsisSanjay ChPas encore d'évaluation

- Synopsis 1Document3 pagesSynopsis 1Sanjay ChPas encore d'évaluation

- List of Figures: Figure No. Page NoDocument4 pagesList of Figures: Figure No. Page NoSanjay ChPas encore d'évaluation

- Chapter 1Document10 pagesChapter 1Sanjay ChPas encore d'évaluation

- Final Gdi Verilog11Document5 pagesFinal Gdi Verilog11Sanjay ChPas encore d'évaluation

- Density Based ControllerDocument2 pagesDensity Based ControllerApurva DesaiPas encore d'évaluation

- Ijater 03 06Document6 pagesIjater 03 06nskprasad89Pas encore d'évaluation

- SMS Based Device Control: Sagar MundadaDocument4 pagesSMS Based Device Control: Sagar MundadaSanjay ChPas encore d'évaluation

- 7 Vol 26 No 2Document6 pages7 Vol 26 No 2Din SleyPas encore d'évaluation

- SIM600Document2 pagesSIM600Sanjay ChPas encore d'évaluation

- 101 WhattmeterDocument2 pages101 WhattmeterjcoloniesPas encore d'évaluation

- EE124 Lecture 15 Differential Amplifier Mar 18 Spring 2020 Annotated PDFDocument9 pagesEE124 Lecture 15 Differential Amplifier Mar 18 Spring 2020 Annotated PDFSabeeq KarimPas encore d'évaluation

- BLF 278Document21 pagesBLF 278Emilio Escalante100% (1)

- Elmeasure Split Core CT CatalogDocument1 pageElmeasure Split Core CT CatalogManikandan BPas encore d'évaluation

- Electronics Final Exam 2013Document6 pagesElectronics Final Exam 2013Sahara MalabananPas encore d'évaluation

- EDX-700HS 800HS 900HS SM Rev0ocrDocument196 pagesEDX-700HS 800HS 900HS SM Rev0ocrbozza85100% (3)

- EECS 245 Lab 5 Bipolar Transistor Characteristics and Amplification ObjectiveDocument4 pagesEECS 245 Lab 5 Bipolar Transistor Characteristics and Amplification ObjectiveSarahPas encore d'évaluation

- EEC 242 Syllabus Fall 2020Document5 pagesEEC 242 Syllabus Fall 2020Faheem ParachaPas encore d'évaluation

- EEA PAM 513 A 14Document4 pagesEEA PAM 513 A 14Dalila FregosoPas encore d'évaluation

- Jfets: T N F, P 2: HE EW Rontiers ARTDocument5 pagesJfets: T N F, P 2: HE EW Rontiers ARTzarozePas encore d'évaluation

- Syllabus Instrumentation For Engineers (AET-454)Document3 pagesSyllabus Instrumentation For Engineers (AET-454)rajeevPas encore d'évaluation

- Applying The DAC08: Integrated CircuitsDocument8 pagesApplying The DAC08: Integrated CircuitskondoritoclPas encore d'évaluation

- Ad829 PDFDocument21 pagesAd829 PDFManish KumarPas encore d'évaluation

- Sailor. For Global Communication: Sailor Transmitter T2131 and T2135 Error 83Document5 pagesSailor. For Global Communication: Sailor Transmitter T2131 and T2135 Error 83Camila SuarezPas encore d'évaluation

- I-NX8V2-IM REV H Installation Manual PDFDocument99 pagesI-NX8V2-IM REV H Installation Manual PDFCarbon Nano TubePas encore d'évaluation

- ISFET PH Sensor Characterization - Towards Biosensor Microchip Application (ART) PDFDocument4 pagesISFET PH Sensor Characterization - Towards Biosensor Microchip Application (ART) PDFJaime BarraganPas encore d'évaluation

- B.TECH SyllabusDocument184 pagesB.TECH Syllabusjonas knoxPas encore d'évaluation

- Transistors ApplicationsDocument28 pagesTransistors ApplicationsShahir Afif IslamPas encore d'évaluation

- Optimized Frequency-Shaping Circuit Topologies For LDO's: Gabriel A. Rincon-Mora, and Phillip E. AllenDocument6 pagesOptimized Frequency-Shaping Circuit Topologies For LDO's: Gabriel A. Rincon-Mora, and Phillip E. Allenjulio perezPas encore d'évaluation

- RF CalculatorDocument4 pagesRF CalculatorMuhammad ShahidPas encore d'évaluation

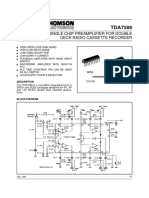

- TDA7286 Single Chip Preamplifier For Double Deck Radio CasseDocument6 pagesTDA7286 Single Chip Preamplifier For Double Deck Radio CasseDunatoMPas encore d'évaluation

- HTP 072Document93 pagesHTP 072hasitha jayawardanaPas encore d'évaluation

- Pin Configuration of Three Legs Variable CapacitorDocument14 pagesPin Configuration of Three Legs Variable CapacitorFernandoPas encore d'évaluation

- LC MOS 8-Bit DAC With Output Amplifiers AD7224: mP-Compatible With Double Buffered InputsDocument8 pagesLC MOS 8-Bit DAC With Output Amplifiers AD7224: mP-Compatible With Double Buffered InputsAleksandr MakushinPas encore d'évaluation

- Exploring Sound Worksheet 5 1 1 1Document3 pagesExploring Sound Worksheet 5 1 1 1api-641450739Pas encore d'évaluation

- Resonant Filter Sweeps Asr and Eps-16 Plus: in TheDocument16 pagesResonant Filter Sweeps Asr and Eps-16 Plus: in TheAnonymous QgauLK2jdnPas encore d'évaluation

- AEDFA BO 13 - AEDFA BO 18 - AEDFA BO 23 - AEDFA PA 30 - AEDFA PA 35 - Specs - NaDocument2 pagesAEDFA BO 13 - AEDFA BO 18 - AEDFA BO 23 - AEDFA PA 30 - AEDFA PA 35 - Specs - NaAnonymous 60esBJZIjPas encore d'évaluation

- Operation 1Document43 pagesOperation 1Michelle RomulPas encore d'évaluation

- Datasheet PDFDocument11 pagesDatasheet PDFMaugrys CastilloPas encore d'évaluation

- Lesson-4 Circuit ComponentsDocument21 pagesLesson-4 Circuit ComponentsThevenin Norton TOng TongPas encore d'évaluation