Académique Documents

Professionnel Documents

Culture Documents

Charge Pumps

Transféré par

BLUEE009Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Charge Pumps

Transféré par

BLUEE009Droits d'auteur :

Formats disponibles

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-1

LECTURE 120 FILTERS AND CHARGE PUMPS

(READING: [4,6,9,10])

Objective

The objective of this presentation is examine the circuits aspects of loop filters and

charge pumps suitable for PLLs in more detail.

Outline

Filters

Charge Pumps

Summary

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-2

FILTERS

Why Does the PLL Need a Filter?

Input

Signal

Phase

Frequency

Detector

Oscillator

Output

Signal

Error

Signal

Voltage

Controlled

Oscillator

Loop

Filter

Contolling

Voltage

Fig. 01-01

The loop filter is important to the performance of the PLL.

1.) Removes high frequency noise of the detector

2.) Influences the hold and capture ranges

3.) Influences the switching speed of the loop in lock.

4.) Easy way to change the dynamics of the PLL

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-3

Passive Loop Filters

R1

1

1

1.) F(s) =

=

=

sR1C1 + 1 1 + s1,

1

R1+sC1

R1

1 = R1C1

C1

Fig. 3.1-26

2.) F(s) =

1

R2 + sC

1

R1 + R2+ sC

1 = C(R1 + R2)

1 + s2

sCR2 + 1

= sC (R1 + R2) + 1 = 1 + s1

R1

C

and

2 = R2C

R2

Advantages:

Fig. 3.1-27

Linear

Relatively low noise

Unlimited frequency range

Disadvantages:

Hard to integrate when the values are large (C>100pF and R > 100k)

Difficult to get a pole at the origin (increase the order of the type of PLL)

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Active Filters

1.) Active lag filter-I

1

R2 + sC2

C1 sR2C2 + 1

F(s) = =

C sR C + 1

1

1 1

2

R1 + sC1

C1 s2 + 1

= -C2 s1 + 1 , 1 = R1C1 and 2 = R2C2

2.) Active lag filter II

1

R2sC2

1

R2 + sC2

R2 sR1C1+1

R2 s1 + 1

=

=

F(s) =

R s + 1

1

R

C

+1

sR

1

2

2

1

2

R1sC1

1

R1 + sC1

ECE 6440 - Frequency Synthesizers

Page 120-4

C1

R1

C2

R2

+

Fig. 3.1-28

R1

C1

R2

C2

+

Fig. 3.1-29

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-5

Active Filters - Continued

3.) Active PI filter.

1

R2 + sC2

sR2C2 + 1

s2 + 1

= - sR C = - s

F(s) = - R1

1 2

1

R1

R2

C2

1 = R1C2 and 2 = R2C2

+

Advantages:

Fig. 3.1-30

Can get poles at the origin

Can reduce the passive element sizes using transresistance

R12

R2

R1

R1

We can show that R1(eq.) = 2R1 + Rx

Vin

Assume R1 = 10k and Rx = 10

i1

Rx

100,000k

+

10M

gives R1(eq.) = 20k +

10

Disadvantages:

Noise

Power

Frequency limitation

ECE 6440 - Frequency Synthesizers

C2

Fig. 3.1-31

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-6

Higher-Order Active Filters

1.) Cascading first-order filters (all poles are on the negative real axis)

Uses more op amps and dissipates more power.

2.) Extending the lag-lead filter.

Vin

R1

2

R1

2

C3

R2

C2

Vout

+

Fig. 120-02

From the previous slide we can write,

sR1C3

sR2C2+1

Z2(s) = sC2

Z1(s)(eq.) = R1 4 +1 and

sR2C2+1

s2+1

Vout

sC2

sR2C2+1

=

=

Vin = - sR C

sR1C3

s1(s3+1)

1 3

sC2R1 4 +1

R1 4 +1

where 1 = R1C2, 2 = R2C2, and 3 = 0.25R1C3

The additional pole could also be implemented by an RC network at the output.

However, now the output resistance is not small any more.

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-7

Non-Idealities of Active Filters

DC Offsets:

Example

vin R1

Model

VIO

IOS

R2

vout

vin

R1

VIO

R2

vout

IOS

+

Fig. 120-01

What is the input and output offset voltages of this example?

R2

Output offset voltage = VOS(out) = R1 VIO + R2IOS

Input offset voltage = VOS(in) = -VIO + R1IOS

Assume the op amp is a 741 with VIO = 3mV, IOS = 100nA, and R1 = R2 = 10k.

VOS(out) = 3mV + 10k100nA = 4mV

VOS(in) = -3mV + 10k100nA = -2mV

We have seen previously that these input offset voltages can lead to large spurs in the

PLL output.

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-8

Non-Idealities of Active Filters - Continued

Inverting and Noninverting Amplifiers:

R2

R1

vIN

vOUT

vIN

R2

R1

vOUT

Fig. 9.2-01

Gain and GB = :

Vout R1+R2

Vin = R1

Gain , GB = :

Avd(0)R1

R1+R2

Vout(s) R1+R2

=

Vin(s) R1

Avd(0)R1

1 + R1+R2

Gain , GB :

GBR1

R1+R2 H

Vout(s) R1+R2 R1+R2

GBR1 = R1 s+H

Vin(s) = R1

s + R1+R2

ECE 6440 - Frequency Synthesizers

Vout

R2

=

Vin

R1

R1Avd(0)

R2

R1+R2

Vout(s)

Avd(0)R1

Vin(s)

R1

1 + R1+R2

GBR1

R2 H

Vout(s) R2 R1+R2

=

=

GBR1 - R1 s+H

Vin(s) R1

s + R1+R2

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-9

Non-Idealities of Active Filters - Continued

Example:

Assume that the noninverting and inverting voltage amplifiers have been designed for

a voltage gain of +10 and -10. If Avd(0) is 1000, find the actual voltage gains for each

amplifier.

Solution

For the noninverting amplifier, the ratio of R2/R1 is 9.

1000

Avd(0)R1/(R1+R2) = 1+9 = 100.

Vout

100

V = 10 101 = 9.901 rather than 10.

in

For the inverting amplifier, the ratio of R2/R1 is 10.

Avd(0)R1 1000

R1+R2 = 1+10 = 90.909

Vout

90.909

V = -(10)1+90.909 = - 9.891 rather than -10.

in

ECE 6440 - Frequency Synthesizers

Lecture 120 Filters and Charge Pumps (6/9/03)

P.E. Allen - 2003

Page 120-10

Non-Idealities of Active Filters - Continued

Finite Gainbandwidth:

Assume that the noninverting and inverting voltage amplifiers have been designed for

a voltage gain of +1 and -1. If the unity-gainbandwidth, GB, of the op amps are

2Mrads/sec, find the upper -3dB frequency for each amplifier.

Solution

In both cases, the upper -3dB frequency is given by

GBR1

H = R1+R2

For the noninverting amplifier with an ideal gain of +1, the value of R2/R1 is zero.

H = GB = 2 Mrads/sec (1MHz)

For the inverting amplifier with an ideal gain of -1, the value of R2/R1 is one.

GB1 GB

H = 1+1 = 2 = Mrads/sec (500kHz)

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-11

Non-Idealities of Active Filters - Continued

Integrators Finite Gain and Gainbandwidth:

Avd(s) (s/)

Avd(s) sR1C2

I

Vout 1 sR1C2 + 1

(s/) + 1

=

=

Vin

Avd(s) (s/)

Avd(s) sR1C2 s

sR1C2

1 + (s/) + 1

1 + sR1C2+1

Avd(0)a GB GB

where

Avd(s) = s+a = s+a s

Vout

Case 1: s 0 Avd(s) = Avd(0) Vin - Avd(0)

GB I

GB

Vout

V - s s

Case 2: s Avd(s) = s

in

Vout

I

Case 3: 0 < s < Avd(s) =

V - s

in

|Vout(j)/Vin(j)|

Arg[Vout(j)/Vin(j)]

I

180

10Avd(0) 10I

135

Avd(0)

Avd(0) dB

Eq. (3)

Eq. (1)

0 dB

I

x1 = I

Avd(0)

x2 = GB

log10

90

45

0

Eq. (2)

GB

10

10GB

I

Avd(0)

GB

log10

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-12

CHARGE PUMPS

The use of the PFD permits the use of a charge pump in place of the conventional PD and

low pass filter. The advantages of the PFD and charge pump include:

The capture range is only limited by the VCO output frequency range

The static phase error is zero if the mismatches and offsets are negligible.

A

VDD

I1

A

QA

PFD

I1=I2=I

Fig. 12.4-2N

X

Vout

QB

Cp

Y

I2

QA

QB

Vout

QA high deposits charge on Cp (A leads B).

QB high removes charge from Cp (B leads A).

QA and QB low Vout remains constant.

We have seen that a resistor in series with Cp is necessary for stability.

(QB is high for a short time due to reset delay but the difference between average values

between QA and QB still accurately represents the input phase or frequency difference.)

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-13

Types of Charge Pumps

Conventional Tri-Stage

Low power consumption, moderate speed, moderate clock skew

Low power frequency synthesizers, digital clock generators

Current Steering

Static current consumption, high speed, moderate clock skew

High speed PLL (>100MHz), translation loop, digital clock generators

Differential input with Single-Ended output

Medium power, moderate speed, low clock skew

Low-skew digital clock generators, frequency synthesizers

Fully Differential

Static current consumption, high speed (>100MHz)

Digital clock generators, translation loop, frequency synthesizer (with on-chip filter)

Advantages of charge pumps

Consume less power than active filters

Have less noise than active filters

Do not have the offset voltage of op amps

Provide a pole at the origin

More compatible with the objective of putting the filter on chip

ECE 6440 - Frequency Synthesizers

Lecture 120 Filters and Charge Pumps (6/9/03)

P.E. Allen - 2003

Page 120-14

Nonidealities in Charge Pumps

Leakage current:

Small currents that flow when the switch is off.

Mismatches in the Charge Pump:

The up and down (charge and discharge) currents are unequal.

Timing Mismatch in PFD:

Any mismatch in the time at which the PFD provides the up and down outputs.

Charge Sharing:

The presence of parasitic capacitors will cause the charge on the desired capacitor to

be shared with the parasitic capacitors.

Woogeun Rhee, Design of High-Performance CMOS Charge Pumps in Phase-Locked Loops, Proc. of 1999 ISCAS, Page II-545-II548, May

1999.

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Charge Pumps

The low pass filter in the PLL

can be implemented by:

1.) Active filters which require

an op amp

2.) Passive filters and a charge

pump.

The advantages of a charge

pump are:

Reduced noise

Reduced power

consumption

No offset voltage

Page 120-15

VDD

Up

MP3

Up

VDD

MP5

IP

IP1

IP2

Iout

VDD

Vc

Dn

IP

MP1

MP4

Up

IN1

Passive

Filter

MP2

IN2

MN3

MN5

Dn

MN4

MN1

MN2

Dn

Fig. 12.4-22

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-16

Discriminator-Aided PFD/Charge Pump

This circuit reduces the pull-in time, TP, and enhances the switching speed of the PLL

while maintaining the same noise bandwidth and avoiding modulation damping.

Technique:

Increase the gain of the phase detector for increasing values of phase error.

iP

iP

Characteristic of a Conventional PD

-AD

AD

Characteristic of a Nonlinear PD

Fig. 3.1-32

The gain of the phase detector is increased when e becomes larger than AD or

smaller than -AD. During the time the phase detector gain has increased by k, the loop

filter bandwidth is also increased by k.

C-Y Yang and S-I Liu, Fast-Switching Frequency Synthesizer with a Discriminator-Aided Phase Detector, IEEE J. of Solid-State Circuits, Vol. 35,

No. 10, Oct. 2000, pp. 1445-1452.

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-17

Discriminator-Aided Phase Detector (DAPD) Continued

Schematic of a phase detector with DAPD and charge-pump filter:

VDD

VDD

(k2-1)Ip0

Ip0

Vi

Vc

PD

V

Vosc

D

Rz

If the absolute value of

the delay between Vi

and Vosc is greater

than AD, the output

signal of the DAPD is

high and increases the

charge pump current

by k2 and adjusts the

loop filter bandwidth.

Ip0

(k2-1)Ip0

Cp

RAD

VDD

R

Delay

AD

Cz

Low Pass DAD

Filter

PD

D

FLD

VDD

R

Delay

AD

Low Pass UAD

Filter

Discriminator-Aided

Phase Detector

PD

V

Fig. 3.1-33

0.35m CMOS: Switching time for a 448 MHz to 462 MHz step is reduced from 90s to

15s (k = 3).

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-18

A Type-I Charge Pump

This PLL uses an on-chip, passive discrete-time loop filter with a single state, chargepump to implement the loop filter. The stabilization zero is created in the discrete-time

domain rather than using RC time constants.

Block diagram of the Type-I, charge pump PLL frequency synthesizer:

(Test chip)

Sampling pulse

generation

Clock

buffer

Clk

Vref

Up

Two state

PFD

Vdiv

Charge

Pump

Vcp

Clkb Reset

Discrete-time

Vh

domain loop filter

RC low pass filter

(optional)

Upb

Programmable

divider

VCO

Vtune

Fig. 120-03

B. Zhang, P.E. Allen and J.M. Huard, A Fast Switching PLL Frequency Synthesizer With an On-Chip Passive Discrete-Time Loop Filter in 0.25m

CMOS, IEEE J. of Solid-State Circuits, vol. 38, no. 6, June 2003, pp. 855-865.

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-19

Type-I Charge Pump Continued

Comparison of a conventional 3-state PFD and a 2-state PFD:

Vdd

Vref

Up

Vdd

Upb

Vref

Clk Qb

Rst

Up

Clk Qb

Rst

NAND

Vdiv

NAND

Rst

Clk Qb

Rst

Clk Qb

Vdiv

Dn

Conventional 3-state PFD

Q

2-state PFD

Fig. 120-04

Dual polarity and single polarity charge pumps:

ID

Up

Vcp

ID

Up

Vcp

Dn

Cload

ID

Dual Polarity

Single Polarity

Fig. 120-05

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-20

Single Polarity Charge Pump

VDD

M4

M6

M5

M7

IBias

Vcp

R

Upb

Up

M8

M12

M9

M10

Fig. 120-07

No matching problems.

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-21

Type-I Charge Pump Continued

The discrete-time loop filter:

S1

Vcp

S2

Vch

Cs

Ch

Fig120-06

klff1(s)

s

where z = esTs, Ts is the sampling period (S1), klf is a gain constant, and f1(s) accounts for

the loading effect of the low pass filter.

The open-loop transfer function of this system is given as,

KdKoklff1(s)

KdKoklff1(s) TsKdKoklff1(s)

T(s)

=

(sT

)

=

T(s) = (1-z-1)

s

sN

s2N

s2N

which is a Type I system if <<2/Ts.

F1(s) (1-z-1)

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-22

Type-I Charge Pump Continued

Clock generator and clock waveforms:

Discrete-time loop filter:

VDD

M17

VDD

M18

M19

M20

PRE

Enable

Vs

2

3

CLK

Clk

M30 M31 M34

Vcp

Vh

CLR

M35

Reset

1

VDD

VDD

M4

M8

VDD

M23

VDD

M24

VDD

M28

M6

M7

M25

M26

M27

M29 M33 M32

Cs

Ch

Clkb

VDD

VDD

VDD

M16

M12

M10

M15

M11

M9

Fig. 120-07

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-23

Type-I Charge Pump Continued

Comparison of the frequency response of the conventional and single state architectures:

Conventional architecture

Single-state architecture

Results:

Conventional Architecture

-53dBc

140s

Off-chip filter

Reference spur

Switching time

Loop filter size

Type-I Architecture

-62dBc

30s

Integrated (70pF)

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-24

Use of Active Filters with Charge Pumps

Second-Order PLL:

VDD

VDD

IP

Up

IP

Up

Vcp

Dn

R1

Dn

Vcp

R1

IP

C1

+

IP

C1

Fig. 120-09

PLL Crossover Frequency:

Kv

K22 + K44 + 4 K4

c2 =

where K = NC1

2

PLL Settling Time for a Frequency step of :

2

ts2 c2

1+

ECE 6440 - Frequency Synthesizers

4

1+ K44

ln

2

1- 2 2

(ts2)

where = ()

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-25

Charge Pump with a Third-Order Filter

The additional pole of a

VDD

third-order PLL provides

IP

more spurious suppression.

However, the phase lag

Up

associated with the pole

introduces a stability issue. Dn

R1

Circuit:

IP

C1

VDD

IP

Up

Vcp

C2

C1

R1

Dn

Vcp

C2

IP

Fig. 120-10

The impedance of the loop filter is,

C1

s +1

b

and b = C2

Z(s) = b+1

s

where = R1C1

s2C1b+1 +1

The loop gain for this PLL is

KoIP b

s +1

LG(s) = - 2N b+1

s

s2C1b+1 +1

The phase margin of the loop is,

c3

-1

-1

where c3 is the crossover frequency

PM = tan (c3) - tan b+1

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-26

Charge Pump with a Third-Order Filter Continued

Differentiating with respect to c3, shows that max. phase margin occurs when

c3 = b+1 /

1

b+1

Maximum phase margin as a function of b = C1/C2.

PM(max) = tan-1( b+1 ) - tan-1

Phase Margin (Degrees)

80

70

60

50

40

30

20

10

0

20

40

60

b = C1/C2

80

100

Fig. 120-11

Note that for b 1, the phase margin is less than 20.

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-27

ts3/Ti = ts3/Tref

Charge Pump with a Third-Order Filter Continued

An analytical expression for settling time is difficult to calculate for the third-order filter.

The following figure shows the simulated settling time to 10ppm accuracy as a function of

phase margin when /N = 0.04 (i = ref).

Phase Margin - Degrees

For /N < 0.04 and 20<PM<79, we may estimate the settling time to 10ppm accuracy

as

2

ts3 c3 [0.0067PM2 0.6303PM + 16.78]

ECE 6440 - Frequency Synthesizers

Lecture 120 Filters and Charge Pumps (6/9/03)

P.E. Allen - 2003

Page 120-28

Charge Pump with a Third-Order Filter Continued

A loop filter design recipe:

1.) Find Kv for the VCO.

2.) Choose a desired PM and find b from the max. PM equation.

3.) Choose the crossover frequency, c3, and find from c3 = b+1 /.

4.) Select C1 and IP such that they satisfy

IPKv b C1

2N b+1 = 2 b+1

5.) Calculate the noise contribution of R12. If the calculated noise is negligible the design

is complete. If not, then go back to step 4.) and increase C1.

Example: Let Kv = 107 rads/sec., N = 1000, PM = 50 and f c3 = 10kHz.

1

b 6.65 (by iteration)

Now, 50 = tan-1( b+1 ) - tan-1

b+1

b+1

6.65+1

= 2f c3 = 21000 = 0.44 msec

IPKv b 2

If IP = 200A, then C1 = 2N b+1

= 19.34 nF R1 = C1 = 22.72k

b+1

Noise = 4kTR = 4(1.38x10-23)(300)(22.72k) = 3.76x10-16 V2/Hz

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-29

Charge Pump with a Fourth-Order Filter

To further reduce the spurs with out decreasing the crossover frequency and thereby

increasing the settling time, an additional pole needs to be added to the loop.

Circuit:

VDD

VDD

IP

IP

Up

R3

Vcp

Dn

Up

R1

Dn

R1

IP

C1

C2

C3

C2

IP

C1

-+

+

R3

Vcp

C3

Fig. 120-12

The impedance of the passive filter is given as,

s + 1

Z(s) =

C2 C3

sC11+ C + C B(s)2 + As + 1

1

1

where

2 C2

1+b 1+C1

b 2C2

,

B

=

A=

1+b

1+b C1 , = R1C1, 3 = R3C3 and

C1

b = C2+C3

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-30

Charge Pump with a Fourth-Order Filter Continued

Phase margin:

A(c4)

PM = tan-1(c4) - tan-11-B( )2 where c4 = crossover frequency

c4

The maximum phase margin is obtained when the derivative of the above equation with

respect to c4 is set to zero. The results are:

2B+AB+A-A2 2

1 2B+AB+A-A2

4(1-A)

+

2 B(B-A)

B(B-A) B(B-A)

For c4 to be the crossover frequency, it must satisfy the following equation,

1

c4 =

1+(c4)2

1+b

2

=

C

2

2

2

1 b c4

(Ac4) +[1-B(c4) ]

Practical simplifications:

IPKv

2N

C2

A positive phase margin Zero lower than the two high frequency poles C1 < 1

For the fourth pole not to decrease the phase margin it has to be more than a decade

2

away from the zero, therefore, b << 1.

With these conditions we find that B << A.

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-31

Charge Pump with a Fourth-Order Filter Continued

If B << A, then the previous relationships become,

IPKv b C1

1

1+b

1

A 1+b , c4

and 2N 1+b 2 1+b

A

The maximum phase margin also simplifies to,

1

PM(max) tan-1( 1+b) - tan-1

1+b

Exact phase margin:

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-32

t4/Ti = ts4/Tref

Charge Pump with a Fourth-Order Filter Continued

Simulation is used to estimate the settling time of the fourth-order loop to 10 ppm

accuracy when /N < 0.04:

Phase Margin - Degrees

Note that the settling time at a given phase margin is independent of 2/ and is the same

as that of a third-order loop.

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-33

Charge Pump with a Fourth-Order Filter Continued

Spur suppression of the fourth-order filter.

ECE 6440 - Frequency Synthesizers

Lecture 120 Filters and Charge Pumps (6/9/03)

P.E. Allen - 2003

Page 120-34

Charge Pump with a Fourth-Order Filter Continued

Loop filter design procedure:

1.) Find Kv for the VCO.

2.) Choose a desired phase margin and find b. (If PM = 50, then b = 6.5)

3.) Choose the crossover frequency c4 and find . ( 2.7/c4 if b = 6.5)

4.) Choose the desired spur attenuation and find 2/ from the previous page.

IPKv b C1

5.) Select C1 and IP such that they satisfy 2N 1+b 2 1+b .

6.) Calculate the noise contribution of R1 and R3.

Example: Let Kv = 107 rads/sec., N = 1000, PM = 50, f c4 = 1kHz and fref = 100kHz.

Since PM = 50, b = 6.5

2.7/c4 = 2.7/(21000) = 430sec.

Let us choose 2/ as 0.1 which corresponds to about 90dB of suppression.

IPKv b 2

If IP = 200A, then C1 = 2N b+1

= 18.63 nF R1 = C1 = 23.09k

b+1

2 = 0.1 = 43sec

If C3 = 1nF, then R3 = 2/C3 = 43sec/1nF = 43k

Noise: vR12 = 4kTR1 = 3.823 x10-16 V2/Hz and vR32 = 4kTR3 = 7.12 x10-16 V2/Hz

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-35

Charge Pump with a Fourth-Order Filter Continued

Open loop transfer function for a typical fourth-order PLL:

PSPICE File:

dB or Degrees

Fourth-order, charge-pump PLL loop gain

.PARAM N=1000, KVCO=1E7, T=0.43E-3, T2=43E-6, KD=1, E=10

.PARAM A=0.2287 B=0.00868

*VCO Noise Transfer Function

VIN 1 0 AC 1.0

RIN 1 0 10K

EDPLL1 2 0 LAPLACE {V(1)}=

+{-KD*KVCO*46.52E6*(S*T+1)/(S+E)/(S+E)/(B*T*T*S*S+A*T*S+1)}

RDPLL1 2 0 10K

*Steady state AC analysis

.AC DEC 20 10 100MEG

250

.PRINT AC VDB(2) VP(2)

.PROBE

200

.END

150

Phase Shift

Magnitude

100

50

Phase Margin 90

0

-50

-100

10

100

1000

ECE 6440 - Frequency Synthesizers

104

105

Frequency (Hz)

106

107

108

Fig. 120-13

P.E. Allen - 2003

Lecture 120 Filters and Charge Pumps (6/9/03)

Page 120-36

SUMMARY

Filters

Determines the dynamic performance of the PLL

Active and passive filters

Order of the filter higher the order, the more noise and spur suppression

Nonidealities of active filters

- DC offsets

- Finite op amp gain

- Finite gain-bandwidth

- Noise

Charge Pumps

Avoid the use of the op amp to achieve a pole at the origin (Type-II systems)

Nonidealities in charge pumps

- Leakage current

- Mismatches in the up and down currents

- Timing mismatches

- Charge sharing

ECE 6440 - Frequency Synthesizers

P.E. Allen - 2003

Vous aimerez peut-être aussi

- 110 Waveform Generator Projects for the Home ConstructorD'Everand110 Waveform Generator Projects for the Home ConstructorÉvaluation : 4 sur 5 étoiles4/5 (1)

- AN-1141 Application Note: Powering A Dual Supply Precision ADC With Switching RegulatorsDocument8 pagesAN-1141 Application Note: Powering A Dual Supply Precision ADC With Switching RegulatorsVINITA AGARWALPas encore d'évaluation

- HS-2420RH - Fast Sample and HolDocument8 pagesHS-2420RH - Fast Sample and HolDeepa DevarajPas encore d'évaluation

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Pas encore d'évaluation

- Ch2a Op Amp v3Document66 pagesCh2a Op Amp v3sadyehclenPas encore d'évaluation

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Évaluation : 2.5 sur 5 étoiles2.5/5 (3)

- IRG4BC30K-S: Features Features Features Features FeaturesDocument8 pagesIRG4BC30K-S: Features Features Features Features FeaturesRafael MonzonPas encore d'évaluation

- The Improved Howland Current Pump: by Tim Green - PA-Linear Applications Engineering ManagerDocument8 pagesThe Improved Howland Current Pump: by Tim Green - PA-Linear Applications Engineering ManagermfqcPas encore d'évaluation

- 741Document9 pages741Dimuthu DharshanaPas encore d'évaluation

- S T K 4 2 3 1 I I 2-Channel Loowmin Af Power Amp (Dual Supplies)Document8 pagesS T K 4 2 3 1 I I 2-Channel Loowmin Af Power Amp (Dual Supplies)Arthur JonesPas encore d'évaluation

- Exercises in Electronics: Operational Amplifier CircuitsD'EverandExercises in Electronics: Operational Amplifier CircuitsÉvaluation : 3 sur 5 étoiles3/5 (1)

- OPA277Document9 pagesOPA277Ahtesham KhanPas encore d'évaluation

- Analog Circuit Design Volume 2: Immersion in the Black Art of Analog DesignD'EverandAnalog Circuit Design Volume 2: Immersion in the Black Art of Analog DesignPas encore d'évaluation

- Av02 0752enDocument8 pagesAv02 0752ench.navnPas encore d'évaluation

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsD'EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsPas encore d'évaluation

- Directional Relay Sip BDocument12 pagesDirectional Relay Sip BAnonymous fU04Z4clPas encore d'évaluation

- Operational Amplifier Circuits: Analysis and DesignD'EverandOperational Amplifier Circuits: Analysis and DesignÉvaluation : 4.5 sur 5 étoiles4.5/5 (2)

- Opa 2353Document27 pagesOpa 2353Hoang Văn ThịnhPas encore d'évaluation

- 110 Integrated Circuit Projects for the Home ConstructorD'Everand110 Integrated Circuit Projects for the Home ConstructorÉvaluation : 4.5 sur 5 étoiles4.5/5 (2)

- Universal DC/DC Converter: (Top View)Document11 pagesUniversal DC/DC Converter: (Top View)Engine Tuning UpPas encore d'évaluation

- Applications Features: 1988 Burr-Brown Corporation PDS-837E Printed in U.S.A. October, 1997Document10 pagesApplications Features: 1988 Burr-Brown Corporation PDS-837E Printed in U.S.A. October, 1997Arjuna Ajita Ananta VijayaPas encore d'évaluation

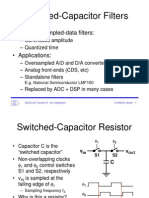

- Switched-Capacitor Filters: - "Analog" Sampled-Data FiltersDocument24 pagesSwitched-Capacitor Filters: - "Analog" Sampled-Data FiltersPushpendra DwivediPas encore d'évaluation

- Applications FeaturesDocument12 pagesApplications FeatureseduardofelisPas encore d'évaluation

- Ultralow Noise, High Speed, Bifet Op Amp: 冑Hz At 10 Khz V P-P, 0.1 Hz To 10 Hz 冑Hz Current Noise At 1 Khz S Slew RateDocument12 pagesUltralow Noise, High Speed, Bifet Op Amp: 冑Hz At 10 Khz V P-P, 0.1 Hz To 10 Hz 冑Hz Current Noise At 1 Khz S Slew RateVasily KorolevPas encore d'évaluation

- 0574.solving Op Amp Stability 2013 - Part 2Document60 pages0574.solving Op Amp Stability 2013 - Part 2diadddPas encore d'évaluation

- PNP General Purpose Amplifier: Absolute Maximum RatingsDocument10 pagesPNP General Purpose Amplifier: Absolute Maximum Ratingsmike_helplinePas encore d'évaluation

- OPA2134 TI DatasheetDocument14 pagesOPA2134 TI DatasheetJhenuPas encore d'évaluation

- Setting Calulation For Gen Tms TRF and BusbarDocument10 pagesSetting Calulation For Gen Tms TRF and BusbarVíctor Rojas100% (1)

- Features Description: FM IF SystemDocument7 pagesFeatures Description: FM IF Systemlu1agpPas encore d'évaluation

- Opa 134 DatasheetDocument19 pagesOpa 134 DatasheetNikos SpirouPas encore d'évaluation

- CNT74 4Document8 pagesCNT74 4Juan Carlos H. SoriaPas encore d'évaluation

- 25W Mono Amplifier With Mute/St-By: DescriptionDocument9 pages25W Mono Amplifier With Mute/St-By: Descriptiondunc4ntPas encore d'évaluation

- Datasheet 741Document5 pagesDatasheet 741Lucas Ernesto Caetano ErnestoPas encore d'évaluation

- Simple Op Amp Measurements: by James M. BryantDocument3 pagesSimple Op Amp Measurements: by James M. BryantFer TgPas encore d'évaluation

- MV Network Design Answer Book en Schneider Electric Date 2112009Document37 pagesMV Network Design Answer Book en Schneider Electric Date 2112009Anonymous kdFzbQ4jfPas encore d'évaluation

- Ami Gyro Coverter KW960C - ManDocument11 pagesAmi Gyro Coverter KW960C - ManZaw Khaing WinPas encore d'évaluation

- Rectifier Expt With Prelab QuestionsDocument11 pagesRectifier Expt With Prelab Questionskishorejerry54Pas encore d'évaluation

- Ultralow Noise Bifet Op Amp Ad743: MV P-P, 0.1 HZ To 10 HZDocument12 pagesUltralow Noise Bifet Op Amp Ad743: MV P-P, 0.1 HZ To 10 HZRicardo Teixeira de AbreuPas encore d'évaluation

- 4 N 35Document7 pages4 N 35Muhammad KrisdiyantoPas encore d'évaluation

- Module 2 Op-AmpDocument26 pagesModule 2 Op-AmpSTUDENTS OF DOE CUSATPas encore d'évaluation

- Ring OscillatorDocument12 pagesRing OscillatorCmeLiv InmyHart NpaynoRentPas encore d'évaluation

- IGBT Plasma Panasonic Placa Ysus IRG4BC40UDocument8 pagesIGBT Plasma Panasonic Placa Ysus IRG4BC40UAntonio ChavezPas encore d'évaluation

- OPA131 OPA2131 OPA4131: FeaturesDocument8 pagesOPA131 OPA2131 OPA4131: FeaturesBhargav TulabandulaPas encore d'évaluation

- CN0350Document7 pagesCN0350Narayan AptePas encore d'évaluation

- LTC 1052Document25 pagesLTC 1052roozbehxoxPas encore d'évaluation

- Icl 8038 DataDocument10 pagesIcl 8038 DataTushar Kanti BeraPas encore d'évaluation

- Mini Tutorial: Multiple Feedback FiltersDocument3 pagesMini Tutorial: Multiple Feedback FiltersSigifredo R. DarciaPas encore d'évaluation

- G4PC40UDocument10 pagesG4PC40URICHIHOTS2Pas encore d'évaluation

- RC Phase Shift Oscillator and RC Coupled Ce Amplifier - Lab ExperimentDocument8 pagesRC Phase Shift Oscillator and RC Coupled Ce Amplifier - Lab ExperimentMani BharathiPas encore d'évaluation

- Ivc102 DatasheetDocument15 pagesIvc102 DatasheetChristian CândidoPas encore d'évaluation

- OPA277 OPA2277 OPA4277: Description FeaturesDocument25 pagesOPA277 OPA2277 OPA4277: Description FeaturesErtan UysalPas encore d'évaluation

- Basic Op-Amp Circuits: EE 126 - Industrial Electronics Handout: Operational Amplifiers Operational Amplifiers (Op-Amps)Document6 pagesBasic Op-Amp Circuits: EE 126 - Industrial Electronics Handout: Operational Amplifiers Operational Amplifiers (Op-Amps)kyope17Pas encore d'évaluation

- Ir Music TransmitterDocument20 pagesIr Music TransmitterYedla Avinash Lucky'sPas encore d'évaluation

- Opa 2132Document18 pagesOpa 2132Shree RaamPas encore d'évaluation

- Data SheetDocument35 pagesData SheetvvvssssvvvPas encore d'évaluation

- Ssm3k36mfv 0.5a20v Sot-VesmDocument5 pagesSsm3k36mfv 0.5a20v Sot-VesmBLUEE009Pas encore d'évaluation

- Esd Esd9b5.0st5g 5v 1a Sod923 RohsDocument4 pagesEsd Esd9b5.0st5g 5v 1a Sod923 RohsBLUEE009Pas encore d'évaluation

- Analog Devices PSRRDocument3 pagesAnalog Devices PSRRBLUEE009Pas encore d'évaluation

- NPN BRT Dtc143tm3t5g (Sot-723) RohsDocument10 pagesNPN BRT Dtc143tm3t5g (Sot-723) RohsBLUEE009Pas encore d'évaluation

- VARISTOR CHIP 5.5V20A 100PF 0402 RoHSDocument10 pagesVARISTOR CHIP 5.5V20A 100PF 0402 RoHSBLUEE009Pas encore d'évaluation

- Led Philips Flash Led 2.04X1.64X0 - 0.7MMDocument13 pagesLed Philips Flash Led 2.04X1.64X0 - 0.7MMBLUEE009Pas encore d'évaluation

- LQP03TN - 02 Series 0603 (MM) 0201 (Inch)Document4 pagesLQP03TN - 02 Series 0603 (MM) 0201 (Inch)BLUEE009Pas encore d'évaluation

- LQG15HS Series (0402 Size)Document2 pagesLQG15HS Series (0402 Size)BLUEE009Pas encore d'évaluation

- Miniflex 5-Bfn Ii: 0.5mm PitchDocument2 pagesMiniflex 5-Bfn Ii: 0.5mm PitchBLUEE009Pas encore d'évaluation

- Property of Lite-On Only FeaturesDocument11 pagesProperty of Lite-On Only FeaturesBLUEE009Pas encore d'évaluation

- Host-Side Single Cell Lithium Battery Gauge: General Description FeaturesDocument14 pagesHost-Side Single Cell Lithium Battery Gauge: General Description FeaturesBLUEE009Pas encore d'évaluation

- Fpf1203 / Fpf1203L / Fpf1204 / Fpf12045: Intellimax™ Ultra-Small, Slew-Rate-Controlled Load SwitchDocument12 pagesFpf1203 / Fpf1203L / Fpf1204 / Fpf12045: Intellimax™ Ultra-Small, Slew-Rate-Controlled Load SwitchBLUEE009Pas encore d'évaluation

- SMD Led: Product Data SheetDocument16 pagesSMD Led: Product Data SheetBLUEE009Pas encore d'évaluation

- FUSB2500 FullDocument56 pagesFUSB2500 FullBLUEE009Pas encore d'évaluation

- Ic 78Document56 pagesIc 78Patricio TorresPas encore d'évaluation

- Carrier Current Receiver PDFDocument5 pagesCarrier Current Receiver PDFTEDY-RPas encore d'évaluation

- 12 December 2002Document68 pages12 December 2002Jean-Marie Francois100% (1)

- Demonstrate Simple Phase Demodulation Using Hilbert TransformDocument3 pagesDemonstrate Simple Phase Demodulation Using Hilbert TransformYonathan SetiawanPas encore d'évaluation

- MARU 320 Manual Vol 1 PDFDocument300 pagesMARU 320 Manual Vol 1 PDFDwijaputra TemplorerPas encore d'évaluation

- Basic Feature 3GDocument122 pagesBasic Feature 3Ghery_brucePas encore d'évaluation

- 2020 Updated CS Manual-Sir AsifDocument74 pages2020 Updated CS Manual-Sir AsifSheroz AliPas encore d'évaluation

- Bjectives: Digital Communications LAB VI (EE4331)Document15 pagesBjectives: Digital Communications LAB VI (EE4331)River hutabaratPas encore d'évaluation

- Analog and Digital Communication Systems: The Transmission of Information Is Called CommunicationDocument71 pagesAnalog and Digital Communication Systems: The Transmission of Information Is Called Communication20-403 TejashwiniPas encore d'évaluation

- Two Way Radio CommunicationsDocument2 pagesTwo Way Radio Communicationsabross36Pas encore d'évaluation

- Jaws MK 2 CB - Conversión A 10MDocument14 pagesJaws MK 2 CB - Conversión A 10MGeraldrum Zyzcom HdzPas encore d'évaluation

- Electronic Communication TrainerDocument1 pageElectronic Communication TrainerFandeto Gaming100% (1)

- Chapter 13 Oscillators and MixersDocument23 pagesChapter 13 Oscillators and MixersBảo BìnhPas encore d'évaluation

- Icom IC-M502 Service ManualDocument44 pagesIcom IC-M502 Service ManualYayok S. Anggoro100% (1)

- Ronald Wilting - EpcosDocument22 pagesRonald Wilting - EpcoslatrachePas encore d'évaluation

- PLL AlgorithmsDocument6 pagesPLL AlgorithmsLazuardi FaizPas encore d'évaluation

- Icom Ic 2800HDocument50 pagesIcom Ic 2800HradioclubcopiapoPas encore d'évaluation

- Refresher ModulationDocument28 pagesRefresher ModulationMairiz MontealtoPas encore d'évaluation

- Analog Communication Lab ManualDocument109 pagesAnalog Communication Lab ManualksrajuhydPas encore d'évaluation

- ALINCO DJ 175 Service ManualDocument28 pagesALINCO DJ 175 Service Manualmdc2013Pas encore d'évaluation

- Distributed Antenna Solutions For Public Safety, Lte, Cellular and Wifi NetworksDocument4 pagesDistributed Antenna Solutions For Public Safety, Lte, Cellular and Wifi NetworkstelcoPas encore d'évaluation

- 800 10518Document2 pages800 10518riritnePas encore d'évaluation

- Uhf Ask Receiver IC U3741BM: FeaturesDocument33 pagesUhf Ask Receiver IC U3741BM: FeaturesBegu CataPas encore d'évaluation

- Analog Communication Lab Manual PDFDocument21 pagesAnalog Communication Lab Manual PDFAjeet BhardwajPas encore d'évaluation

- 80MRX40Document3 pages80MRX40AhmadAkhbariPas encore d'évaluation

- Demodulation of DSB-SC AM SignalsDocument3 pagesDemodulation of DSB-SC AM SignalsMalik M. Farid AwanPas encore d'évaluation

- Spectrum Monitoring HandbookDocument202 pagesSpectrum Monitoring HandbookMikhail LavrentyevPas encore d'évaluation

- CST Unit 3 - PPT 1 PDFDocument17 pagesCST Unit 3 - PPT 1 PDFAnjali BharadwajPas encore d'évaluation

- WPC Noc Rca & Action DetailDocument2 pagesWPC Noc Rca & Action Detailgerika shafiraPas encore d'évaluation

- ECE 421 Lab4Document39 pagesECE 421 Lab4LuelsonCordovaDeclaradorPas encore d'évaluation