Académique Documents

Professionnel Documents

Culture Documents

MOS Inverter (5.8) 1 PerPage

Transféré par

Jose CamposCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

MOS Inverter (5.8) 1 PerPage

Transféré par

Jose CamposDroits d'auteur :

Formats disponibles

cay:E:-/?

-3

425

//'(/: .::e 61d.

5.8 THE CMOS DIGITAL LOGIC INVERTER

__j

Complementary MOS or CMOS logic circuits have been available as standard packages for

use in conventional digital system design since the early 1970s. Such packages contain logic

gates and other digital system building blocks with the number of gates per package ranging

from a few (small-scale integrated or SSI circuits) to few tens (medium-scale integrated or

MSI circuits).

In the late 1970s, as the era of large- and very-large-scale integration (LSI and VLSI;

hundreds to hundreds of thousands of gates per chip) began, NMOS became the fabrication

technology of choice. Indeed, early VLSI circuits such as the early microprocessors employed NMOS technology. Such circuits utilized the enhancement-load, and later the depletion-load, amplifier as the basic inverter configuration. Although at thaUime the design

flexibility and other advantages that CMOS offers were known, the CMOS technology then

was too complex to produce these high-density VLSI chips economically. However, as

advances in processing technology were made, this state of affaifs changed radically. At the

time of this writing, CMOS technology has virtually replaced NMOS at all levels of integration, in both analog and digital applications.

For any IC technology used in digital circuit design, the basic circuit element is the

logic inverter. Once the operation and characteristics of, the inverter circuit are thoroughly

understood, the results can be extended to the design of logic gates and other more complex

circuits. In this section, we provide such a study for the CMOS inverter.

The basic CMOS inverter is shown in Fig. 5.55. It utilizes two matched enhancementtype MOSFETs: one, QN, with an n channel and the other, Qp, with a p channel. As

indicated, the body of each device is connected to its' source and thus no body effect arises.

We shall therefore use the simplified circuit schematic diagram shown in Fig. 5.55(b). As

will be seen shortly, the CMOS circuit realizes the conceptual inverter implementation

studied in Chapter 1 (Fig. 1.32) where a pair of switches are operated in a complementary

fashion by the input voltage v1.

426

FIELD-EFFECT TRANSISTORS (FETs)

v, ,,_____

v,,~J----e

(a)

Fig. 5.55

(b)

(a) The CMOS inverter.

(b) Simplified circuit schematic for the inverter.

Circuit Operation

We first consider the two extreme cases: when VJ is at logic-0 level, which is approximately

0 V, and when VJ is at logic-I level, which is approximately VDD volts. In both cases, we

shall consider the n-channel device QN to be the driving transistor and the p-channel device

Qp to be the load. However, since the circuit is completely symmetric, this assumption is

obviously arbitrary, and the reverse would lead to identical results.

Figure 5.56 illustrates the case when VJ = VDD' showing the iD-VDs characteristic curve

for QN with VcsN = VDD (Note that iD = i and VDsN = v 0 ). Superimposed on the QN

+

VscP

=0

Load curve

(vscP = 0)

(a)

-----{) vo === 0

O VoL = 0

(b)

.(c)

Fig. 5.56 Operation of the CMOS inverter when VJ is high: (a) circuit with VJ = VDD (logic-1

level, or VoH); (b) graphical construction to determine the operating point; and (c) equivalent

circuit.

5.8

THE CMOS DIGITAL LOGIC INVERTER

427

characteristic curve is the load curve, which is the io-VSD curve of Qp for the case

vscP = 0 V. Since vscP < !Vt/, the load curve will be a horizontal straight line at almost

zero current level. The operating point will be at the intersection of the two curves, where

we note that the output voltage is nearly zero (typically less than 10 mV) and the current

through the two devices is also nearly zero. This means that the power dissipation in the

circuit is very small (typically a fraction of a microwatt). Note, however, that although

QN is operating at nearly zero current and zero drain-source voltage (i.e., near the origin of

the iD-VDs plane), the operating point is on a steep segment of the iD-VDs characteristic

curve. Thus QN provides a low-resistance path between the output terminal and ground,

with the resistance obtained using Eq. (5.13) as

(5.85)

Figure 5.56(c) shows the equivalent circuit of the inverter when the input is high. This

circuit confirms that v 0

VoL = 0 V, and that. the power dissipation in the inverter is

zero.

The other extreme case, when v1 = 0 V, is illustrated in Fig. 5.57. In this case QN is

operating at vcsN = O; hence its iD-VDs characteristic is almost a horizontal straight line

at zero current level. The load curve is the iD-VsD characteristic of the p-channel device

with VscP = V DD As shown, at the operating point the output voltage is almost equal to

VoD (typically less than 10 mV below VDD), and the current in the two devices is still nearly

zero. Thus the power dissipation in the circuit is very small in both extreme states.

Figure 5.57(c) shows the equivalent circuit of the inverter when the input is low. Here

we see that Qp provides a low-resistance path between the output terminal and the de supply

VDD' with the resistance given by

YDSP

(5.86)

VDD

VDD

+

VscP

~ J/[k~(~)P(VDD - jv,p1)]

Load curve

Voo

(vscP

Voo)

rosP

vo

ii

--

VcsN

(a)

VoL

:== 0

=0

--

VDL

Vo

+

VcsN

VDD

(b)

Vo

(c)

Fig. 5.57 Operation of the CMOS inverter when VJ is low: (a) circuit with VJ = OV (logic-0

level, or VoL); (b) grap~ical construction to determine the operating point; and (c) equivalent

circuit.

428

FIELD-EFFECT TRANSISTORS (FETs)

The equivalent circuit confirms that in this case v0

VoH = VDD and that the power

dissipation in the inverter is zero.

It should be noted, however, that in spite of the fact that the quiescent current is zero,

the load-driving capability of the CMOS inverter is high. For instance, with the input high,

as in the circuit of Fig. 5.56, transistor QN can sink a relatively large load current. This

current can quickly discharge the load capacitance, as will be seen shortly. Because of its

action in sinking load current and thus pulling the output voltage down toward ground,

transistor QN is known as the "pull-down" device. Similarly, with the input low, as in the

circuit of Fig. 5.57, transistor Qp can source a relatively large load current. This current

can quickly charge up a load capacitance, thus pulling the output voltage up toward VDD

Hence, Qp is known as the "pull-up" device. The reader will recall that we used this terminology in connection with the conceptual inverter circuit of Fig. 1.32.

From the above, we conclude ~hat the basic CMOS logic inverter behaves as an ideal

inverter:

1. The output voltage levels are 0 and VDD and thus the signal swing is the maximum

possible. This, coupled with the fact that the inverter can be designed to provide a

symmetrical voltage-transfer characteristic, results in wide noise margins.

2. The static power dissipation in the inverter is zero (neglecting the dissipation due

to leakage currents) in both of its states. (Recall that the static power dissipation is

so named so as to distinguish it from the dynamic power dissipation arising from

the repeated switching of the inverter, as will be discussed shortly.)

' 3. A low-resistance path exists between the output terminal and ground (in the lowoutput state) or VDD (in the high-output state). These low-resistance paths ensure

that the output voltage is 0 or VDD independent of the exact values of the (WIL)

ratios or the other device parameters. Further, the low output resistance makes the

inverter less sensitive to the effects of noise and other disturbances.

4. The active pull-up and pull-down devices provide the inverter with high outputdriving capability in both directions. As will be seen, this speeds up the operation

considerably.

5. The input resistance of the inverter is infinite (because le = 0). Thus the inverter

can drive an arbitrarily large number of similar inverters with no loss in signal level.

Of course, each additional inverter increases the load capacitance of the driving

inverter and slows down the operation. Shortly, we will consider the inverter switching times.

The Voltage Transfer Characteristic

The complete voltage-transfer characteristic (VTC) of the CMOS inverter can be obtained

by repeating the graphical procedure, used above in the two extreme cases, for all intermediate values of v1. In the following, we shall calculate the critical points of the resulting

voltage transfer curve. For this we need the i-v relationships of QN and Qp. For QN,

ioN =

k;(~)J(v1 -

Vm)Vo -

~ifo]

(5.87)

5.8

THE CMOS DIGITAL LOGIC INVERTER

429

and

for Vo

VJ -

>

Vrn

(5.88)

For Qp,

ivp = k;(~)Jcvvv -

VJ -

IV,,,l)CVDo - va) -

~(Vvv - va>2]

for Vo

>

VJ

IVrpl

(5.89)

and

1 ,

(w)

lDp=2,kPLP(VDD-vJ-Vip)

1

1

The CMOS inverter is usually designed to have

(5.90)

V,.

IV,,,I

and

k;( ~). k;( ~) . It

=

should be noted that since /Lp is 0.3 to 0.5 times the value of f..lm to make k' (WIL) of the~wo

devices equal, the width of the p-channel device is made two to three times that of the

n-channel device. More specifically, the two devices are designed to have equal lengths,

with widths related by

WP = f..ln

Wn

/Lp

This will result in

k; ( ~) n

;,,

k; ( ~) , and the inverter will have symmetric transfer char-

acteristic and equal current-driving cfpability in both directions (pull-up and pull-down).

With QN and Qp matched, the CMOS inverter has the voltage transfer characteristic

shown in Fig. 5.58. As .~ndicated, the transfer characteristic has five distinct segments corresponding to different combinations of modes of operation of QN and Qp. The vertical

segment BC is obtained when both QN and Qp are operating in the saturation region. Because we are neglecting the finite output resistance in saturation, the inverter gain in this

region is infinite. From symmetry, this vertical segment occurs at VJ = VDD/2 and is

bounded by vo(B) = VDD/2 + Vi and vo(C) = VDD/2 - Yr.

The reader will recall from Section 1. 7 that in addition to VoL and VoH, two other

points on the transfer curve determine the noise margins of the inverter. These are the

maximum permitted logic-0 or "low" level at the input, VJL, and the minimum permitted

logic-I or "high" level at the input, VJH. These are Jormally defined. as the two points on

the transfer curve at which the incremental gain is unity (i.e., the slope is -1 VN).

To determine VJH we note that QN is in the triode region, and thus its current is given

by Eq. (5.87), while Qp is in saturation and its current is given by Eq. (5.90). Equating

iDN and inp, and assuming matched devices,'gives

(VJ -

Vi)vo

2 -2I Vo

2I

cvDD

v1

vt)2

(5.91)

430

FIELD-EFFECT TRANSISTORS (FETs)

QN in saturation

Qp in triode region

Vo

VoH

QNoff

IA

= VDD i - - - - + - -

I

I

I

~ Slope = -: I

I

I

I

(V~D + v) - - -1- -

-----j-

I

I

I

I

I

I

I

I

QNand Qp

.

.

m saturation

c

___ ,I____:_

I

I

I

I

I

I

I

I

I

I

vth -Fig. 5.58

VDD

The voltage transfer characteristic of the CMOS inverter.

Differentiating both sides relative to VJ results in

(vJ -

dvo

Vr)dVJ

dvo

vo-d = -(Vvv VJ

Vo -

VJ -

Vr)

in which we substitute VJ = Vm and dv0 /dvJ = -1 to obtain

Vvv

2

vo = Vm -

(5.92)

Substituting in Eq. (5.91) VJ = Vm and for v 0 from Eq. (5.92) gives

Vm = t(5Vvv - 2Vr)

(5.93)

VIL can be determined in a manner similar to that used to find Vm. Alternatively, we

can use the symmetry relationship

'

Vvv

Vi>v

Vm - - - = - - - VIL

5.8

THE CMOS DIGITAL LOGIC INVERTER

431

together with Vm from Eq. (5.93) to obtain

VIL

t(3VDD

(5.94)

2Vi)

The noise margins can now be determined as follows:

NMH = VoH - VIH

VDD - t(5VDD - 2Vt)

t(3VDD + 2V1)

NML = VIL - VoL

t(3VDD + 2Vi) - 0

-i\-(3VDD

(5.95)

(5.96)

2V1)

As expected, the symmetry of the voltage transfer characteristic results in equal noise margins. Of course, if QN and Qp are not matched, the voltage transfer characteristic will no

longer be symmetric, and the noise margins will not be equal (see Problem 5.94).

Exercises

5.31 For a CMOS inverter with matched MOSFETs having

if VDD

Ans.

V, = 1 V, find

ViL, VJH, and the noise margins

5 v.

2.1 V; 2.9 V; 2.1

5.32 Consider a CMOS inverter with Vrn = IVrpl = 2 V, (WIL)n = 20, (WIL)p = 40, ,nCox = 2,pCox =

20 ,A!V 2 , and VDD = 10 V. For v1 = VDD find the maximum current that the inverter can sink while Vo

remains :5 0.5 V.

Ans.

1.55 mA

5.33 An inverter fabricated in a 1.2-,m CMOS technology uses the minimum possible channel lengths (i.e.,

Ln = LP = 1.2 ,m). If Wn = 1.8 ,m, find the value of WP that would result in QN and Qp being matched.

For this technology, k~ = 80 ,A!V 2 and k; = 27 ,AN 2 Also calculate the value of the output resistance of

the inverter when vo = VOL ~-

Ans.

5.4 ,m; 2 k!l

5.34 Show that the threshold voltage V,h of a CMOS inverter (see Fig. 5.58) is given by

vth

IVrpl)

r(VDD -

+ Vrn

-----~--

where

r=

k;(WIL)p

k~(WIL)n

432

FIELD-EFFECT TRANSISTORS (FETs)

Dynamic Operation

As explained in Section 1.7, the speed of operation of a digital system (e.g., a computer)

is determined by the propagation delay of the logic gates used to construct the system.

Since the inverter is the basic logic gate of any digital IC technology, the propagation delay

of the inverter is a fundamental parameter in characterizing the technology. In the following,

we analyze the switching operation of the CMOS inverter to determine its propagation delay.

Figure 5.59(a) shows the inverter with a capacitor C between the output node and ground.

Here C represents the sum of the internal capacitances of the MOSFEts QN and Qp, the

capacitance of the interconnect wire between the inverter output node and the input of the

other logic gates the inverter is driving, and the total input capacitance of these load (or

fan-out) gates. We assume that the inverter is driven by the ideal pulse (zero rise and fall

tiDP

IC

(a)

Vo

VDD

VDD

Vo

I

I

tPHL~~

I

~~tPLH

11

11

----

0

(b)

Operating

point at

1 = o+

F

VcsN = VDD

IE

I Capaciior I

I discharge I

I through QN t

Operating point I

after switching I

is completed 1

1

I

I Op~rating

I / pomt at

I

t = O-

--~~~~----'-~~-'-~---"'--~--~---1~

V~D

-(d)

(c)

Fig. 5.59 Dynamic operation of a capacitively loaded CMOS inverter:

and output waveforms;

discharges through QN;

(a) circuit; (b) input

(c) trajectory of the operating point as the- input goes high and C

(d) equivalent circuit during the capacitor discharge.

5.8

THE CMOS DIGITAL LOGIC INVERTER

433

times) shown in Fig. 5.59(b). Since the circuit is symmetric (assuming matched MOSFETs),

the rise and fall times of the output waveform should be equal. It is sufficient, therefore, to

consider either the tum-on or the tum-off process. In the following, we consider the first.

Figure 5.59(c) shows the trajectory of the operating point obtained when the input pulse

goes from VoL = 0 to VoH = VDD at time t = 0. Just prior to the leading edge of the

input pulse (that is, at t = 0-) the output voltage equals VDD and capacitor C is charged

to this voltage. At t = 0, v1 rises to VDD, causing Qp to turn off immediately. From then

on, the circuit is equivalent to that shown in Fig. 5.59(d) with the initial value of v 0 =

VDD Thus the operating point at t = O+ is point E, at which it is seen that QN will be in

the saturation region and conducting a large current. As C discharges, the current of QN

remains constant until v 0 = VDD - Vr (point F). Denoting this portion of the discharge

interval tPHLl (where the subscript HL indicates the high-to-low transition), we can write

C[VDD tpHL1

= I ,

(w)

2_kn L

Vi)]

(VDD -

Vi)

n(VDD -

(5.97)

CVr

~k~(~).

V,)

(VDD -

Beyond point F, transistor QN operates in the triode region, and thus its current is given by

Eq. (5.87). This portion of the discharge interval can be described by

iDNdt

= -C dvo

Substituting for iDN from Eq. (5.87) and rearranging the differential equation, we obtain

-

k~(WIL)n

dt

2C

1

= --- - - - - -dvo

----2(VDD -

Vr)

- - - - - rlo 2(VDD -

(5.98)

Vo

Vr)

To find the component of the delay time iPHL during which v 0 decreases from (VDD

Vr) to the 50% point, v 0 = VDD/2, we integrate both sides of Eq. (5.98). Denoting this

component of delay time tpH2, we find that

-

k n'(TIT/L)

yy,

n

2c

___l___ Jvo=VDDl2

PHL2 -

2(VDD -

V)

t

dvo

vo=VDD-Vi

rlo -

(5.99)

Vo

2(VDD-Vr)

Using the fact that

dx

ax 2 - x

In

(i -

__!__)

ax

enables us to evaluate the integral in Eq. (5.99) and thus obtain

tPHL2 =

kn(W/L)n(VDD -

Vr)

ln

(3VDD -

4Vr)

VDD

The two components of tPHL in Eqs. (5.97) a:vd (5.100) can be added to obtain

(5.100)

434

FIELD-EFFECT TRANSISTORS (FET!'>)

Vt

+ -1 ln (3VDD

2

VDD

4Vt)]

(5.101)

For the usual case of Vi = 0.2VDD' this equation reduces to

t

PHL

1.6C

- ----- k~(W/L)n VDD

(5.102)

Similar analysis of the tum-off process yields an expression for tPLH identical to that in Eq.

(5.102) except for k~(WIL)n replaced with k;(WIL)p. The propagation delay tp is the average

of tPHL and tPLH From Eq. (5.102), we note that to obtain lower propagation delays and

hence faster operation, C should be minimized, a high process transconductance parameter

k' should be utilized, the transistor WIL ratio should be increased, and the power-supply

voltage VDD should be increased~ There are, of course, design trade-offs and physical limits

involved in making choices for these parameter values. This subject, however, is too advanced for our present needs.

Exercises

5.35 A CMOS inverter in a VLSI circuit operating from a 5-V supply has (WIL)n = 10 ,m/5 ,m,

(WIL)p = 20 ,m/5 ,m, Vin = IVipl = 1 V, f.LnCox = 2 ,pCox = 20 ,AN 2 If the total effective load ca-

pacitance is 0.1 pF, find

ilj,i

!1)!

rr~

Ans.

f PHL f PLH,

and

tp.

0.8 ns; 0.8 ns; 0.8 ns

5.36 For the CMOS inverter of Exercise 5.32, which is intended for SSI and MSI circuit applications, find

tp

if the load capacitance is 15 pF.

Ans.

6 ns

Current Flow and Power Dissipation

As the CMOS inverter is switched, current flows through the series connection of QN and

Qp. Figure 5.60 shows the inverter current as a function of VJ. We note that the current

peaks at the switching threshold, VJ = Vih = Vvvl2. This current gives rise to dynamic

power dissipation in the CMOS inverter. However, a more significant component of dynamic power dissipation results from the current that flows in QN and Qp when the inverter

is loaded by a capacitor C.

An expression for this latter component can be derived as follows: Consider once more

the circuit in Fig. 5.59(a). At t = 0-, v0 = VDD and the energy stored on the capacitor is

1-CVzw. At t = 0, VJ goes high to VDD' Qp turns off, and QN turns on. Transistor QN then

discharges the capacitor, and at the end of the discharge interval, the capacitor voltage is

reduced to zero. Thus during the discharge interval, energy of -!- CVbv is removed from C

and dissipated in QN. Next consider the other half of the cycle when VJ goes low to zero.

5.8

THE CMOS DIGITAL LOGIC INVERTER

435

Fig. 5.60 The current in the

CMOS inverter versus the input

voltage.

Vin

VDD

Transistor QN turns off, and Qp conducts and charges the capacitor. Let the instantaneous

current supplied by Qp to C be denoted i. This current is, of course, coming from the power

supply VDD Thus the energy drawn from the supply during the charging period will be

fVDDi dt = VDDf i dt = VDD Q, where Q is the charge supplied to the capacitor; that is,

Q = CVDD Thus the energy drawn from the supply during the charging interval is cvbD

At the end of the charging interval, the capacitor voltage will be VDD, and thus the energy

stored in it Will be -t CVbD It follows that during the charging interval, half of the energy

drawn from the supply, -tcvbD, is dissipated in Qp.

From the above, we see that in every cycle, -t CVbD of energy is dissipated in QN and

-tcvbD dissipated in Qp, for a total energy dissipation in the inverter of cvbD Now if the

inverter is switched at the rate off cycles per second, the dynamic power dissipation in it

will be

(5.103)

Observe that the frequency of operation is related to the propagation delay: The lower the

propagation delay, the higher the frequency at which the circuit can be operated and, according to Eq. (5.103), the higher the power dissipation in the circuit. A figure of merit or

a quality measure of the particular circuit technology is the delay-power product (DP),

The delay-power product tends to be a constant for a particular digital circuit technology

and can be used to compare different technologies. Obviously the lower the value of DP

the more effective is the technology. The delay-power product has the units of joules, and

is in effect a measure of the energy dissipated per cycle of operation. Thus for CMOS where

most of the power dissipation is dynamic, we can take DP as simply CVbD

Exercises

5.37 .For the inverter specified in Exercise 5.32, find the peak current drawn from

Ans.

1.8 mA

VDD

during switching.

436

FIELD-EFFECT TRANSISTORS (FETs)

5.38 Let the inverter specified in Exercise 5.32 be loaded by a 15-pF capacitance. Find the dynamic power

dissipation that results when the inverter is switched at a frequency of 2 MHz. What is the average current

drawn from the power supply?

Ans.

3 mW; 0.3 mA

5.39 Consider a CMOS VLSI chip having 100,000 gates fabricated in a 1.2-m CMOS technology. Let the

load capacitance per gate be 30 fF. If the chip is operated from a 5-V supply and is switched at a rate of 100

MHz, find (a) the power dissipation per gate, and (b) the total power dissipated in the chip assuming that only

30% of the gates are switched at any one time.

Ans.

75 ,W; 2.25

A Final Remark

In this section, we have provided an introduction to CMOS digital circuits. We shall return

to this subject in Chapter 13, where CMOS logic gates and other CMOS digital circuits are

studied.

Vous aimerez peut-être aussi

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (345)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Es 321 Power Electronics: - Power Semiconductor Diodes and Circuits 06 Lecture Diode CharacteristicsDocument23 pagesEs 321 Power Electronics: - Power Semiconductor Diodes and Circuits 06 Lecture Diode Characteristicsunity123d deewPas encore d'évaluation

- Nanomaterials 12 00485 v3Document34 pagesNanomaterials 12 00485 v3Asha JakharPas encore d'évaluation

- Plotting A Moore's Law For Flexible ElectronicsDocument2 pagesPlotting A Moore's Law For Flexible ElectronicsrtbuhlerPas encore d'évaluation

- Advanced Packaging Current Trends & ChallengesDocument11 pagesAdvanced Packaging Current Trends & ChallengesGary Ryan DonovanPas encore d'évaluation

- Novel Lithography Technique Using An ASML Stepper/Scanner For The Manufacture of Display Devices in MEMS WorldDocument6 pagesNovel Lithography Technique Using An ASML Stepper/Scanner For The Manufacture of Display Devices in MEMS WorldShane LiuPas encore d'évaluation

- Lecture 09 Transient Characteristics of The PN JunctionDocument20 pagesLecture 09 Transient Characteristics of The PN JunctionKishor ShiyaniPas encore d'évaluation

- Power Electronics Devices and Circuits Second Edition PDFDocument383 pagesPower Electronics Devices and Circuits Second Edition PDFRuben Ignacio Salazar Baez100% (7)

- Smps Mosfet: IRL3713 IRL3713S IRL3713LDocument6 pagesSmps Mosfet: IRL3713 IRL3713S IRL3713Laaa dddPas encore d'évaluation

- Switching or ON OFF Characteristics of SCR or ThyristorDocument10 pagesSwitching or ON OFF Characteristics of SCR or ThyristorDhayanandhPas encore d'évaluation

- Basic Terminology in Physical Design VLSI Basics and Interview QuestionsDocument10 pagesBasic Terminology in Physical Design VLSI Basics and Interview Questionsdivya gaddePas encore d'évaluation

- Electronic Devices and Circuits: Andhra Pradesh, IndiaDocument5 pagesElectronic Devices and Circuits: Andhra Pradesh, Indiak jayaram kumar ACETPas encore d'évaluation

- EC111:Fundamental of Electronics Engineering: Assistant Professor, ECE DepartmentDocument51 pagesEC111:Fundamental of Electronics Engineering: Assistant Professor, ECE DepartmentrupeshPas encore d'évaluation

- Nota Final ExamDocument7 pagesNota Final ExamzulPas encore d'évaluation

- Irfb 4020Document2 pagesIrfb 4020LEWIS RODRIGUEZPas encore d'évaluation

- Custom Ic Design: Cmos Standard Cell Circuit Design, Simulation and LayoutDocument19 pagesCustom Ic Design: Cmos Standard Cell Circuit Design, Simulation and Layoutkajal awasthiPas encore d'évaluation

- RectifierDocument11 pagesRectifierasislakhaPas encore d'évaluation

- Datasheet5641 ZenerDocument6 pagesDatasheet5641 ZenerDoppler ElectronicaPas encore d'évaluation

- Class 5Document43 pagesClass 5SANT SARANPas encore d'évaluation

- Advanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedDocument8 pagesAdvanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedLiver Haro OrellanesPas encore d'évaluation

- Role of Surface States and Interface Charges in 2deg in Sputtered Zno HeterostructuresDocument5 pagesRole of Surface States and Interface Charges in 2deg in Sputtered Zno HeterostructuresakashPas encore d'évaluation

- EE 466/586 VLSI Design: School of EECS Washington State University Pande@eecs - Wsu.eduDocument32 pagesEE 466/586 VLSI Design: School of EECS Washington State University Pande@eecs - Wsu.eduPhạm Đức ThuậnPas encore d'évaluation

- Electronic Circuit-MIDTERMDocument25 pagesElectronic Circuit-MIDTERMCeasy Boy PeraltaPas encore d'évaluation

- Wide Band Gap SemiconductorsDocument45 pagesWide Band Gap SemiconductorspawaniitkgpPas encore d'évaluation

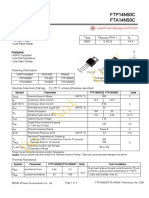

- Do Not Copy: FTP14N50 C FTA14N50 CDocument4 pagesDo Not Copy: FTP14N50 C FTA14N50 CListenPas encore d'évaluation

- CD4070Document6 pagesCD4070api-3708997Pas encore d'évaluation

- Basic Electronics and Sensor Technology: UNIT-1Document55 pagesBasic Electronics and Sensor Technology: UNIT-1Sandhya SaiPas encore d'évaluation

- 2 SC 4467Document4 pages2 SC 4467Michelson Hincapie MoralesPas encore d'évaluation

- TIP42, TIP42A, TIP42B, TIP42C PNP Silicon Power TransistorsDocument4 pagesTIP42, TIP42A, TIP42B, TIP42C PNP Silicon Power TransistorsThanh HaiPas encore d'évaluation

- PNPN and Other Device BoylestadDocument20 pagesPNPN and Other Device BoylestadJohn Lester Laurentino RamirezPas encore d'évaluation

- EXPERIMENT 11: Uni-Junction Transistor (UJT) CHARACTERISTICSDocument4 pagesEXPERIMENT 11: Uni-Junction Transistor (UJT) CHARACTERISTICSnPas encore d'évaluation