Académique Documents

Professionnel Documents

Culture Documents

7490

Transféré par

Henry CastandCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

7490

Transféré par

Henry CastandDroits d'auteur :

Formats disponibles

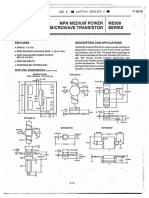

Revised March 2000

DM7490A

Decade and Binary Counters

General Description

Features

The DM7490A monolithic counter contains four masterslave flip-flops and additional gating to provide a divide-bytwo counter and a three-stage binary counter for which the

count cycle length is divide-by-five.

Typical power dissipation

145 mW

Count frequency 42 MHz

The counter has a gated zero reset and also has gated setto-nine inputs for use in BCD nines complement applications.

To use the maximum count length (decade or four-bit

binary), the B input is connected to the QA output. The

input count pulses are applied to input A and the outputs

are as described in the appropriate Function Table. A symmetrical divide-by-ten count can be obtained from the

counters by connecting the QD output to the A input and

applying the input count to the B input which gives a divideby-ten square wave at output QA.

Ordering Code:

Order Number

DM7490AN

Package Number

N14A

Package Description

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Connection Diagram

2000 Fairchild Semiconductor Corporation

DS006533

www.fairchildsemi.com

DM7490A Decade and Binary Counters

August 1986

DM7490A

Function Tables

Logic Diagram

BCD Count Sequence (Note 1)

Count

Outputs

QD

QC

QB

QA

L

BCD Bi-Quinary (5-2) (Note 2)

Count

Outputs

QA

QD

QC

QB

L

Reset/Count Function Table

Reset Inputs

R0(1)

R0(2)

H

H

Outputs

QD

QC

QB

The J and K inputs shown without connection are for reference only and

are functionally at a HIGH level.

QA

R9(1)

R9(2)

COUNT

COUNT

COUNT

COUNT

H = HIGH Level

L = LOW Level

X = Dont Care

Note 1: Output QA is connected to input B for BCD count.

Note 2: Output QD is connected to input A for bi-quinary count

www.fairchildsemi.com

Supply Voltage

Note 3: The Absolute Maximum Ratings are those values beyond which

the safety of the device cannot be guaranteed. The device should not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the absolute maximum ratings.

The Recommended Operating Conditions table will define the conditions

for actual device operation.

7V

Input Voltage

5.5V

0C to +70C

Operating Free Air Temperature Range

65C to +150C

Storage Temperature Range

Recommended Operating Conditions

Symbol

Parameter

Min

Nom

Max

4.75

5.25

Units

VCC

Supply Voltage

VIH

HIGH Level Input Voltage

VIL

LOW Level Input Voltage

0.8

IOH

HIGH Level Output Current

0.8

mA

IOL

LOW Level Output Current

16

mA

fCLK

Clock Frequency

32

(Note 4)

16

Pulse Width

15

(Note 4)

30

Reset

15

tW

tREL

Reset Release Time (Note 4)

25

TA

Free Air Operating Temperature

MHz

ns

ns

C

70

Note 4: TA = 25C and VCC = 5V.

DC Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted)

Symbol

Parameter

Conditions

VI

Input Clamp Voltage

VCC = Min, II = 12 mA

VOH

HIGH Level

VCC = Min, IOH = Max

VOL

II

IIH

IIL

Min

2.4

Output Voltage

VIL = Max, VIH = Min

LOW Level

VCC = Min, IOL = Max

Output Voltage

VIH = Min, VIL = Max (Note 6)

Typ

(Note 5)

Max

Units

1.5

3.4

0.2

Input Current @ Max Input Voltage VCC = Max, VI = 5.5V

V

0.4

mA

HIGH Level

VCC = Max

80

Input Current

VI = 2.7V

Reset

40

120

LOW Level

VCC = Max

3.2

Input Current

VI = 0.4V

Reset

1.6

4.8

IOS

Short Circuit Output Current

VCC = Max (Note 7)

ICC

Supply Current

VCC = Max (Note 8)

18

29

mA

57

mA

42

mA

Note 5: All typicals are at VCC = 5V, TA = 25C.

Note 6: QA outputs are tested at IOL = Max plus the limit value of IIL for the B input. This permits driving the B input while maintaining full fan-out capability.

Note 7: Not more than one output should be shorted at a time.

Note 8: ICC is measured with all outputs open, both RO inputs grounded following momentary connection to 4.5V, and all other inputs grounded.

www.fairchildsemi.com

DM7490A

Absolute Maximum Ratings(Note 3)

DM7490A

AC Switching Characteristics

at VCC = 5V and TA = 25C

Symbol

fMAX

tPLH

Parameter

Min

Maximum Clock

A to QA

32

Frequency

B to QB

16

Propagation Delay Time

Propagation Delay Time

HIGH-to-LOW Level Output

tPLH

Propagation Delay Time

LOW-to-HIGH Level Output

tPHL

Propagation Delay Time

HIGH-to-LOW Level Output

tPLH

Propagation Delay Time

LOW-to-HIGH Level Output

tPHL

Propagation Delay Time

HIGH-to-LOW Level Output

tPLH

Propagation Delay Time

LOW-to-HIGH Level Output

tPHL

Propagation Delay Time

HIGH-to-LOW Level Output

tPLH

Propagation Delay Time

LOW-to-HIGH Level Output

tPHL

Propagation Delay Time

HIGH-to-LOW Level Output

tPLH

Propagation Delay Time

LOW-to-HIGH Level Output

tPHL

Propagation Delay Time

HIGH-to-LOW Level Output

tPHL

RL = 400, CL = 15 pF

To (Output)

LOW-to-HIGH Level Output

tPHL

From (Input)

Units

MHz

A to QA

16

ns

A to QA

18

ns

A to QD

48

ns

A to QD

50

ns

B to QB

16

ns

B to QB

21

ns

B to QC

32

ns

B to QC

35

ns

B to QD

32

ns

B to QD

35

ns

SET-9 to QA, QD

30

ns

SET-9 to QB, QC

40

ns

40

ns

Propagation Delay Time

SET-0

HIGH-to-LOW Level Output

Any Q

www.fairchildsemi.com

Max

DM7490A Decade and Binary Counters

Physical Dimensions inches (millimeters) unless otherwise noted

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Package Number N14A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and

Fairchild reserves the right at any time without notice to change said circuitry and specifications.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD

SEMICONDUCTOR CORPORATION. As used herein:

2. A critical component in any component of a life support

device or system whose failure to perform can be reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and (c) whose failure

to perform when properly used in accordance with

instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the

user.

www.fairchildsemi.com

www.fairchildsemi.com

Vous aimerez peut-être aussi

- Process Control Fundamentals 2Document73 pagesProcess Control Fundamentals 2Otuekong Ukpong100% (2)

- Inductometro DigitalDocument9 pagesInductometro DigitalHenry CastandPas encore d'évaluation

- Using The Parallel Port in LabVIEWDocument6 pagesUsing The Parallel Port in LabVIEWAlberto EnriquePas encore d'évaluation

- Aplicaciones de La Derivada-Matematica Dic-2008Document2 pagesAplicaciones de La Derivada-Matematica Dic-2008Circulo De Estudios CoredPas encore d'évaluation

- Instrumentation Training Tutorial Part1Document6 pagesInstrumentation Training Tutorial Part1Gary8100% (1)

- ASIO4ALL v2 Instruction ManualDocument11 pagesASIO4ALL v2 Instruction ManualDanny_Grafix_1728Pas encore d'évaluation

- NE56800 To NE56887Document9 pagesNE56800 To NE56887Henry CastandPas encore d'évaluation

- Motorola An 780ADocument6 pagesMotorola An 780ArobinsonsPas encore d'évaluation

- QSGDocument7 pagesQSGHenry CastandPas encore d'évaluation

- Pi Face HTTP InterfaceDocument2 pagesPi Face HTTP InterfaceHenry CastandPas encore d'évaluation

- BTA08-600B: Haopin Microelectronics Co.,LtdDocument5 pagesBTA08-600B: Haopin Microelectronics Co.,LtdHenry CastandPas encore d'évaluation

- ICM7218CDocument11 pagesICM7218CHenry CastandPas encore d'évaluation

- Datasheet l298bDocument14 pagesDatasheet l298bgioganPas encore d'évaluation

- SecurView Release NoteDocument1 pageSecurView Release NoteHenry CastandPas encore d'évaluation

- Nud3105 DDocument10 pagesNud3105 DHenry CastandPas encore d'évaluation

- En Web QIG SecurViewProDocument8 pagesEn Web QIG SecurViewProHenry CastandPas encore d'évaluation

- TV-IP110 CamaraDocument12 pagesTV-IP110 CamaraHenry CastandPas encore d'évaluation

- Introduccion A La Mecatronica y Los Sistemas de MeDocument1 pageIntroduccion A La Mecatronica y Los Sistemas de MeHenry CastandPas encore d'évaluation

- Datasheet PDFDocument10 pagesDatasheet PDFVenkatesh VakamulluPas encore d'évaluation

- Ir 2113Document18 pagesIr 2113rohitsingh2909Pas encore d'évaluation

- General Description: Quad Bilateral SwitchDocument23 pagesGeneral Description: Quad Bilateral Switchtotal4321Pas encore d'évaluation

- 1N4728 To 1N4764DDocument3 pages1N4728 To 1N4764DHenry CastandPas encore d'évaluation

- Max7219 Max7221Document17 pagesMax7219 Max7221Miguel Nallar SaucedoPas encore d'évaluation

- Silicon Transistor ArrayDocument6 pagesSilicon Transistor ArrayHenry CastandPas encore d'évaluation

- IRFZ24NDocument8 pagesIRFZ24NarcatusPas encore d'évaluation

- Arduino InductanceDocument4 pagesArduino InductanceHenry CastandPas encore d'évaluation

- CCD Signal Processors With Integrated Timing Driver: AD9848/AD9849Document36 pagesCCD Signal Processors With Integrated Timing Driver: AD9848/AD9849Henry CastandPas encore d'évaluation

- BAV99LT1 Dual Series Switching Diode: Maximum RatingsDocument4 pagesBAV99LT1 Dual Series Switching Diode: Maximum Ratingsaniruddhaphatak93Pas encore d'évaluation

- Series As HC-49/S: FeaturesDocument2 pagesSeries As HC-49/S: FeaturesCristian CaballeroPas encore d'évaluation

- LM386 Low Voltage Audio Power AmplifierDocument10 pagesLM386 Low Voltage Audio Power Amplifierapple.scotch.fool3550Pas encore d'évaluation

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (120)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- E-Manual: First Edition May 2016Document122 pagesE-Manual: First Edition May 2016Erick Patricio TipanPas encore d'évaluation

- Everything You Need To Know To Start With CDocument53 pagesEverything You Need To Know To Start With CLady Marcela Sánchez MorenoPas encore d'évaluation

- t430 T430i Fru Bom 20130410Document11 pagest430 T430i Fru Bom 20130410Ed SaPas encore d'évaluation

- Living in A Digital Age: The Magic of ComputersDocument4 pagesLiving in A Digital Age: The Magic of Computersahl emPas encore d'évaluation

- Philips SDK ManualDocument16 pagesPhilips SDK ManualMartin HríbikPas encore d'évaluation

- 5 - Foundations - 11 - 26 - 2 - M5Document73 pages5 - Foundations - 11 - 26 - 2 - M5Viktor BesenyeiPas encore d'évaluation

- Srs of Insta 1 PDFDocument13 pagesSrs of Insta 1 PDFRohit KumarPas encore d'évaluation

- Printers Quotations: HP Laserjet P4015N Price 13500Document3 pagesPrinters Quotations: HP Laserjet P4015N Price 13500Mohsin Warriach0% (1)

- Module 5Document39 pagesModule 5OK BYEPas encore d'évaluation

- HYNIX DDR5 Module - New Part Number Decoder - r.2.1 - Sep 2021Document5 pagesHYNIX DDR5 Module - New Part Number Decoder - r.2.1 - Sep 2021Aleksandr Nevedrov100% (1)

- La-5322p Nswaa NtwaaDocument58 pagesLa-5322p Nswaa NtwaaVadim Shapovalov100% (1)

- BZT52C2V4Document3 pagesBZT52C2V4Fikri HidayatPas encore d'évaluation

- Mindfire Solutions Sample Technical Placement Paper Level1Document5 pagesMindfire Solutions Sample Technical Placement Paper Level1placementpapersamplePas encore d'évaluation

- Current LimitingDocument3 pagesCurrent Limitingmessage4guruPas encore d'évaluation

- Module 3 Test Answers Py EseDocument7 pagesModule 3 Test Answers Py Esereza supriatna100% (1)

- Docker Django DevelopmentDocument22 pagesDocker Django DevelopmentMehmet DemirPas encore d'évaluation

- Foshan Blue Rocket Elec 2N2222A - C358533Document6 pagesFoshan Blue Rocket Elec 2N2222A - C358533mrahPas encore d'évaluation

- Programming Fundamentals IT-119Document23 pagesProgramming Fundamentals IT-119Meran XoranyPas encore d'évaluation

- Lnterfacing A GPS Module With Arduino - Idyl - Io PDFDocument1 pageLnterfacing A GPS Module With Arduino - Idyl - Io PDFdefConPas encore d'évaluation

- Oracle® Demantra: System Requirements Guide Release 12.2Document28 pagesOracle® Demantra: System Requirements Guide Release 12.2Sundar PurushothamanPas encore d'évaluation

- TPR0505S-1W Input Voltage: 5V, Output Voltage: 5V, Isolated 1W DC/DC Converters in A SIP PackageDocument3 pagesTPR0505S-1W Input Voltage: 5V, Output Voltage: 5V, Isolated 1W DC/DC Converters in A SIP PackagetoppowerPas encore d'évaluation

- 81131H Regolat-Program ENGDocument13 pages81131H Regolat-Program ENGGopal HegdePas encore d'évaluation

- Understanding Time Delay Relay FunctionsDocument6 pagesUnderstanding Time Delay Relay FunctionsAndrew BullPas encore d'évaluation

- Office 365 Multi Factor Authentication Setup GuideDocument7 pagesOffice 365 Multi Factor Authentication Setup Guideit cleancoPas encore d'évaluation

- Use of Social MediaDocument61 pagesUse of Social MediaBaba HeadquaterPas encore d'évaluation

- Automatic Water Level Indicator and Controller by Using ARDUINODocument10 pagesAutomatic Water Level Indicator and Controller by Using ARDUINOSounds of PeacePas encore d'évaluation

- XBOX 360 Jtag and Modifying TutorialDocument31 pagesXBOX 360 Jtag and Modifying TutorialNumair Imran100% (2)

- Handling of Sensor Bridge OffsetDocument6 pagesHandling of Sensor Bridge OffsetAsdrubale Mancupacapa ArrivoPas encore d'évaluation

- Lab 7 ReportDocument33 pagesLab 7 ReportNIKESH RANABHATPas encore d'évaluation