Académique Documents

Professionnel Documents

Culture Documents

Eca Question Bank With Tag

Transféré par

rppvchDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Eca Question Bank With Tag

Transféré par

rppvchDroits d'auteur :

Formats disponibles

R13 JNTU: Kakinada

II-ii B. Tech ECE

ELECTRONIC CIRCUITANALYSIS

UNIT-I

1. Mention any three applications of a CE amplifier. Consider a single stageCE

amplifier with RS = 1K and RL = 1.2K. Using typical values of h-parameters find

Ai, AV, Ri and Ro.

(R-10,S-1,Aug-2014)

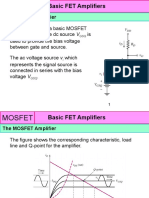

2. Explain how FET can be used as an amplifier. The FET shown in figure 1 has

the following parameters: IDSS = 5.6 mA, and VP = -4V. Find o, if (i) i = 0 and (ii)

i = 10V.

(R-10,S-1,Aug-2014)

3. Draw AC equivalent circuit for a CE amplifier with a bypassed emitter resistor

and with un-bypasses emitter resistor. Briefly explain each circuit.

(R-10,S-2,Aug-2014)

4. What are the advantages of h-parameters.

(R-10,S-2,Aug-2014)

5. The circuit shown in the Figure1, the CS amplifier with self-bias and by pass

resistor Ro.

(R-10,S-3,Aug-2014)

6. Derive the expressions for Ri, Ro and AV, using its equivalent circuit.

(R-10,S-3,Aug2014)

7. A self-biased CE amplifier circuit has R 1 = 100 K , R2 = 10K, Rc = 5K, RE = 1K,

Compute AI, AV, AVS and Ri. The h-parameters of the tran i tor are hie =10K.

(R-10,S-4,Aug-2014)

8. Draw the circuit diagram of Common Drain amplifier and derive an expression

for its Voltage gain.

(R-10,S-4,Aug-2014)

9. The h-parameters of the transistor used in CE amplifier are hfe = 50, hie =1.1K,

hre = 2.510-4, hoe = 24 A/V. Find out current gain and voltage gains with and

without source resistance , input and output impedances , given that R L= 10 K

and RS= 1 K.

(R-10,S-1,April/May-2013)

10.Discuss the classification of amplifiers based on frequency range, type of

coupling, power delivered, and signal handled.

(R-10,S-1,April/May-2013)

11.The h-parameters of a transistor are h fe = 50, hie = 1.1K, hre = 2.5x10-4, hoe = 24

A/V Calculate AI, AV, AVS, Ri, and Ro for Figure 1b

(R-10,S-2,April/May-2013)

Department of Electronics and Communication EngineeringRAMACHANDRA COLLEGE OF ENGINEERING:

ELURU

Electronic Circuit Analysis Question Bank

R13 JNTU: Kakinada

II-ii B. Tech ECE

ELECTRONIC CIRCUITANALYSIS

12.State Miller's theorem. Explain its significance in transistor circuit analysis.

(R-10,S-3, April/May-2013)

13.For the Common Gate amplifier shown below Figure 1, derive expressions for

voltage gain, input impedance and output impedance. Power supplies are

omitted for simplicity. Neglect capacitances.

(R-10,S-3,April/May-2013)

14.Sketch the circuit of a Common Source amplifier. Derive an expression for the

Voltage gain at low frequencies. What is the maximum value of AV.

(R-10,S-1,Jan/Feb-2014)

15.Calculate the voltage gain AV = Vo/Vi at 1 KHz for the circuit shown in 1b.The

FET parameters are gm=2 mA and rd=10K. Neglect capacitances. If the

capacitance 0.003F is also considered, calculate the voltage gain.

(R-10,S-1,Jan/Feb-2014)

16.Derive the equations for the current gain, input impedance, voltage gain and

output impedance of an emitter follower operating at low frequencies in terms of

common emitter h-parameters.

(R-10,S-2,Jan/Feb-2014)

17.Using Millers theorem, prove that for a CE amplifier with resistive load the

Department of Electronics and Communication EngineeringRAMACHANDRA COLLEGE OF ENGINEERING:

ELURU

Electronic Circuit Analysis Question Bank

R13 JNTU: Kakinada

II-ii B. Tech ECE

ELECTRONIC CIRCUITANALYSIS

output gmRL.

(R-10,S-2,Jan/Feb-2014)

18.Derive the equation for voltage gain and input impedance of a common

source JFET amplifier with the help of its circuit diagram and its equivalent

circuit.

(R-10,S-3,Jan/Feb-2014)

19.Calculate AiRi, Av, Ro for the CC amplifier circuit with CE h-parameters given

by hfe=50, hie=1k, hoe = 50k also the resistance parameters given by RL=1k.

(R-10,S-3,Jan/Feb-2014)

20.An Emitter follower circuit has the following parameters RL=1k, RS= 50, hfe=50,

hie = 1k, hoe = 50k , R1 = 100k , R2 = 10k , RE = 10k . Calculate Ri, Ro,Av, and

Aifor the above circuit.

(R-10,S-4,Jan/Feb-2014)

21.Derive an expression for the voltage gain of common source amplifier by using

low frequency model.

(R-10,S-1,Jan/Feb-2015)

22. For a single stage common emitter transistor amplifier configuration, RS=10K and RL=

10K. The h-parameter values are hfc= - 51, hic =1.1K _ , hrc = 1, hoc = 25 A/V. Find

AI; AV; AVS; Ri, and Ro.

(R-10,S-2,Jan/Feb-2015)

23. Show that in Hybrid - model, the diffusion capacitance is proportional to the emitter

bias current.

(R-10,S-4,Jan/Feb-2015)

24. What is the frequency range to consider Giacolletto model of a transistor at high

frequencies? What is the significance of fT in discussing the frequency range of a

transistor at high frequencies?

(R-10,S-2,Jan/Feb-2015)

25. Draw the circuit of a Common Source FET amplifier. Derive an expression for the

Voltage gain at low frequencies. What is the maximum value of AV.

(R-10,S-3,Jan/Feb-2012)

26. Draw the Common Source amplifier at Higher Frequencies and derive an expression for

voltage gain.

(R-10,S-2,April/May-2012)

27. Discuss about various capacitances in a transistor at high frequencies.

(R-10,S-4,Aug-2012)

28. For the emitter follower circuit as shown in Figure 1, calculate the quiescent voltage and

current for VCC=20 V, hfc = 1.3K _, hoc = 2.8 x 10-6 mhos and hrc is negligibly small.

Reactance of capacitance need not be considered at the frequencies of interest. If R1 = 27

_ , R2 = 8.6 k _ , RL= RE =500 _ , Rs = 1k _ , Rc=1.2 k_, Find the maximum undistorted

peak to- peak output voltage.

(R-10,S-1,Aug-2012)

Department of Electronics and Communication EngineeringRAMACHANDRA COLLEGE OF ENGINEERING:

ELURU

Electronic Circuit Analysis Question Bank

R13 JNTU: Kakinada

II-ii B. Tech ECE

ELECTRONIC CIRCUITANALYSIS

UNIT-II

1. An RC coupled FET Amplifier has the following circuit values: R L =10K,

RG=500K, Cc=0.01F, Csh=150 pF, =25, rd=10 K and gm =2.5mA/V, find Am,

f1and f2 and also derive the three parameter expressions.

(R-10,S-1,Aug-2014)

2. Derive the relation between f2 and f2n when such, n-identical amplifier stages are

cascaded.

(R-10,S-1,Aug-2014)

3. In an RC-coupled BJT amplifier, it is given that RL=6.8k, effective AC load after

Cc is Rac=1k, Cc=1 f, CE=24F, RE=2.2k, hfe =49, RS=5k and hie=1k, find the low

frequency cut off point.

(R-10,S-2,Aug-2014)

4. An RC-coupled BJT amplifier, it is given that RL=6.8k, effective AC load after Cc

isRac=1k, Cc=1 f, CE=24F, RE=2.2k, hfe =49, RS=5k and hie=1k, find the low

frequency cut off point.

(R-10,S-1,Jan/Feb-2014)

5. Compare different types of amplifier circuits based on the type of coupling.

(R-10,S-1,Jan/Feb-2014)

6. The gain of an RC coupled 2 stage FET amplifier falls by 90% of the mid-band

value at 400 kHz. If gm of each FET is 10 m A/V, and total output capacitance

for each stage is 20 pf. Calculate the RL required and the stage mid-band gain.

(R-10,S-1,Jan/Feb-2015)

Department of Electronics and Communication EngineeringRAMACHANDRA COLLEGE OF ENGINEERING:

ELURU

Electronic Circuit Analysis Question Bank

R13 JNTU: Kakinada

II-ii B. Tech ECE

ELECTRONIC CIRCUITANALYSIS

7. A three stage CE amplifier using silicon BJT as shown Figure 5, has R F=50 K,

RF2=10K, =50, RL1=15 K and Vcc=20 V.

Calculate the value of V c3. Also show

that the amplifier is DC.

(R-10,S-3,April/May-2015)

8. Draw the circuit of two stages R-C coupled JFET amplifier and explain its

working.

(R-10,S-4,Aug-2014)

9. Draw the circuit diagram of single stage R-C coupled BJT amplifier. Discuss the

effect of an emitter bypass capacitor on low-frequency response.

(R-10,S-2,Jan/Feb-2014)

10.Differentiate between direct and capacitive coupling of multiple stages of

amplifiers.

(R-10,S-2,Jan/Feb-2014)

11.With the help of a neat circuit diagram, describe the working of a Cascode

amplifier

(R-10,S-1,Aug-2014)

12.The gain of an RC coupled 2 stage FET amplifier falls by 90% of the mid band

value at 400 kHz. If g m of each FET is 10 m A/V, and total output capacitance

for each stage is 20 pF, calculate the RL required and the mid band gain of each

stage

(R-10,S-4,April/May-2013)

13.Write a short note on Bandwidth of amplifiers

(R-10,S-1,Aug-2014)

14.List out the special features of Darlington pair and Cascode amplifiers

(R-10,S-2,May-2012)

15.A two-stage amplifier circuit (CE-CC configuration) is shown in figure 4b. The hparameter values are hfe = 50, hie=2 K ,hre =6 104, hoe = 25A/V. hfc = -51, hic

=2 K, hrc = 1, hoc = 25 A/V. Find the input and output impedances and

individual, as well as overall voltage and current gains. (R-10,S-2,Jan/Feb-2012)

16.For a Darlington pair the overall current gain and input impedance with an

emitter resistance are given as 1130 and 1.2 M respectively. Calculate the value

of emitter resistance RE.

(R-10,S-3,April/May-2013)

17.Three identical stages of amplifiers cascaded with lower and upper cut off

frequencies given by 300Hz and 5kHz respectively, compute the overall lower

and higher cut off frequencies with appropriate equations. (R-10,S-1,Aug-2014)

Department of Electronics and Communication EngineeringRAMACHANDRA COLLEGE OF ENGINEERING:

ELURU

Electronic Circuit Analysis Question Bank

R13 JNTU: Kakinada

II-ii B. Tech ECE

ELECTRONIC CIRCUITANALYSIS

18.What is frequency response of an amplifier? Draw the equivalent circuits of RC

coupled amplifier at low and high frequencies and derive the expression for

voltage gain.

(R-10,S-3,Dec-2012)

19.Two FET based amplifiers with gains of 30 dB are cascaded together. Find the

overall gain. Also find bandwidth of the overall circuit, if individual lower and

higher 3 dB frequencies are 20 Hz and 20 kHz respectively. (R-10,S-1,Jan/Feb-2012)

20.Show that the input impedance and overall voltage gain of a Darlington pair is

much larger compared to an individual CE amplifier with same transistor.

(R-10,S-1,Aug-2014)

21.Derive the expression for current gain of a two stage RC coupled CE amplifiers

(R-10,S-1,April/May-2013)

22.For a cascaded CE-CC configuration, the h-parameters are given ashfe=50,

hoe=10-4 A/V, hic=1k ,hrc=1, hfc= -51, hoc=10-4 A/V. Find the input and output

impedances of the cascaded configuration.

(R-10,S-1,Jan/Feb-2013)

23.Derive the expressions for overall voltage gain, current gain and power gain,

when two identical amplifier stages are cascaded.

(R-10,S-2,Dec-2012)

24. Draw the circuit of Darlington emitter follower. Explain why the input impedance is

higher than that of a single-stage emitter follower.

(R-10,S-3,April/May-2013)

25. When 2-stages of identical amplifiers are cascaded, obtain the expressions for overall

voltage gain and power gain.

(R-10,S-2,Aug-2014)

26. List out various types of distortions that occur in transistor amplifiers. Discuss the causes

for each.

(R-10,S-4,Aug-2014)

27. Write short notes on: Cascode amplifier b) Transformer coupled amplifier. c) Darlington

pair.

(R-10,S-1,April/May-2012)

28. Obtain the expressions for overall voltage gain, current gain and power gain of a twostage identical cascaded amplifier.

(R-10,S-1,Jan/Feb-2015)

29. What are the advantages of Darlington pair? Explain with a neat diagram.

(R-10,S-4,April/May-2012)

UNIT-III

1. Classify various feedback amplifiers. Explain how negative feedback improves

the characteristics of amplifier.

(R-10,S-1,Aug-2014)

2. For voltage series feedback amplifier with parameters of the internal amplifier as

AV= 200; Rin= 5K; R0= 20K; Bandwidth = 50 kHz and having feedback factor =

- 0.02. Calculate:

(R-10,S-1,Aug-2014)

Voltage gain AVf

i)

Input impedance Rinf

ii)

Output impedance Rof

iii)

3. Explain the nature of feedback in an emitter follower circuit. State the

advantages of this circuit and mention its use. Can this circuit be used as a

Department of Electronics and Communication EngineeringRAMACHANDRA COLLEGE OF ENGINEERING:

ELURU

Electronic Circuit Analysis Question Bank

R13 JNTU: Kakinada

voltage amplifier?

II-ii B. Tech ECE

ELECTRONIC CIRCUITANALYSIS

(R-10,S-3, April/May-2013)

4. The total harmonic distortion of an amplifier is reduced from 15% to 3% when

4% negative feedback is used. Find (i) voltage gain without feedback (ii) voltage

gain with feedback?

(R-10,S-1,Jan/Feb-2013)

5. A Common source FET amplifier has a load resistance of 500k . The ac drain

resistance of the device is 100k and the transconductance is 0.8mAV -1. Calculate

the voltage gain of the amplifier.

(R-10,S-1,Jan/Feb-2012)

6. Draw the block diagrams of four types of negative feedback amplifier circuits and

explain which amplifier can be used to get higher input impedance and lower

output impedance with appropriate derivation

(R-10,S-3,April/May-2013)

7. Apply the method of feedback circuit analysis for a voltage series feedback

amplifier and explain all steps with appropriate diagrams.

(R-10,S-1,Aug-2014)

8. Prove that negative feedback in amplifiers reduces the distortion and noise with

appropriate equations.

(R-10,S-1,Jan/Feb-2014)

9. An Amplifier with negative feedback gives an output of 12.5V with an input of

1.5V.

(R-10,S-4,April/May-2013)

10.When feedback is removed, it requires 0.25V input for the same output. Find i)

Value of voltage gain without feedback ii) Value of , if the input and output are

in phase and is real.

(R-10,S-4,Aug-2014)

11.Explain the procedure to obtain the basic amplifier configuration without

feedback but taking the loading of the feedback network into account

( R-10,S-1,Jan/Feb-2015)

12.An amplifier has a mid band gain of 125 and bandwidth of 250 kHz. If 4%

negative feedback is introduced and the new bandwidth and gain.

(R-10,S-3,April/May-2013)

13.Derive the equations for voltage gain, input impedance and output impedance of

a CE amplifier with current-shunt negative feedback. (R-10,S-1,April/May-2013)

14.Explain the effects of negative feedback on amplifier characterisitcs?

(R-10,S-3,April/May-2013)

15.An amplifier having a gain of 500 without feedback has an overall negative

feedback applied which reduces the gain to 100.Calculate the fraction of output

voltage feedback? If due to ageing of components, the gain without feedback falls

by 20% calculate the percentage fall in gain with feedback?

(R-10,S-1,Jan/Feb-2012)

16.If the non-linear distortion in a negative feedback amplifier with an open loop

gain of 100 is reduced from 40% to 10%with feedback, compute the feedback

factor, of the amplifier.

(R-10,S-2,Jan/Feb-2015)

30.Draw the circuit diagram of a current series feedback amplifier, Derive

expressions to show the effect of negative feedback on input & output

impedances, bandwidth, distortion of the amplifier.

(R-10,S-1,Aug-2014)

31.The and the open loop gain of an amplifier are -10% and -80 respectively. By

Department of Electronics and Communication EngineeringRAMACHANDRA COLLEGE OF ENGINEERING:

ELURU

Electronic Circuit Analysis Question Bank

R13 JNTU: Kakinada

II-ii B. Tech ECE

ELECTRONIC CIRCUITANALYSIS

how much % the closed loop gain changes if the open loop gain increases by

25%?

(R-10,S-3,April/May-2013)

17.With the help of a suitable BJT based voltage series feedback amplifier diagram,

explain the features and benefits of negative feedback in amplifiers.

(R-10,S-2,Jan/Feb-2014)

18.Derive the expressions for Av, Zi, Zo and AI of voltage shunt feedback.

(R-10,S-3,April/May-2013)

19.Determine voltage gain, input and output impedance of negative feedback amplifier

having A=100, Ri=10k Ro=20k for a feedback factor of =0.1 and 0.5.

(R-10,S-

3,April/May-2013)

20.Explain the general characteristics of negative feedback amplifiers. Compare the

advantages and disadvantages of positive and negative feedback. (R-10,S3,April/May-2013)

21.Derive the expressions for voltage gain, R i and Ro of voltage series feedback

amplifiers. (R-10,S-3,April/May-2013)

22.What are the different types of feedback amplifiers? Give their equivalent

circuits. (R-10,S-3,April/May-2013)

23.Explain with the help of mathematical expressions, how the negative feedback in

amplifiers increases.amplifier bandwidth and reduces distortion in amplifiers. (R10,S-3,April/May-2013)

24.An amplifier circuit has a gain of 60 dB and an output impedance Z o=10K. It is

required to modify its output impedance to 500 by applying negative feedback.

Calculate the value of the feedback factor. Also find the percentage change in the

overall gain, for 10% change in the gain of the internal amplifiers.

(R-10,S-3,April/May-2013)

25. Explain the advantages of negative feedback amplifiers. (R-10,S-3,April/May-2013)

26. What is linear analysis of feedback amplifiers? Illustrate with examples. (R-10,S-3,April/May2013)

27. Show that bandwidth increases with negative feedback. (R-10,S-3,April/May-2013)

28. Draw the block diagram of a single loop negative feedback circuit and explain each and

every block in detail. (R-10,S-3,April/May-2013)

29. Draw and explain the circuit of a voltage series feedback circuit. (R-10,S-3,April/May-2013)

30. What are types of amplifier circuits in any feedback systems? Discuss. (R-10,S-3,April/May2013)

31. What are the basic amplifiers used in a negative feedback system. Derive the relationship

between input and source resistance, output and load resistance of these basic amplifiers.

(R-10,S-3,April/May-2013)

32. Show that input resistance increases with series mixing.

(R-10,S-3,Aug-2014)

UNIT-IV

1. Draw the circuit diagram of Colpitts oscillator. Explain its disadvantages. How

it is overcome with Clapp oscillator.

(R-10,S-2,Jan/Feb-2015)

2. Prove that in an RC-phase shift oscillator, the minimum h fe required is 29 to

Department of Electronics and Communication EngineeringRAMACHANDRA COLLEGE OF ENGINEERING:

ELURU

Electronic Circuit Analysis Question Bank

R13 JNTU: Kakinada

II-ii B. Tech ECE

ELECTRONIC CIRCUITANALYSIS

sustain the frequency of oscillations.

(R-10,S-2,Jan/Feb-2015)

3. Derive the equation for frequency of oscillations of a FET RC-phase shift

Oscillator and also derive condition for sustained oscillations.

(R-10,S-2,Jan/Feb-2015)

4. Prove that the gain of Wien bridge oscillator using BJT amplifier must be at

least 3 for the oscillations to occur. (R-10,S-2,Jan/Feb-2015)

5. Derive the expression for frequency of oscillation of BJT phase-shift oscillator

its operation with neat circuit diagram. (R-10,S-2,Jan/Feb-2015)

6. A crystal oscillator has the following parameters: L=0.33H, C=0.065pF, C=1.0pF

and R=5.5k . i) Find the series resonant frequency. ii) Find the Q of the

crystal. (R-10,S-2,Jan/Feb-2015)

33.Find the capacitance C and h fe for the transistor Phase-Shift oscillator to provide

a resonating frequency of 10kHZ. Assume R1=25k , R2=60 k , Rc=40k , R=7.1k

and hie=1.8k . (R-10,S-2,Jan/Feb-2015)

34.Explain barkhausen criterion for sustained oscillations and also explain how the

criterion is satisfied in a BJT RC- Phase-Shift oscillator. (R-10,S-2,Jan/Feb-2015)

35.Classify different type of oscillators based on frequency range.

(R-10,S-2,Jan/Feb-

2015)

36.Calculate the value of C used in the Wein-bridge circuit that determines the

oscillator frequency of 10 kHz. Assume R=50 K in the Wein-bridge circuit. (R-10,S2,Jan/Feb-2015)

37.Draw the electrical equivalent circuit of a crystal and draw the frequency versus

reactance curve and show the two resonant frequencies f S and fP on the graph. (R10,S-2,Jan/Feb-2015)

38.Describe the crystal oscillator. What is the advantage of a crystal oscillator over

an LC oscillator? (R-10,S-2,Jan/Feb-2015)

39.A tuned collector oscillator connected across the primary has a capacitance of

100pF.The d.c resistance of the primary coil is 10 ohm and the transistor used

has hie=1k ohm, hre=10-4, hfe=50 and hoe=10-4 A/V. Find the frequency of

oscillation and the mutual inductance between the primary and secondary coils

required to sustain the oscillations ? (R-10,S-2,Jan/Feb-2015)

40.Draw the circuit diagram of Colpitts oscillator. Explain its disadvantages.

How it is overcome with Clapp oscillator. (R-10,S-2,Jan/Feb-2015)

41.Prove that in an RC-phase shift oscillator, the minimum h fe required is 29 to

sustain the frequency of oscillations. (R-10,S-2,Jan/Feb-2015)

42. Draw the circuit of colpitts oscillator and explain its working. Derive the frequency of

oscillator and condition for sustained oscillation. (R-10,S-2,Jan/Feb-2015)

43. State and explain Barkhausen criterion. (R-10,S-2,Jan/Feb-2015)

44. Draw the block diagram of generalized LC oscillator and from that derive the frequency of

oscillation for a) Hartley Oscillator b) Colpitts Oscillator. (R-10,S-2,Jan/Feb-2015)

45. Derive frequency of oscillation of a Wien-bridge oscillator circuit with necessary

diagrams. (R-10,S-2,Jan/Feb-2015)

Department of Electronics and Communication EngineeringRAMACHANDRA COLLEGE OF ENGINEERING:

ELURU

Electronic Circuit Analysis Question Bank

R13 JNTU: Kakinada

II-ii B. Tech ECE

ELECTRONIC CIRCUITANALYSIS

46. What is the Condition for sustained oscillations and draw and explain the RC-phase shift

oscillators with Transistor.

(R-10,S-2,Jan/Feb-2015)

UNIT-V

1. Explain why a power amplifier is always preceded by a voltage amplifier?

(R-10,S-1,Jan/Feb-2015)

2. Design a class B power amplifiers to deliver 25 W to a load resistor R L = 8 ohms,

using transformer coupling. Vm = Vcc=25V. Assume necessary data.

(R-10,S-2,Jan/Feb-2015)

3. Derive the equation for maximum value of efficiency of a class A transformer

coupled amplifier.

(R-10,S-1,Jan/Feb-2015)

4. Calculate the effective load resistance RL seen looking into the primary of

a10:1 transformer connected to an output load of 16 ohms. (R-10,S-2,Jan/Feb-2015)

Define conversion efficiency of an amplifier. (R-10,S-4,Jan/Feb-2015)

4.

Draw the circuit of transformer less push pull amplifier circuit with loud speaker as

the load resistance. Justify the circuit operation with emitter follower circuit

working. (R-10,S-3,aug-2014)

5.

Calculate transformer turns ratio required to match an 8 ohms speaker load to an

amplifier so that effective load resistance is 3.2 kilo-ohms. (R-10,S-2,Jan/Feb-2015)

6.

7. Derive the expression for maximum collector Power Dissipation P c(Max) in the

case of class B power amplifiers. . (R-10,S-3,aug-2014)

8. Draw the circuit diagram of a single ended power amplifier? Explain the function

of each component used in he circuit? . (R-10,S-2,aug-2014)

9. Classify large signal amplifiers based on its operating point. Distinguish these

amplifiers in terms of the conversion efficiency. . (R-10,S-1,aug-2014)

10.Draw the push-pull power amplifier circuit. Derive the expression for the output

current in push- pull amplifier with base current as I b = Ibmsint. . (R-10,S-4,aug2014)

11.A single stage class A amplifier Vcc=20V, VCEQ =10V, ICQ =600 mA, RL=16

Department of Electronics and Communication EngineeringRAMACHANDRA COLLEGE OF ENGINEERING:

ELURU

Electronic Circuit Analysis Question Bank

R13 JNTU: Kakinada

II-ii B. Tech ECE

ELECTRONIC CIRCUITANALYSIS

The ac outputcurrent varies by 300mA, with the ac input signal. Find The power

supplied by the dc source to the amplifier circuit.

i)AC power consumed by the load resistor.

ii)AC power developed across the load resistor.

iii)DC power wasted in transistor collector.

iv)Overall efficiency

. (R-10,S-3,jan/feb-2014)

12.What are the drawbacks of transformer coupled power amplifiers? .

(R-10,S-1,jan/feb-2014)

13.What is Harmonic distortion in transistor amplifier circuits? Discuss second

harmonic distortion. . (R-10,S-2,jan/feb-2014)

14.A single transistor is operating as an ideal class B amplifier with a 500 load. A

dc meter in the collector circuit reads 10 mA. How much signal power is

delivered to the load? . (R-10,S-1,jan/feb-2014)

15.Write short notes on requirement and types of heat sinks for power dissipation

in large signal amplifiers. . (R-10,S-4,jan/feb-2014)

16.With the help of a neat circuit diagram, explain the operation of a

complementary symmetry configured class B power amplifier. .

(R-10,S-1,jan/feb-2014)

17.A push pull amplifier utilizes a transformer whose primary has a total of 160

turns and whose secondary has 40 turns. It must be capable of delivering 40W

to an 8 load under maximum power conditions. What is the minimum possible

value of Vcc? . (R-10,S-3,april/may-2013)

18.Differentiate between push-pull and complementary-symmetry configurations of

a class B power amplifier. (R-10,S-2,april/may-2013)

19.Explain the reasons for crossover distortion in class-B power amplifiers and

suggest a suitable circuit for its minimization. (R-10,S-2,april/may-2013)

20.Derive the expression for Maximum efficiency and working of transformer coupled

Class A Amplifier(R-10,S-1,april/may-2013)

21.Define collector circuit efficiency of a power amplifier and explain how total

distortion can be reduced in a power amplifier through push-pull configuration.

(R-10,S-3,april/may-2013)

22.Explain how the power amplifiers are classified based on class of operation and

also compare. (R-10,S-1,april/may-2013)

23.A single transistor is operating as an ideal class B amplifier with a 1-K load. A dc

meter in the collector circuit reads 10mA. How much signal power is delivered to

the load? (R-10,S-3,aug-2014)

24.Derive the efficiency of the class-B power amplifier. Though class-B single ended

power amplifier efficiency is high, why it is not used in practical circuits?

Explain in detail. (R-10,S-2,aug-2014)

25.What are the disadvantages of using transformers in a push-pull amplifier?

(R-10,S-1,aug-2014)

26.Explain a few techniques that eliminates the use of input transformers.

(R-10,S-1,aug-2014)

Department of Electronics and Communication EngineeringRAMACHANDRA COLLEGE OF ENGINEERING:

ELURU

Electronic Circuit Analysis Question Bank

R13 JNTU: Kakinada

II-ii B. Tech ECE

ELECTRONIC CIRCUITANALYSIS

27. What are the advantages of push-pull connection in AF power amplifiers?

(R-10,S-1,aug-2014)

28. Design a push-pull class B power amplifier to achieve maximum output power to a 10 _

load. The two transistors have the following ratings Pc(max) = 5W; VCE(max) = 45V.

IC(max) = 1A. Assume Necessary data. (R-10,S-2,jan/feb-2014)

29. With a neat circuit diagram explain the operation of class AB power amplifier and

mention its advantages. (R-10,S-1,jan/feb-2015)

30. Draw the circuit of class-B Power amplifier. Explain its operation and derive the

expression for efficiency of the amplifier by making necessary assumptions

(R-10,S-2,jan/feb-2015)

UNIT-VI

1. Statethe functions and frequency ranges of operation of Tuned amplifiers with

relevant reasons.

(R-10,S-1,jan/feb-2015)

2. Explain and also mention the class of operation of the amplifier for limiting the

amplitude of gain to the desired level

(R-10,S-2,jan/feb-2015)

3. Derive the equation for the 3 dB band width of capacitance coupled single

tuned amplifier.

(R-10,S-3,jan/feb-2015)

4. Explain the principle of stabilizing the double-tuned transformer coupled

amplifier response against the internal feedback. (R-10,S-4,jan/feb-2015)

5. Explain the function of swamping resistor in improving the bandwidth of tuned

amplifiers. (R-10,S-1,jan/feb-2014)

6. Draw the circuit of typical single tuned RF amplifier stage employing a

transistor, explain its operation. If the tuned circuit contains L=200H,

C=126pF, RL=5 k. Calculate the Bandwidth of the amplifier. (R-10,S-2,jan/feb-2014)

7. Explain the principle of stagger tuning technique of transformer-coupled

amplifier that is used to obtain band pass filter characteristic with band of 10

KHZ with all necessary diagrams for illustration. (R-10,S-3,jan/feb-2014)

8. Draw the circuit of double-tuned transformer-coupled amplifier. Discussthe

nature of responses of the amplifier for different values of KQ=1; KQ>1 and

KQ<1. (R-10,S-4,jan/feb-2014)

9. Draw a simple BJT tuned amplifier circuit and its ideal response

characteristics. (R-10,S-1,aug-2014)

10.Inthe single tuned amplifier, the circuit bandwidth is 5 kHz and voltage gain

has a maximum value at 1000 kHz, when the tuning capacitor is adjusted to

500 pf. Calculate the (R-10,S-2,aug-2014)

11.Draw the circuit diagram and small signal AC equivalent circuit of a single

tuned amplifier (using BJT) with the tank circuit connected at the input side.

R-10,S-3,aug-2014)

Department of Electronics and Communication EngineeringRAMACHANDRA COLLEGE OF ENGINEERING:

ELURU

Electronic Circuit Analysis Question Bank

R13 JNTU: Kakinada

II-ii B. Tech ECE

ELECTRONIC CIRCUITANALYSIS

12.With a neat diagram show how to cascade tuned amplifiers and determine gain

and band width. (R-10,S-4,aug-2014)

13.What is synchronous tuning? Derive an expression for bandwidth of an n-stage

synchronously tuned amplifier? (R-10,S-1,april/may-2013)

14.Show that for an n stage synchronously tuned amplifier; maximum bandwidth

is obtained when the single stage gain is 4.34 dB. (R-10,S-2,april/may-2013)

15.Derive an expression for bandwidth of a capacitive coupled tuned amplifier in

CE configuration. Make necessary assumptions and mention them

(R-10,S-3,april/may-2013)

16.Discuss the necessity of stabilization circuits in tuned amplifiers.

(R-10,S-4,april/may-2013)

17.Draw the circuit diagram of a Double tuned amplifier. Draw and explain in

detail the frequency response for different values of coefficient of coupling (K)

i.e. K=1, K= 1.5, K=2 and also explain what is Loose coupling and Tight

coupling? (R-10,S-1,april/may-2013)

18.What is synchronous tuning? Derive an expression for bandwidth of an n-stage

synchronously tuned amplifier? (R-10,S-1,jan/feb-2015)

19.Show that for an n stage synchronously tuned amplifier, maximum. bandwidth

is obtained when the single stage gain is 4.34 dB. (R-10,S-2,jan/feb-2015)

20.Explain how the stagger-tuned design is superior to synchronously tuned design

in the design of a multistage amplifier? (R-10,S-3,jan/feb-2015)

21.Explain the working of Single Tuned Amplifier with circuit diagram.

(R-10,S-1,jan/feb-2014)

22.Explain the significance of various levels of coupling of transformer used in

double tuned amplifiers with necessary diagrams. (R-10,S-3,jan/feb-2014)

23. Discuss about the effect of Cascading Single tuned amplifiers on Band width.

(R-10,S-1,aug-2014)

24. What are the limitations of stagger tuned amplifiers?

(R-10,S-4 ,aug-2014)

25. Explain the operation of single tuned amplifier and derive the expression for Q factor.

(R-10,S-3,aug-2014)

26. What is staggering of tuned amplifiers? Discuss about its advantages and disadvantages.

(R-10,S-1,jan/feb-2015)

27. Substantiate the necessity of the following in tuned amplifiers.

a) Heat Sinks

b) Stabilization circuits

(R-10,S-4,,jan/feb-2014)

Department of Electronics and Communication EngineeringRAMACHANDRA COLLEGE OF ENGINEERING:

ELURU

Electronic Circuit Analysis Question Bank

Vous aimerez peut-être aussi

- L211 Series Resonance and TimeFrequency Response of Passive Networks PDFDocument25 pagesL211 Series Resonance and TimeFrequency Response of Passive Networks PDFglenlcy100% (1)

- Impedance of RL Circuits: Series RL Circuits: Experiment No. 2Document16 pagesImpedance of RL Circuits: Series RL Circuits: Experiment No. 2NicoPas encore d'évaluation

- 9A04402 Electronic Circuit AnalysisDocument8 pages9A04402 Electronic Circuit AnalysissivabharathamurthyPas encore d'évaluation

- RA 9A04402 Electronic Circuits AnalysisDocument2 pagesRA 9A04402 Electronic Circuits AnalysissivabharathamurthyPas encore d'évaluation

- Jntu Hyd 2 2ece Eca Set 2Document18 pagesJntu Hyd 2 2ece Eca Set 2Travis BennettPas encore d'évaluation

- ECA (R10) April 2012 PDFDocument93 pagesECA (R10) April 2012 PDFhvrkPas encore d'évaluation

- Iec Lab - Exp 08 - Fall 23-24Document8 pagesIec Lab - Exp 08 - Fall 23-24rakibulislamakash40Pas encore d'évaluation

- ECA FinalDocument4 pagesECA Final143ramyaPas encore d'évaluation

- AnalogIntegratedCircuts LAB MANUAL by Prabhu Kumar SurarapuDocument80 pagesAnalogIntegratedCircuts LAB MANUAL by Prabhu Kumar Surarapuprabhu4scribdPas encore d'évaluation

- Analog Multiplier Using Operational AmplifiersDocument4 pagesAnalog Multiplier Using Operational AmplifiersxongassilvaPas encore d'évaluation

- 9A04402 Electronic Circuit AnalysisDocument4 pages9A04402 Electronic Circuit AnalysissivabharathamurthyPas encore d'évaluation

- Exp 8Document12 pagesExp 8esumshunPas encore d'évaluation

- Electronic Devices and Circuits 2-1 N-D-12Document15 pagesElectronic Devices and Circuits 2-1 N-D-12nbprPas encore d'évaluation

- AEC Lab ManualDocument70 pagesAEC Lab ManualRohan BosePas encore d'évaluation

- Answer All QuestionsDocument1 pageAnswer All QuestionsBIBIN CHIDAMBARANATHANPas encore d'évaluation

- Iec Lab - Exp 08 - Fall 23-24Document8 pagesIec Lab - Exp 08 - Fall 23-24mahinc021Pas encore d'évaluation

- Electronic Circuit AnalysisDocument8 pagesElectronic Circuit AnalysisToaster97Pas encore d'évaluation

- Laboratory Manual: EM 222 Circuit Analysis IiDocument6 pagesLaboratory Manual: EM 222 Circuit Analysis IiHarun KahramanPas encore d'évaluation

- Exp 6 - OscillatorDocument6 pagesExp 6 - OscillatorJanica Rheanne JapsayPas encore d'évaluation

- Experiment 2 Lab ManualDocument6 pagesExperiment 2 Lab ManualSikat Gabriel L.100% (1)

- All The Best.: +V VCC RC RFDocument2 pagesAll The Best.: +V VCC RC RFMaheswaran UmaiyorupaganPas encore d'évaluation

- 2.electronics Circuits IIDocument9 pages2.electronics Circuits IImanimangaiPas encore d'évaluation

- 9A02405 Analog Electronic CircuitsDocument4 pages9A02405 Analog Electronic CircuitssivabharathamurthyPas encore d'évaluation

- Digital Assignment - I: Sig Sig L C A CDocument2 pagesDigital Assignment - I: Sig Sig L C A CMudit SharmaPas encore d'évaluation

- B S F E, 2011: Achelor OF Cience Inal XaminationDocument3 pagesB S F E, 2011: Achelor OF Cience Inal XaminationSaikat PayraPas encore d'évaluation

- Lab Report 2Document17 pagesLab Report 2Nguyễn ThắngPas encore d'évaluation

- Ee 352 Ec Ii LabDocument61 pagesEe 352 Ec Ii LabSatya SandeepPas encore d'évaluation

- Pspice and Matlab For Electronics: An Integrated Approach: BibliographyDocument1 pagePspice and Matlab For Electronics: An Integrated Approach: BibliographyJohn SmithPas encore d'évaluation

- PWR Test 02Document1 pagePWR Test 02dabhianand13Pas encore d'évaluation

- RF OscillatorsDocument11 pagesRF OscillatorsMohammad Irani0% (1)

- LINEAR INTEGRATED CIRCUITS Question BankDocument17 pagesLINEAR INTEGRATED CIRCUITS Question BankDeepak SantPas encore d'évaluation

- Karpagam College of Engineering: Coimbatore-32Document2 pagesKarpagam College of Engineering: Coimbatore-32D Geetha DuraiPas encore d'évaluation

- Experiment No:-: Name of The Experiment: Components: ObjectiveDocument3 pagesExperiment No:-: Name of The Experiment: Components: ObjectiveSoumiPas encore d'évaluation

- Eee2210 Analogue Elec II Omae Tie-PrintreadyDocument4 pagesEee2210 Analogue Elec II Omae Tie-PrintreadyMike ShakespearePas encore d'évaluation

- A Simple Method For Tracing PV Curve of A Radial Transmission LineDocument4 pagesA Simple Method For Tracing PV Curve of A Radial Transmission LineWallison CarvalhoPas encore d'évaluation

- Práctica 1: Amplificador Emisor Común ObjetivoDocument4 pagesPráctica 1: Amplificador Emisor Común ObjetivoLuisa María LondoñoPas encore d'évaluation

- Jntu Hyd 2 2ece PDC Set 2Document18 pagesJntu Hyd 2 2ece PDC Set 2Krishna RamaPas encore d'évaluation

- Basic Op-Amp Circuits: EE 126 - Industrial Electronics Handout: Operational Amplifiers Operational Amplifiers (Op-Amps)Document6 pagesBasic Op-Amp Circuits: EE 126 - Industrial Electronics Handout: Operational Amplifiers Operational Amplifiers (Op-Amps)kyope17Pas encore d'évaluation

- AEC BankDocument9 pagesAEC BankprakashkerurPas encore d'évaluation

- Analog CircuitsDocument128 pagesAnalog CircuitsAnvesh MagantiPas encore d'évaluation

- Resonant TrafoDocument6 pagesResonant TrafoJojoy MonoPas encore d'évaluation

- Common Emitter Amplifier: S.No Name of The Component/ Equipment Specifications QtyDocument0 pageCommon Emitter Amplifier: S.No Name of The Component/ Equipment Specifications Qtyagama1188Pas encore d'évaluation

- Experiment No-4Document6 pagesExperiment No-4devanshurajpoot1Pas encore d'évaluation

- Half Wave Converter 1Document8 pagesHalf Wave Converter 1UddhavPas encore d'évaluation

- Electronic Circuit AnalysisDocument8 pagesElectronic Circuit AnalysisSatish SmartPas encore d'évaluation

- Audio Amplifier (English)Document11 pagesAudio Amplifier (English)Zhamir ZhakwanPas encore d'évaluation

- R7310204 Power ElectronicsDocument1 pageR7310204 Power ElectronicssivabharathamurthyPas encore d'évaluation

- Experiment 5Document4 pagesExperiment 5Jay LopezPas encore d'évaluation

- C1EC01-C1405 - ELECTRONIC CIRCUIT ANALYSIS & DESIGN MergedDocument18 pagesC1EC01-C1405 - ELECTRONIC CIRCUIT ANALYSIS & DESIGN Mergedchini_naniPas encore d'évaluation

- Analog Electronic Circuit (ECE - 201)Document3 pagesAnalog Electronic Circuit (ECE - 201)Manoj Kumar RPas encore d'évaluation

- R5100207-Electronic Devices & CircuitsDocument2 pagesR5100207-Electronic Devices & CircuitssivabharathamurthyPas encore d'évaluation

- Common Emitter Transistor Common Emitter Transistor Amplifier AmplifierDocument9 pagesCommon Emitter Transistor Common Emitter Transistor Amplifier AmplifierMauro FernandoPas encore d'évaluation

- Electric Circuits &electronics Device Question PaperDocument5 pagesElectric Circuits &electronics Device Question PaperSalai Kishwar JahanPas encore d'évaluation

- Chap 1Document84 pagesChap 1lvsaruPas encore d'évaluation

- Audio IC Circuits Manual: Newnes Circuits Manual SeriesD'EverandAudio IC Circuits Manual: Newnes Circuits Manual SeriesÉvaluation : 5 sur 5 étoiles5/5 (1)

- Exercises in Electronics: Operational Amplifier CircuitsD'EverandExercises in Electronics: Operational Amplifier CircuitsÉvaluation : 3 sur 5 étoiles3/5 (1)

- Instrumentation and Test Gear Circuits ManualD'EverandInstrumentation and Test Gear Circuits ManualÉvaluation : 5 sur 5 étoiles5/5 (1)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1D'EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Évaluation : 4.5 sur 5 étoiles4.5/5 (3)

- Non-Redundant Radix-8 Signed Digit Encoding Techniques For DesigningDocument30 pagesNon-Redundant Radix-8 Signed Digit Encoding Techniques For DesigningrppvchPas encore d'évaluation

- MWE Lesson Plan 2016-17Document3 pagesMWE Lesson Plan 2016-17rppvchPas encore d'évaluation

- Format Question Paper AnalysisDocument4 pagesFormat Question Paper Analysisrppvch0% (1)

- CellsDocument8 pagesCellsrppvchPas encore d'évaluation

- By, CH - Praveen 14ME1D5703 M.Tech - VLSI Under The Guidance Of, MR.D Venkanna Babu Assistant Professor, Dept. of ECEDocument68 pagesBy, CH - Praveen 14ME1D5703 M.Tech - VLSI Under The Guidance Of, MR.D Venkanna Babu Assistant Professor, Dept. of ECErppvchPas encore d'évaluation

- The Aging-Aware Vedic Multiplier Design With The AhlDocument17 pagesThe Aging-Aware Vedic Multiplier Design With The AhlrppvchPas encore d'évaluation

- EMI 1unitDocument44 pagesEMI 1unitrppvchPas encore d'évaluation

- Oc Nov 2014 Solns JntukDocument62 pagesOc Nov 2014 Solns JntukrppvchPas encore d'évaluation

- Electronic Instrumentation H S KalsiDocument652 pagesElectronic Instrumentation H S KalsiAjayChandrakar60% (10)

- Digital Logic DesignDocument4 pagesDigital Logic DesignrppvchPas encore d'évaluation

- Electronic Instrumentation H S KalsiDocument652 pagesElectronic Instrumentation H S KalsiAjayChandrakar60% (10)

- MIxed Signal Simulation Lab Manual I M.tech II SemDocument150 pagesMIxed Signal Simulation Lab Manual I M.tech II SemrppvchPas encore d'évaluation

- Edc SP UpdatedDocument14 pagesEdc SP UpdatedrppvchPas encore d'évaluation

- Eca Labmanual MultisimDocument57 pagesEca Labmanual Multisimvinodh123Pas encore d'évaluation

- MRK DSP Subjects1Document4 pagesMRK DSP Subjects1rppvchPas encore d'évaluation

- Mpi Viva LabDocument3 pagesMpi Viva LabrppvchPas encore d'évaluation

- Eca Lab Manual PDFDocument56 pagesEca Lab Manual PDFrppvch100% (5)

- Gate EC Syllabus and WeightageDocument4 pagesGate EC Syllabus and WeightagerppvchPas encore d'évaluation

- Face Detection and Tracking Using Live Video Acquisition - MATLAB & Simulink Example - MathWorks IndiaDocument5 pagesFace Detection and Tracking Using Live Video Acquisition - MATLAB & Simulink Example - MathWorks IndiarppvchPas encore d'évaluation

- Chapter 7 of Fundamentals of MicroelectronicsDocument33 pagesChapter 7 of Fundamentals of MicroelectronicsjenellanePas encore d'évaluation

- Eca PDC Lab ManualDocument146 pagesEca PDC Lab Manualsoumya varanasiPas encore d'évaluation

- 197Document113 pages197Dhanya Geethanjali SasidharanPas encore d'évaluation

- Lec04 Ae Ms14Document37 pagesLec04 Ae Ms14Mohsin Abbas ZafarPas encore d'évaluation

- Common SourceDocument4 pagesCommon SourceSteve Aaron BernardoPas encore d'évaluation

- Lec17 Cascade AmplifiersDocument7 pagesLec17 Cascade AmplifiersJai KumarPas encore d'évaluation

- ZVP2106A ZVP2106A: Typical CharacteristicsDocument3 pagesZVP2106A ZVP2106A: Typical CharacteristicsMuhammad ZahidPas encore d'évaluation

- Session-04-Current Mirror and Single Stage AmplifierDocument68 pagesSession-04-Current Mirror and Single Stage Amplifieraravind787750% (2)

- The MOSFET AmplifierDocument135 pagesThe MOSFET AmplifierRodrigo WilliamsPas encore d'évaluation

- The Bridged T-CoilDocument5 pagesThe Bridged T-CoilAhmad KamalPas encore d'évaluation

- Switching Regulator Applications: Absolute Maximum RatingsDocument6 pagesSwitching Regulator Applications: Absolute Maximum RatingsLeo GuillermoPas encore d'évaluation

- Electronics Ch5Document31 pagesElectronics Ch5Boudi ChouPas encore d'évaluation

- Field Effect Transistors (Fets) : - Two Types of FetDocument28 pagesField Effect Transistors (Fets) : - Two Types of FetCruise_IcePas encore d'évaluation

- Design of A 2.0 GHZ Low Noise AmplifierDocument4 pagesDesign of A 2.0 GHZ Low Noise AmplifierVaibhav TiwariPas encore d'évaluation

- A 77-GHz CMOS Automotive Radar TransceiverDocument9 pagesA 77-GHz CMOS Automotive Radar TransceiverAbderrahimPas encore d'évaluation

- N-Channel JFET: J210 - J212 / SSTJ210 - SSTJ212Document2 pagesN-Channel JFET: J210 - J212 / SSTJ210 - SSTJ212Luis Carlos OrtegaPas encore d'évaluation

- Polyfet RF Devices: Silicon Gate Enhancement Mode RF Power Transistor VdmosDocument2 pagesPolyfet RF Devices: Silicon Gate Enhancement Mode RF Power Transistor Vdmospatolin_123Pas encore d'évaluation

- Design of Common Source Amplifier: September 2016Document7 pagesDesign of Common Source Amplifier: September 2016Trọng HùngPas encore d'évaluation

- Multiple Choice Questions and Answers On FETDocument14 pagesMultiple Choice Questions and Answers On FETfarhanPas encore d'évaluation

- ABC's of FET's - Rufus P. Turner PDFDocument94 pagesABC's of FET's - Rufus P. Turner PDFAmador Garcia IIIPas encore d'évaluation

- Cascode AmplifierDocument4 pagesCascode AmplifierJoshua LandoyPas encore d'évaluation

- RFIC Notes PDFDocument145 pagesRFIC Notes PDFramanjulun100% (1)

- Lecture NotesDocument28 pagesLecture NotesEE22M306 Manvi ChaudharyPas encore d'évaluation

- Biasing PDFDocument20 pagesBiasing PDFSandhya KrishnamurthyPas encore d'évaluation

- Liu 2021Document14 pagesLiu 2021randomPas encore d'évaluation

- A Study of Different Types of Voltage & Current Sense Amplifiers Used in SRAMDocument6 pagesA Study of Different Types of Voltage & Current Sense Amplifiers Used in SRAMVikas JainPas encore d'évaluation

- Microelectronic CircuitsDocument33 pagesMicroelectronic Circuitsmome 85Pas encore d'évaluation

- Yongheng Yang CPSS Transactions On Power Electronics and Applications CPSS TPEA Vol PDFDocument107 pagesYongheng Yang CPSS Transactions On Power Electronics and Applications CPSS TPEA Vol PDFprembiharisaranPas encore d'évaluation

- Switching Investigations On A Sic Mosfet in A To-247 PackageDocument8 pagesSwitching Investigations On A Sic Mosfet in A To-247 PackageWesley de PaulaPas encore d'évaluation

- 3 Analog Electronics Lab PDFDocument4 pages3 Analog Electronics Lab PDFjeyepuvevPas encore d'évaluation