Académique Documents

Professionnel Documents

Culture Documents

Geometric Programming Based Power-Delay Optimization Using Transistor-Sizing For Submicron and Deep Submicron CMOS Inverter

Transféré par

suchi87Description originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Geometric Programming Based Power-Delay Optimization Using Transistor-Sizing For Submicron and Deep Submicron CMOS Inverter

Transféré par

suchi87Droits d'auteur :

Formats disponibles

Geometric Programming Based Power-Delay

Optimization using Transistor-Sizing for Submicron and

Deep Submicron CMOS Inverter

Manisha Pattanaik and Swapna Banerjee

Department of E & ECE,

Indian Institute of Technology, Kharagpur-721 302, INDIA

i n a n i s h 3 k L . e c c . i i t l - ~ . ~ ~ c t .swapna@ece.iitkgp.emet.in

in,

Abstruci-This paper proposes a new method to formulate

the transistor sizing problem as a geometric programming

by using a modified I-V model in the power-delay product

(PDP), for sub micron and deep sub micron CMOS

inverter circuit. The design objective and constraints are

modeled as posynomial functions of the design variables.

The model has been solved efficiently, which generates a

number of important practical consequences. This method

computes the absolute limit of performance for given

input frequency and load capacitance of a transistor and

technology parameters. The accuracy of performance

prediction in the transistor-sizing (through geometric

programming) problem is verified due to its closeness to

SPICE simulation (0.25-~m).results.Further the approach

has been extended to predict the transistor siring for deep

submicron (0.09- pm) CMOS inverter.

1. INTRODUCTION

Transistor sizing is the operation of enlarging or reducing

the channel width of the transistor. I t is an effcctive

technique to improve the dclay of a CMOS circuit. When

the channel width is increased the current drive capability

increases, which reduces the signal riseifall times at the

gate output. Thc area occupied by the transistors increases

with increased transistor sizcs and may increase the layout

area. Transistor sizes are the most important factor

affecting the area, performance and power dissipation of a

circuit comprising transistor network. The complexity of

transistor sizing is due to the fact that each transistor could

potentially introduce one dimension to the problem. In

some cases simple analytical models can be used: But

there is no analytical model that can be applied to a large

classofcircuits [ I ] .

Several approaches have been suggested in literahre [Z],

[3] that perform optimization for area, delay and power of

digital CMOS circuits. Analytical equation based

optimization requires the evaluation of circuit

pcdormances by using analytical equations. The closed

fonn delay expression for the CMOS inverter circuit based

on the alpha power law MOS model [4] includes the

camier velocity saturation effect for short channel devices.

But it is not giving accurate results particularly for

nanoscale MOSFET devices (below 100nm). Further it

has been observed that though the model proposed by

Yutao Ma et. al [ 5 ] performed well up to 90 nm MOSFET,

the output characteristics for current voltage inodel

dcviates from the experimental results when both V,, and

Vdr are high. A direct approach for transistor sizing is to

minimize the power consumption of a circuit subjected to

a delay constraint. For such an approach to bc applicable,

particularly in deep sub micron regime, a reliable model

for power consumption of a CMOS inverter circuit with

respect to transistor sizing is essential. The objective of

this paper is to develop the power-delay product (PDP)

model by using a compact I-V model proposed in [ 6 ] ,[7]

which performs well for nanascale MOSFET devices.

The main purpose of developing the transistor sizing tool

is to explore the most ideal design solution at which the

circuit satisfies thc required specification and at the same

time the power delay product (PDP) is optimized. The

power delay product (PDP) function is non-linear in

nature, the coefficients of the terms are positive and the

exponents are not restrictcd to positive integers. So a

posynomial geometric programming (GP) approach is

proposed. Geometric programming is a special

optimization technique which is marked by its extreme

efficiency and truly global charactcristics 121, 131, 181, 191.

GP has been used recently to optimally design electronic

circuits including CMOS op-amps 131, transistor sizing of

CMOS circuits [8], 191.

The paper is organized as follows. Section 2 dep'icts the

modified power-delay model 161. Section 3 proposes a

geometric programming model with its solution. Section 4

analyses the results of thc proposed posynamial FP.

Section 5 summarizes the paper.

2. MODtFlED POWER-DELAY

MODEL

In order to analyze the operation of a CMOS inverter far

calculating the power, delay and power-delay product for

different frequencies and load capacitances, an input ramp

with transition time 'Y is applied to a CMOS invener.

The problem in this paper is focused on the dynamic

power dissipation of a CMOS inverter circuit.

The MOSFET drain c u m n t equation used for inverter

analysis is given in [ 6 ] as

I , = 0, V , < V,, (Cut off region)

(I)

Computer-aided Design and Testing /485

where z=n for NMOS transistor and z=p for PMOS

transistor.

P,,

= B,C,,

w* and P,

-

= B_C,,

L,

Wi

L,

are the transistor gain factor of the MOSFET device in

linear region and in saturation region respectively. B_

and B,, are used to control the characteristics of the

saturation region and linear region respectively as

discussed in [6].

The detail analysis for fast input and slow input ramp i s

discussed in [6]. The switching operation of CMOS

inverter is analyzed to determine its propagation delay. By

including the modified carrier mobility proposed in [5],

the propagation delay (t,) is expressed a s

In the above expression, x is the technological factor [6]

depends on the channel length and gate oxide thickness

(b,). So, the dynamic PDP expression can he represented

as follows.

The major focus of this paper is to minimize the PDP,

subjected to the constraints of the total output load

capacitance and the sizes (width) of NMOS and PMOS

transistors used in a simple inverter circuit.

3. GEOMETRIC

PROGRAMMING MODEL

The proposed geometric program (GP) model can be

expressed by rearranging the terms in the objective

function and the constraints and is given by the form

subiected to

where woI and wu2 are the contributions of the first and

second terms in the objective function.

4. RESULTSAND DISCUSSION

The geometric program developcd by using modified I-V

model [6] for minimizing PDP has been solved for

transistor sizing. 0 . 2 5 . ~CMOS technology is used for

inveiter analysis. The solution of geometric program

problem suggests that tlie expression for optimum

transistor sizing ratio for minimum PDP is indepcndent of

load capacitance at any operating frequency. Comparison

of the model results with the Spectre SPICE simulation

results [Figure I ] reveals that this ratio approximately

stabilizes at 2.2 for 0.25-pm technology. This result can bc

predicted accurately within the operating rangc of

frequency and load capacitance with marginal error

[Table. I and Table. 21. Further it has been observed that

the sizes of PMOS and NMOS transistors are increasing

almost linearly with the load and frequency to maintain

same minimum PDP which closcly inatchcs with the

Spectre SPICE simulation results [Figure 2 and Figure 31.

This proves the validity of the modified I-V model [6]

within the operating frequency and load by considering

only the dynamic power dissipation. The proposed GP

model behaves well for submicron (0.25pm) CMOS

inverter.

Our study has further been extended to predict valucs Ibr

deep sub micron range (below 101) om). Thc optimum

transistor sizcs for valying luad and operating frequency

for minimum PDP through geometric programming are

plotted for 0.25 pn in Figure 4 and Figure 5 and for 0.09

pin in Figure 6 and Figure 7. It is observed that though the

rate of increase in size for 0.09pm technology is almost

same with 0.25pm technology. the driving capability of

the circuit with minimum size transistors is more in

comparison to 0.25pm. Further i t has been revcslcd that

[Table. 31, a 0.25pm CMOS inverter can drive a inaninitmi

load of 50ff at 250MHz input frequency, whereas a

0.09pm CMOS inverter can drive a maximum load of

15OfF for the same operating frequency. The maximum

switching frequency with the ininimum size for 250MHz

input frequency is found to he 450 MHz for 0.25pm and

about 535MHz for0.09pm.

5. CONCLUSION

and the non-negativity condition

and a, b, a l , ai, a,,

parameters.

w I ' w,,and

C, 2 0

a4 are technology dependent

Since, the above problem is non-linear in nature and the

exponents ( positive and negative) of the variables do

occur in the expressions, it can he cast as a geometric

program [10][11][12]. By solving (6). (7) and (8), the

optimum ratio of transistor sizes for minimum PDP is as

follows:

A new power-delay posynoinial geomctric program inodcl

has been proposed for CMOS inverter, which is hctter

suited for modem technologies. The dynamic PDP hac

been minimized by considering the major factors dyiiamic

power, delay and area by putting limits on transistor width

and output voltage swing coupled with input load

capacitance. The proposed transistor-sizing problem can

handle a wide variety of specifications and constraints,

which is extremely fast and results in globally optimal

design with marginal error. An important point in judging

the correctness of our model is the correspondence ofthe

model delay of a sized circuit with that of its SPICE delay.

T fNCON 2003 I486

ACKNOWLEDGMENT

This work is partially supported by INTEL, Portland,

USA.

Table.1: Comparison of Model delay with SPICE delay

for 0.25-pm technology (Chd=50 fF)

REFERENCES

[ I ] Gary K. Yeap, Practical low power digital VLSl

design, Kluwer Academic Publishcr, MA, 1998.

[2] P. Mandal and V. Visvanathan, CMOS op-amp sizing

using a geometric programming formulation, IEEE

Trans. on Computer- Aided Design of Integrated Circuits

and Systems. January 2001,Vol. 20, No.1, pp. 22-38.

[3] M. M. Hershenson, S. P. Boyd and T. H. Lee,

GPCAD: A tool for CMOS op-amp synthesis,

Proceedings of International Conference on ComputerAided Design, 1998. pp. 296-303.

Table.2 Comparison of Model delay with SPICE delay

for 0.25-pm technology (Input frequency=500MHz)

[4] T. Sakurai and A. R. Newton, Alpha power law

MOSFET model and its applications to CMOS inverter

delay and other formulas, IEEE Journal of Solid State

Circuits, Vol. 25, pp. 584-594.

[SI Yutao Ma, L. Liu, L. Tian, Z. Yu and Z. Li,

Analvtical charee control and I-V model for

submicrometer and deep sub micrometer MOSFETs fully

comprising quantum mechanical effects, IEEE Trans on.

Computer-Aided Design, April 2001, .V,l. 20, No.4, pp.

495.502.

Table.3: Comparison results of Proposed Model between

~

.

0.2Spm and 0 . 0 9 technologies.

[6] M. Pattanaik and S. Banerjee, A new apptoach to

analyze a sub-micron CMOS inverter, 16Ih IEEEInternational Conference on VLSl Design, January 2003,

ISBN 0-7695-1868-0, pp. 116-121.

[7] M. Pattanaik and S. Banerjee, A new approach to

model the I-V characteristics for nanoscale MOSFETs, .

accepted for presentation at the 2003 International VLSl

Symposium on Technology, Systems and Applications to

be held at Taiwan [in press).

[SI S. S . Sapatnekar, V. B. Rao, P. M. Vaidya, and S . M.

Kang, An exact solution to the transistor sizing problem

for CMOS circuits using convex optimization, IEEE

Trans. on Computer-Aided Design, Nov. 1993, Vol. 12,

pp. 1621-1634.

[9] J. P. Fishburn and A. E. Dunlop. TILOS: A

posynomial programming approach to transistor sizing,

Proceedings of International Conference on Computer

Aided Design, 1995, pp. 326-328.

[IO] R. J. Dufiin, E. L. Peterson and C. Zener, Geometric

programming- Theory and application, John Wiley and

Sons, Inc. NY, 1967.

[ I l l C. Eeightler and D. T. Phill$s, Applied geometric

programming, John Wiley and Sons, Inc. NY, 1976.

1121 M. Avriel, (Edited) Advances

programming, Plenum Press, NY, 1980.

in geometric

l.lxlci .~. , ~ , . ~ ~ - . ~ ~ ~ . ...I :

2

2.2

2.4 2.6

W P .

2.8

Figure I Comparison of proposed model with SPICE

Computer-aided Design and Testing/487

250

zoo

-Proposed

15~1

I

,100

-150

5

--,roo

Symbol-SPICE

-Proposed

Symbol-SPICE

300%

666MHz

=5 504I

' o!-~

250

500

750

1000

ZSOMHz

;--

50ff

500MHz

400MHz

333MHz

50:

0

IUiMMHZ

300

ZOO

100

Frequency (MHz)

CL (fF)

Figure 2. Power-delay optimal PMOS sizes for different

input frequencies and different output load capacitances

(0.25-pm technology)

Figure 5. Power-delay optimal PMOS sizes for different

frequencies and different output load. (0.25-pm

technology)

. .~

+Wp(250 MHz)!

+Wp(333 MHz),

~~~

Symbol-SPICE

-Proposed

100,

i

80 !

400

1 -

Symbol-SPICE

- 5 1

-A-

541

;I

Wp(400 MHz),

X Wp(500 MHZ);

+-Wp(666 MHz):I

-e- Wp(1000 MHZ)

11

.....

..

~~~

250

500

750

01

0

1000

i

200

CL(fF)

Frequency (MHz)

Figure 3. Power-delay optimal NMOS sizes for different

frequencies and diff output load. (0.25-pm technology)

Symbol - SPICE

- 3

E

4

0

OOMHz

400MHz

333MHz

Z50MHz

5 :

'1

600

400

~i~~~~ 6 , optimum

PMOS siZe for ,,,in, p ~ (predicted

p

results using the proposed model for 0.09pm technology)

kWp(156fF

3.5

--

-e-Wp(2dOfF

-+-

2.5

Wp(250 f F

+wp(300 f F

+WP(3Mff)

5 2

*.~

WP(4W ff

~~~.

~~

0 '

0 1

0.5

100 200 300 400

CL

(fv

Figure 4. Power-delay optimal NMOS sizes for different

frequencies and diff output load. (0.25-tun technology)

,.

...l

~~~~

250 500 750 1000

Frequency (MHz)

Figure 7. Optimum PMOS Size for min. PDP (predicted

results using the proposed model for 0.09pm technology)

Vous aimerez peut-être aussi

- Solution Manual for 100 Genesys Design Examples: Second EditionD'EverandSolution Manual for 100 Genesys Design Examples: Second EditionPas encore d'évaluation

- Op Amp PaperDocument6 pagesOp Amp PaperSrinivasu IrlapatiPas encore d'évaluation

- Optimization Phase-Locked Loop Circuits Via Geometric ProgrammingDocument4 pagesOptimization Phase-Locked Loop Circuits Via Geometric ProgrammingAlex WongPas encore d'évaluation

- Optimising A D Flip Flop Through Delay and Power Estimation Using An RC Model and Transistor SizingDocument7 pagesOptimising A D Flip Flop Through Delay and Power Estimation Using An RC Model and Transistor SizingSavio SPas encore d'évaluation

- Research Article: 2.4 GHZ Cmos Power Amplifier With Mode-Locking Structure To Enhance GainDocument5 pagesResearch Article: 2.4 GHZ Cmos Power Amplifier With Mode-Locking Structure To Enhance GainRAJAMOHANPas encore d'évaluation

- Minimization Leakage Current of Full Adder Using Deep Sub-Micron CMOS TechniqueDocument7 pagesMinimization Leakage Current of Full Adder Using Deep Sub-Micron CMOS TechniqueInternational Journal of Application or Innovation in Engineering & ManagementPas encore d'évaluation

- ContentDocument6 pagesContentashwingeorge101Pas encore d'évaluation

- Speed-Power-Accuracy TradeoffDocument8 pagesSpeed-Power-Accuracy TradeoffbackspaceTABPas encore d'évaluation

- AnalogDocument8 pagesAnalogAhmed F RahimPas encore d'évaluation

- Electronics: Design of A Wide-Band Voltage-Controlled Ring Oscillator Implemented in 180 NM CMOS TechnologyDocument17 pagesElectronics: Design of A Wide-Band Voltage-Controlled Ring Oscillator Implemented in 180 NM CMOS TechnologyRam MPas encore d'évaluation

- Design of Folded Cascode OTA in Different Regions of Operation Through G /I MethodologyDocument6 pagesDesign of Folded Cascode OTA in Different Regions of Operation Through G /I MethodologyPramod SrinivasanPas encore d'évaluation

- Design Power and Controller For DC-DC Converter Systems Using PSPICEDocument6 pagesDesign Power and Controller For DC-DC Converter Systems Using PSPICEsandeepbabu28Pas encore d'évaluation

- Low voltage CMOS Schmitt Trigger in 0.18μm technology: Faiz Arith, M.Idzdihar.Idris, M.N.Shah Zainudin, S. A. M. ChachuliDocument8 pagesLow voltage CMOS Schmitt Trigger in 0.18μm technology: Faiz Arith, M.Idzdihar.Idris, M.N.Shah Zainudin, S. A. M. ChachuliIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- Power Constrained Design Optimization of Analog Circuits Based On Physical Gm/i CharacteristicsDocument7 pagesPower Constrained Design Optimization of Analog Circuits Based On Physical Gm/i CharacteristicsNanda KumarPas encore d'évaluation

- Cmos Comparator ThesisDocument5 pagesCmos Comparator Thesisannemarieolathe100% (1)

- Final ProjectDocument5 pagesFinal Projectnksharma.naveen1855Pas encore d'évaluation

- Electronics 08 01156 With CoverDocument18 pagesElectronics 08 01156 With Coverlravikumar.19.eeePas encore d'évaluation

- Double Tail Dynamic CompDocument10 pagesDouble Tail Dynamic CompBhura AnushaPas encore d'évaluation

- Low Power-Area Designs of 1bit Full Adder in Cadence Virtuoso PlatformDocument10 pagesLow Power-Area Designs of 1bit Full Adder in Cadence Virtuoso PlatformAnonymous e4UpOQEPPas encore d'évaluation

- Design of Folded Cascode OTA in Different Regions of Operation Through gmID Methodology PDFDocument6 pagesDesign of Folded Cascode OTA in Different Regions of Operation Through gmID Methodology PDFAyush MalhotraPas encore d'évaluation

- A 1.8Ghz Cmos: Low-Power Truly-Modular Programmable Divider in Standard TechnologyDocument4 pagesA 1.8Ghz Cmos: Low-Power Truly-Modular Programmable Divider in Standard TechnologyMuhammad_Swilam_2010Pas encore d'évaluation

- PhysicsDocument30 pagesPhysicsnewgetzPas encore d'évaluation

- A Design Methodology Using The Inversion Coefficient For Low-Voltage Low-Power CMOS Voltage ReferencesDocument11 pagesA Design Methodology Using The Inversion Coefficient For Low-Voltage Low-Power CMOS Voltage ReferencesVenkatesh DonepudiPas encore d'évaluation

- PHD Proposal LUDocument34 pagesPHD Proposal LUTho Mai DucPas encore d'évaluation

- Low Power Full AdderDocument6 pagesLow Power Full Adderdurairajmary100% (1)

- Jurnal Kutub EmpatDocument7 pagesJurnal Kutub EmpatMuhammad HaekalPas encore d'évaluation

- Treesa s2Document5 pagesTreesa s2jayalakshmisnairPas encore d'évaluation

- Transistor Sizing of Energy-Delay - Efficient CircuitsDocument7 pagesTransistor Sizing of Energy-Delay - Efficient CircuitsDaveMartonePas encore d'évaluation

- A High-Speed High-Resolution Latch Comparator For Pipeline Analog-to-Digital ConvertersDocument4 pagesA High-Speed High-Resolution Latch Comparator For Pipeline Analog-to-Digital ConvertersJessyPas encore d'évaluation

- Machine Learning Based Adaptive PredictionDocument9 pagesMachine Learning Based Adaptive PredictionnhatvpPas encore d'évaluation

- A Mosfet-Only Dac For A General Array Configured Device: E. Montane, G. Hornero, G. Chapinal, J. SamitierDocument5 pagesA Mosfet-Only Dac For A General Array Configured Device: E. Montane, G. Hornero, G. Chapinal, J. SamitierMiguel BrunoPas encore d'évaluation

- Miniaturized Six-Port Receiver For 60 GHZ Communication ENDocument5 pagesMiniaturized Six-Port Receiver For 60 GHZ Communication ENWalter Santiago Campos ArandaPas encore d'évaluation

- INTEGRATION, The VLSI Journal: Shu-Yi Wong, Chunhong ChenDocument14 pagesINTEGRATION, The VLSI Journal: Shu-Yi Wong, Chunhong ChenManpreet SinghPas encore d'évaluation

- Analysis and Design of A Low-Voltage Low-Power Double-Tail ComparatorDocument10 pagesAnalysis and Design of A Low-Voltage Low-Power Double-Tail ComparatorSrinivasAnchalaPas encore d'évaluation

- Power Constrained Design Optimization of Analog Circuits Based On Physical Gm/i CharacteristicsDocument7 pagesPower Constrained Design Optimization of Analog Circuits Based On Physical Gm/i CharacteristicsAn HoaPas encore d'évaluation

- Testing Paper CorrectedDocument9 pagesTesting Paper CorrectedSakthiPriyaPas encore d'évaluation

- Huang Tcas 2010Document11 pagesHuang Tcas 2010Joao SilvaPas encore d'évaluation

- JurnaaalllllDocument18 pagesJurnaaalllllANNURUL ATIYATUN TRIMULYA 1Pas encore d'évaluation

- Design and Analysis of Double Tail Comparator Using Adiabatic LogicDocument7 pagesDesign and Analysis of Double Tail Comparator Using Adiabatic LogicIJSTEPas encore d'évaluation

- Bandwidth Enhacement by Inductor + Current FeedbackDocument14 pagesBandwidth Enhacement by Inductor + Current FeedbackSumant AroraPas encore d'évaluation

- 0.9V 32Nm Dual-Gate Si Finfet: Low-Power Ptl-Based Multiplexer Design inDocument4 pages0.9V 32Nm Dual-Gate Si Finfet: Low-Power Ptl-Based Multiplexer Design inNamrata SaxenaPas encore d'évaluation

- Unified Model of PWM Switch Including Inductor in DCM (0074 1Document2 pagesUnified Model of PWM Switch Including Inductor in DCM (0074 1Jesús MendozaPas encore d'évaluation

- A Method For Constructing Reduced Order Transformer Models For System Studies From Detailed Lumped Parameter Models Ml12088a497Document7 pagesA Method For Constructing Reduced Order Transformer Models For System Studies From Detailed Lumped Parameter Models Ml12088a497cristian1961Pas encore d'évaluation

- D 119Document35 pagesD 119Mohammad Ayatullah MaktoomPas encore d'évaluation

- Journal Pre-Proof: Microprocessors and MicrosystemsDocument19 pagesJournal Pre-Proof: Microprocessors and MicrosystemsGOBINATH KPas encore d'évaluation

- Buchau PaperDocument6 pagesBuchau PaperjuenkkinPas encore d'évaluation

- 12.quantitative Power QualityDocument10 pages12.quantitative Power QualitySanthosh GuduruPas encore d'évaluation

- CMOS Low-Power Analog Circuit DesignDocument55 pagesCMOS Low-Power Analog Circuit DesignRajesh_Nagaraj_9325Pas encore d'évaluation

- Thnsistor Sizing For Minimization of Energy-Delay ProductDocument6 pagesThnsistor Sizing For Minimization of Energy-Delay Productdxtry123Pas encore d'évaluation

- Linearity Enhancement of Operational Transconductance Amplifier Using SourceDocument7 pagesLinearity Enhancement of Operational Transconductance Amplifier Using SourceIAEME PublicationPas encore d'évaluation

- Design of A CMOS Tapered Cascaded Multistage Distributed AmplifierDocument10 pagesDesign of A CMOS Tapered Cascaded Multistage Distributed Amplifierindresh.vermaPas encore d'évaluation

- Iosr Journal c0704011523Document9 pagesIosr Journal c0704011523scsvmvsivakumarPas encore d'évaluation

- Analysis of CMOS 45nm Transmission Gate Based Pulsed Latch AbstractDocument12 pagesAnalysis of CMOS 45nm Transmission Gate Based Pulsed Latch AbstractbaluPas encore d'évaluation

- Dheeraj ReportDocument15 pagesDheeraj ReportGirdhar Gopal GautamPas encore d'évaluation

- Don Bosco Institute of Technology: Department of Electronics and Communication EngineeringDocument23 pagesDon Bosco Institute of Technology: Department of Electronics and Communication EngineeringSeema Shekarappa ChittakkiPas encore d'évaluation

- A Low Power A - D Converter 05613669Document4 pagesA Low Power A - D Converter 05613669Romualdo Begale PrudêncioPas encore d'évaluation

- Modelling and Simulation of Sigma-Delta Adc in Vhdl-AmsDocument5 pagesModelling and Simulation of Sigma-Delta Adc in Vhdl-AmsVitu VituPas encore d'évaluation

- Analog Challenge of Nanometer CMOSDocument8 pagesAnalog Challenge of Nanometer CMOSurpublicPas encore d'évaluation

- Power Systems-On-Chip: Practical Aspects of DesignD'EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardPas encore d'évaluation

- High-Performance D/A-Converters: Application to Digital TransceiversD'EverandHigh-Performance D/A-Converters: Application to Digital TransceiversPas encore d'évaluation

- The Geometric Distribution: P (X I) Q PDocument5 pagesThe Geometric Distribution: P (X I) Q Psuchi87Pas encore d'évaluation

- Sections 3-7, 3-8Document25 pagesSections 3-7, 3-8suchi87Pas encore d'évaluation

- GeometricDocument2 pagesGeometricsuchi87Pas encore d'évaluation

- Geometric Random Variable: AgendaDocument4 pagesGeometric Random Variable: Agendasuchi87Pas encore d'évaluation

- Defense Against SSDF Attack in Cognitive Radio Networks: Attack-Aware Collaborative Spectrum Sensing ApproachDocument4 pagesDefense Against SSDF Attack in Cognitive Radio Networks: Attack-Aware Collaborative Spectrum Sensing Approachsuchi87Pas encore d'évaluation

- Trust Based Channel Preference in Cognitive Radio Networks Under Collaborative Selfish AttacksDocument7 pagesTrust Based Channel Preference in Cognitive Radio Networks Under Collaborative Selfish Attackssuchi87Pas encore d'évaluation

- Identification and Punishment Policies For Spectrum Sensing Data Falsification Attackers Using Delivery-Based AssessmentDocument21 pagesIdentification and Punishment Policies For Spectrum Sensing Data Falsification Attackers Using Delivery-Based Assessmentsuchi87Pas encore d'évaluation

- An Empirical Evaluation of Density-Based Clustering TechniquesDocument8 pagesAn Empirical Evaluation of Density-Based Clustering Techniquessuchi87Pas encore d'évaluation

- Elearnica IrDocument6 pagesElearnica Irsuchi87Pas encore d'évaluation

- An Optimal Data Fusion Rule in Cluster-Based Cooperative Spectrum SensingDocument10 pagesAn Optimal Data Fusion Rule in Cluster-Based Cooperative Spectrum Sensingsuchi87Pas encore d'évaluation

- 6 Most ImpDocument17 pages6 Most Impsuchi87Pas encore d'évaluation

- Reporting Schemes JOURNALDocument24 pagesReporting Schemes JOURNALsuchi87Pas encore d'évaluation

- FCM - The Fuzzy C-Means Clustering AlgorithmDocument13 pagesFCM - The Fuzzy C-Means Clustering Algorithmsuchi87Pas encore d'évaluation

- Digital VLSI Design (ECE314/ ECE514) : Lecture-5Document27 pagesDigital VLSI Design (ECE314/ ECE514) : Lecture-5Roshan SoniPas encore d'évaluation

- FQP9N90C/FQPF9N90C: 900V N-Channel MOSFETDocument10 pagesFQP9N90C/FQPF9N90C: 900V N-Channel MOSFETHeru susantoPas encore d'évaluation

- DEL ManualDocument94 pagesDEL ManualAnand BongirPas encore d'évaluation

- Dec50143 PW3Document10 pagesDec50143 PW3Alif FirdausPas encore d'évaluation

- IgbtDocument10 pagesIgbtNayeem HossainPas encore d'évaluation

- SMD Darlington Transistor (NPN)Document3 pagesSMD Darlington Transistor (NPN)Majk StonePas encore d'évaluation

- BJT Structure and Modes of OperationDocument4 pagesBJT Structure and Modes of OperationJogamaya DeyPas encore d'évaluation

- History of SemiconductorsDocument14 pagesHistory of SemiconductorsSergio Andres Fajardo SaldarriagaPas encore d'évaluation

- 74LS573Document5 pages74LS573Petricia RosalinPas encore d'évaluation

- Mod 5 LP VLSI - Ktunotes - in PDFDocument115 pagesMod 5 LP VLSI - Ktunotes - in PDFakhilabrahamPas encore d'évaluation

- Semiconductor Process FlowDocument48 pagesSemiconductor Process Flowgizer74Pas encore d'évaluation

- True USB GQ Universal Programmer Supported Device List (Re. 7.23)Document73 pagesTrue USB GQ Universal Programmer Supported Device List (Re. 7.23)ecutronicssPas encore d'évaluation

- D - Flip Flop: Task - 4Document20 pagesD - Flip Flop: Task - 4Mehak AgarwalPas encore d'évaluation

- Ass1 PDFDocument2 pagesAss1 PDFSachin GuptaPas encore d'évaluation

- CT354 Optocoupler DatasheetDocument10 pagesCT354 Optocoupler DatasheetFrame JoshPas encore d'évaluation

- SPICE MOSFET Model IntroDocument57 pagesSPICE MOSFET Model IntroFernando Sánchez HernándezPas encore d'évaluation

- NGD18N40CLBT4 Ignition IGBT 18 Amps, 400 VoltsDocument8 pagesNGD18N40CLBT4 Ignition IGBT 18 Amps, 400 VoltsEudis HernandezPas encore d'évaluation

- Introduction To Nanoscience and Nanotechnology (ECE1006)Document13 pagesIntroduction To Nanoscience and Nanotechnology (ECE1006)Dhruv KapadiaPas encore d'évaluation

- 24V 1A Flyback Fairchild - WWW - IranSwitching.ir - PDFDocument1 page24V 1A Flyback Fairchild - WWW - IranSwitching.ir - PDFdraPas encore d'évaluation

- DICA - Bits - Without Ans - docxQFWGDocument9 pagesDICA - Bits - Without Ans - docxQFWGkirankumarperamPas encore d'évaluation

- Sic Schottky Power Diode Modelling in SpiceDocument4 pagesSic Schottky Power Diode Modelling in SpiceKrishna KumarPas encore d'évaluation

- EC105Document23 pagesEC105api-3853441Pas encore d'évaluation

- Breakdown Mechanisma in GaN HEMTDocument9 pagesBreakdown Mechanisma in GaN HEMTATman VaghamshiPas encore d'évaluation

- Digitech XP100Document6 pagesDigitech XP100Anonymous vKD3FG6RkPas encore d'évaluation

- IRFZ48 55V-64A 140W-N-channelenhancemenT PDFDocument8 pagesIRFZ48 55V-64A 140W-N-channelenhancemenT PDFZxdIaminxXzlovewithzxXzyouzxPas encore d'évaluation

- Chapter 11 - MOSFETDocument7 pagesChapter 11 - MOSFETChandima Ishan DharmarathnePas encore d'évaluation

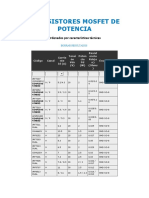

- Transistores Mosfet de PotenciaDocument15 pagesTransistores Mosfet de PotenciaLuis SanchezPas encore d'évaluation

- Taiwan Semiconductor Manufacturing CompanyDocument14 pagesTaiwan Semiconductor Manufacturing CompanyAsrarullah sheriff100% (2)

- Basic VLSI SlidesDocument91 pagesBasic VLSI SlidesDivya AhujaPas encore d'évaluation

- MCU ComparisonDocument288 pagesMCU ComparisonSHYAM THILLAINATHANPas encore d'évaluation