Académique Documents

Professionnel Documents

Culture Documents

Acquired Experiences With Computational Tool MS SV Used in Electronic Circuit Design

Transféré par

Khadar BashaTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Acquired Experiences With Computational Tool MS SV Used in Electronic Circuit Design

Transféré par

Khadar BashaDroits d'auteur :

Formats disponibles

Electrical and Electronic Engineering 2013, 3(4): 97-108

DOI: 10.5923/j.eee.20130304.01

Acquired Experiences with Computational Tool MS2SV

Used in Electronic Circuit Design

Tiago da Silva Almeida1,* , Alexandre Csar Rodrigues da Silva1 , Ian Andrew Grout2

1

Department of Electrical Engineering, Univ. Estadual Paulista - UNESP, Ilha Solteira, 15.385-000, Brazil

Department of Electrical and Computer Engineering, University of Limerik, Limerick, Republic of Ireland

Abstract The top-down methodology and CAD tools are important in development of electronic circuits. Mainly when

design is in high level of abstraction and many levels of representation can be used to modeling the electron ic circuits. Th is

way is necessary to use a tool to execute the synthesis of models, i.e., changing a representation in high level of abstraction in

another in lower level. This paper presents the experiences in use synthesis computational tools to support the synthesis of

digital-to-analog converter models by translating between different tools used in modeling systems and electronic circuits.

This tool is named MS2 SV and works direct ly with the following two co mmercial tools: MATLAB / Simu link and

SystemVision. The MS2 SV synthetizes block diagram developed in Simu link rep resenting a mixed-signal circuit into a lower

level of abstraction in VHDL-AMS. To co mpare the simu lation results was used SystemVision environ ment, because the

MS2 SV generates all design structure to SystemVision. The method validation was performed by analyzing the power

spectral of signal obtained by discrete Fourier transform of three d ifferent kinds of digital-to-analog converters.

Keywords Synthesis, Digital-to-analog Converter, Co mputational Tool, CAD, VHDL-AMS

1. Introduction

Nowadays, computational tools are indispensable in

electronic circuits design due to the increase in comp lexity

of design and the necessity to manage a large amounts data.

Advances in the development of new design methodologies

and computational tools have led to the emergence of ever

more co mp lex designs, i.e., the necessity for more co mplex

electronic circu its in a greater range of applications has

added to advances in computational tool development.

The development of new methodologies and new tools

has become a strategic area of concern in development of

new technologies, in particular the development of CAD

(Co mputer Aided Design) tools[1].

CAD tools can be best understood as design informat ion

management systems, along with graphic creation based

design entry and simu lation of designs created. These

simu lations can be used, shared, published, republished and

reused in different fo rmats, scales and levels of detail.

Further reference on the operation of CAD tools can be seen

in[2].

Co mmercial CA D too ls wo rk typ ically with several

different possible design description formats. In order to

incre-ase designer efficiency and to allo w a designer to

* Corresponding author:

tiagoalmeida@computer.org (Tiago da Silva Almeida)

Published online at http://journal.sapub.org/eee

Copyright 2013 Scientific & Academic Publishing. All Rights Reserved

utilize different design tools within a part icular design, it

has become necessary to automate the steps involved in the

synthesis of a design or to aid the translation between

different formats. According to[3] there are two design

methodologies. Firstly, the bottom-up methodology, where

the modeling of the project is init iated at a low level of

abstraction with many details about physical structure of the

final system being added to until reaching a high level

behavioral or functional model of a system. Secondly, the

top-down methodology, where the modeling is always

initiated at a high level of abstraction and it considers

initially only the behavior of the system with details then

added until the physical and a detailed imp lementation is

created.

The top-down approach has been focus of many reported

works and also this paper. In[3] and[4], the importance of

using hardware description languages (HDLs) is considered

in many aspects of design of electronic circuits and systems,

ranging fro m documentation through to simulat ion and

synthesis into physical implementation. Ho wever, in[4]

there is a particular focus on the VHDL-AMS (VHSIC

Hardware Description Language - Analog and Mixed

Signals).

In this context, this paper presents an imp rovement of a

computational tool named MS2 SV (MATLAB/ Simu link to

SystemVision) wh ich was developed to support the

development of projects presented in[5] and[6]. Th is tool

works d irectly with two co mmercial tools: MATLAB /

Simu link fro m Mathworks and SystemVision fro m Mentor

98

Tiago da Silva Almeida et al.: Acquired Experiences with Computational

Tool M S2SV Used in Electronic Circuit Design

Graphics. Model translation of an electronic circuit is

achieved by translating a mixed-signal block diagram

developed in MATLAB / Simulink into a lower level of

abstraction in VHDL-AMS and simulation project structure

in SystemVision.

The case studies of digital-to-analog converters (DAC)

design were considered expanding the paper[1]. Data

converters are circuits that transform a g iven representation

to another. The ADC (analog to dig ital converter) is used to

convert analog signals to digital data. The digital to

analogue converter works in the opposite manner to the

ADC, converting digital data input to analogue signal

output proportional to value of input digital[1].

Considering the DAC operation, n binary input bits

(which can be considered as representing the binary code of

a decimal value) are received and there are 2n possible

combinations of binary input. There is also an additional

input to the circuit design that is used as a reference signal,

represented by Vref and the reference is a voltage level,

which is used to determine the maximu m value that

converter can generate on its output. The analog value is

generated by the weighted sum of n inputs, mu ltip lied by

the reference voltage.

Inputs are weighted according to magnitude of each bit,

where n is the magnitude of input bit, x is total nu mber of

inputs, and b is DA C input value contained in the b it of n

magnitude, where b n {0,1}, as described in:

x

1

b

n n

n =1 2

VP =

(1)

Using Equation (1), the analogue output voltage fro m the

data converter is obtained by mu ltiply ing the result of

Equation (1) by the reference voltage to obtain:

Vout= VP Vref

(2)

There are several methods possible to implement the DAC

operation (i.e., there are several different DAC design

architectures possible). One co mmon method used is R/ 2R

ladder circu it, where only two values for resistors in circuit

are used (R and 2R), and output current depends on positions

of switches that are controlled by inputs[7].

2. Related Research

The research in synthesis of electronic systems is

mu lti-disciplinary area and presented a lot of papers with

different goals. One of the most important papers is the[8],

where it was presented a matching algorithm based on time

to ext ract the probability distribution of the stochastic

behavior of the circuit. The proposed method has been

extended to deal with h igh dimension problems with almost

linear co mp lexity. Experiments showed the proposed

method can provide up to 1666X runtime speedup with the

same accuracy when co mpared with Monte Carlo method.

[9] proposed an approach to automatic synthesis of

additional decoders. The method attempts to find and

remove cases where there are no equivalent decoders. To

discover all decoders that can exist simultaneously, an

algorith m based on functional dependency has also been

proposed. To select the correct decoder another algorith m is

used to infer fo rmula of each decoder precondition.

[10] has developed a framework for synthesis of

electronic systems at high level based on abstract finite state

mach ines. The framework called synASM is capable of

generating a CDFG (Control Data Flo w Graph) fro m

hardware descriptions based on C language The authors

extended the definitions of abstract state machines to

support the parallelis m and timing. After generating the

CDFG extended, it was possible the automatic generation of

optimizab le hard ware descriptions in VHDL and implement

ation in FPGA.

[11] presented a co mplete approach decoder for communi

cation systems. The modelling was based on finite state

mach ines and the method was capable of identifying

whether decode exists or not, by observing the input

sequence and output of encoder.[12] presented a method of

representation and synthesis of Boolean expressions

recursively. The method performs a sequence of operations

denial implications of using two memristors. With the

method proved possible to reduce the number of necessary

implications for the expression representation and inference

using mult iple inputs can reduce the computation of

memristor imp lementation.

[13] p roposed an algorithm for identifying flowcharts

structure. Twelve structures were identified and then the

algorith m was used to generate the code flowchart

identified using recursion. The technologies and algorithms

were used in an integrated development platform.[14]

presented a approach of output bit selection based on

counter for output response compaction in test systems

observable. The hard ware implementation requires only a

counter and a multip lexer. Thus, the complexity was

reduced and the control area was simplified. Furthermore,

since no change in the ATPG (Automat ic Test Pattern

Generation) tool was not required. Two output selection

algorith ms have been developed in several operations which

counters can be employed.

[15] discussed some work and the importance of

developing CAD tools for the synthesis and design of

systems and mult i-core architectures, highlighting the

importance of mu lti-core optimized and efficient resource

allocation. In[16] was rev ised performance measures of

some data type converters ADC (Analog-to-Digital

Converter), such as SNR (Signal to Noise Ratio), SINAD

(Signal to Noise Ratio more d istortion), SFDR (Spurious

free Dynamic Range), THD (Total Harmon ic Distortion)

and ENOB (Effective Nu mber of Bits). These metrics were

analyzed with the case study of an ideal 14-b it converter in

MATLAB and a converter with 12-b it commercial

manufactured by Analog Devices.

In[17] was developed a methodology to imp lement

processors FFT (Fast Fourier Transfo rm) on reprogramma

ble devices using VHDL language. The description used in

the implementation in VHDL is called FFT rad ix-2 and

Electrical and Electronic Engineering 2013, 3(4): 97-108

decimation in time.[18] p roposed a classification model

tools electronic systems design known as ESL (Electronic

System Level). The paper details the features and

approaches that differ co mputational tools for both

modeling the hardware level and at the level of software. At

work was still pointed the incompatibility problems

between tools and weaknesses they have.

[19] has developed an algorith m for automatic generation

of analog circu it models for modeling of circuit failures on

high level. The algorith m was written in MATLA B and

generates a description in VHDL-AMS for the simu lation

and analysis of model failures SystemVision environ ment.

In[20] was presented a methodology for genetic optimizatio

n based on VHDL-AMS for Fuzzy Logic controllers. The

fuzzy logic controller was used for modeling work in

automotive systems in mixed physical do main. A genetic

algorith m was developed and simulated in SystemVision

environment, is employed in the generation of rough fuzzy

sets.

Thus, this paper follows the same tendency in these

papers. Thus, it was built computational tools demonstrate

in section 3.

3. Methodology

Two key features were then added to the tool:

1. The designer is able to add new components fro m the

Simu link libraries. With this feature, the designer can use

99

different elements previously defined in the standard

Simu link libraries.

2. The addition of new Simu lin k libraries developed by

the designer with more co mp lex models, or to change the

lib rary named LIB_MS2SV also used in previously paper[1].

This added flexib ility is made possible by creating a

directory structure and configuration. Fro m the root director

y bin configuration files are split between configurations of

elements fro m libraries of MATLAB / Simu lin k (lib

directory) and elements of toolbox Simu link (blk directory)

subject to translation. The pseudo-code concerning the

VHDL-AMS models are also arranged between directories.

The translation of the model starts with reading a Simu link

generated file with an .mdl extension. Initially, a check is

made of elements and libraries used in model. If there are no

unknown libraries or elements, the translation process starts.

The tool stores a list of co mponents in model, the list of

connections between these components and other important

informat ion for generation of circuit netlist. Then, p roject

structure required for simu lat ion and analysis in SystemVisi

on is generated too[1]. Finally, all descriptions in VHDL AMS and files for debugging for pro ject needs are generated.

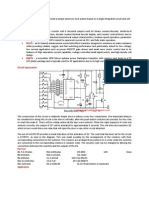

Figure 1 shows the functional diagram of the MS2 SV tool.

If subsystems are used, a VHDL-AMS model for each

subsystem used is generated. The MS2 SV enables the

relationship between elements in the same library by creating

hierarchical models.

Figure 1. Functional diagram of the MS2 SV tool illustrating the steps involved in translating the model to generate input file structure in SystemVision

environment[1]

100

Tiago da Silva Almeida et al.: Acquired Experiences with Computational

Tool M S2SV Used in Electronic Circuit Design

Figure 2. Class diagram of translations rules of MS2 SV

Figure 3. Sequence diagram of MS2 SV tool illustrating translation process elements being primitive toolbox of Simulink without interaction with user

libraries

Electrical and Electronic Engineering 2013, 3(4): 97-108

101

Figure 4. Sequence diagram of MS2 SV tool representing translation process of elements being user libraries or even using primitive elements

The Figure 2 represents the class diagram of tool M S2 SV

in a software perspective. Even all interface layers is

represents because some aspects do not change the MS2 SV

functionality. In Figure 2 only the classes Main, Save and

VHDL are into interface layer. The others class makes the

translation inference engine. The SystemFile class is

responsible to generate all pro ject structure to simulate in

SytemVis ion environment. The TranslateCode isresponsib

le to generate all VHDL-AMS files. This class inherits the

features of Checking class, and Checking class checks if

there is any primit ive of Simu lin k, user libraries or

subsystems. Checking inherits the features of Li b class and

Li b class is responsible to catch the models into libraries.

Last one, Li b inherits the features of ReadMDL, it

responsible to reads the models in MATLA B / Simu link.

Figure 3 shows the sequence diagram of MS2 SV tool to

case of primit ive elements translation in Simu lin k toolbo x.

The translation process is started with a verificat ion of

elements inside the model using Checking class operation.

The Checking class uses the operation of ReadMDL class

to read the Simu lin k file. The reading the Simu lin k file is

done more than once because the interface that controls the

inference engine allowing different file being loaded without

translation.

Figure 4 shows the sequence diagram of MS2 SV tool to

the case of translate of elements inside libraries created by

designer. The process is quite similar to the Figure 3, but it

includes the Lib class. Lib class copy the descriptions saved

into internal libraries in tool MS2 SV to represent libraries

described by designer.

4. Case Study

The DAC08, A D7524 and AD7528 DAC were chosen to

model and simulate to evaluate the proposed methodology.

All of them are monolithic data converter with 8 b it

resolution used in applications such gain control circuit and

stereo audio.

4.1. DAC08

DAC08 is simpler operating model consisting basically of

a converter with a resolution of 8 bit parallel input, which

performs the digital to analogue conversion.

The conversion of digital data into analog is done using

the ladder R/ 2R where the binary inputs control the

switching between the current arrival of resistors and current

coming directly fro m the reference voltage.

Based on the specifications found in the datasheet of

DAC08 converter[21], it was possible to model in MATLAB

/ Simu lin k. Other details of the imp lementation on a physical

level, such as compatibility with TTL (Transistor-Transistor

102

Tiago da Silva Almeida et al.: Acquired Experiences with Computational

Tool M S2SV Used in Electronic Circuit Design

Logic) and CM OS (Co mp lementary Metal Oxide

Semiconductor) technology were not considered, because

the focus of this paper is modelling at high level of

abstraction.

The creation of the subsystems involved the use of

Equation (2) in order to adjust the weights of each bit, as

shown in Figure 5[22].

Figure 5 shows the subsystem that represents the ladder

R/2R, wh ich was constructed with basic components

available in Simu lin k libraries. The mult iplication between

the digital input and weights of each input was made with the

Gain co mponents, the sum with seven Sum co mponents

of two values and mu ltiply ing the result by the reference

voltage using Product component. In this system there are

two outputs, the analog signal and the difference between the

output and the reference voltage.

An aspect that is important to emphasize in the creation of

the R/2R ladder model shown in Figure 5 is that there are

Data Type Conversion components. These components are

used to change the way representation of the binary signal

(logic 0 or 1) for decimal representation (0 V or 1 V) and

subsequent mu ltip lication by weight. In MATLAB /

Simu link this co mponent is not necessary, however, in

VHDL-AMS co mponent that becomes important due to

different ways of representing a signal in this language (i.e.

the signal types used in VHDL and VHDL-AMS).

4.2. AD7524

AD7524 has internally a flip-flops set of latch type

capable of storing last digital input and a logic interface

capable of controlling reading and storing digital input.

The mode selection is controlled by CSB and WRB inputs.

When CSB and WRB are at logic lo w (0) is enabled writing

mode, that is, the analog output representing the binary value

at input bus DB0 -DB7 . But when CSB o r WRB assumes a

logic high (1), A D7524 is in hold mode, analog output has

the value corresponding to last input in DB0 -DB7 before

WRB or CSB assume logic h igh. Table 1 shows the

relationship of control inputs and selection mode of

AD7524[23].

Table 1. Selection mode pins to control the AD7524

CSB

WRB

Selection

mode

Write

1

X

X

1

Hold

Comments

The output corresponds to activity

on the input bus (DB0 to DB7).

The output corresponds to the last

valid entry, stored in flip-flops.

Figure 6 represents the buffers used by the AD7524 to

store last valid digital input. This component is basically

formed by a set of latches and an input common to all latches

to enable the output.

Figure 7 illustrates the circuit capable to represent a

selection mode in Tab le 1. Th is circuit is minimu m using

only three logic gates (two NOTs and one AND) and Figure

8 shows a complete AD7524 with a circu it of selection mode,

a latch buffer to store last input and ladder R/ 2R.

Figure 5. Subsystem in Simulink that represents ladder R/2R using basic components of the Simulink toolbox, such as Product, Sum, Gain and Data

Type Conve rsion

Electrical and Electronic Engineering 2013, 3(4): 97-108

103

Figure 6. Subsystem that represents internal buffers converter AD7524, being formed by components Te rminator and Latch output (the Qb output from

each latch is not used in this work)

Figure 7. Subsystem that represents the logic controller of AD7524 and formed only by using AND and NO T gates

Figure 8. Complete system AD7524 with all subsystems in Figure 5, 6 and 7

104

Tiago da Silva Almeida et al.: Acquired Experiences with Computational

Tool M S2SV Used in Electronic Circuit Design

4.3. AD7528

AD7528 is equivalent to two AD7524 converters in a

single IC (integrated circu it). The data bus of the AD7528 is

also numbered fro m DB0 to DB7 . Each internal converter

(DA C A and DAC B) has an individual reference pin, both

can vary 25 V. The AD7528 has only three control p ins

called DA CA/DACB, CSB and WRB. The relationship

between control pins is illustrated in the Table 2. At a

mo ment when the AD7528 is in hold mode the last valid

input is stored in buffers individually in each internal

converter[24].

Table 2. Selection mode pin to control the AD7528 indicating write mode

of the DAC A with all pins active low logic level or in write mode DAC B

only with pin in DACA/DACB active-high level, any change in the CSB pin

or WRB both converters are in hold mode

DACA/DACB

WRB

CSB

DAC A

Write

Hold

Hold

Write

X

X

1

X

X

1

Hold

Hold

Hold

Hold

DAC B

According to the approach described in[24], we created

two identical blocks to represent the ladder R/2R, one for the

DAC A and one for the DA C B. Similar to R/ 2R ladder

subsystem of Figure 5, the subsystem of Figure 6 was used

twice in the complete system, i.e. one for each block of the

AD7528 internal converter (DA C A and DA C B).

Figure 9 rep resents the logic controller responsible for the

selection of which internal drive will be chosen and if

converter is in hold or write mode representing behaviour

described in Table 2. This subsystem is basically formed by

simp le logic gates available in toolbox of Simu link as basic

primitive[22].

Figure 9. Subsystem that represents logic controller of AD7528 and

formed only by using AND and NO T gates

Figure 10 shows the complete AD7528 converter model

created in MATLA B / Simu lin k. In each converter, there are

two separate outputs, first one is analog output signal

generated by the converter and second one is the difference

between analog output and reference voltage. Based on[25],

in order to generate a sine wave signal, MATLAB was able

to send the signal to each bit according to its magnitude of

the pins of the AD7528 with the Fro m Workspace

component. Subsequently, the outputs were captured and

sent back to MATLAB with the To Workspace component

to generate the graphic simu lation. The reference voltage and

the pin configuration for each internal converter were created

using Constant components (pins DACA/DACB, CSB and

WRB).

Figure 10. Complete model of AD7528 converter in Simulink with components From Workspace that receive digital signals from MATLAB and sends

output back to MATLAB after simulation through To Workspace component

Electrical and Electronic Engineering 2013, 3(4): 97-108

The DA CA/DACB pin could have been used to carry out

switching between two converters internally creating two

different waveforms fro m one input. However, as the

converters are exactly the same, the kind of simu lation does

not alter the analysis of signal generated.

After construction and simu lation in MATLA B / Simu link,

the MS2 SV translates model to the SystemVision

environment. The h ierarchy structure of model in Simulink

was maintained in VHDL-AMS codes and MS2 SV generated

the same configuration of co mponents. The below listing is

part of code generated by MS2 SV using ladder R/ 2R in

Figure 5.

105

EDULIB (Educational Library).

To perform the simulat ion, SystemVis ion was used the

same input used in MATLAB / Simu lin k. Thus was created

an input file with the extension .dat. It was created to an

additional VHDL-AMS code to read this file and send the

signal each bit input to the converters, as listed below.

use std.textio.all;

library IEEE;

use ieee.std_logic_1164.all;

use IEEE.std_logic_textio.all;

entity lerarqp is

port (relogio: in std_logic;

saida: out std_ulogic_vector (8 downto 1));

end entity lerarqp;

-- Digital Systems and Signals Processing Laboratory

-- genhdl\..\Ladder_R2R.vhd

-- Generated by MS2SV (Matlab / Simulink to

SystemVision) version 1.7

-- File created Tue Sep 08 16:00:12 2009

library IEEE;

use ieee.std_logic_1164.all;

use ieee.electrical_systems.all;

library EduLib;

use WORK.all;

entity Ladder_R2R is

port (

signal D1_D: in std_logic;

signal D2_D: in std_logic;

signal D3_D: in std_logic;

signal D4_D: in std_logic;

signal D5_D: in std_logic;

signal D6_D: in std_logic;

signal D7_D: in std_logic;

signal D8_D: in std_logic;

terminal A1: electrical

);

end entity Ladder_R2R;

architecture arch_Ladder_R2R of Ladder_R2R is

terminal \1$N0\: electrical;

terminal \1$N1\: electrical;

...

begin

DataType: entity EDULIB.D2A_BIT(IDEAL)

generic map ( VHIGH => 1.0,

VLOW => 0.0 )

port map (

D => D1_D,

A => \1$N0\

);

...

E_Gain: entity EDULIB.E_GAIN(BEHAVIORAL)

generic map ( K => 0.5 )

port map (

INPUT => \1$N0\,

OUTPUT => \1$N8\

);

...

E_Sum: entity EDULIB.E_SUM

port map (

IN1 => \1$N8\,

IN2 => \1$N9\,

OUTPUT => \1$N16\

);

...

end architecture arch_Ladder_R2R;

architecture behavior of writewaveform is

file f_out: text open WRITE_MODE is

"C:\Mentor_Projects\DAC08_Test\hdl\output.dat";

--quantity escreve_sinal across entrada to ref;

begin

writying: process

variable L: LINE;

begin

write(L,REAL'(entrada));

writeline(f_out,L);

wait until (relogio'event) and

(relogio='1');

end process writying;

end architecture behavior;

This VHDL-AMS code has a structural abstraction. It

represent the linkage between the co mponents which co mpos

all DAC system. The exactly behavior o f co mponents are in

internal libraries in SystemVision environ ment named

For each case study was used a different reference voltage

in simu lation, 10V, 8V, 6V and 4V, for DA C08, AD7524,

AD7528 A and AD7528 B, respectively. Figure 11 shows

the simulat ion results for 1 second.

architecture behavior of lerarqp is

begin

testing: process

file f_in: text open READ_MODE is "input.dat";

variable L: LINE;

variable L_BIT: std_ulogic_vector (8 downto 1);

begin

while not endfile(f_in) loop

readline (f_in,L);

hread (L,L_BIT);

wait until (relogio'event) and

(relogio='1');

saida <= L_BIT;

end loop;

end process testing;

end architecture behavior;

It was used to save the simu lation results in SystemVision

in another file with the extension .dat to that was possible

to analysis the signal generated also in MATLAB, as listed

below.

use std.textio.all;

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_textio.all;

--use IEEE.electrical_systems.all;

entity writewaveform is

port (

signal relogio: in std_logic;

entrada: in real);

end entity writewaveform;

106

Tiago da Silva Almeida et al.: Acquired Experiences with Computational

Tool M S2SV Used in Electronic Circuit Design

Figure 11. Result of simulation of all case studies in Simulink and signal from SystemVision in simulation total time of 1 second

The different voltages were used to a better view

waveform in Figure 11. However, in SystemVision

environment was used 10V fo r all converters and it was

plotted only one wave at Figure 11 because all converters

presented the same simulation results. In MATLAB /

Simu link the AD7524, AD7528 A and AD7528 B presented

noise in output because the delays in flip-flop of type latch.

Another difference noted in Figure 11 is lo w delay in

simu lation in SystemVision environ ment co mpared with

simu lation MATLA B / Simu link. Th is happened because the

way how the VHDL-AMS see the frequency inside the

SystemVision environment is different of frequency in

MATLAB / Simu lin k.

5. Analysis of Simulation

j =1

(3)

(4)

k =1

N = e( 2 i )/ N

(5)

The DC (Discrete Current) level of signal was extracted

through shifting the signal along the y axis at zero. This

resulted in a sine wave signal ranging fro m -5 to 5 for 10V,

-4 to 4 for 8V, -3 to 4 for 6V and -2 to 2 for 4V.

The process of conversion digital to analog represents an

interpolation between values of samples provided as inputs,

for 20001 points. In this case studies are used linear

interpolation, which points of adjacent samples are

connected by a straight line. The system output xr(t) is given

by:

=

xr (t )

To verify the quality of signal generated, it was made an

analysis of signal obtained through simulat ion. This analysis

was performed through power spectral analysis of the signal

obtained from discrete Fourier transform.

Figure 12 illustrates amplitude spectrum o f y(t) for all case

studies, in MATLAB / Simu lin k and VHDL-AMS. The

graph was generated using the discrete Fourier transform

described as[26]:

X (k ) = x( j ) N( j 1) ( k 1)

x( j ) = (1/ N ) X (k )B ( j 1) ( k 1)

x(nT )h(t nT )

(6)

n =

At the same time, the system has unity gain and linear

phase. Systems with this frequency response features

produce an output that is a shift in the time of input[26].

Importantly, this is a pseudo-conversion to analog, as the

conversion happens only while Vref is constant.

In Figure 12 is possible note difference in AD7524,

AD7528 A and AD7528 B because of noise in signal. The

signal fro m DA C08 and AD7524 presented a distortion in

sine wave showed in Figure 12 too. At the end, the most

perfect signal presented by amplitude spectral was the signal

Electrical and Electronic Engineering 2013, 3(4): 97-108

fro m SystemVision environ ment.

107

Scientific and Technological Develop ment (CNPq, process:

141744/2010-3 and 309023/ 2012-2).

REFERENCES

[1]

T.S. Almeida, A.C.R. Silva and I.A. Grout, "M ethodology

analysis of a computational tool used in electronic circuit

design," in: Instrumentation and Measurement Technology

Conference (I2MTC), 2011 IEEE , 2011, pp.1-6, 10-12.

[2]

E. Erdener and H. Gruenwald, CAD Standards and

institutions of higher education, Facilities, v. 19, n. 7, pp.

287-295, 2001.

[3]

T. Riesgo, Y. Torroja and E. Torre, Design methodologies

based on hardware description languages, IEEE Transaction

s on Industrial Electronics, v. 46, n. 1, pp. 3-12, 1999.

[4]

E. Christen and K. Bakalar, VHDL-AM S - a hardware

description language for analog and mixed - signal

applications IEEE Transactions on Circuits and Systems, v.

46, n. 10, pp. 1263-1272, 1999.

[5]

A. C. R. Silva, I. A. Grout, R. Jeffrey and T. O'Shea,

Generating VHDL-AM S M odels of Digital-to-Analogue

Converters From M atlab/Simulink, in: Thermal, Mechanical

and Multi-Physics Simulation Experiments in Microelectroni

c and Microsystems, 2007 - EUROSIM 2007, 2007, London,

2007, pp. 1-7.

[6]

A. C. R. Silva and I. A. Grout, A M ethodology and a Tool to

Design of M ixed - Signal Technology, in: Electronic,

Robotics and Automotive Mechanics Conference, Cuernavaca.

2007, pp. 164-169.

[7]

R. J. Tocci, N. S. Widmer and G. L. M oss, Sistemas digitais:

princpios e aplicaes, 10. Ed, So Paulo, Brazil: Pearson,

2008.

[8]

F. Gong; Basir-Kazeruni, S.; L. He; H. Yu, "Stochastic

Behavioral M odeling and Analysis for Analog/M ixed-Signal

Circuits," Computer-Aided Design of Integrated Circuits and

Systems, IEEE Transactions on , vol.32, no.1, pp.24-33, Jan.

2013.

[9]

ShengYu Shen; Ying Qin; KeFei Wang; Zhengbin Pang;

JianM in Zhang; Sikun Li, "Inferring Assertion for

Complementary Synthesis," Computer-Aided Design of

Integrated Circuits and Sys tems, IEEE Transactions on ,

vol.31, no.8, pp.1288-1292, Aug. 2012.

Figure 12. Graph of spectral power all output signals in Simulink and

SystemVision with peak in frequency at 2.9297 Hz

6. Conclusions

The use of CAD tools and a top-down methodology is a

reality that is present in the most electronic circu it design

projects, and the development of new co mputational tools to

aid in pro ject implementation is h ighly desirable, because the

range of CA D tools used introduces incompatibilities that

can be time consuming and costly in translating between

them. Hence, there is the need for suitable tools to be able to

translate models between different representations.

The improvement of tool M S2 SV presented in[1] proved

extremely convenient as it allows for the creation of mu ltip le

lib raries for d ifferent projects and also recycle the libraries

for use in others projects. This allows a significant savings of

time and hence costs.

By analy zing power spectral of a discrete-time signal, one

can say that the output signals in MATLAB / Simu link and

VHDL-AMS are almost identical. It fact was d ifferent in first

paper[1] when was used only one case study. This fact

allo ws us to change our vision about the abstraction levels

and details in modelling. Even in the same environ ment

(MATLA B / Simu link) we have difference in spectral signal.

If the system be simu lating in another environ ment, we will

also have different simulat ions.

This point let our hypothesis of importance explorer more

alternatives and standard methodologies of electronic circu it

design.

Nevertheless, our methodology and tool need further

investigation and analysis to consider the need for the

development of larger and more co mplex systems. To allow

expand our conclusion even more.

ACKNOWLEDGMENTS

The authors would like to thank National Council for

[10] Sinha, R.; Patel, H.D., "synASM : A High-Level Synthesis

Framework With Support for Parallel and Timed Constructs,"

Computer-Aided Design of Integrated Circuits and Systems,

IEEE Transactions on , vol.31, no.10, pp.1508-1521, Oct.

2012.

[11] Hsiou-Yuan Liu; Yen-Cheng Chou; Chen-Hsuan Lin; Jiang,

J.-H.R., "Automatic Decoder Synthesis: M ethods and Case

Studies," Computer-Aided Design of Integrated Circuits and

Systems, IEEE Transactions on , vol.31, no.9, pp.1319-1331,

Sept. 2001.

[12] Poikonen, J.H.; Lehtonen, E.; Laiho, M ., "On Synthesis of

Boolean Expressions for M emristive Devices Using

Sequential Implication Logic," Computer-Aided Design of

Integrated Circuits and Sys tems, IEEE Transactions on ,

108

Tiago da Silva Almeida et al.: Acquired Experiences with Computational

Tool M S2SV Used in Electronic Circuit Design

vol.31, no.7, pp.1129-1134, July 2012.

[13] X. Wu et al, Research and Application of Code Automatic

Generation Algorithm Based on Structured Flowchart,

Journal of Software Engineering And Applications, v. 4, n. 9,

pp.534-545, 2011.

[14] Wei-Cheng Lien; Kuen-Jong Lee; Tong-Yu Hsieh;

Chakrabarty, K; Yu-Hua Wu, "Counter-Based Output

Selection for Test Response Compaction," Computer-Aided

Design of Integrated Circuits and Systems, IEEE

Transactions on , vol.32, no.1, pp.152-164, Jan. 2013.

[19] Likun Xia; Bell, I.M .; Wilkinson, A.J., "Automated M odel

Generation Algorithm for High-Level Fault M odeling,"

Computer-Aided Design of Integrated Circuits and Systems,

IEEE Transactions on , vol.29, no.7, pp.1140-1145, July

2010.

[20] L. Wang and T. J. Kazmierski, VHDL-AM S based genetic

optimization of fuzzy logic controllers, The International

Journal for Computation and Mathematics in Electrical and

Electronic Engineering, v. 26, n. 2, pp. 447-460, 2007

[21] Analog Devices Inc. (2010) CMOS dual 8-bit buffered

multiplying DAC: AD7528[Online]. Available http://www.

datasheetcatalog.org/datasheet/analogdevices/78586868AD

7528_b.pdf.

[15] D. M arculescu and P. Li, Guest editorial special section on

PAR-CAD: parallel CAD algorithms and CAD for parallel

architecture / systems, Computer-Aided Design of Integrated

Circuits and Systems, IEEE Transactions on, v. 31, n. 1, p.

7-8, 2012.

[22] E. Y. M atsumoto, Simulink 7.2: Guia Prtico, So Paulo,

Brazil: rica, 2008.

[16] Pedroso M eloni, L.G.; Gusso Lenzi, K., "Performance

M easurement Simulations for Analog-to-Digital Converters,"

Latin America Transactions, IEEE (Revista IEEE America

Latina) , vol.10, no.1, pp.1168-1174, Jan. 2012.

[23] Analog Devices Inc. (2002) CMOS 8-Bit Buffered

Multiplying DAC: AD7524[Online]. Available http:// www.

datasheetcatalog.org/datasheet/analogdevices/888358036ad7

524.pdf.

[17] Correa, I. S.; Freitas, L.C.; Klautau, A.; Weyl Albuquerque

Costa, J.C., "VHDL Implementation of a Flexible and

Synthesizable FFT Processor," Latin America Transactions,

IEEE (Revista IEEE America Latina), vol.10, no.1,

pp.1180-1183, Jan. 2012.

[24] Analog Devices Inc. (2002) 8-Bit, High-Speed, Multiplying

D/A Converter (Universal Digital Logic Interface) DAC:

DAC08[Online]. Available http://www. datasheetcata log.

Org / datasheet/ analogdevices/80487346DAC08_b.pdf.

[18] Gerstlauer, A.; Haubelt, C.; Pimentel, A.D.; Stefanov, T.P.;

Gajski, D.D.; Teich, J., "Electronic System-Level Synthesis

M ethodologies," Computer-Aided Design of Integrated

Circuits and Systems, IEEE Transactions on , vol.28, no.10,

pp.1517-1530, Oct. 2009.

[25] E. Y. M atsumoto, Matlab 7: Fundamentos, So Paulo, Brazil:

rica, 2010.

[26] A. V. Oppenheim, A. S. Willsky, Sinais e sistemas, So Paulo,

Brazil: Person Education, 2010.

Vous aimerez peut-être aussi

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsD'EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsPas encore d'évaluation

- Using Artificial Neural Networks for Analog Integrated Circuit Design AutomationD'EverandUsing Artificial Neural Networks for Analog Integrated Circuit Design AutomationPas encore d'évaluation

- VlsiDocument32 pagesVlsibalasaravanan0408Pas encore d'évaluation

- SR PSpice SimulationDocument11 pagesSR PSpice SimulationMark Chow Khoon KeatPas encore d'évaluation

- Design of Roba Multiplier For High-Speed Yet Energy-Efficient Digital Signal Processing Using Verilog HDLDocument16 pagesDesign of Roba Multiplier For High-Speed Yet Energy-Efficient Digital Signal Processing Using Verilog HDLNishitha NishiPas encore d'évaluation

- Bit Error Optimization of Coded Ofdm System Over RDocument10 pagesBit Error Optimization of Coded Ofdm System Over RzelalemaschaleyPas encore d'évaluation

- Design of Roba Multiplier Using Mac UnitDocument15 pagesDesign of Roba Multiplier Using Mac UnitindiraPas encore d'évaluation

- A2 IntroDocument28 pagesA2 IntroPranesh 06Pas encore d'évaluation

- Formal Design and Verification of On Chip Networking: Al Sammane, J. Schmaltz and BorrioneDocument2 pagesFormal Design and Verification of On Chip Networking: Al Sammane, J. Schmaltz and BorrioneMichael ZimmermanPas encore d'évaluation

- Analytical Estimation of Signal Transition Activity From Word-Level StatisticsDocument16 pagesAnalytical Estimation of Signal Transition Activity From Word-Level StatisticsKumar N KrishnaMurthyPas encore d'évaluation

- Vlsi Handbook ChapDocument34 pagesVlsi Handbook ChapJnaneswar BhoomannaPas encore d'évaluation

- Educational UEDUCATIONAL USE OF PSCAD/EMTDC MODELS FOR EVALUATING DIGITAL PROTECTIVE RELAYSseDocument7 pagesEducational UEDUCATIONAL USE OF PSCAD/EMTDC MODELS FOR EVALUATING DIGITAL PROTECTIVE RELAYSseIASCPas encore d'évaluation

- Major Conference PaperDocument14 pagesMajor Conference Papermanishmeenahlm2Pas encore d'évaluation

- Computer Generation of Streaming Sorting NetworksDocument9 pagesComputer Generation of Streaming Sorting Networksdang2327Pas encore d'évaluation

- 1 s2.0 S143484112100385X MainDocument12 pages1 s2.0 S143484112100385X MainShylu SamPas encore d'évaluation

- Low Power ASIC Implementation From A CAL Dataflow DescriptionDocument15 pagesLow Power ASIC Implementation From A CAL Dataflow DescriptionMohan RajPas encore d'évaluation

- Two Dimensional DCTIDCT Architecture 2001Document29 pagesTwo Dimensional DCTIDCT Architecture 2001swathipushpaPas encore d'évaluation

- Zede 26Document84 pagesZede 26sumi_phdPas encore d'évaluation

- Simulink Behavioral Modeling of A 10-Bit Pipelined ADCDocument9 pagesSimulink Behavioral Modeling of A 10-Bit Pipelined ADCbhasin_hemantPas encore d'évaluation

- Design and Analysis of Approximate Compressors For MultiplicationDocument11 pagesDesign and Analysis of Approximate Compressors For MultiplicationAnju BalaPas encore d'évaluation

- Radix-4 and Radix-8 Multiplier Using Verilog HDLDocument6 pagesRadix-4 and Radix-8 Multiplier Using Verilog HDLIJARTETPas encore d'évaluation

- Quantifying The Wave-Effect of Irregular LDPC Codes Based On Majority-Based Hard-DecodingDocument5 pagesQuantifying The Wave-Effect of Irregular LDPC Codes Based On Majority-Based Hard-DecodingasdasddsaPas encore d'évaluation

- 50ICRASE130513Document4 pages50ICRASE130513Kanaga VaratharajanPas encore d'évaluation

- Implementation of Adaptive Viterbi DecoderDocument7 pagesImplementation of Adaptive Viterbi DecoderseventhsensegroupPas encore d'évaluation

- Microelectronics Journal: Shuo Yang, Jun Cheng, Pei WangDocument8 pagesMicroelectronics Journal: Shuo Yang, Jun Cheng, Pei WangShylu SamPas encore d'évaluation

- FPGA Based Implementation of 2D Discrete Cosine Transform AlgorithmDocument13 pagesFPGA Based Implementation of 2D Discrete Cosine Transform AlgorithmPragati PrajapatiPas encore d'évaluation

- WordlengthresuctionDocument18 pagesWordlengthresuctionswetha sillveriPas encore d'évaluation

- Implementation and Code Generation of Digital Circuits and System Using MATLAB & SIMULINKDocument16 pagesImplementation and Code Generation of Digital Circuits and System Using MATLAB & SIMULINKVLSISD36 Edwin DominicPas encore d'évaluation

- Implementation and Code Generation of Digital Circuits and System Using MATLAB & SIMULINKDocument16 pagesImplementation and Code Generation of Digital Circuits and System Using MATLAB & SIMULINKhamim ahmedPas encore d'évaluation

- A Synthesisable Quasi-Delay Insensitive Result Forwarding Unit For An Asynchronous ProcessorDocument8 pagesA Synthesisable Quasi-Delay Insensitive Result Forwarding Unit For An Asynchronous ProcessorHoogahPas encore d'évaluation

- Modeling Heterogeneous Systems Using Systemc-Ams Case Study: A Wireless Sensor Network NodeDocument6 pagesModeling Heterogeneous Systems Using Systemc-Ams Case Study: A Wireless Sensor Network Nodesimon9085Pas encore d'évaluation

- The Guider System For Classical Controller DesignDocument5 pagesThe Guider System For Classical Controller DesignEsmael FloresPas encore d'évaluation

- A Low Power Layered Decoding Architecture For LDPC Decoder Implementation For IEEE 802.11n LDPC CodesDocument6 pagesA Low Power Layered Decoding Architecture For LDPC Decoder Implementation For IEEE 802.11n LDPC CodesDinesh MahadasuPas encore d'évaluation

- 1 s2.0 S0026269219309346 MainDocument9 pages1 s2.0 S0026269219309346 MainShylu SamPas encore d'évaluation

- 1997 TCASII I. Galton Spectral Shaping of Circuit Errors in Digital To Analog ConvertersDocument10 pages1997 TCASII I. Galton Spectral Shaping of Circuit Errors in Digital To Analog Converterskijiji userPas encore d'évaluation

- Low-Density Parity-Check Code Constructions For Hardware ImplementationDocument5 pagesLow-Density Parity-Check Code Constructions For Hardware ImplementationBhavani PrasadPas encore d'évaluation

- High-Speed Area-Efficient VLSI Architecture of Three-Operand Binary AdderDocument6 pagesHigh-Speed Area-Efficient VLSI Architecture of Three-Operand Binary Adderk NiroshaPas encore d'évaluation

- TSP CMC 27974 Yamini SCIDocument16 pagesTSP CMC 27974 Yamini SCIRooban SPas encore d'évaluation

- Very High-Level Synthesis of Datapath and Control Structures For Reconfigurable Logic DevicesDocument5 pagesVery High-Level Synthesis of Datapath and Control Structures For Reconfigurable Logic Devices8148593856Pas encore d'évaluation

- ASIC Design of A High Speed Low Power Circuit For Factorial Calculation Using Ancient Vedic MathematicsDocument10 pagesASIC Design of A High Speed Low Power Circuit For Factorial Calculation Using Ancient Vedic MathematicsNeem PlantPas encore d'évaluation

- Artificial Evolution and ElectronicsDocument12 pagesArtificial Evolution and ElectronicsretonPas encore d'évaluation

- Implementation of Error Detection Mechanism Using NetSimDocument3 pagesImplementation of Error Detection Mechanism Using NetSimeditorijsaaPas encore d'évaluation

- Prezentare Paper NBiS 2014Document22 pagesPrezentare Paper NBiS 2014Catalin NegruPas encore d'évaluation

- CFD Report (Introduction To CFD)Document10 pagesCFD Report (Introduction To CFD)Israel Torres100% (1)

- Roba MulDocument56 pagesRoba MulNishitha NishiPas encore d'évaluation

- DSD Mini Project Report1Document15 pagesDSD Mini Project Report1dineshPas encore d'évaluation

- Content PDFDocument14 pagesContent PDFrobbyyuPas encore d'évaluation

- Analysis and Modelling of CMOS GM-C Filters Through Machine LearningDocument11 pagesAnalysis and Modelling of CMOS GM-C Filters Through Machine LearningDr. D. V. KamathPas encore d'évaluation

- Design of A High Speed Serializer, Timing Analysis and Optimization in TSMC 28nm Process TechnologyDocument6 pagesDesign of A High Speed Serializer, Timing Analysis and Optimization in TSMC 28nm Process TechnologyEditor IJRITCCPas encore d'évaluation

- A Reconfigurable Time Multiplexed Multichannel ADC Model For Efficient Data AcquisitionDocument4 pagesA Reconfigurable Time Multiplexed Multichannel ADC Model For Efficient Data Acquisitionaakashbari.ec20Pas encore d'évaluation

- Multithreaded Algorithms For The Fast Fourier TransformDocument10 pagesMultithreaded Algorithms For The Fast Fourier Transformiv727Pas encore d'évaluation

- An Improved Data Stream SummaryDocument18 pagesAn Improved Data Stream SummaryMH DevPas encore d'évaluation

- 36-Multilevel A-Diakoptics For The Dynamic Power-Flow Simulation of Hybrid Power Distribution SystemsDocument10 pages36-Multilevel A-Diakoptics For The Dynamic Power-Flow Simulation of Hybrid Power Distribution SystemsZyad GhaziPas encore d'évaluation

- Transistor Transistor Language Secret Signification Synchronization Sign Into Discrete Event Simulation Environment DynamismDocument12 pagesTransistor Transistor Language Secret Signification Synchronization Sign Into Discrete Event Simulation Environment DynamismssfofoPas encore d'évaluation

- 18bce0537 VL2020210104308 Pe003Document31 pages18bce0537 VL2020210104308 Pe003CHALASANI AKHIL CHOWDARY 19BCE2390Pas encore d'évaluation

- Optimal Circuits For Parallel Multipliers: Paul F. Stelling,,, Charles U. Martel, Vojin G. Oklobdzija,,, and R. RaviDocument13 pagesOptimal Circuits For Parallel Multipliers: Paul F. Stelling,,, Charles U. Martel, Vojin G. Oklobdzija,,, and R. RaviMathew GeorgePas encore d'évaluation

- A Low-Power Reconfigurable Data-Flow Driven DSP System: Motivation and BackgroundDocument10 pagesA Low-Power Reconfigurable Data-Flow Driven DSP System: Motivation and BackgroundChethan JayasimhaPas encore d'évaluation

- The Design of A Low Power Asynchronous Multiplier: Yijun Liu, Steve FurberDocument6 pagesThe Design of A Low Power Asynchronous Multiplier: Yijun Liu, Steve FurberMishi AggPas encore d'évaluation

- Carry Select AdderDocument72 pagesCarry Select Adderharshithakr100% (1)

- 12345Document3 pages12345Khadar BashaPas encore d'évaluation

- TimerDocument8 pagesTimerKhadar BashaPas encore d'évaluation

- Desktop-A19L7Cl 201a0693306fDocument1 pageDesktop-A19L7Cl 201a0693306fKhadar BashaPas encore d'évaluation

- 1234Document3 pages1234Khadar BashaPas encore d'évaluation

- 123Document2 pages123Khadar BashaPas encore d'évaluation

- TimerDocument8 pagesTimerKhadar BashaPas encore d'évaluation

- SysDocument4 pagesSysKhadar BashaPas encore d'évaluation

- Common-Mode Rejection RatioDocument1 pageCommon-Mode Rejection RatioKhadar BashaPas encore d'évaluation

- Common-Mode Rejection RatioDocument2 pagesCommon-Mode Rejection RatioKhadar BashaPas encore d'évaluation

- Common-Mode Rejection RatioDocument1 pageCommon-Mode Rejection RatioKhadar BashaPas encore d'évaluation

- Common-Mode Rejection RatioDocument1 pageCommon-Mode Rejection RatioKhadar BashaPas encore d'évaluation

- Common-Mode Rejection RatioDocument1 pageCommon-Mode Rejection RatioKhadar BashaPas encore d'évaluation

- Common-Mode Rejection RatioDocument2 pagesCommon-Mode Rejection RatioKhadar BashaPas encore d'évaluation

- Common-Mode Rejection RatioDocument1 pageCommon-Mode Rejection RatioKhadar BashaPas encore d'évaluation

- Common-Mode Rejection RatioDocument1 pageCommon-Mode Rejection RatioKhadar BashaPas encore d'évaluation

- AsusDocument1 pageAsusKhadar BashaPas encore d'évaluation

- Lica LabDocument7 pagesLica LabKhadar BashaPas encore d'évaluation

- December 2016 Current AffairsDocument103 pagesDecember 2016 Current AffairsKhadar BashaPas encore d'évaluation

- Common-Mode Rejection RatioDocument1 pageCommon-Mode Rejection RatioKhadar BashaPas encore d'évaluation

- Lica LabDocument7 pagesLica LabKhadar BashaPas encore d'évaluation

- Lica LabDocument7 pagesLica LabKhadar BashaPas encore d'évaluation

- Current Affairs Quiz August 2016Document74 pagesCurrent Affairs Quiz August 2016Khadar BashaPas encore d'évaluation

- 10 Spelling & Capitalization DVDDocument4 pages10 Spelling & Capitalization DVDPJ HongPas encore d'évaluation

- AsusDocument1 pageAsusKhadar BashaPas encore d'évaluation

- ConstitutionDocument9 pagesConstitutionKhadar BashaPas encore d'évaluation

- EDocument179 pagesEKhadar BashaPas encore d'évaluation

- EulaDocument60 pagesEulaGleider TorresPas encore d'évaluation

- Geography of IndiaDocument16 pagesGeography of Indiaatul mishraPas encore d'évaluation

- Improve Your VocublarlyDocument50 pagesImprove Your VocublarlyKhadar BashaPas encore d'évaluation

- Serial Age of Enpires 3Document1 pageSerial Age of Enpires 3Khadar BashaPas encore d'évaluation

- GEM4D Geotech Block Models Process DescriptionDocument5 pagesGEM4D Geotech Block Models Process DescriptionMarcos GuimarãesPas encore d'évaluation

- Manual For Laying 110-500 KV XLPE Power CablesDocument84 pagesManual For Laying 110-500 KV XLPE Power CablesZoran PetrovićPas encore d'évaluation

- Wea Met Aws310 Brochure 210x280 B211290en C Low v2Document4 pagesWea Met Aws310 Brochure 210x280 B211290en C Low v2Anonymous rpSGuQPPas encore d'évaluation

- Given Values: Pressure Temperature Compressor Inlet 1.0325 Bar 300K Turbine Outlet 1.0325 Bar 815K Pressure Ratio 18.6Document3 pagesGiven Values: Pressure Temperature Compressor Inlet 1.0325 Bar 300K Turbine Outlet 1.0325 Bar 815K Pressure Ratio 18.6Walter BircherPas encore d'évaluation

- Question Report - 11Document17 pagesQuestion Report - 11Suryakant AgrawalPas encore d'évaluation

- Weld Map & NDE Extent of Pressure VesselDocument32 pagesWeld Map & NDE Extent of Pressure VesselMahesh Kumar100% (2)

- Digital Image ProcessingDocument156 pagesDigital Image ProcessingAnushka BajpaiPas encore d'évaluation

- Spe Math p2 Revision Yr7Document24 pagesSpe Math p2 Revision Yr7Hadizah JulaihiPas encore d'évaluation

- LUXEN SERIES 5 182 144cells 530-550w MONOFACIALDocument2 pagesLUXEN SERIES 5 182 144cells 530-550w MONOFACIALOscar DuduPas encore d'évaluation

- Al-Farabi The Theory of Emanation and THDocument14 pagesAl-Farabi The Theory of Emanation and THManuel Ricardo Fernandes SoaresPas encore d'évaluation

- HD 70 CDocument101 pagesHD 70 CPhamVanGiangPas encore d'évaluation

- Daatabase AssignmentDocument4 pagesDaatabase AssignmentIshani Puvimannasinghe100% (1)

- Calculations QuestionssDocument42 pagesCalculations QuestionssAlluringcharmsPas encore d'évaluation

- Phase Diagrams: By: Cherides P. MarianoDocument25 pagesPhase Diagrams: By: Cherides P. MarianoWild RiftPas encore d'évaluation

- Electronic Door LockDocument2 pagesElectronic Door LocktaindiPas encore d'évaluation

- Configure Ap Aruba ConsoleDocument2 pagesConfigure Ap Aruba ConsoleKule MemphisPas encore d'évaluation

- Full Download Test Bank For Information Technology Project Management 9th Edition Kathy Schwalbe PDF Full ChapterDocument36 pagesFull Download Test Bank For Information Technology Project Management 9th Edition Kathy Schwalbe PDF Full Chapterpannageimban.81c15100% (16)

- Pick and Place Robotic Arm Controlled by Computer - TJ211.42.M52 2007 - Mohamed Naufal B. OmarDocument26 pagesPick and Place Robotic Arm Controlled by Computer - TJ211.42.M52 2007 - Mohamed Naufal B. OmarSAMPas encore d'évaluation

- Btech Ce 3 Sem Fluid Mechanics Kce303 2022Document2 pagesBtech Ce 3 Sem Fluid Mechanics Kce303 2022shivchauhan0507Pas encore d'évaluation

- Labour Productivity ChartDocument635 pagesLabour Productivity ChartFrederick AgliamPas encore d'évaluation

- Сравнит. лингвистикаDocument22 pagesСравнит. лингвистикаАнастасия ДобровольскаяPas encore d'évaluation

- Irjet V4i10201 PDFDocument8 pagesIrjet V4i10201 PDFBesmir IsmailiPas encore d'évaluation

- What Is Trim?: Changed by Moving Masses Already On Board Forward or AFTDocument2 pagesWhat Is Trim?: Changed by Moving Masses Already On Board Forward or AFTamirsyawal87Pas encore d'évaluation

- Experiment 3: Department of Civil Engineering, IIT DelhiDocument2 pagesExperiment 3: Department of Civil Engineering, IIT DelhiSRPas encore d'évaluation

- Assignment - 02 - ASP - NET Core Web API With EntityFramework and Web AppDocument7 pagesAssignment - 02 - ASP - NET Core Web API With EntityFramework and Web AppdrubypjnkPas encore d'évaluation

- Edited C Spectra - APT and DEPTDocument4 pagesEdited C Spectra - APT and DEPTKasun RatnayakePas encore d'évaluation

- Casing and Tubing Crossovers: ScopeDocument4 pagesCasing and Tubing Crossovers: Scopeislam atifPas encore d'évaluation

- Denture Base MaterialsDocument117 pagesDenture Base MaterialsLalit KumarPas encore d'évaluation

- Soal B.inggris Paket 3Document9 pagesSoal B.inggris Paket 3sitiPas encore d'évaluation

- Properties in Shear: (Eg. Ssy 0.5sy)Document34 pagesProperties in Shear: (Eg. Ssy 0.5sy)Yusuf SahinPas encore d'évaluation