Académique Documents

Professionnel Documents

Culture Documents

1st Handout 8051

Transféré par

SaawanBaggDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

1st Handout 8051

Transféré par

SaawanBaggDroits d'auteur :

Formats disponibles

Reference:

The 8051 Microcontroller: Architecture, Programming & Applications

by

Kenneth J. Ayala

What is Microcontroller (C)

Microprocessor is CPU on chip.

Microcontroller is computer on chip.

Microcontroller functions as a complete system without the need of any external

components.

Due to advanced VLSI technology, it is currently possible to put CPU, memory, I/O ports,

oscillator, timers and counters on a single chip.

It is extensively used in millions of applications used in our daily life (where heavy

computation and memory consumption is not required) e.g. toys, cameras, video recorders,

CD players, washing machines etc.

Key features (must have)

i. CPU (8-bit)

ii. On chip oscillator (for clock and synchronization)

iii. On chip RAM

iv. On chip ROM

v. On chip I/O ports

vi. Serial port

vii. Timer-counter

viii. On chip BUS control

Architecture and organization of Microcontroller

External

Interrupts

Interrupt

control

ROM for

program

code

On-Chip

RAM

Timer/

counters

BUS

Control

I/O

Ports

Serial

Port

CPU

Oscillator

Block diagram of a Microcontroller

IC 8051 family (Atmel)

89XX

ROM

(byte)

RAM

(byte)

Timer/c

ounter

INT

Source

I/O

pins

pins

8951

4K

128

32

40

8952

8K

256

32

40

8953

12K

256

32

40

8955

20K

256

32

40

898252

8K

256

32

40

898051

1K

64

16

20

892051

2K

128

16

20

8051 Program memory (ROM)

ROM is a factory programmed memory for basic IC functioning.

Normal ROMs can not be reprogrammed.

Alternatives are EPROM (Electrically Programmable ROM).

EPROMs can be programmed offline (IC is not connected for any applications) by suitable

EPROM programmer.

Erasing can be done via UV light.

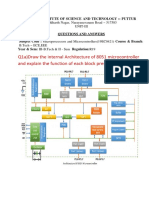

The 8051 architecture

8051 block diagram

The 8051 architecture

1.

2.

3.

4.

5.

6.

8 bit ALU with registers; Accumulator (A) and B

16 bit Program Counter (PC) and Data Pointer (DPTR) (DPL, DPH)

8 bit Program Status Word (PSW)

8 bit stack pointer (SP)

Internal ROM of 4K byte

Internal RAM of 128 byte

Four registers banks, each containing eight registers

[= 32 byte]

Sixteen bytes which can be addressed at bit level

[= 16 byte]

Eighty bytes of general purpose data memory

[= 80 byte]

7. 32 I/O pins arranged as four 8-bit ports: P0-P3

8. Two 16-bit time/counters (TL0, TL1, TH0, TH1)

9. Full duplex serial data receiver transmitter: SBUF

10. Control registers: TCON, TMOD, SCON, PCON, IP & IE

11. Two external and three internal interrupt sources

12. Oscillator and clock circuits

IP:

IE:

SBUF:

TCON:

TMOD:

SCON:

PCON:

Interrupt priority

Interrupt enable

Serial data buffer register

Timer/Counter control register

Timer mode control register

Serial port control register

Power control register

The 8051 architecture

8051 registers and memory

The 8051 pin diagram

The 8051 architecture

Pin diagram of 8051

Port 0: Port 0 is a dual purpose port. In general it is used as a general purpose I/O port, but

with an external memory, it becomes a multiplexed address and data bus.

Port 1: Port 1 is an 8-bit bidirectional I/O port. No alternate functions are assigned for Port

1 pins , thus they are used solely for interfacing to external devices.

Port 2: Port 2 is an 8-bit dual purpose port serving as general I/O port , or as the high byte

of the address bus for designs with external memories.

Port 3: Port 3 is an 8-bit bidirectional I/O port. It also serves the functions of various

special features of the 80C51 Family as follows:

P3.0

RXD

(Serial input port)

P3.1

TXD

(Serial output port)

P3.2

INT0

(External interrupt 0)

P3.3

INT1

(External interrupt 1)

P3.4

T0

(Timer/Counter 0 external input)

P3.5

T1

(Timer/Counter 1 external input)

P3.6

WR

(External data memory write strobe)

P3.7

RD

(External data memory read strobe)

The 8051 architecture

Pin diagram of 8051

ALE/PROG: Port 0 is used for both address and data. Address Latch Enable pin is used for

de-multiplexing the address and data. This pin is also the program pulse input (PROG)

during EPROM programming.

PSEN: Program Store Enable is the read strobe to external Program Memory. PSEN is not

activated when the device is executing out of internal Program Memory.

EA/VPP: When External Access Enable is held high the CPU executes out of internal

Program Memory. Holding EA low forces the CPU to execute out of external memory

regardless of the Program Counter value. In the EPROM devices, this pin also receives the

programming supply voltage (VPP) during EPROM programming.

XTAL1: Input to the inverting oscillator amplifier.

XTAL2: Output from the inverting oscillator amplifier.

VCC: Supply voltage

VSS: Circuit ground potential

The 8051 architecture

8051 Memory organization

4K byte On-Chip ROM (to store all hardware programs).

If internal ROM is running out of memory then there is a facility to use external ROM.

There is a pin EA (External Access). If EA = 1 then internal ROM and if EA = 0 then external

ROM will be used.

0FFF

FFFF

Internal

External

ROM

ROM

EA = 1

0000

4K

On-Chip RAM: arranged in two parts;

128 byte internal data RAM

128 byte Special Function Register

FF

Special

Function

Register

7F

Internal

data

RAM

00

EA = 0

64K 1000

External

data

RAM

FFFF

80

00FF

The 8051 architecture

8051 Memory organization

8051 implements separate memory space for programs (code) and data.

The on-chip RAM contains a rich arrangement of general purpose storage, bit addressable

storage, register banks, and special function registers.

The internal memory space is divided between register banks (00H-1FH), bit-addressable

RAM (20H-2FH), general purpose RAM (30H-7FH) and special function registers (80HFFH).

FF

Special Function Registers

80 Direct addressing Only

7F

Direct and Indirect

Addressing

30

2F

Bit Addressable

20

1F

General Purpose Register

4 Register Banks

00

The 8051 architecture

Four register bank

Each bank has R0-R7

Selectable by PSW.3 & 4

Bit addressable memory 20H 2FH (16

locations X 8-bits = 128 bits )

1AH 23H.2

The 8051 architecture

8051 oscillator and clock

A quartz crystal and capacitors are employed to generate

clock pulses and the crystal frequency is the basic

internal clock frequency of the microcontroller.

Typical clock frequency are between 1MHz to 16MHz and

can be observed at XTAL2 pin.

The smallest interval of time to accomplish any simple

instruction, or part of complex instruction, is the

machine cycle which itself is made up of six states.

A state is the basic time interval for

discrete operations of the microcontroller.

Program instructions may require one, two

or four machine cycles to be executed,

depending on the type of instruction.

Time taken by an instruction to be executed can be

calculated by finding the number of cycles C and is given

by the following relation:

Machine cycle =

12

crystal frequency

Tinst =

C1

XTAL1

30pF

C2

Quartz crystal

oscillator

XTAL2

30pF

GND

no.of machine cycles 12

crystal frequency

The 8051 architecture

Accumulator (A) and B register

The accumulator (A) is the most versatile register and is used for many operations

including addition, subtraction, integer multiplication and division, and Boolean

bit manipulations.

The register A is also used for all data transfers between the 8051 and any external

memory.

The B register is used with the A register for multiplication and division operations

and has no other function than as a location where data may be saved.

The 8051 architecture

Program Counter

Program Counter (PC) indicates where the microcontroller is in its instruction

sequence.

Program instructions bytes are fetched from locations in the memory that are

addressed by the PC.

PC holds either the address of the instruction being executed or the address of the

next instruction to be executed.

The PC is automatically incremented after every instruction byte is fetched and may

also be altered by certain instructions.

The PC is the only register that does not have an internal address.

Data Pointer

The Data Pointer (DPTR), used to access external code or data memory, is a 16-bit

register at address 82h (DPL) and 83h (DPH).

The following three instructions write 55h into external RAM location 1000h:

MOV

MOV

MOVX

A, #55h

DPTR, #1000h

@DPTR, A

The 8051 architecture

Program Status Word (PSW) and Flags

The program status word (PSW) at address D0H contains status bits (flags) as shown below.

PSW has four math flags that respond automatically to the outcomes of math operations

and three general purpose user flags that can be set to 0 or 1 by the programmer.

Carry Flag: CF is dual purpose bit. It is set 1 if there is a carry out of bit 7 during an add or

if there is a borrow into bit 7 during a subtract. CF is also the Boolean Accumulator

serving as a 1-bit register for Boolean operation.

Auxiliary Carry: When adding binary-coded-decimal (BCD) values, the AC flag is set if a

carry was generated out of bit 3 into bit 4.

The 8051 architecture

Flag 0: F0 is a general purpose flag bit available for user applications.

Register bank select bits: RS0 and RS1 are register bank select bits. They are cleared after a

system reset and are changed by programmer.

Overflow flag: OV is set after an addition or subtraction operation if there was an arithmetic

overflow. When signed numbers are added or subtracted, software can examine this bit to

determine if the result is in proper range or not.

Parity bit: P is automatically set or cleared each machine cycle to establish even parity with

the accumulator. The number of 1-bits in the accumulator plus the P bit is always even. (if

no. of 1 bits is odd in A then P = 1, if no. of 1 bits in A is even then P = 0.)

The 8051 architecture

Stack Pointer

The SP is an 8-bit register at address 81H. It contains the address of the data item currently

on top of the stack. Stack operations include pushing data on the stack and popping data

off the stack.

When data is to be placed on the stack, the SP increments before storing data on the stack so

that the stack grows up as data is stored. As data is retrieved from the stack, the byte is read

from the stack and then the SP decrements to point to the next available byte of stored data.

The 8051 architecture

Interrupts

An interrupt is the occurrence of a condition an event that causes a temporary

suspension of a program while the condition is serviced by another program called

subroutine.

Interrupts may be generated by internal chip operations or provided by external sources. Any

interrupt can cause the 8051 to perform a hardware call to an interrupt handling subroutine

that is located at a predetermined address in program memory.

There are five interrupt sources on the 8051; two external interrupts (INT0 and INT1) at port

pins P3.2 and P3.3, two timer interrupts (Timer flag 0 and Timer flag 1) and one serial port

interrupt (RI or TI).

Programmer is able to alter control bits of Interrupt Enable register (IE), Interrupt Priority

register (IP) and the Timer Control register (TCON).

After the interrupt is handled by the interrupt subroutine, the interrupted program must

resume operation at the instruction where the interrupt took place.

Program resumption is done by storing the interrupted PC address on the stack in RAM

before changing the PC to the interrupt address in ROM. The PC address will be restored

from the stack after an RETI instruction is executed at the end of interrupt subroutine.

The 8051 architecture

Special Function Registers

The 8051 operations that do not use the internal 128-byte RAM address from 00H to 7FH are

done by a group of specific internal registers, each called a Special Function Registers (SFR),

which may be addressed much like internal RAM, using addresses 80H to FFH.

Note that most of the 128 addresses from 80H to FFH are not defined, only 21 SFR addresses

are defined.

Some SFRs are also bit addressable together with byte addressable. So programmer should

be careful when accessing bits versus bytes.

Note that any address used in a program must start with a number; thus address E0H for the

A SFR will begin with 0 and would be 0E0H. Failure to use this number convention will result

in an assembler error when program is assembled.

The 8051 architecture

Special Function Registers

The 8051 architecture

Interrupt Enable register (IE)

Interrupt Priority register (IP)

The 8051 architecture

Counters and Timers

The 8051 contains two 16-bit timer/counters for timing intervals or counting events. Timer 0

is at addresses 8AH (TL0, low-byte) and 8CH (TH0, high-byte), and Timer 1 is at addresses

8BH (TL1, low-byte) and 8DH (TH1, high-byte). Timer operation is set by the time/counter

control register (TCON) at address 88H and the time mode control register (TMOD) at

address 89H. Only TCON is bit addressable (TCON.0 to TCON.7).

Time/Counter control register (TCON)

Time mode control register (TMOD)

The 8051 architecture

Time/Counter control register (TCON)

The 8051 architecture

Serial data input/output

The 8051 contains an on-chip serial port for communicating with serial devices with a serial

interface (A/D converters, shift registers, nonvolatile RAMs, etc.).

One register, the serial data buffer (SBUF) at address 99H, holds both the transmit data and

receive data. Writing to SBUF loads data for transmission; reading SBUF accesses received

data.

Various modes of operation are programmable through the bit-addressable serial port

control register (SCON) at address 98H.

The power control register (PCON) at address 87H controls data rates and contains

miscellaneous control bits.

Pins RXD (P3.0) and TXD (P3.1) connect to the serial data network.

Vous aimerez peut-être aussi

- Design By: Harman S. Gahir Ap, Mca CGC-GharuanDocument38 pagesDesign By: Harman S. Gahir Ap, Mca CGC-GharuanHarman GahirPas encore d'évaluation

- Architecture of the 8051 MicrocontrollerDocument22 pagesArchitecture of the 8051 MicrocontrollerchakrimvnPas encore d'évaluation

- MPMC Eee Unit - III 8051 MicrocontrollerDocument35 pagesMPMC Eee Unit - III 8051 MicrocontrollerAnonymous 4u5XkWGOPas encore d'évaluation

- 8051 Uc CompleteDocument129 pages8051 Uc CompletemalhiavtarsinghPas encore d'évaluation

- Micro Controller 89c51Document17 pagesMicro Controller 89c51g_prashanth0704075Pas encore d'évaluation

- Microprocessor Lab Manual EE0310Document44 pagesMicroprocessor Lab Manual EE0310sathishkumar.vPas encore d'évaluation

- Unit-Iv The 8051 Architecture Contents at A GlanceDocument28 pagesUnit-Iv The 8051 Architecture Contents at A GlanceKushwanth KaramsettiPas encore d'évaluation

- MICROCONTROLLERS SYSTEM DESIGNDocument28 pagesMICROCONTROLLERS SYSTEM DESIGNKiran KrishnanPas encore d'évaluation

- 8051 Architecture: 8051 Architecture Consists of These FeaturesDocument30 pages8051 Architecture: 8051 Architecture Consists of These Featuresdlwdeadman_monster819100% (1)

- Microcontroller Based Down Counter SystemDocument24 pagesMicrocontroller Based Down Counter SystemChandan Bera100% (1)

- Unit V 8051 Microcontrollers: Comparison Between Microprocessors and MicrocontrollersDocument15 pagesUnit V 8051 Microcontrollers: Comparison Between Microprocessors and MicrocontrollersAmy OliverPas encore d'évaluation

- Unit III The 8051 MicrocontrollerDocument25 pagesUnit III The 8051 MicrocontrollerArun kumar jaiswalPas encore d'évaluation

- Microcontrollers: Created By: Sachin Bhalavat (Elect. & Comm. Engg.)Document52 pagesMicrocontrollers: Created By: Sachin Bhalavat (Elect. & Comm. Engg.)madhu518Pas encore d'évaluation

- 8051architecturesb 121025020524 Phpapp01Document50 pages8051architecturesb 121025020524 Phpapp01madhu518Pas encore d'évaluation

- 8051 Microcontroller Architecture OverviewDocument28 pages8051 Microcontroller Architecture OverviewPranav SinhaPas encore d'évaluation

- BGK MPMC Unit-3 Q and ADocument21 pagesBGK MPMC Unit-3 Q and AMallesh ArjaPas encore d'évaluation

- Intel 8051mc Architecture & Intel 8085 Microprocessor Family.Document13 pagesIntel 8051mc Architecture & Intel 8085 Microprocessor Family.Abhi SharmaPas encore d'évaluation

- 8051 PPTDocument51 pages8051 PPTKudumu Vara PrasadPas encore d'évaluation

- Introduction to 8051 Microcontroller ArchitectureDocument31 pagesIntroduction to 8051 Microcontroller ArchitecturenikitaPas encore d'évaluation

- 8051 MicrocontrollerDocument60 pages8051 Microcontrollergokul docPas encore d'évaluation

- MPMC Iii Unit Q&aDocument21 pagesMPMC Iii Unit Q&aswetha bagadi it's good but how it will workPas encore d'évaluation

- Unit Embedded SystemsDocument43 pagesUnit Embedded SystemsJagruthi ReddyPas encore d'évaluation

- The 8051 ArchitectureDocument80 pagesThe 8051 ArchitectureManoj GadgePas encore d'évaluation

- AT89S52Document20 pagesAT89S52Bhargav GoudPas encore d'évaluation

- 8051 Microcontroller Architecture and Memory OrganizationDocument21 pages8051 Microcontroller Architecture and Memory OrganizationHarsha MkrPas encore d'évaluation

- 8051Document57 pages8051Marut DhunganaPas encore d'évaluation

- Unit-Vi Introduction To MicrocontrollersDocument13 pagesUnit-Vi Introduction To MicrocontrollersTechnoGateKhammamPas encore d'évaluation

- The 8051 Microcontroller: Lets EXPLORE Inside 8051 !!Document45 pagesThe 8051 Microcontroller: Lets EXPLORE Inside 8051 !!ZuricHuntPas encore d'évaluation

- Unit - Iv Syllabus 8051 MicrocontrollerDocument52 pagesUnit - Iv Syllabus 8051 MicrocontrollerSakthivel Palani100% (1)

- 8051 Microcontroller Part 1Document21 pages8051 Microcontroller Part 1Sardar IrfanullahPas encore d'évaluation

- Architecture of the 8051 MicrocontrollerDocument41 pagesArchitecture of the 8051 MicrocontrollerAlex MathewPas encore d'évaluation

- Unit 1-1Document49 pagesUnit 1-1vidhya sPas encore d'évaluation

- Biometric Voting InformationDocument43 pagesBiometric Voting InformationJDNET TECHNOLOGIESPas encore d'évaluation

- Microcontroller & RISC Architecture (2 Marks - Question Bank)Document61 pagesMicrocontroller & RISC Architecture (2 Marks - Question Bank)Dr. N.Shanmugasundaram100% (3)

- Unit - I Difference Between Microprocessor and MicrocontrollerDocument30 pagesUnit - I Difference Between Microprocessor and MicrocontrollerGopinathan MPas encore d'évaluation

- MC Unit-2Document15 pagesMC Unit-2Yugandar Reddy NarraPas encore d'évaluation

- 8051 NotesDocument24 pages8051 Notessreedhar_vkPas encore d'évaluation

- 8051 Microcontroller (2 Marks - Question Bank)Document13 pages8051 Microcontroller (2 Marks - Question Bank)Dr. N.Shanmugasundaram97% (34)

- 80c51 Family ArchitectureDocument15 pages80c51 Family Architectureenriquebadajoz5659Pas encore d'évaluation

- Unit 4Document48 pagesUnit 4formyywork17Pas encore d'évaluation

- Unit4mpmc CSD - WatermarkDocument36 pagesUnit4mpmc CSD - Watermarksundeep94261Pas encore d'évaluation

- AT89S52Document19 pagesAT89S52Nikhith ReddyPas encore d'évaluation

- CST307Document12 pagesCST307Ajnamol N RPas encore d'évaluation

- Unit 5 - Microprocessor & Its Application - WWW - Rgpvnotes.inDocument12 pagesUnit 5 - Microprocessor & Its Application - WWW - Rgpvnotes.inPrayag ParasharPas encore d'évaluation

- Microcontroller 8051 - NotesDocument35 pagesMicrocontroller 8051 - NotesAnirban MandalPas encore d'évaluation

- Features of 8051Document21 pagesFeatures of 8051Basheer V.PPas encore d'évaluation

- EE6008 Notes RejinpaulDocument234 pagesEE6008 Notes RejinpaulB.S. Mothika sriPas encore d'évaluation

- 1 Architecture of 8051 Microcontroller PDFDocument18 pages1 Architecture of 8051 Microcontroller PDFPavin Ka85% (68)

- 8085 MicroprocessorDocument25 pages8085 Microprocessorprofessor2062Pas encore d'évaluation

- 8085Document56 pages8085Kunal MeherPas encore d'évaluation

- MPMC Unit 3Document168 pagesMPMC Unit 3Vijaya KumarPas encore d'évaluation

- Microcontroller 1 J2 and 3 Module NotesDocument38 pagesMicrocontroller 1 J2 and 3 Module NotesArun RajPas encore d'évaluation

- Unit 4 Micro Controller 8051Document20 pagesUnit 4 Micro Controller 8051Anbalagan Guru100% (1)

- Microcontrollers - 8051 Pin DescriptionDocument33 pagesMicrocontrollers - 8051 Pin DescriptionMohamed ShahatPas encore d'évaluation

- 89C51 MicrocontrollerDocument7 pages89C51 MicrocontrollerpranaysudaPas encore d'évaluation

- 8051 Microcontroller Basics by Er. Swapnil V. KawareDocument39 pages8051 Microcontroller Basics by Er. Swapnil V. KawareswapnilPas encore d'évaluation

- Control Unit - 89C52: Introduction About Micro ControllerDocument20 pagesControl Unit - 89C52: Introduction About Micro ControllerSubhashini AruchamyPas encore d'évaluation

- 8051 Microcontroller GuideDocument78 pages8051 Microcontroller GuideArun JyothiPas encore d'évaluation

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960D'EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Pas encore d'évaluation

- Zero Dimension (Exam) 3 PDFDocument74 pagesZero Dimension (Exam) 3 PDFSaawanBaggPas encore d'évaluation

- Zero Dimension (Exam) 3 PDFDocument74 pagesZero Dimension (Exam) 3 PDFSaawanBaggPas encore d'évaluation

- Preguntas Resueltas PDFDocument46 pagesPreguntas Resueltas PDFJustin BullockPas encore d'évaluation

- Problems in Classical MechanicsDocument5 pagesProblems in Classical MechanicsJay ShAhPas encore d'évaluation

- The Laplace Transform SimplifiedDocument53 pagesThe Laplace Transform SimplifiedShanuka DissanayakaPas encore d'évaluation

- 1430-Opera Cluster Solution - InstallationDocument60 pages1430-Opera Cluster Solution - InstallationITDananjaya100% (2)

- B UCSM GUI Storage Management Guide 3 1 Chapter 010101Document16 pagesB UCSM GUI Storage Management Guide 3 1 Chapter 010101vijay kumarPas encore d'évaluation

- SectionA IntroductionDocument7 pagesSectionA IntroductionPaweł KopyśćPas encore d'évaluation

- Win Plot For Al Got Ex Getting StartedDocument24 pagesWin Plot For Al Got Ex Getting StartedDora BAPas encore d'évaluation

- Use Jupyter Notebooks for Data AnalysisDocument10 pagesUse Jupyter Notebooks for Data Analysistsoh100% (1)

- Corrected Oracle 1z0-997 - FinalDocument47 pagesCorrected Oracle 1z0-997 - FinalFatima Tuz Zohora100% (1)

- Form - Show (IWin32Window) Method (System - Windows.Forms) - Microsoft DocsDocument3 pagesForm - Show (IWin32Window) Method (System - Windows.Forms) - Microsoft DocsJohn SmithPas encore d'évaluation

- Computer Repair in Sydney - Anti - Plag01Document1 pageComputer Repair in Sydney - Anti - Plag01Sheetal RathodPas encore d'évaluation

- Unit 2 Installation & Configuration of Android PDFDocument6 pagesUnit 2 Installation & Configuration of Android PDFShaikh WasimaPas encore d'évaluation

- ASK1CA Development Board User's Manual: Shenzhen Tencent Computer Technology Co., LTDDocument8 pagesASK1CA Development Board User's Manual: Shenzhen Tencent Computer Technology Co., LTDalteracbarryPas encore d'évaluation

- hotEx RADIUS Manager Installation GuideDocument40 pageshotEx RADIUS Manager Installation Guidekhvp100% (1)

- Error LogsDocument4 pagesError LogsamitPas encore d'évaluation

- Linux Kernel SeriesDocument140 pagesLinux Kernel SeriesdjstrattosPas encore d'évaluation

- CatOS Vs IOSDocument9 pagesCatOS Vs IOSprojectkmoPas encore d'évaluation

- Tux Droid Basics: The Paginated Version Is Available HereDocument31 pagesTux Droid Basics: The Paginated Version Is Available HereAngel-Panda DiazPas encore d'évaluation

- CS8493 Operating Systems Question BankDocument38 pagesCS8493 Operating Systems Question BankdredPas encore d'évaluation

- Microcontroller Embedded System Design Kec061Document2 pagesMicrocontroller Embedded System Design Kec061henap26195Pas encore d'évaluation

- Release Notes - Cyclone 6.0.1Document1 pageRelease Notes - Cyclone 6.0.1rufino.perea.2Pas encore d'évaluation

- Chapter 1 - IT Essentials - PC Hardware & SoftwareDocument7 pagesChapter 1 - IT Essentials - PC Hardware & Softwaretrim-k75% (8)

- Upgrade or downgrade Entry device firmwareDocument5 pagesUpgrade or downgrade Entry device firmwareBeto MonrockPas encore d'évaluation

- NetPlanner 18-9-0 Installation InstructionsDocument29 pagesNetPlanner 18-9-0 Installation InstructionsShyjin IPPas encore d'évaluation

- EM-IGS-Series (IGS-10020MT - IGS-10080MFT - IGS-12040MT - IGS-20040MT) - v3.0Document401 pagesEM-IGS-Series (IGS-10020MT - IGS-10080MFT - IGS-12040MT - IGS-20040MT) - v3.0jkrreeoonPas encore d'évaluation

- Introduction To Computer: Generations of Computer History of Computer Types of ComputerDocument41 pagesIntroduction To Computer: Generations of Computer History of Computer Types of ComputerMarkPas encore d'évaluation

- Micrologic E Demo Case V2Document34 pagesMicrologic E Demo Case V2Felipe Andres Troncoso ReyesPas encore d'évaluation

- Instalacion HyperspinDocument16 pagesInstalacion HyperspinJorge Andres Ortega SaavedraPas encore d'évaluation

- Nos 730 TroubleshootingDocument82 pagesNos 730 TroubleshootingPrinceRaiPas encore d'évaluation

- System Administrator Resume SampleDocument2 pagesSystem Administrator Resume Sampleresume7.com67% (3)

- Deploying IPv6 in Unified Communications Networks With Cisco Unified Communications Manager PDFDocument144 pagesDeploying IPv6 in Unified Communications Networks With Cisco Unified Communications Manager PDFCharly GlezPas encore d'évaluation

- Jason Stoddard's ResumeDocument1 pageJason Stoddard's ResumeJason StoddardPas encore d'évaluation

- National LVDS Owners Manual 4th Edition 2008Document116 pagesNational LVDS Owners Manual 4th Edition 2008Yani SuPas encore d'évaluation