Académique Documents

Professionnel Documents

Culture Documents

CIGRE NOV 21 23 CT Saturation Detection

Transféré par

Marcelo Andrés Ravest VeasDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

CIGRE NOV 21 23 CT Saturation Detection

Transféré par

Marcelo Andrés Ravest VeasDroits d'auteur :

Formats disponibles

A NOVEL CT SATURATION DETECTION ALGORITHM FOR BUS

DIFFERENTIAL PROTECTION

Zhiying Zhang, Krish Narendra, Dave Fedirchuk

George Punnoose, Premnath

ERLPhase Power Technologies Ltd.

Winnipeg, Canada

Easun Reyrolle Ltd.

Bangalore, India

Abstract - This paper presents a novel algorithm (patented)

for detecting the early CT saturation in bus differential

protection, which, combing with the late CT saturation

block zone and other security enhancement features

provides great securities to the bus differential relay on

external faults, and also maintains the relay with high

sensitivity and fast operation for internal faults.

Index Terms CT saturation, Bus protection, 87B Differential

Protection

1.0 INTRODUCTION

CT saturation is not uncommon in bus differential protection.

Many literatures are available [1],[2],[3],[4], which describes

this phenomenon, especially during external fault conditions.

Microprocessor relays are generally considered as low

impedance relays. The analog inputs (primary current) to these

relays are from the station CTs and to match the required

voltage to the microprocessor level, the currents are further

stepped down on the relay using smaller CTs. Bus protection

involves various configurations of the terminal devices which

typically include feeders, transformers, generators, and the

combinations of various devices. There are different

protection methods or philosophies available to protect a bus

bar element in power system. The most commonly used

method in micro processor relays is based on the percentage

differential scheme. In this paper, a novel CT saturation

algorithm [5] (patented) will be described which is realized by

evaluating the phase relationship of the first derivative (i.e.

dIO/dt and dIR/dt) of the readily available operating current

(IO) and the restraint current (IR) in bus differential

protection. For an internal fault, both IO and IR start to

increase simultaneously and the phase angle between dIO/dt

and dIR/dt is very small and can be considered to be in phase.

For an external fault with CT saturation, no matter how severe

and how soon the CT starts to saturate, the phase angle of

dIO/dt is always lagging with respect to dIR/dt. The use of the

derivative calculations (dIO/dt, dIR/dt) is to capture the IO, IR

trajectory movement sensitively, quickly and accurately. This

algorithm has been tested thoroughly by using the real time

digital simulator (RTDS). The test results have showed that

this algorithm works correctly and reliably for all the test

cases (internal/external, with/without CT saturation, early CT

saturation or late CT saturation, etc.). The test results also

showed that this algorithm is immune to harmonics, DC

offset, line angle, fault types and fault arcing resistance. This

paper will present some of these test results.

2.0 MOTIVATION TO THE NEW ALGORITHM

With the availability of faster digital signal processors at

lower cost, it is not difficult to implement various schemes to

encounter the challenges posed by the legacy measuring

systems. The station CTs are generally designed to meet all

possible fault conditions. Many off-line studies are conducted

prior to the implementation of the protection scheme.

However, there are circumstances, which are beyond control,

which can pose challenges to advanced microprocessor

technology. It is not uncommon that the electrical bus

protection relays are subject to severe saturation due to

external fault currents. The motivation to this algorithm is the

CT saturation caused during external fault, which is described

below.

FIGURE 1: TRAJECTORY OF OPERATING (IO) AND RESTRAIN

CURRENTS (IR)

The CT saturation detection algorithm is illustrated in Figure

1, in which 3 trajectories of IO vs. IR are displayed for (1) an

internal fault, (2) an external fault with earlier CT saturation,

i.e. saturation occurred in less than a cycle after the fault

inception (could be in 1 or 2 ms after the fault inception). This

case normally occurs with the extreme high fault current, and

(3) an external fault with late CT saturation, i.e. the saturation

occurred in greater than one cycle (saturation could occur 2 or

3 cycles later after the fault inception). This case normally

occurs with high DC component (the actual fault current may

not be very high).

20% of slope (see figure 1). Note that IRs (setting) should be

set a little bit greater than the maximum bus transfer load (this

guideline will be in the users manual). For external fault with

late CT saturation, the fault level must be high enough to

make the IO/IR trajectory get into this zoon.

The early and late CT saturations are shown in Figure 2 and

Figure 3 respectively.

3.0 CT SATURATION DETECTION ALGORITHM

FIGURE 2: EARLY CT SATURATION

In the current investigation, the bus protection system includes

a saturation detector that will detect all possible CT saturation

conditions for external faults and block the differential

protection from operating, when this condition prevails. The

proposed method is immune to partial or fully offset

waveforms, harmonics, fault arching resistance, capacitive or

inductive loads, saturation (early or late), and saturation

occurring during only a portion of a detected fault. This

algorithm does not interfere with internal faults (with or

without saturation) and performs the bus protection without

sacrificing the speed and security.

An example of the fault current and the sum of non-fault

currents at a bus needs to be protected is depicted in Figure 4.

FIGURE 3: LATE CT SATURATION

The CT saturation detection algorithm contains two parts to

deal with early CT saturation (curve 2 in figure 1) and late CT

saturation (curve 3 in Figure 1) respectively.

2.1 Early CT saturation Detection

As shown in Figure 2, there is always a non-saturated part on

the fault current waveform initially after the fault inception

though this non-saturated part may only exist for a very short

period of time. In the IO/IR plot, this initial non-saturated part

represents the short movement of the trajectory along the IR

axis in Figure 1 (curve (2)). An algorithm has been developed

to detect this movement along IR axis (even though this

movement may be very short) by comparing the angle

difference between the second harmonics of the dIO/dt and the

dIR/dt [5]. This algorithm has been proven to be extremely

sensitive and effective to correctly detect any early/fast CT

saturation by using the RTDS (Real Time Digital Simulator).

Various test cases, including internal faults, external faults,

arcing resistance, different load level, different CT burdens,

etc., had been tested.

FIGURE 4: CURRENT SIGNALS (FAULT AND NOFAULT): I1(t) NO FALUT, I2(t)= FAULT PHASE WITH

SATURATION

In a conventional way, from the sampled signal, fundamental

phasors are estimated for operating (IO) or differential current

and restrain current (IR) using the following relationship

---(1)

Where, wn= decimated sample count, and IO and IR are

operating and retrain currents respectively. The following

diagram shows the phasor traces.

2.2. Late CT Saturation Detection

The above-described algorithm is only effective when the CT

saturation occurs in the first cycle after the fault. It cannot

detect the late CT saturation. The late CT saturation is

detected by using the Block Zoon defined in Figure 1 (shadow

area). This block zoon is bounded by IR=2*IRs and line with

FIGURE 5: OPERATING (IO) and RESTRAIN (IR)

CURRENTS ESTIMATED USING (1).

The rate of change of the operating current, and the restrain

current is estimated to track the trajectory with respect to time

as shown in Figure 6.

4.0 ADDITIONAL SECURITY FOR HIGH X/R SYSTEM

When the bus protection zone is connected with Generators

and transformers, which exhibit high X/R ratio (30 ~ 100) ,

the system will experience a slow CT saturation, and the

operating and restrain current trajectories exhibit different

behavior. An additional security is provided for the conditions

as referred in Figure 9.

FIGURE 6: TRAJECTORY OF OPERATING CURRENT

AND RESTRAIN CURRENT

A second harmonic of the derivative expression as shown in

Figure 6 is evaluated. In turn, the phase between the second

harmonic of the derivatives of the operating current and

restrain current is estimated and compared against the

threshold value. For the above case, the resulting phase angle

is depicted in Figure 7.

FIGURE 9: IO AND IR TRAJCETORY UNDER LATE CT

SATURATION CONDITIONS

For additional security, some pickup delays are also applied to

the differential protection function as described below.

4.1 IOmin and Slope1 (S1)

______ Phase angle (radians)

---------- Threshold level

x-axis: Samples, y-axis: phase angle in radians

FIGURE 7: PHASE ANGLE ESTIMATATION AND

COMPARISON AGAINST THRESHOLD

The performance of the saturation detector (block or nonblock) is shown below.

As shown in Figure 9, when the IO, IR trajectory enters into

the trip zone from IOmin or slope1 region, a 6 ms (8 ms for

50Hz system) pickup delay is applied so as to be certain that

the IO, IR trajectory has reliably come into the trip zone. To

ensure the fast operating speed of 87B function for internal

faults, IRs should be set to be greater than the maximum bus

transfer load plus safety margin. The safety margin should be

greater than S1/100 per unit. In this way, the IO, IR

trajectories for internal faults are always entered into the trip

zone from the IOmin and slope1 region rather than from the

slope2 region under any pre-fault conditions.

4.2 Slope2 (S2)

x-axis: Samples , y-axis: binary decision (1- block )

FIGURE 8: ILLUSTRATION

DETECTOR PERFORMANCE

OF

SATURATION

When a slow CT saturation occurs during an external fault as

described in section 2.2, the IO, IR trajectory may enter the

trip zone, but always from the slope2 region. In most cases

when the slow CT saturation occurs, the IO, IR trajectory will

enter into the saturation block zone first so that the block flag

will be set and 87B trip will be blocked accordingly. However,

in some special situations when the fault current contains low

AC current combined with high magnitude slow decaying DC

current, the external fault current level may not be high

enough to bring the IO, IR trajectory into the saturation block

zone, but it might still bring the IO, IR trajectory into the trip

zone from slope2 region for a short period of time (the CT

recovers to normal quickly). In order to make the relay secure

under these special situations, a 36 ms (45ms for 50Hz

system) pickup delay is applied. As described before, this

delay does not affect the operating speed for internal faults.

4.3 IOH High Setting

There is no any intentional delay as long as the IO exceeds the

IOH setting threshold no matter where the IO, IR trajectory

comes from. The purpose of the IOH zone is to clear the

extremely severe bus internal faults as soon as possible.

5.0 CONCLUSIONS

A novel CT saturation algorithm for bus differential protection

has been presented and discussed. This algorithm has been

well tested for all possible CT saturation and with additional

security measures described; this algorithm is immune to

partial or fully offset fault signals, harmonics, fault arching,

and severity of CT saturation.

6.0

REFERENCES

[1]

Bus Differential Protection, J. G. Adrichak Jorge

Cardenas, 22nd WPRC Conference, Spokane, Ocotber

1995, pp 1-11.

[2]

The Art and Science of Protective Relaying , C.

Russel Mason.

[3]

Prediction of CT saturation period for differential

relay adaptation purposes , Waldemar Rebizant et.

al. , International Conference on Advanced Power

System Automation and Protection, Korea, 2004, pp

1-6.

[4]

An Impedance based CT saturation detection

algorithm for Bus- Bar differential Protection,

Cesareo Fernandez, IEEE Transaction on Power

Delivery, Vol 16, No. 4, October 2001, pp 468-472.

[5]

Electrical Bus Protection Method and Apparatus,

Dave FedirChuk et. al, US Patent - 7,199,991 B2,

Issued April 2007.

7.0 AUTHORS BIOGRAPHY

ZHIYING ZHANG - received his B.Sc. and M.Sc. degrees in

Electrical Engineering from the North China Electric Power

University (NCEPU), China, in 1982 and in 1985 respectively.

He received his Ph.D. degree in Electrical Engineering from

the University of Manitoba, Canada, in 1994. From 1993 to

2000, he worked for APT Power Technologies as a senior

relay design engineer, and since 2000, he has been working

for NxtPhase Corp. as a senior product development engineer.

He is a registered professional engineer in the province of

Manitoba. His areas of interest include power system

protection, control and monitoring.

KRISH NARENDRA obtained his B.E. (Electrical

Engineering) in 1986 from University Visweswaraiah College

of Engineering (UVCE), and Msc (E.E) , Ph.D. (E.E) with a

specialisation in High Voltage Engineering from Indian

Institute of Science, India in 1989 and 1993 respectively. He

joined Electrical and Computer Engineering Department of

Concordia University, Montreal as a Research Scholar in

1995.

From 1996 - 2000 he was with APT Power

Technologies as a senior software developer. In 2000 he

joined NxtPhase T&D Corporation and since 2006 he is the R

& D Engineering Manager, ERLPhase Power Technologies

Ltd, Winnipeg, Canada. He has about 15 years of software

development expertise and about 16 publications to his credit.

He is actively participating in the PRSC working groups and a

member of the PRTT of NASPI. His areas of interests include

Power Systems Disturbance Analysis, Protection, HVDC

Controls, Neural Networks, Fuzzy logic, Phasor Technology

(PMUs). He can be contacted at Knarendra@nxtphase.com.

Vous aimerez peut-être aussi

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Pas encore d'évaluation

- Dayco-Timing Belt Training - Entrenamiento Correa DentadaDocument9 pagesDayco-Timing Belt Training - Entrenamiento Correa DentadaDeiby CeleminPas encore d'évaluation

- Paralleling Cts For Line Differential ProtectionDocument15 pagesParalleling Cts For Line Differential ProtectionYeissonSanabria100% (1)

- Introduction to Power System ProtectionD'EverandIntroduction to Power System ProtectionPas encore d'évaluation

- Low Impedance Restricted Earth Fault ProtectionDocument4 pagesLow Impedance Restricted Earth Fault ProtectionGary_Tan_Kai_S_9974Pas encore d'évaluation

- Mkm1133 Instrumentation and Control SystemDocument19 pagesMkm1133 Instrumentation and Control SystemNurul Nadia Mohd ZawawiPas encore d'évaluation

- Trafo 3 AsdDocument4 pagesTrafo 3 AsdAchyar Maulana PratamaPas encore d'évaluation

- Pamphlet 89 Chlorine Scrubbing SystemsDocument36 pagesPamphlet 89 Chlorine Scrubbing Systemshfguavita100% (4)

- Transformer Inrush Conditions in Differential Protection SchemesDocument25 pagesTransformer Inrush Conditions in Differential Protection Schemesengwazi100% (2)

- Power Electronics Applied to Industrial Systems and Transports: Volume 5: Measurement Circuits, Safeguards and Energy StorageD'EverandPower Electronics Applied to Industrial Systems and Transports: Volume 5: Measurement Circuits, Safeguards and Energy StoragePas encore d'évaluation

- Introduction to Power System ProtectionD'EverandIntroduction to Power System ProtectionÉvaluation : 5 sur 5 étoiles5/5 (1)

- Storage Tanks Overfill Prevention Better PracticesDocument2 pagesStorage Tanks Overfill Prevention Better PracticesRicardo Bec100% (1)

- Power System Protection - Part 06 PDFDocument16 pagesPower System Protection - Part 06 PDFSalih Ahmed ObeidPas encore d'évaluation

- 87 CT Class ExplanationDocument11 pages87 CT Class ExplanationdskymaximusPas encore d'évaluation

- SD-NOC-MAR-202 - Rev00 Transfer of Personnel at Offshore FacilitiesDocument33 pagesSD-NOC-MAR-202 - Rev00 Transfer of Personnel at Offshore Facilitiestho03103261100% (1)

- Diffuse Algorithms for Neural and Neuro-Fuzzy Networks: With Applications in Control Engineering and Signal ProcessingD'EverandDiffuse Algorithms for Neural and Neuro-Fuzzy Networks: With Applications in Control Engineering and Signal ProcessingPas encore d'évaluation

- 06227522Document4 pages06227522Muhammad SulaimanPas encore d'évaluation

- Quantifying The Potential Impacts of Disturbances On Power System ProtectionDocument4 pagesQuantifying The Potential Impacts of Disturbances On Power System ProtectionmohsinamanPas encore d'évaluation

- AP PTC 2012 19 Teratam EnuDocument7 pagesAP PTC 2012 19 Teratam EnubcqbaoPas encore d'évaluation

- A New Differential Protection Scheme For Busbar Considering CT Saturation EffectDocument4 pagesA New Differential Protection Scheme For Busbar Considering CT Saturation EffectMuruganPas encore d'évaluation

- TeedDocument7 pagesTeedRaguramanPas encore d'évaluation

- Ger 3961 PDFDocument16 pagesGer 3961 PDFBalan PalaniappanPas encore d'évaluation

- Oscilloscopes and Chart Recorders (Revision 3.0, 24/5/2008)Document11 pagesOscilloscopes and Chart Recorders (Revision 3.0, 24/5/2008)Eyad IbrahimPas encore d'évaluation

- Differential Relay With Adaptation During Saturation PeriodDocument6 pagesDifferential Relay With Adaptation During Saturation Periodasim saeedPas encore d'évaluation

- WindowDocument4 pagesWindowsirisiri100Pas encore d'évaluation

- 5988 6254ej W 2Document140 pages5988 6254ej W 2poorna434Pas encore d'évaluation

- Adaptive Distance Protection Compensated: Transmission LinesDocument6 pagesAdaptive Distance Protection Compensated: Transmission LinesthavaselvanPas encore d'évaluation

- Appl 03 Coordination of Overcurrent Relais With Fuses enDocument10 pagesAppl 03 Coordination of Overcurrent Relais With Fuses enUpi SupriyatnaPas encore d'évaluation

- GRB100 Rev3Document0 pageGRB100 Rev3comportPas encore d'évaluation

- CT Saturation 1Document6 pagesCT Saturation 111389Pas encore d'évaluation

- Fundamentals of Power System Protection Lecture 2: Protection Paradigms - Apparatus ProtectionDocument7 pagesFundamentals of Power System Protection Lecture 2: Protection Paradigms - Apparatus Protectionsunny1725Pas encore d'évaluation

- Generator Transformer Backup ProtectionDocument7 pagesGenerator Transformer Backup ProtectionbansalrPas encore d'évaluation

- 6928 DeterminingCT RC 20190905 Web PDFDocument15 pages6928 DeterminingCT RC 20190905 Web PDFDouglas Omar Rodriguez PerezPas encore d'évaluation

- Analysis of The Behavior of One Digital Distance Relay Under Islanding Condition With ATPDocument6 pagesAnalysis of The Behavior of One Digital Distance Relay Under Islanding Condition With ATPJaime Florez ChoquePas encore d'évaluation

- Performance Improvement For Distance Relay Based Fuzzy Logic For All Prospective FaultsDocument9 pagesPerformance Improvement For Distance Relay Based Fuzzy Logic For All Prospective FaultsRizki SetiawanPas encore d'évaluation

- New Method of Power Swing Blocking For Digital Distance ProtectionDocument8 pagesNew Method of Power Swing Blocking For Digital Distance ProtectionJohari Zhou Hao LiPas encore d'évaluation

- Busbar Protection - A ReviewDocument5 pagesBusbar Protection - A ReviewPrajiWazharyPas encore d'évaluation

- 6928 DeterminingCT RC 20210129 WebDocument15 pages6928 DeterminingCT RC 20210129 WebKrishnan KrishPas encore d'évaluation

- Analysis of Oscillograms (v6.0)Document21 pagesAnalysis of Oscillograms (v6.0)luhusapaPas encore d'évaluation

- Enhanced Modelling and Early Detection oDocument8 pagesEnhanced Modelling and Early Detection oDalal HelmiPas encore d'évaluation

- Bus Bar ProtectionDocument6 pagesBus Bar ProtectionRitesh JaiswalPas encore d'évaluation

- Chapter 3 Basics of Protective RelayingDocument17 pagesChapter 3 Basics of Protective Relayingkaren dejoPas encore d'évaluation

- Distance Protection With Tele-Protection On An OHL FeederDocument32 pagesDistance Protection With Tele-Protection On An OHL FeederAndres Alva JustoPas encore d'évaluation

- Fault Resistance, Location and Inception Angle Effects On DC Offset of The Fault CurrentsDocument6 pagesFault Resistance, Location and Inception Angle Effects On DC Offset of The Fault CurrentsItalo ChiarellaPas encore d'évaluation

- 1MRG008054 en Application Note Function Description For High Impedance Busbar Protection PDFDocument13 pages1MRG008054 en Application Note Function Description For High Impedance Busbar Protection PDFnp_bhuvaneswarPas encore d'évaluation

- RF Seeker Stabilisation AntenneDocument4 pagesRF Seeker Stabilisation AntennetttPas encore d'évaluation

- A New Approach Transformer Ground Differential: FOR ProtectionDocument15 pagesA New Approach Transformer Ground Differential: FOR ProtectionproteccionesPas encore d'évaluation

- Ger 3981Document18 pagesGer 3981riddler_007Pas encore d'évaluation

- Teaching Distance Relay Using Matlab - Simulink Graphical User Interface - Hafizi Idris - AcademiaDocument4 pagesTeaching Distance Relay Using Matlab - Simulink Graphical User Interface - Hafizi Idris - AcademiarajababudonikiPas encore d'évaluation

- A New Method of Voltage Sag and Swell Detection: Raj Naidoo, Member, IEEE, and Pragasen Pillay, Fellow, IEEEDocument8 pagesA New Method of Voltage Sag and Swell Detection: Raj Naidoo, Member, IEEE, and Pragasen Pillay, Fellow, IEEEjcrodriguez83Pas encore d'évaluation

- Microprocessor Based Controller For A Motor Car Park: Ebegba, D and Anyasi, F.IDocument7 pagesMicroprocessor Based Controller For A Motor Car Park: Ebegba, D and Anyasi, F.IInternational Organization of Scientific Research (IOSR)Pas encore d'évaluation

- What Is EOCR ?: Mechanical Load Current of Motor Detecting Current With CT SensorDocument13 pagesWhat Is EOCR ?: Mechanical Load Current of Motor Detecting Current With CT SensorNaveen Gupta100% (1)

- Areva P443 Protection by Areva PaperDocument6 pagesAreva P443 Protection by Areva PaperRajesh BoddunaPas encore d'évaluation

- Kumar 2016Document5 pagesKumar 2016muayid al omaryPas encore d'évaluation

- Robust Non-Communication Line Protection Scheme Using Novel QuantitiesDocument8 pagesRobust Non-Communication Line Protection Scheme Using Novel QuantitiessunitharajababuPas encore d'évaluation

- Carga Harmonica Diferencial PDFDocument25 pagesCarga Harmonica Diferencial PDFFernando AlegriaPas encore d'évaluation

- High Impedance Busbar Differential ProtectionDocument16 pagesHigh Impedance Busbar Differential Protectionዛላው መናPas encore d'évaluation

- CT Saturation Study Using PSCAD JA and Lewis ModelsDocument6 pagesCT Saturation Study Using PSCAD JA and Lewis ModelsLUIS ANGEL YARANGA SANTIPas encore d'évaluation

- GATE Chemical Engineering 2015Document18 pagesGATE Chemical Engineering 2015Sabareesh Chandra ShekarPas encore d'évaluation

- Bamboo People - An Interdisciplinary Unit For High SchoolDocument6 pagesBamboo People - An Interdisciplinary Unit For High SchoolChipo Jean MarundaPas encore d'évaluation

- تأثير العناصر الثقافية والبراغماتية الأسلوبية في ترجمة سورة الناس من القرآن الكريم إلى اللغة الإ PDFDocument36 pagesتأثير العناصر الثقافية والبراغماتية الأسلوبية في ترجمة سورة الناس من القرآن الكريم إلى اللغة الإ PDFSofiane DouifiPas encore d'évaluation

- Hydrology Report at CH-9+491Document3 pagesHydrology Report at CH-9+491juliyet strucPas encore d'évaluation

- CTRLX Automation BrochureDocument60 pagesCTRLX Automation BrochureNinja do SofáPas encore d'évaluation

- Noth PicturesDocument17 pagesNoth PicturesJana AssaPas encore d'évaluation

- Practice Test - Math As A Language - MATHEMATICS IN THE MODERN WORLDDocument8 pagesPractice Test - Math As A Language - MATHEMATICS IN THE MODERN WORLDMarc Stanley YaoPas encore d'évaluation

- Caroline G Babin: Undergraduate Degree at Louisiana State University in Baton Rouge, Louisiana - Currently EnrolledDocument2 pagesCaroline G Babin: Undergraduate Degree at Louisiana State University in Baton Rouge, Louisiana - Currently EnrolledCaroline BabinPas encore d'évaluation

- S25580 MSDS Corn Starch FisherchiDocument6 pagesS25580 MSDS Corn Starch FisherchiProcurement ProlinePas encore d'évaluation

- Afa Coursework ExamplesDocument6 pagesAfa Coursework Examplesiuhvgsvcf100% (2)

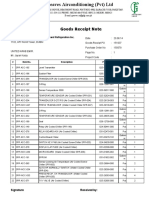

- Goods Receipt Note: Johnson Controls Air Conditioning and Refrigeration Inc. (YORK) DateDocument4 pagesGoods Receipt Note: Johnson Controls Air Conditioning and Refrigeration Inc. (YORK) DateSaad PathanPas encore d'évaluation

- Manual HobartDocument39 pagesManual HobartВолодимир БроPas encore d'évaluation

- Chemical Engineering & Processing: Process Intensi Fication: ArticleinfoDocument9 pagesChemical Engineering & Processing: Process Intensi Fication: Articleinfomiza adlinPas encore d'évaluation

- 02 Lab 1.HCIDocument2 pages02 Lab 1.HCILopao SerojemPas encore d'évaluation

- Filling The Propylene Gap On Purpose TechnologiesDocument12 pagesFilling The Propylene Gap On Purpose Technologiesvajidqc100% (1)

- With You: Full-Line CatalogDocument68 pagesWith You: Full-Line CatalogCOMIPas encore d'évaluation

- Scope and Sequence 2020 2021...Document91 pagesScope and Sequence 2020 2021...Ngọc Viễn NguyễnPas encore d'évaluation

- Manitou 1350RDocument4 pagesManitou 1350RcandlaganPas encore d'évaluation

- KSP Solutibilty Practice ProblemsDocument22 pagesKSP Solutibilty Practice ProblemsRohan BhatiaPas encore d'évaluation

- PCM 2.4l Turbo 5 de 5Document2 pagesPCM 2.4l Turbo 5 de 5Felix VelasquezPas encore d'évaluation

- Dredge Yard Gate Valve BrochureDocument5 pagesDredge Yard Gate Valve BrochureFederico BabichPas encore d'évaluation

- Waste Foundry Sand and Its Leachate CharDocument10 pagesWaste Foundry Sand and Its Leachate CharJanak RaazzPas encore d'évaluation

- Engineering Geology: Wei-Min Ye, Yong-Gui Chen, Bao Chen, Qiong Wang, Ju WangDocument9 pagesEngineering Geology: Wei-Min Ye, Yong-Gui Chen, Bao Chen, Qiong Wang, Ju WangmazharPas encore d'évaluation

- Why We Need A Flying Amphibious Car 1. CarsDocument20 pagesWhy We Need A Flying Amphibious Car 1. CarsAsim AhmedPas encore d'évaluation

- Diltoids Numberletter Puzzles Activities Promoting Classroom Dynamics Group Form - 38486Document5 pagesDiltoids Numberletter Puzzles Activities Promoting Classroom Dynamics Group Form - 38486sinirsistemiPas encore d'évaluation

- HP Scanjet Pro 2500 F1 Flatbed Scanner: Boost Productivity With Fast, Versatile ScanningDocument2 pagesHP Scanjet Pro 2500 F1 Flatbed Scanner: Boost Productivity With Fast, Versatile ScanningParesh BabariaPas encore d'évaluation