Académique Documents

Professionnel Documents

Culture Documents

The 8051 Microcontroller Architecture: Contents

Transféré par

Iqbal Uddin KhanTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

The 8051 Microcontroller Architecture: Contents

Transféré par

Iqbal Uddin KhanDroits d'auteur :

Formats disponibles

08/09/2015

The 8051 Microcontroller

architecture

Contents:

Introduction

Block Diagram and Pin Description of the 8051

Registers

Some Simple Instructions

Assembly language

Running an 8051 program

Memory mapping in 8051

8051 Flag bits and the PSW register

Addressing Modes

16-bit, BCD and Signed Arithmetic in 8051

Stack in the 8051

LOOP and JUMP Instructions

CALL Instructions

I/O Port Programming

08/09/2015

Three criteria in Choosing a Microcontroller

1. meeting the computing needs of the task efficiently and cost

effectively

speed, the amount of ROM and RAM, the number of I/O ports and

timers, size, packaging, power consumption

easy to upgrade

cost per unit

2. availability of software development tools

assemblers, debuggers, C compilers, emulator, simulator, technical

support

3. wide availability and reliable sources of the microcontrollers.

3

The 8051 microcontroller

A Harvard architecture (separate instruction/data memories)

Single chip microcontroller (C)

Developed by Intel in 1980 for use in embedded systems.

Today largely superseded by a vast range of faster and/or functionally

enhanced 8051-compatible devices manufactured by more than 20

independent manufacturers

08/09/2015

Block Diagram

External interrupts

Interrupt

Control

On-chip

ROM for

program

code

Timer/Counter

On-chip

RAM

Timer 1

Timer 0

Counter

Inputs

CPU

OSC

Bus

Control

4 I/O Ports

P0 P1 P2 P3

Serial

Port

TxD RxD

Address/Data

5

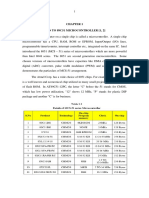

Comparison of the 8051 Family Members

Feature

ROM (program space in bytes)

RAM (bytes)

Timers

I/O pins

Serial port

Interrupt sources

8051

4K

128

2

32

1

6

8052

8K

256

3

32

1

8

8031

0K

128

2

32

1

6

08/09/2015

Pin Description of the 8051

08/09/2015

Pins of 80511/4

Vccpin 40

Vcc provides supply voltage to the chip.

The voltage source is +5V.

GNDpin 20ground

XTAL1 and XTAL2pins 19,18

These 2 pins provide external clock.

Way 1using a quartz crystal oscillator

Way 2using a TTL oscillator

Example 4-1 shows the relationship between XTAL and the

machine cycle.

Pins of 80512/4

RSTpin 9reset

It is an input pin and is active highnormally low.

The high pulse must be high at least 2 machine cycles.

It is a power-on reset.

Upon applying a high pulse to RST, the microcontroller will

reset and all values in registers will be lost.

Reset values of some 8051 registers

Way 1Power-on reset circuit

Way 2Power-on reset with debounce

10

08/09/2015

Pins of 80513/4

/EApin 31external access

There is no on-chip ROM in 8031 and 8032 .

The /EA pin is connected to GND to indicate the code is stored

externally.

/PSEN ALE are used for external ROM.

For 8051, /EA pin is connected to Vcc.

/ means active low.

/PSENpin 29program store enable

This is an output pin and is connected to the OE pin of the ROM.

See Chapter 14.

11

Pins of 80514/4

ALEpin 30address latch enable

It is an output pin and is active high.

8051 port 0 provides both address and data.

The ALE pin is used for de-multiplexing the address and data by

connecting to the G pin of the 74LS373 latch.

I/O port pins

The four ports P0, P1, P2, and P3.

Each port uses 8 pins.

All I/O pins are bi-directional.

12

08/09/2015

Figure 4-2 (a). XTAL Connection to 8051

Using a quartz crystal oscillator

We can observe the frequency on the XTAL2

pin.

13

Figure (b). XTAL Connection to an External Clock Source

N

C

Using a TTL oscillator

XTAL2 is unconnected.

EXTERNAL

OSCILLATOR

SIGNAL

XTAL2

XTAL1

GND

14

08/09/2015

RESET Value of Some 8051 Registers:

Register

PC

ACC

B

PSW

SP

DPTR

Reset Value

0000

0000

0000

0000

0007

0000

RAM are all zero.

15

Power-On RESET Circuit

Vcc

+

10 uF

31

30 pF

11.0592 MHz

19

EA/VPP

X1

8.2 K

30 pF

18

X2

9 RST

16

08/09/2015

Power-On RESET with Debounce

Vcc

31

10 uF

EA/VPP

X1

30 pF

X2

RST

9

8.2 K

17

Pins of I/O Port

The 8051 has four I/O ports

Port 0 pins 32-39P0P0.0P0.7

Port 1pins 1-8 P1P1.0P1.7

Port 2pins 21-28P2P2.0P2.7

Port 3pins 10-17P3P3.0P3.7

Each port has 8 pins.

Named P0.X X=0,1,...,7, P1.X, P2.X, P3.X

ExP0.0 is the bit 0LSBof P0

ExP0.7 is the bit 7MSBof P0

These 8 bits form a byte.

Each port can be used as input or output (bi-direction).

18

08/09/2015

Registers

A

B

R0

DPTR

DPH

DPL

R1

R2

PC

PC

R3

R4

Some 8051 16-bit Register

R5

R6

R7

Some 8-bitt Registers of

the 8051

19

Memory Map (RAM)

20

10

08/09/2015

CPU timing

Most 8051 instructions are executed in one cycle.

MUL (multiply) and DIV (divide) are the only instructions that take more than two

cycles to complete (four cycles)

Normally two code bytes are fetched from the program memory during every

machine cycle.

The only exception to this is when a MOVX instruction is executed. MOVX is a onebyte, 2-cycle instruction that accesses external data memory.

During a MOVX, the two fetches in the second cycle are skipped while the external

data memory is being addressed and strobed.

21

8051 machine cycle

22

11

08/09/2015

Example :

Find the machine cycle for

(a) XTAL = 11.0592 MHz

(b) XTAL = 16 MHz.

Solution:

(a) 11.0592 MHz / 12 = 921.6 kHz;

machine cycle = 1 / 921.6 kHz = 1.085 s

(b) 16 MHz / 12 = 1.333 MHz;

machine cycle = 1 / 1.333 MHz = 0.75 s

23

Timers

8051 has two 16-bit on-chip timers that can be used for timing

durations or for counting external events

The high byte for timer 1 (TH1) is at address 8DH while the low byte

(TL1) is at 8BH

The high byte for timer 0 (TH0) is at 8CH while the low byte (TL0) is at

8AH.

Timer Mode Register (TMOD) is at address 88H

26

12

08/09/2015

Timer Mode Register

Bit 7: Gate bit; when set, timer only runs while \INT high. (T0)

Bit 6: Counter/timer select bit; when set timer is an event

counter when cleared timer is an interval timer (T0)

Bit 5: Mode bit 1 (T0)

Bit 4: Mode bit 0 (T0)

Bit 3: Gate bit; when set, timer only runs while \INT high. (T1)

Bit 2: Counter/timer select bit; when set timer is an event

counter when cleared timer is an interval timer (T1)

Bit 1: Mode bit 1 (T1)

Bit 0: Mode bit 0 (T1)

27

Timer Modes

M1-M0: 00 (Mode 0) 13-bit mode (not commonly used)

M1-M0: 01 (Mode 1) - 16-bit timer mode

M1-M0: 10 (Mode 2) - 8-bit auto-reload mode

M1-M0: 11 (Mode 3) Split timer mode

28

13

08/09/2015

8051 Interrupt Vector Table

29

The Stack and Stack Pointer

The Stack Pointer, like all registers except DPTR and PC, may hold an 8-bit (1-byte)

value.

The Stack Pointer is used to indicate where the next value to be removed from the

stack should be taken from.

When you push a value onto the stack, the 8051 first increments the value of SP and

then stores the value at the resulting memory location.

When you pop a value off the stack, the 8051 returns the value from the memory

location indicated by SP, and then decrements the value of SP.

This order of operation is important. When the 8051 is initialized SP will be initialized

to 07h. If you immediately push a value onto the stack, the value will be stored in

Internal RAM address 08h. This makes sense taking into account what was mentioned

two paragraphs above: First the 8051 will increment the value of SP (from 07h to 08h)

and then will store the pushed value at that memory address (08h).

SP is modified directly by the 8051 by six instructions: PUSH, POP, ACALL, LCALL, RET,

and RETI. It is also used intrinsically whenever an interrupt is triggered

30

14

08/09/2015

The End

31

15

Vous aimerez peut-être aussi

- 2.8051 Pin Diagram.1Document29 pages2.8051 Pin Diagram.1Yakkali KiranPas encore d'évaluation

- The 8051 Microcontroller ArchitectureDocument30 pagesThe 8051 Microcontroller Architecturesuperbs1001Pas encore d'évaluation

- The 8051 Microcontroller: Lets EXPLORE Inside 8051 !!Document45 pagesThe 8051 Microcontroller: Lets EXPLORE Inside 8051 !!ZuricHuntPas encore d'évaluation

- A Presentation On Microcontroller 8051Document22 pagesA Presentation On Microcontroller 8051Praveen ShrivastavaPas encore d'évaluation

- The 8051 MicrocontrollerDocument72 pagesThe 8051 MicrocontrollertansnvarmaPas encore d'évaluation

- ON Microcontroller-8051 and Applications: BY G N V Ratna Kishor M.Sc.,M.Tech. Asst. ProfessorDocument66 pagesON Microcontroller-8051 and Applications: BY G N V Ratna Kishor M.Sc.,M.Tech. Asst. ProfessorbhavanimaddulaPas encore d'évaluation

- Unit 2Document59 pagesUnit 2ayush charde 786Pas encore d'évaluation

- 8051 Microcontroller FeaturesDocument42 pages8051 Microcontroller FeaturesTech_MX67% (3)

- 8051 Microcontroller: Chapter - 2Document58 pages8051 Microcontroller: Chapter - 2nebyuPas encore d'évaluation

- 8051 NotesDocument41 pages8051 NotesSringaSyamPas encore d'évaluation

- Unit IVDocument26 pagesUnit IVSoundarrajan RajanPas encore d'évaluation

- WINSEM2023-24 BECE204L TH VL2023240505623 2024-01-05 Reference-Material-IIDocument64 pagesWINSEM2023-24 BECE204L TH VL2023240505623 2024-01-05 Reference-Material-IIpratyakshswamiPas encore d'évaluation

- 8051 MicrocontrollerDocument222 pages8051 Microcontrollergirish100% (1)

- Design By: Harman S. Gahir Ap, Mca CGC-GharuanDocument38 pagesDesign By: Harman S. Gahir Ap, Mca CGC-GharuanHarman GahirPas encore d'évaluation

- Architecture 8051Document22 pagesArchitecture 8051Selva Kumar SkPas encore d'évaluation

- MPMC - UNIT - 2 - All SlidesDocument117 pagesMPMC - UNIT - 2 - All Slidesneeraj ChowdaryPas encore d'évaluation

- MPMC Unit 3Document168 pagesMPMC Unit 3Vijaya KumarPas encore d'évaluation

- The 8051 Microcontroller: Prepared By, R-Thandaiah PrabuDocument46 pagesThe 8051 Microcontroller: Prepared By, R-Thandaiah PrabushankarsahniPas encore d'évaluation

- 8051 Vs Motorola 68HC11Document19 pages8051 Vs Motorola 68HC11zuanne83Pas encore d'évaluation

- 8051 Architecture Contains The Following:: Block DiagramDocument17 pages8051 Architecture Contains The Following:: Block DiagramAtul GoyalPas encore d'évaluation

- 8051Document72 pages8051Arjun Aj100% (1)

- Microcontrollers LAB Manual: LAB CODE: EC - 607, EE - 410Document28 pagesMicrocontrollers LAB Manual: LAB CODE: EC - 607, EE - 410Ajay PatilPas encore d'évaluation

- 4-MODULE-3 Microcontroller 8051 - Pin Description-10!01!2024Document53 pages4-MODULE-3 Microcontroller 8051 - Pin Description-10!01!2024gerapel837Pas encore d'évaluation

- TP2804Document17 pagesTP2804jose jozePas encore d'évaluation

- Presentation AviDocument29 pagesPresentation AvipoonamshallyPas encore d'évaluation

- 08 - Chapter 1 PDFDocument47 pages08 - Chapter 1 PDFMalcolm DopaimPas encore d'évaluation

- Klu 8051Document165 pagesKlu 8051manvithbPas encore d'évaluation

- 8051Document32 pages8051Narasimman Don100% (1)

- 0 - MPunit-6 & 7Document118 pages0 - MPunit-6 & 7Vinay KumarPas encore d'évaluation

- A Brief Introduction of Micro Controllers 8051Document64 pagesA Brief Introduction of Micro Controllers 8051Pradeep Varma0% (1)

- 8051 Microcontroller Objectives: Understand The 8051 Architecture Use SFR in C Use I/O Ports in CDocument60 pages8051 Microcontroller Objectives: Understand The 8051 Architecture Use SFR in C Use I/O Ports in CKhushwant TanwarPas encore d'évaluation

- 8051 Lab ManualDocument35 pages8051 Lab ManualVenkat BalajiPas encore d'évaluation

- Submitted To: Submitted By: Mr. Abishek Sharma Arish Kumar Sharma 100640418019 Ece-ADocument25 pagesSubmitted To: Submitted By: Mr. Abishek Sharma Arish Kumar Sharma 100640418019 Ece-ASharan ThapaPas encore d'évaluation

- MP MC Unit IVDocument26 pagesMP MC Unit IVS D NagulanPas encore d'évaluation

- Unit 4 ADocument50 pagesUnit 4 ASahil SinghPas encore d'évaluation

- 8-Bit Microcontroller With 4K Bytes Flash AT89C4051: FeaturesDocument18 pages8-Bit Microcontroller With 4K Bytes Flash AT89C4051: FeaturesAri SoerjantoPas encore d'évaluation

- Automatic Speed BreakerDocument69 pagesAutomatic Speed BreakerRohitesh KumarPas encore d'évaluation

- The 8051 Microcontroller: (Please Ignore Repeated Slides If Any. Also, Refer Text Too While Studying All The Slides)Document78 pagesThe 8051 Microcontroller: (Please Ignore Repeated Slides If Any. Also, Refer Text Too While Studying All The Slides)Nicky SanthoshPas encore d'évaluation

- AT89S2051Document46 pagesAT89S2051Hr ReferralPas encore d'évaluation

- Lab 1+2 Timer and StopwatchDocument14 pagesLab 1+2 Timer and StopwatchMuhd Ikram ShabryPas encore d'évaluation

- Primer Tutorial On 8051Document21 pagesPrimer Tutorial On 8051ChanderKishoreJoshiPas encore d'évaluation

- 8051 MicrocontrollerDocument83 pages8051 Microcontrollerhareesh.makesu100% (1)

- Module 1Document93 pagesModule 1Kishore KumarPas encore d'évaluation

- Microcontroller 8051 100110090948 Phpapp02Document94 pagesMicrocontroller 8051 100110090948 Phpapp02savisuPas encore d'évaluation

- Test 1Document56 pagesTest 1Satyam LalaPas encore d'évaluation

- 2.1 Microcontroller: Embedded SystemsDocument23 pages2.1 Microcontroller: Embedded SystemspavanPas encore d'évaluation

- Millman Halkias - Integrated ElectronicsDocument28 pagesMillman Halkias - Integrated ElectronicsPranav SinhaPas encore d'évaluation

- Micro Controller Risc ArchitecturesDocument33 pagesMicro Controller Risc ArchitecturesSankar SubramaniamPas encore d'évaluation

- Introduction To Project: Chapter-1Document31 pagesIntroduction To Project: Chapter-1amit6357100% (1)

- At89s52 MicrocontrollerDocument6 pagesAt89s52 MicrocontrollerMikroc Thupati SrinivsPas encore d'évaluation

- 8-Bit Microcontroller With 2K Bytes Flash AT89C2051: FeaturesDocument15 pages8-Bit Microcontroller With 2K Bytes Flash AT89C2051: FeaturesTrần Trung HiếuPas encore d'évaluation

- Microcontroller Lab Manual With Arduino Programe PDFDocument63 pagesMicrocontroller Lab Manual With Arduino Programe PDFTejasaiPas encore d'évaluation

- 3Document34 pages3Ankit AgrawalPas encore d'évaluation

- 80C51 Family Derivatives: 8XC552/562 OverviewDocument60 pages80C51 Family Derivatives: 8XC552/562 OverviewMiguel MacpPas encore d'évaluation

- A4.8051 Communication Protocols - UART, RS232Document5 pagesA4.8051 Communication Protocols - UART, RS232sneha singhPas encore d'évaluation

- MA1Document143 pagesMA1Manish NarkhedePas encore d'évaluation

- Microcontroller 8051Document42 pagesMicrocontroller 8051om18sahuPas encore d'évaluation

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960D'EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Pas encore d'évaluation

- Microprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureD'EverandMicroprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureÉvaluation : 1 sur 5 étoiles1/5 (1)

- R-Pi - Python - IEEE - 02Document45 pagesR-Pi - Python - IEEE - 02Iqbal Uddin KhanPas encore d'évaluation

- AFPGA Assignments - CompleteDocument25 pagesAFPGA Assignments - CompleteIqbal Uddin KhanPas encore d'évaluation

- Course Outline - COAL - Fall 2015Document4 pagesCourse Outline - COAL - Fall 2015Iqbal Uddin KhanPas encore d'évaluation

- Lab 01 - 07Document40 pagesLab 01 - 07Iqbal Uddin KhanPas encore d'évaluation

- 1 Clearance Form (Concerned Dept)Document1 page1 Clearance Form (Concerned Dept)Iqbal Uddin KhanPas encore d'évaluation

- 1 - Write A Module For A 8 To 1 MuxDocument7 pages1 - Write A Module For A 8 To 1 MuxIqbal Uddin KhanPas encore d'évaluation

- Lab 00 - Specimen OSDocument6 pagesLab 00 - Specimen OSIqbal Uddin KhanPas encore d'évaluation

- Chapter 01Document17 pagesChapter 01Iqbal Uddin KhanPas encore d'évaluation

- Lab 00Document4 pagesLab 00Iqbal Uddin KhanPas encore d'évaluation

- Embedded Systems and Rasp-Pi 1 Per 1Document36 pagesEmbedded Systems and Rasp-Pi 1 Per 1Iqbal Uddin KhanPas encore d'évaluation

- Lec - 6 CodesDocument2 pagesLec - 6 CodesIqbal Uddin KhanPas encore d'évaluation

- Lecture - Week 1Document12 pagesLecture - Week 1Iqbal Uddin KhanPas encore d'évaluation

- Basic Electronics (CS) Fall 2014Document3 pagesBasic Electronics (CS) Fall 2014Iqbal Uddin KhanPas encore d'évaluation

- Linux PocketDocument181 pagesLinux PocketDebraj PalPas encore d'évaluation

- Intro To Linux - v1Document16 pagesIntro To Linux - v1Iqbal Uddin KhanPas encore d'évaluation

- Assignment - 5Document2 pagesAssignment - 5Iqbal Uddin KhanPas encore d'évaluation

- RE - Assign - IDocument7 pagesRE - Assign - IIqbal Uddin KhanPas encore d'évaluation

- An Overview of Multi - Processor InterconnectsDocument10 pagesAn Overview of Multi - Processor InterconnectsIqbal Uddin KhanPas encore d'évaluation

- Hamdard University Express Bus Service - HEBS - SRS - RE FinalDocument19 pagesHamdard University Express Bus Service - HEBS - SRS - RE FinalIqbal Uddin KhanPas encore d'évaluation

- Lab 09 - ACN - IPDocument3 pagesLab 09 - ACN - IPIqbal Uddin KhanPas encore d'évaluation

- RE - Assignment - IIDocument9 pagesRE - Assignment - IIIqbal Uddin KhanPas encore d'évaluation

- Lab 07 - TCPDocument6 pagesLab 07 - TCPIqbal Uddin Khan100% (1)

- Examining The Science Behind - Water CarDocument4 pagesExamining The Science Behind - Water CarIqbal Uddin KhanPas encore d'évaluation

- Lab 5 DNSDocument9 pagesLab 5 DNSIqbal Uddin KhanPas encore d'évaluation

- Lab 04 ACN DR ArshadDocument5 pagesLab 04 ACN DR ArshadIqbal Uddin KhanPas encore d'évaluation

- Advanced Computer Networks - DR ArshadDocument3 pagesAdvanced Computer Networks - DR ArshadIqbal Uddin KhanPas encore d'évaluation

- An Over View of Body Area NetworkDocument11 pagesAn Over View of Body Area NetworkIqbal Uddin KhanPas encore d'évaluation

- A Chunk-Based Distributed File System For Supporting Multimedia Communication - SummaryDocument2 pagesA Chunk-Based Distributed File System For Supporting Multimedia Communication - SummaryIqbal Uddin KhanPas encore d'évaluation

- WBAN - Presentation - Wireless NetworksDocument46 pagesWBAN - Presentation - Wireless NetworksIqbal Uddin KhanPas encore d'évaluation

- M.Phil SyllabusDocument15 pagesM.Phil Syllabusnanobala15Pas encore d'évaluation

- 8051 NotesDocument61 pages8051 Notessubramanyam62Pas encore d'évaluation

- EE2354 Question Bank BESTDocument18 pagesEE2354 Question Bank BESTGokul ChandrasekaranPas encore d'évaluation

- 8-Bit MTP Micro-ControllerDocument33 pages8-Bit MTP Micro-ControllerSoumya Jyoti DanPas encore d'évaluation

- Embedded Systems IntroductionDocument44 pagesEmbedded Systems IntroductionGokulSubramanianPas encore d'évaluation

- C 8051 F 04 XDocument328 pagesC 8051 F 04 XIna SestacovschiPas encore d'évaluation

- Ec302T Microprocessor and MicrocontrollerDocument6 pagesEc302T Microprocessor and Microcontrollergoons7777Pas encore d'évaluation

- Microcontroller Lab ManualDocument38 pagesMicrocontroller Lab Manualharshitha100% (1)

- Accident Identification Using GPS and GSM TechnologyDocument94 pagesAccident Identification Using GPS and GSM TechnologyGururaj Hegde78% (9)

- Micro Controller Based Heartbeat Monitoring System: Project Reference No.: 39S - Be - 0609Document4 pagesMicro Controller Based Heartbeat Monitoring System: Project Reference No.: 39S - Be - 0609vaishnaviPas encore d'évaluation

- AT89C51 MicrocontrollerDocument8 pagesAT89C51 MicrocontrollerSaroj TimsinaPas encore d'évaluation

- E 05 B 040Document7 pagesE 05 B 040Tariq Zuhluf100% (2)

- Unit-4.ppt MicrocontrollerDocument74 pagesUnit-4.ppt MicrocontrollerVigneshwaran KandaswamyPas encore d'évaluation

- ds12887 RTC InterfacingDocument11 pagesds12887 RTC InterfacingJay TiwariPas encore d'évaluation

- 8051 Architecture (Enhanced) OctY09Document59 pages8051 Architecture (Enhanced) OctY09Santhoshreddy GogulaPas encore d'évaluation

- MC PLC Lab 2013Document37 pagesMC PLC Lab 2013sivaeeinfoPas encore d'évaluation

- A51 Assembler A251 Assembler: Macro Assemblers For The 8051 and MCS 251 MicrocontrollersDocument245 pagesA51 Assembler A251 Assembler: Macro Assemblers For The 8051 and MCS 251 Microcontrollersbinhnhi0007Pas encore d'évaluation

- 8051 Microcontroller Book by Ayala PDFDocument3 pages8051 Microcontroller Book by Ayala PDFAvi AvinashPas encore d'évaluation

- Four Quadrant DC Motor Control SystemDocument41 pagesFour Quadrant DC Motor Control SystemSaravanan Viswakarma50% (2)

- Periyar University Latest Syllabus M.sc-Physhics - 2017Document78 pagesPeriyar University Latest Syllabus M.sc-Physhics - 2017பிரபாகரன் பிரபாகரன்Pas encore d'évaluation

- Sac c868Document82 pagesSac c868greemaxPas encore d'évaluation

- 08.601 MBSD Module 1Document39 pages08.601 MBSD Module 1Assini HussainPas encore d'évaluation

- Microprocessor and Microcontroller Laboratory AssignmentDocument16 pagesMicroprocessor and Microcontroller Laboratory AssignmentKote Bhanu PrakashPas encore d'évaluation

- 1 Intro and IO Ports.Document10 pages1 Intro and IO Ports.raheelPas encore d'évaluation

- Microprocessors 1: The 8051 Instruction SetDocument28 pagesMicroprocessors 1: The 8051 Instruction SetnagasaikiranPas encore d'évaluation

- Practical No3 (A) (B) (C) (D)Document16 pagesPractical No3 (A) (B) (C) (D)Amish Rajesh MashruPas encore d'évaluation

- Control Transfer Instructions and Programming Using 8051 MicrocontrolleDocument72 pagesControl Transfer Instructions and Programming Using 8051 MicrocontrollePujaChaudhuryPas encore d'évaluation

- AN448 - Determining Baud Rates For 8051 UARTsDocument3 pagesAN448 - Determining Baud Rates For 8051 UARTsAngie RahmawatiePas encore d'évaluation

- EC2308 Microprocessor and Microcontroller Lab Manual ArunDocument65 pagesEC2308 Microprocessor and Microcontroller Lab Manual Arunkarthick0580% (1)

- Microcontroller Based Design: Muhammad Usman RafiqueDocument107 pagesMicrocontroller Based Design: Muhammad Usman RafiqueHammadMehmoodPas encore d'évaluation