Académique Documents

Professionnel Documents

Culture Documents

ALU - Arithmetical and Logical Unit

Transféré par

OlwenntaronCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

ALU - Arithmetical and Logical Unit

Transféré par

OlwenntaronDroits d'auteur :

Formats disponibles

Laboratrio de Sistemas, Processadores e Perifricos

Projeto da Unidade Lgica-Aritmtica

Prof. Julio C. D. de Melo DELT/EEUFMG

1.

Introduo

A Unidade Lgica-Aritmtica (ULA) de um processador o mdulo responsvel pela realizao de todas as

operaes lgicas e aritmticas definidas pelo seu conjunto de instrues. Entre as operaes lgicas esto AND,

OR, XOR e NOT, alm daquelas relativas ao deslocamento esquerda ou direita do contedo de um registrador.

As trs primeiras so binrias (operam sobre dois registradores) e as de deslocamento e o NOT so unrias (operam

sobre um nico registrador). Entre as operaes aritmticas, a adio e a subtrao esto presentes em todos os

processadores, sendo as operaes de multiplicao e diviso restritas aos processadores de maior desempenho.

Outras operaes incluem a comparao, realizada atravs da subtrao sem atualizao de registradores mas

refletindo o resultado nos sinalizadores.

O resultado de uma operao na ULA tipicamente armazenado num registrador mas pode ser descartado se o

que se deseja apenas sinalizar a condio resultante da operao tal como, por exemplo, se a adio de dois

nmeros produz um resultado positivo, negativo ou nulo. A condio armazenada em sinalizadores (flags), que

refletem condies tais como:

zero: o resultado da operao na ULA produziu o valor 0 (zero)

positivo: idem, produziu um valor positivo (formato complemento-de-2)

negativo: idem, produziu um valor negativo (formato complemento-de-2)

estouro: idem, produziu um valor que ultrapassa o limite mximo (positivo ou negativo) para nmeros em

formato complemento-de-2

vai-um (carry): idem, produziu um vai-um final do bit mais significativo (formato sem sinal)

paridade: idem, indica se o nmero de 1s no resultado par ou no

Na arquitetura MIPS, como explicado no livro-texto, decidiu-se implementar apenas um sinalizador, o de zero,

sendo os outros derivados dele em funo da realizao de outras operaes entre os operandos.

2. Objetivos

O objetivo desta aula prtica a implementao, simulao e teste de uma ULA que implemente as seguintes

operaes lgicas e aritmticas:

AND, OR, NOR: AND, OR e NOR lgicos, entre dois operandos de 32 bits

ADD: adio de dois operandos de 32 bits no formato complemento-de-2

SUB: subtrao de dois operandos de 32 bits no formato complemento-de-2

SLT: comparao entre dois operandos de 32 bits no formato complemento-de-2

O projeto lgico dever ser definido atravs da linguagem VHDL, j estudada nas disciplinas de sistemas

digitais. No site da disciplina, h vrias referncias sobre a linguagem. Aps a entrada do projeto lgico, ele dever

ser compilado e simulado, para verificao do seu correto funcionamento.

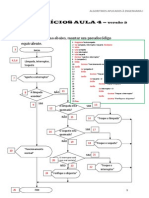

3. Parte Experimental

A parte experimental consiste em testar o projeto de uma ULA que suporte um subconjunto das instrues

definidas para o processador MIPS. Para isto, conforme descrito no captulo 4 do livro-texto (figura 4.12), sero

implementadas as funes dadas na tabela abaixo e que faro uso da ALU em seu processamento:

opcode

ALUOp

Operation

funct

ALU function

ALU control

lw

00

load word

XXXXXX

add

0010

sw

00

store word

XXXXXX

add

0010

beq

01

branch equal

XXXXXX

subtract

0110

R-type

10

add

100000

add

0010

R-type

10

subtract

100010

subtract

0110

R-type

10

AND

100100

AND

0000

R-type

10

OR

100101

OR

0001

R-type

10

set-on-less-than

101010

set-on-less-than

0111

3.1. Atividade 1

Nesta atividade, voc dever verificar o funcionamento do projeto da ULA atravs de sua simulao. Para isto,

proceda como descrito a seguir:

Curso de Engenharia Eltrica da UFMG Sistemas, Processadores e Perifricos

3.

Crie um novo projeto: FileNew Project Wizard. Clique em Next.

Selecione o seu diretrio de trabalho e entre com o nome ULA. Selecione o arquivo com o nome

ULA.vhd, clique em Add e em Next.

Selecione a famlia Cyclone II e o dispositivo do kit DE2 (EP2C35672C6N) e clique em Next e Finish.

4.

5.

Compile o projeto selecionando ProcessingStart Compilation ou o cone na barra de ferramentas.

Simule o projeto no ModelSim utilizando o arquivo ULA_tb.vhd, que realiza a operao 1+1 = 2.

1.

2.

Verifique o funcionamento da ULA alterando o arquivo de testes de forma a gerar valores diferentes para os

operandos A e B, bem como alterando a funo F.

3.2. Atividade 2

A atividade 2 consiste em verificar o funcionamento da ULA no kit DE2. Como o projeto da ULA ser, mais

tarde, incorporado ao projeto do processador, ele ser considerado como um COMPONENTE de um projeto

maior, ilustrando a natureza hierrquica dos projetos em VHDL. Para isto, os operandos A e B viro das chaves

SW(6..0) e SW(13..7), respectivamente, e a funo F ser definida pelas chaves SW(17..14). A sada dever ser ligada

aos LEDs vermelhos LEDR(6..0) e LEDG(0). Lembre-se de importar o arquivo de atribuies do kit DE2

(AssignmentsImport Assignments e selecione DE2_pin_assignments.csv)

Para isso, siga os passos:

1. Crie um novo projeto, no mesmo diretrio, com o nome ULA_DE2, para enfatizar que esta verso

para testes no kit. Ignore o aviso de que j h um projeto no mesmo diretrio.

2. Crie um arquivo em VHDL com a mesma estrutura do projeto da ULA, exceto que nele no haver

qualquer cdigo mas simplesmente uma conexo entre portas (este um conceito conhecido como

encapsulamento). Neste novo arquivo, para suas entradas e sadas utilize os nomes dos pinos

correspondentes a chaves e LEDs como descrito acima.

3. Adicione um componente ULA arquitetura deste novo arquivo, copiando a entidade ULA e

renomeando entity para component e a sequncia end ULA para end component

4. Faa o mapeamento de portas de forma que os sinais equivalentes nos dois projetos estejam

conectados. Exemplo: ... A => SW(6 downto 0), ... No caso, A o sinal que est associado ao

operando A no projeto da ULA e SW ser a entrada do projeto ULA_DE2 conectada s chaves SW[6]

a SW[0].

5. Compile o projeto e teste-o no kit.

3.3. Atividade 3

A atividade 3 consiste em adicionar, ao cdigo da atividade 2, as seguintes funes ULA: OR, NOR, SUB e

LUI, sendo esta ltima definida como no conjunto de instrues do MIPS. Para testar seu projeto, modifique o

arquivo ULA_tb.vhd e simule-o no ModelSim.

Cdigo da atividade 1: Unidade Lgica-aritmtica (ULA)

-- @2012 - Prof. Julio C. D. de Melo - DELT/EEUFMG

-- Sistemas, Processadores e Perifricos

-- Projeto do processador uMIPS: Unidade Lgica-Aritmtica

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

-- ULA

entity ULA is

port(

A, B : in std_logic_vector (31 downto 0);

F : in std_logic_vector(3 downto 0);

Y : out std_logic_vector (31 downto 0);

Z: out std_logic

);

end ULA;

-----

Entradas A e B da ULA

Controle da ULA

Sada da ULA

flag de zero

architecture beh of ULA is

signal saida : std_logic_vector (31 downto 0);

signal AX, BX : std_logic_vector (31 downto 0);

signal FN : std_logic_vector (3 downto 0);

begin

FN <= F;

AX <= A;

BX <= B;

process (AX, BX, FN)

Prof. Julio C. D. de Melo DELT/EEUFMG - 2

Curso de Engenharia Eltrica da UFMG Sistemas, Processadores e Perifricos

begin

case FN is

when "0000"=>

saida <= AX AND BX;

-- AND lgico

when "0010" =>

-- adio

saida <= std_logic_vector (signed (AX) + signed (BX));

when "0111" =>

-- SLT

if (signed (AX) < signed (BX)) then

saida <= x"00000001";

else

saida <= x"00000000";

end if;

when others => saida <= (others => '0');

end case;

-- o que no foi definido ainda

end process;

Y <= saida;

Z <= '1' when (saida = x"00000000") else '0';

-- resultado

-- flag de zero

END beh;

Arquivo de teste da Unidade Lgica-aritmtica (ULA)

-- @2012 - Prof. Julio C. D. de Melo - DELT/EEUFMG

-- Sistemas, Processadores e Perifricos

-- Projeto do processador uMIPS: Arquivo de teste da Unidade Lgica-Aritmtica

-- Declarao de bibliotecas

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

-- Entidade principal

entity ULA_tb is

port(

saida : out std_logic_vector (31 downto 0);

flag : out std_logic

);

end ULA_tb;

architecture unica of ULA_tb is

component ULA is

port(

A, B : in std_logic_vector (31 downto 0);

F : in std_logic_vector(3 downto 0);

Y : out std_logic_vector (31 downto 0);

Z: out std_logic

);

end component;

-- Sada da ULA

-- flag de zero

-----

Entradas A e B da ULA

Controle da ULA

Sada da ULA

flag de zero

signal AX, BX : std_logic_vector (31 downto 0);

signal FN : std_logic_vector (3 downto 0);

begin

teste: ULA

port map (

A => AX,

B => BX,

F => FN,

Y => saida,

Z => flag

);

process

begin

wait for 1 ns;

AX <= X"00000001";

BX <= X"00000001";

FN <= "0010";

wait;

end process;

end unica;

-- A = 1

-- B = 1

-- F = adio => sada = 2 e flag = 0

Prof. Julio C. D. de Melo DELT/EEUFMG - 3

Vous aimerez peut-être aussi

- Modelo Curriculo para Alunos - CópiaDocument2 pagesModelo Curriculo para Alunos - CópiawilliamtgaPas encore d'évaluation

- Curso WorkflowDocument64 pagesCurso Workflowthiarllisb100% (2)

- Aprendizagem significativa AusubelDocument2 pagesAprendizagem significativa AusubelAndré TavaresPas encore d'évaluation

- Baixar Arquivos SWFDocument2 pagesBaixar Arquivos SWFRogerio VilelaPas encore d'évaluation

- Projeto 4 - 2016 - 1Document2 pagesProjeto 4 - 2016 - 1OlwenntaronPas encore d'évaluation

- ELT010 Instrumentação IndustrialDocument3 pagesELT010 Instrumentação IndustrialOlwenntaronPas encore d'évaluation

- Quartus IIDocument5 pagesQuartus IIOlwenntaronPas encore d'évaluation

- Introduction To VHDLDocument8 pagesIntroduction To VHDLOlwenntaronPas encore d'évaluation

- ALU - Arithmetical and Logical UnitDocument3 pagesALU - Arithmetical and Logical UnitOlwenntaronPas encore d'évaluation

- Excel - A Folha de Calculo Como Ferramenta de Apoio Ao Trabalho Do ProfessorDocument6 pagesExcel - A Folha de Calculo Como Ferramenta de Apoio Ao Trabalho Do ProfessorRita TorrePas encore d'évaluation

- Alguns Atalhos Úteis Do Corel DrawDocument6 pagesAlguns Atalhos Úteis Do Corel DrawJulio SilvaPas encore d'évaluation

- Análise Global Do Programa de Prevenção de Riscos Ambientais2Document10 pagesAnálise Global Do Programa de Prevenção de Riscos Ambientais2arlenemoreira50% (2)

- Livro Eletromecânica FBEDocument291 pagesLivro Eletromecânica FBEandreia_lopes2398Pas encore d'évaluation

- ManualPrestador Demonstrativos PDFDocument29 pagesManualPrestador Demonstrativos PDFrodabcPas encore d'évaluation

- Circuitos Lógicos TTLDocument7 pagesCircuitos Lógicos TTLGabriela ShimaPas encore d'évaluation

- Livro Introdução A Visão Computacional Com Python e OpenCVDocument46 pagesLivro Introdução A Visão Computacional Com Python e OpenCVIsabela LopesPas encore d'évaluation

- Jogos 2D: Estilos e FormatosDocument8 pagesJogos 2D: Estilos e FormatosJosemar JuniorPas encore d'évaluation

- Desligar CapsDocument7 pagesDesligar CapsDiscípulo Paulo HenriquePas encore d'évaluation

- Automação Industrial - LivroDocument117 pagesAutomação Industrial - Livrokaka43Pas encore d'évaluation

- Está A Brincar, Sr. Feynman! - Richard P. FeynmanDocument281 pagesEstá A Brincar, Sr. Feynman! - Richard P. FeynmanbaixarlivrosnoscribPas encore d'évaluation

- RPC - Código em Linguagem CDocument5 pagesRPC - Código em Linguagem CAlessandroPas encore d'évaluation

- Guia para ArtCamDocument7 pagesGuia para ArtCamadilson_iaPas encore d'évaluation

- TI-Nspire CASDocument289 pagesTI-Nspire CASbrunei952352Pas encore d'évaluation

- Introdução a um Sistema OperativoDocument3 pagesIntrodução a um Sistema OperativoHugo AmaralPas encore d'évaluation

- Apostila Prática Autocad 2D PDFDocument30 pagesApostila Prática Autocad 2D PDFalemaneto1056100% (1)

- HardwareDocument10 pagesHardwareademaralvePas encore d'évaluation

- Projeto - Sistema de Controle de Clínica MédicaDocument168 pagesProjeto - Sistema de Controle de Clínica MédicaRonny MartinsPas encore d'évaluation

- Curso de Marketing Digital OnlineDocument3 pagesCurso de Marketing Digital OnlineCurso de E-CommercePas encore d'évaluation

- Exercicios Pseudocodigo e Fluxograma Aula 4 v3 GabaritoDocument7 pagesExercicios Pseudocodigo e Fluxograma Aula 4 v3 GabaritoRonaldo RoquePas encore d'évaluation

- Software para Estudo de Viabilidade, Aproveitamento Hidrelétrico, Cadastro Multifinalitário.Document18 pagesSoftware para Estudo de Viabilidade, Aproveitamento Hidrelétrico, Cadastro Multifinalitário.MARIA NELY ALVARENGA LIMAPas encore d'évaluation

- Como criar formato personalizado no AutoCADDocument8 pagesComo criar formato personalizado no AutoCADLotharSchmidtPas encore d'évaluation

- Criptoativos Dados Abertos 03112022Document90 pagesCriptoativos Dados Abertos 03112022Rodrix DigitalPas encore d'évaluation

- Funções avançadas Excel previsão vendas agrícolaDocument9 pagesFunções avançadas Excel previsão vendas agrícolaNicholas Vinicius SilvaPas encore d'évaluation

- AclsDocument3 pagesAclsAndré Camargos VazPas encore d'évaluation

- Função Fork (Ubuntu)Document6 pagesFunção Fork (Ubuntu)Raphael FreitasPas encore d'évaluation