Académique Documents

Professionnel Documents

Culture Documents

Design of (7, 4) Hamming Encoder and Decoder Using VHDL

Transféré par

UsmanSSCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Design of (7, 4) Hamming Encoder and Decoder Using VHDL

Transféré par

UsmanSSDroits d'auteur :

Formats disponibles

www.futminna.edu.

ng

www.seetconf.futminna.edu.ng

Design of (7, 4) Hamming Encoder and Decoder Using VHDL

Usman Sammani Sani1*, Ibrahim Haruna Shanono2

1,2

Department of Electrical Engineering,

Bayero University, Kano, P.M.B. 3011, Nigeria

Corresponding Authors Email: usmanssani@live.com, Phone Number: 08025791503

ABSTRACT

Hamming code is one of the commonest codes used in the protection of information from error. It takes a block of k input

bits and produce n bits of codeword. This work presents a way of designing (7, 4) Hamming encoder and decoder using

Very High Speed Integrated Circuit Hardware Description Language (VHDL). The encoder takes 4 bits input data and

produces a 7 bit codeword. The encoder was designed through the usual generator matrix multiplication while in the

decoder design the computation of the syndrome vector was ignored. Meanwhile, the different states that can represent a

particular input were calculated and the decoder was designed to identify each codeword representing a particular input.

Results have shown that the method is also reliable.

Keywords: Hamming, VHDL, Encoder, Decoder, Syndrome vector.

single bit error (Peter, 2002) and are mostly used in

Random Access Memory for error correction

purpose (Mistri et al, 2014).

1.

INTRODUCTION

Hamming codes are used in error detection and

correction in digital communication circuitries.

Hamming codes belong to the class of block codes

which are codes that work on a block of bits rather

than individual bits of data. A block code

designated by (n, k) means k bits of input data is

used in producing a codeword, C with n bits of data

(Edward and David, 1994), (Richard, 2003). The n

k bits added are called parity check bits. Thus a

(7, 4) Hamming encoder produces 7 bits from 4

bits and the codeword has 4 parity check bits.

Hamming codes are usually generated by

multiplying the input block, x by a generator

matrix, G (John, 2007). Digital communications

involves 0s and 1s. Both the generator matrix and

the input matrix are in form of 0s and 1s. The

addition involved during the multiplication of the

two matrices is modulo two addition (Edward

and David, 1994). For example a (7, 4) Hamming

code has the generator matrix

(3)

For a codeword C,

Z = Hr

(4)

In this work, a (7, 4) Hamming encoder and

decoder is designed using Very High Speed

Integrated Circuit Hardware Description Language

(VHDL). VHDL is a programming language that

became popular in the 1990s. It is similar to other

high level programming languages such as C but in

its own case it doesnt have a compiler but has a

synthesizer. The synthesizer translates the written

source code into an equivalent hardware described

by the source code. The process of this translation

is called synthesis (Enoch, 2006).

2.

METHODOLOGY

The G and H matrices above were used in the

process. The encoder and decoder design will be

discussed separately.

2.1

Encoder Design

The encoder has a generator matrix in which it

produces the codewords. The codeword is a vector

with seven bits. Each bit is obtained by multiplying

the input matrix by a column in G as shown below:

C(1) = x(1)

C(2) = x(2)

C(3) = x(3)

C(4) = x(4)

C(5) = x(1) XOR x(2) XOR x(4)

(1)

For an input x,

C = Gx

(2)

Hamming codes are decoded by multiplying the

codeword received, r by a parity check matrix, H to

see whether there is an error or not. The resulting

matrix is called a syndrome vector, Z. If Z is zero,

it means there is no error while if Z is not zero,

then the position of the bit that is in error is

indicated by Z. Hamming codes can only correct a

!"

www.futminna.edu.ng

www.seetconf.futminna.edu.ng

C(6) = x(1) XOR x(3) XOR x(4)

C(7) = x(2) XOR x(3) XOR x(4)

11

12

13

14

15

16

C(n) stands for the nth bit in the codeword and x(n)

stands for the nth bit of the input bits. The VHDL

code was then developed and synthesized using

XILINX ISE 10.1 software.

Table 1. Codewords for 4 input data.

S/N X

C

1

0000 0000000

2

0001 0001111

3

0010 0010011

4

0011 0011100

5

0100 0100101

6

0101 0101010

7

0110 0110110

8

0111 0111001

9

1000 1000110

10

1001 1001001

x

0000

2.

0001

3.

0010

4.

0011

1010101

1011010

1100011

1101100

1110000

1111111

Hamming codes can correct a single error. So in

this work, bits of a codeword representing a

particular input were altered one by one and each

new codeword represents that same input.

Therefore in this case the need of computing the

syndrome vector and later on correcting the bit in

error has been abandoned, unlike in (Saleh, 2015),

where the syndrome vector was computed. This

method also differs from that of (Hosamani and

Karne, 2014), in which the parity bits were inserted

directly without the use of a defined generator

matrix at the encoder and then the received parity

bits were also computed at the decoder. Thus in

our own case, each of the 16 input combinations

has 8 different codewords representing it. The

whole seven bits possible combinations of

codewords has thus been assigned the correct input

representing it (i.e. 27 = (16 x 8) = 128). The table

below shows the different combinations of

codewords and there corresponding inputs.

2.2

Decoder Design

For restoring the original message, the codewords

corresponding to the 16 possible combinations of

input were calculated using some Matlab codes.

The results of the 16 combinations of 4 bit input

data resulted in the table below:

S/N

1.

1010

1011

1100

1101

1110

1111

Table 2. Codewords extension of 4 bits input.

1011100

0111100

0001100

0010100

0011000

0011110

0011101

5.

0100 0100101

1100101

0000101

0110101

0101101

0100001

0100111

0100100

6.

0101 0101010

1101010

0001010

0111010

0100010

0101110

0101000

0101011

7.

0110 0110110

1110110

0010110

C

0000000

1000000

0100000

0010000

0001000

0000100

0000010

0000001

0001111

1001111

0101111

0011111

0000111

0001011

0001101

0001110

0010011

1010011

0110011

0000011

0011011

0010111

0010001

0010010

0011100

!#

www.futminna.edu.ng

www.seetconf.futminna.edu.ng

0100110

0111110

0110010

0110100

0110111

8.

9.

10.

11.

12.

0111

1000

1001

1010

1011

0111001

1111001

0011001

0101001

0110001

0111101

0111011

0111000

1000110

0000110

1100110

1010110

1001110

1000010

1000100

1000111

1001001

0001001

1101001

1011001

1000001

1001101

1001011

1001000

1010101

0010101

1110101

1000101

1011101

1010001

1010111

1010100

1011010

13.

1100

14.

1101

15.

1110

16.

1111

Codes were also written in VHDL to describe the

decoder.

RESULTS

3.

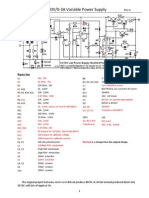

Figure 1. Register transfer level of the encoder.

!$

0011010

1111010

1001010

1010010

1011110

1011000

1011011

1100011

0100011

1000011

1110011

1101011

1100111

1100001

1100010

1101100

0101100

1001100

1111100

1100100

1101000

1101110

1101101

1110000

0110000

1010000

1100000

1111000

1110100

1110010

1110001

1111111

0111111

1011111

1101111

1110111

1111011

1111101

1111110

www.futminna.edu.ng

www.seetconf.futminna.edu.ng

Figure 2. Component view of the encoder

Figure 3. Register transfer level of the decoder

Figure 4. Component view of the Decoder

Hosamani R., Karne A.S., design and Implementation of

Hamming Code on FPGA Using Verilog, International

journal of Engineering and Advanced technology, Vol.4,

Issue 2, 2014, pp 181-184.

5.

CONCLUSION

The paper has presented a way of designing (7, 4)

Hamming encoder and decoder using VHDL. The encoder

was designed the normal way while some modifications

were made in the decoder design that avoided the

computation of a syndrome vector. Results have shown

how VHDL simplifies the design of digital hardware and

how the design procedure is effective. The same process

can be used in the design of any Hamming encoder and

decoder. The designed circuits can be used in places they

would be applicable or even be left as trainers for students

to understand the concept of Hamming encoding and

decoding. Thus several digital logic circuits meant for

experiment could be designed so that they can be used on a

single target device such as a Field Programmable Gate

Array. This reduces the cost of setting up a laboratory.

John P., Masoud S., Digital Communications, McGrawHill, 2007, pp 413-418.

Peter S., Error Control Coding; from theory to practice,

John Wiley and Sons ltd, 2002, pp 6769.

Mistri R. K. et al, Reduced Area and Improved Delay

Module Design of 16 bit Hamming Codec Using HSPICE

22nm Technology Based on GDI Technique, international

Journal of Scientific and Research publications, vol. 4,

Issue 7, 2014, pp 1-6.

Richard E. B., Algebraic Codes for Data Transmission,

Cambridge University Press, 2003, pp54.

REFERENCES

Edward A. L., David G.M., Digital Communication,

Kluwer Academic Publishers, 1994, pp613-617.

Saleh A.H., Design of Hamming Encoder and Decoder

Circuits for (64,7) Code and (128,8) Code Using VHDL,

Journal of Scientific and Engineering Research, Vol. 4,

Issue 1, 2015, pp 1-4.

Enoch O. H., Digital Logic and Microprocessor Design

with VHDL, La Sierra University, 2006, pp 23-26.

!%

Vous aimerez peut-être aussi

- GuidewireClaimCenter Performance TestPlanDocument18 pagesGuidewireClaimCenter Performance TestPlanshanthan117Pas encore d'évaluation

- Boiler MaintenanceDocument144 pagesBoiler Maintenanceaziz100% (2)

- RPVP Puerto PrincesaDocument8 pagesRPVP Puerto PrincesaRanny LomibaoPas encore d'évaluation

- 1170 Imagerunner Advance DX 4700 Series PC r0 200228Document180 pages1170 Imagerunner Advance DX 4700 Series PC r0 200228Marco Antonio Valverde MarinPas encore d'évaluation

- Solve Process Problems Quickly with Simulation TrainingDocument6 pagesSolve Process Problems Quickly with Simulation TrainingAnonymous qPt2MHzXTPas encore d'évaluation

- Binary Decoder and Encoder Circuit Diagram and Truth TablesDocument8 pagesBinary Decoder and Encoder Circuit Diagram and Truth TablessankulsybcaPas encore d'évaluation

- Interfacing of 4x4 Matrix Keyboard and 4 Digit 7 Segment Display - Free Electronic Projects & 8085 ProjectsDocument4 pagesInterfacing of 4x4 Matrix Keyboard and 4 Digit 7 Segment Display - Free Electronic Projects & 8085 ProjectsSaideep Narasimhan100% (1)

- Practice Questions On Huffman Encoding - GeeksforGeeksDocument6 pagesPractice Questions On Huffman Encoding - GeeksforGeeksZohaib Hasan KhanPas encore d'évaluation

- LDPC - Low Density Parity Check CodesDocument6 pagesLDPC - Low Density Parity Check CodespandyakaviPas encore d'évaluation

- Design of Hamming Code Using VerilogDocument5 pagesDesign of Hamming Code Using VerilogDevanshu Anand100% (1)

- Encoder and DecoderDocument17 pagesEncoder and Decoderjiremy noriegaPas encore d'évaluation

- Final DE + VHDL Lab B18EC3080 As On 31 July 2019Document191 pagesFinal DE + VHDL Lab B18EC3080 As On 31 July 2019Vishal AtharPas encore d'évaluation

- Information Theory & Source CodingDocument14 pagesInformation Theory & Source CodingmarxxPas encore d'évaluation

- Convolutional Coding PresentationDocument23 pagesConvolutional Coding PresentationTsega GetuPas encore d'évaluation

- Reed SolomonDocument72 pagesReed SolomonkalkamPas encore d'évaluation

- Assignment 1Document8 pagesAssignment 1phyrdowsPas encore d'évaluation

- MP 8086 Lab Manual TRAINER KITDocument70 pagesMP 8086 Lab Manual TRAINER KITKavitha Subramaniam100% (1)

- Convolutional Codes PuncturingDocument13 pagesConvolutional Codes PuncturinghunterdlrPas encore d'évaluation

- Lab Assignment 3Document3 pagesLab Assignment 3toolz100% (1)

- Reed SolomonDocument18 pagesReed Solomonrampravesh kumarPas encore d'évaluation

- Digital Logic Design CourseDocument1 pageDigital Logic Design CourseVinay PasiPas encore d'évaluation

- Information TheoryDocument46 pagesInformation TheoryAMIE Study Circle, Roorkee100% (1)

- Microprocessors & Interfacing Lab ManualDocument30 pagesMicroprocessors & Interfacing Lab Manualjeravi84100% (1)

- DLD LAB Sessional 2Document10 pagesDLD LAB Sessional 2AitazazPas encore d'évaluation

- Reed SolomonDocument149 pagesReed SolomoncalidorPas encore d'évaluation

- MC 8051 Lab Manual 2012Document163 pagesMC 8051 Lab Manual 2012Harieswar ReddyPas encore d'évaluation

- Code No: 45088Document8 pagesCode No: 45088SRINIVASA RAO GANTAPas encore d'évaluation

- The International Journal of Computer Game Development and Education (CGDEIJ)Document1 pageThe International Journal of Computer Game Development and Education (CGDEIJ)Anonymous wswGZWOApPas encore d'évaluation

- Predictive coding: Lossless and lossy approaches in 40 charactersDocument5 pagesPredictive coding: Lossless and lossy approaches in 40 charactersKrishanu ModakPas encore d'évaluation

- ECE3073 P4 Bus Interfacing Answers PDFDocument3 pagesECE3073 P4 Bus Interfacing Answers PDFkewancamPas encore d'évaluation

- M.Tech ES ARM LABDocument14 pagesM.Tech ES ARM LABdownloadscribdpdfPas encore d'évaluation

- Code Converters, Multiplexers and DemultiplexersDocument36 pagesCode Converters, Multiplexers and DemultiplexersJohn Oneil F. Quiambao0% (1)

- Computer Game Development and Education: An International Journal (CGDEIJ)Document1 pageComputer Game Development and Education: An International Journal (CGDEIJ)Anonymous wswGZWOApPas encore d'évaluation

- Convolutional CodesDocument26 pagesConvolutional CodesPiyush MittalPas encore d'évaluation

- HT12DDocument5 pagesHT12DBalasubramanian RajuPas encore d'évaluation

- Tiger SHARC ProcessorDocument36 pagesTiger SHARC ProcessorChintan PatelPas encore d'évaluation

- Chapter-5: Assembly Language Programming Using 8086 (16 Marks)Document55 pagesChapter-5: Assembly Language Programming Using 8086 (16 Marks)PRABHAKAR MOREPas encore d'évaluation

- Computer Graphics & Multimedia Lab (Etcs-257) : Experiment 1Document64 pagesComputer Graphics & Multimedia Lab (Etcs-257) : Experiment 1011S6Amit PandeyPas encore d'évaluation

- Cycle-I: Computer Communication Networks Lab Manual (18TE63), 2020-2021Document77 pagesCycle-I: Computer Communication Networks Lab Manual (18TE63), 2020-2021SHANTANU B SPas encore d'évaluation

- Subnetting Questions 1Document12 pagesSubnetting Questions 1smzohaibabbasPas encore d'évaluation

- Encoders and Decoders, Multiplexer, Tri-State InverterDocument25 pagesEncoders and Decoders, Multiplexer, Tri-State InverterRohit SainiPas encore d'évaluation

- Packed BCD To Unpacked BCDDocument5 pagesPacked BCD To Unpacked BCDRajveer JainPas encore d'évaluation

- VLSI Design: 2 To 4 DecoderDocument1 pageVLSI Design: 2 To 4 DecoderohgiggitygooPas encore d'évaluation

- Computer CodesDocument22 pagesComputer CodesAniqa AshrafPas encore d'évaluation

- STLD BitsDocument18 pagesSTLD BitsKornepati SureshPas encore d'évaluation

- Problem Set 2 - Solutions: C && C C && CDocument8 pagesProblem Set 2 - Solutions: C && C C && CpriyaPas encore d'évaluation

- BCD To 7 Segment Display ProjectnewDocument5 pagesBCD To 7 Segment Display ProjectnewSaeed Ali ShahaniPas encore d'évaluation

- Programming Assignment 1Document3 pagesProgramming Assignment 1Keshav AwasthiPas encore d'évaluation

- Rabin Cryptography and Implementation Using C Programming LanguageDocument19 pagesRabin Cryptography and Implementation Using C Programming Languageal-amin shohagPas encore d'évaluation

- Digital ClockDocument11 pagesDigital ClockAmiin Gadari100% (4)

- Question & Answer PDFDocument10 pagesQuestion & Answer PDFKalyan DasPas encore d'évaluation

- ECE3073 Computer Systems Practice Questions Bus InterfacingDocument2 pagesECE3073 Computer Systems Practice Questions Bus InterfacingkewancamPas encore d'évaluation

- CSE 231 Final - Summer 2021Document2 pagesCSE 231 Final - Summer 2021Sifat AnwarPas encore d'évaluation

- Comprehensive Assignments for DCDR (2161603) SubjectDocument4 pagesComprehensive Assignments for DCDR (2161603) SubjectShubhuPas encore d'évaluation

- Short Question EEDocument6 pagesShort Question EEAswini SamantarayPas encore d'évaluation

- Linear Codes: 3.1 BasicsDocument17 pagesLinear Codes: 3.1 BasicsBudianTo YangPas encore d'évaluation

- Programming Fundamentals Lab 08 (1D Array)Document5 pagesProgramming Fundamentals Lab 08 (1D Array)Ahmad AbduhuPas encore d'évaluation

- Homework Solutions 4Document4 pagesHomework Solutions 4Minh HoangPas encore d'évaluation

- aHR0cDovL2lzdC51anMuZWR1LmNuL2ZpbGUvYW5zd2Vycy5wZGY PDFDocument9 pagesaHR0cDovL2lzdC51anMuZWR1LmNuL2ZpbGUvYW5zd2Vycy5wZGY PDFThomas BoyerPas encore d'évaluation

- Theory QBankDocument7 pagesTheory QBankPrashant RautPas encore d'évaluation

- Viva Question Mux EXP 6Document3 pagesViva Question Mux EXP 6shrinidhi NPas encore d'évaluation

- Get Access To C100DEV Exam Dumps Now: Pass MongoDB Certified Developer Associate Exam With Full Confidence - Valid IT Exam Dumps QuestionsDocument5 pagesGet Access To C100DEV Exam Dumps Now: Pass MongoDB Certified Developer Associate Exam With Full Confidence - Valid IT Exam Dumps QuestionsMai PhuongPas encore d'évaluation

- Unit IiDocument61 pagesUnit IiNikhilSinghPas encore d'évaluation

- Design of (7, 4) Hamming Encoder and Decoder Using VHDL.: September 2015Document5 pagesDesign of (7, 4) Hamming Encoder and Decoder Using VHDL.: September 2015Maileth Rivero PalacioPas encore d'évaluation

- Ijert Ijert: FPGA Implementation of Orthogonal Code Convolution For Efficient Digital CommunicationDocument7 pagesIjert Ijert: FPGA Implementation of Orthogonal Code Convolution For Efficient Digital Communicationtariq76Pas encore d'évaluation

- Faia 345 Faia210413Document9 pagesFaia 345 Faia210413UsmanSSPas encore d'évaluation

- Variation of The Capacitance of Supercapacitors With Current and FrequencyDocument4 pagesVariation of The Capacitance of Supercapacitors With Current and FrequencyUsmanSSPas encore d'évaluation

- Design of A Digital Clock Using Very High Speed Ic Hardware Description LanguageDocument3 pagesDesign of A Digital Clock Using Very High Speed Ic Hardware Description LanguageUsmanSSPas encore d'évaluation

- An Equivalent Circuit of Carbon Electrode SupercapacitorsDocument9 pagesAn Equivalent Circuit of Carbon Electrode SupercapacitorsUsmanSSPas encore d'évaluation

- A Study On Carbon Electrode SupercapacitorsDocument8 pagesA Study On Carbon Electrode SupercapacitorsUsmanSSPas encore d'évaluation

- Designing An Artificial Neural Network Model For The Prediction of Kidney Problems Symptom Through Patient's Metal Behavior For Pre - Clinical Medical DiagnosticDocument4 pagesDesigning An Artificial Neural Network Model For The Prediction of Kidney Problems Symptom Through Patient's Metal Behavior For Pre - Clinical Medical DiagnosticUsmanSSPas encore d'évaluation

- Pump HydraulicsDocument5 pagesPump HydraulicsSiddharth Kharat100% (1)

- Android Tutorial - Broadcast ReceiversDocument15 pagesAndroid Tutorial - Broadcast ReceiversTrieu Ngo HuyPas encore d'évaluation

- LMS Adaptive FiltersDocument14 pagesLMS Adaptive FiltersalialibabaPas encore d'évaluation

- Core 3Document2 pagesCore 3RidhiPas encore d'évaluation

- Structural Analysis of Beams Using Moment Distribution MethodDocument15 pagesStructural Analysis of Beams Using Moment Distribution MethodneetuPas encore d'évaluation

- Freezing pipes-FPSDocument2 pagesFreezing pipes-FPSBinu SulochananPas encore d'évaluation

- Cisco SD-WAN Policy Architecture - Dana Yanch PDFDocument1 pageCisco SD-WAN Policy Architecture - Dana Yanch PDFEmilio PazPas encore d'évaluation

- 2020 Can Am Off Road - Apache Track Kits Leaflet - enDocument7 pages2020 Can Am Off Road - Apache Track Kits Leaflet - enNicolas VillamayorPas encore d'évaluation

- Explorador Ww90j6410cwec Version 02Document13 pagesExplorador Ww90j6410cwec Version 02Cristi PopescuPas encore d'évaluation

- Ieee 1346-1998Document45 pagesIeee 1346-1998pepitorodirguez100% (1)

- Oral and Practical Tests: MechanicDocument19 pagesOral and Practical Tests: MechanicHugo AlmeidaPas encore d'évaluation

- Narayana 10 01 24 SR Star Co Scmodel A, B&C Jee Main GTM 12n Key&sDocument10 pagesNarayana 10 01 24 SR Star Co Scmodel A, B&C Jee Main GTM 12n Key&sReddyPas encore d'évaluation

- Chapter 4.1 Basic Call Procedure (ED01 - 53 - EN)Document53 pagesChapter 4.1 Basic Call Procedure (ED01 - 53 - EN)quaderbtech06Pas encore d'évaluation

- Phase Diagrams IntroductionDocument76 pagesPhase Diagrams IntroductionGikiTopiPas encore d'évaluation

- Control Valve and Steam Line PDFDocument19 pagesControl Valve and Steam Line PDFRofi MuhammadPas encore d'évaluation

- Pure Chem p2 - 26pgDocument26 pagesPure Chem p2 - 26pgJhomer CrespoPas encore d'évaluation

- Gas Sensors: Jiturvi Chokshi ENPM-808BDocument27 pagesGas Sensors: Jiturvi Chokshi ENPM-808Banon_44955929Pas encore d'évaluation

- Mock Test Jee MainDocument142 pagesMock Test Jee MainAkash Ghosh0% (1)

- Chapter 15. Applications of Integration: Exercises 15.2Document2 pagesChapter 15. Applications of Integration: Exercises 15.2Donghyun AhnPas encore d'évaluation

- The B-GON Solution: To Mist EliminationDocument20 pagesThe B-GON Solution: To Mist EliminationDimitris Sardis LPas encore d'évaluation

- Physicaltestingofrubberrogerbrown2006 Book 150514103634 Lva1 App6892Document389 pagesPhysicaltestingofrubberrogerbrown2006 Book 150514103634 Lva1 App6892AbdelhamidHarratPas encore d'évaluation

- Transmission ErrorDocument7 pagesTransmission ErrorTapas JenaPas encore d'évaluation

- Emergency CallDocument6 pagesEmergency CallNugrohoPas encore d'évaluation

- Modified 0-30V - 0-3A Variable Power Supply - Rev.2Document2 pagesModified 0-30V - 0-3A Variable Power Supply - Rev.2Manuel Cereijo NeiraPas encore d'évaluation

- Optimal Design & Operation of RO Systems 3-Day SeminarDocument10 pagesOptimal Design & Operation of RO Systems 3-Day SeminarasankandessPas encore d'évaluation