Académique Documents

Professionnel Documents

Culture Documents

FFT - On FPGA

Transféré par

Suresh KumarTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

FFT - On FPGA

Transféré par

Suresh KumarDroits d'auteur :

Formats disponibles

Defence Science Journal, Vol. 63, No. 2, March 2013, pp. 210-213, DOI: 10.14429/dsj.63.

4266

2013, DESIDOC

Research Paper

Field-Programmable Gated Array Implementation of Split-Radix

Fast Fourier Transform for High Throughput

P.S. Sai Pavan, B. Renuka*, and B.Vinatha

Bharat Electronics Limited, Hyderabad500 076, India

*

E-mail: renukab@bel.co.in

Abstract

As the signal processing required in electronic warfare (EW) domain is complex and the sample rates to be handled

are very high, IP cores which are freely available are not of much use. A study of various fast fourier transform (FFT)

algorithms has been carried out and spit-radix FFT has been chosen to be implemented due to fewer multiplications3.

This algorithm is attractive to be implemented using field-programmable gated array (FPGA). This paper presents

split-radix FFT algorithm for implementation of 512-pt FFT on FPGA platform for EW applications. The algorithm

is such designed that it can achieve a throughput of up to 1500 MSPS. 512-pt SRFFT is implemented using parallel

pipelined architecture in order to maximize processing speed and thus achieve a throughput of 1500 MSPS with area

optimization. The pipeline structure is partitioned to balance the input throughput and to optimize the available FPGA

resources. The standard Cooley-Tukey radix-2 FFT algorithm requires N/2 log2 N (for N=512, 2304 multiplications)

multiplications and N log2 N additions where as radix-4 FFT requires N/2 log4 N multiplications and N log2 N

additions. The SRFFT presented in this paper has a multiplicative complexity of only about two-thirds that of the

radix-2 FFT, and is better than the radix-4 FFT or any higher power-of-two radix as well. The initial latency is

less than N clock cycles.

Keywords: Fast fourier transform, split-radix FFT, field-programmable gated array, commutator

1. Introduction

To perform frequency analysis on a discrete-time signal

x[n], it is necessary to convert the time-domain sequence to an

equivalent frequency-domain representation1. Fourier transform

X () gives the spectrum of the sequence x[n]. However, X()

is a continuous function of frequency and therefore is not a

computationally convenient representation of the sequence x[n].

For computational purposes, we consider the representation

of a sequence x[n] by samples of its spectrum X() Such a

frequency domain representation leads to the discrete fourier

transform (DFT), which is a powerful computational tool for

performing frequency analysis of discrete-time signals4.

The DFT plays an important role in many applications of

digital signal processing including linear filtering, correlation

analysis, and spectrum analysis. The number of complex

multiplication and addition operations required by simple

forms of both the discrete fourier transform (DFT) and inverse

discrete fourier transform (IDFT) is of the order of N2 where

N is the number of data points to calculate, each of which

requires N complex arithmetic operations. The fast fourier

transform (FFT) is another method for calculating the DFT.

The FFT decomposes the set of data to be transformed into a

series of smaller data sets and decomposesthosesmaller sets

into evensmallersets. There are two different approaches to

find DFT of a sequence:

(1) Divide and conquer approach.

(2) Linear filtering approach.

In the former approach, a DFT of size N, where N is a

composite number, is reduced to computation of smaller DFTs

from which the larger DFT is computed. FFT algorithms

(Radix-2, Radix-4 and Split Radix) fall into this category. The

latter approach is based on linear filtering operation on the

data. Two algorithms, the Goertzel algorithm and the chirptransform algorithm compute the DFT via linear filtering of

the data sequence2.

In this paper, 512-pt Split Radix FFT (SRFFT)

implementation is presented. SRFFT algorithms exploit both

radix-2 and radix-4 decomposition in the same FFT algorithm to

reduce the number of multiplications. Even numbered samples

are implemented using Radix-2, where as odd numbered

samples are implemented with Radix-4 FFT algorithms4.

2. FFT Algorithm

SRFFT algorithm for the fast computation of the DFT

is developed by Duhamel and Hollmann for data sequences

having a length which is integer power of 2 (N=2m). Radix-2

decimation-in-frequency indicates that the even-numbered

points of the DFT can be computed independent of the oddnumbered points. So, there is a possibility of using different

computational methods for independent parts of the algorithm

to reduce the number of computations. Given a sequence xn

of length N (integer power of two), the computation of the

coefficients Xk using the SRFFT algorithm with decimation-infrequency is done by observing that the even coefficients can

Received 07 September 2012, revised 08 February 2013, online published 23 March 2013

210

pavan, et al.: FPGA Implementation of Split-Radix FFT for High Throughput

be expressed by the following equation3:

x 2k =

xk =

N/2 1

n =0

N 1

(x n + x n + N/2 )WN 2nk

, k = 0, 1, 2........N/2 1 (1)

x n WN nk , k = 0, 1, 2........N 1

(2)

and odd coefficients are expressed by the following

equation:

x 4k+1 =

n =0

N /4 1

n =0

x n x N

n+

j x N x 3N

n+

n+

4

4

WN n WN 4 nk , k = 0, 1,....N / 4 1

x 4k+3 =

N /4 1

n =0

x n x N

n+

2

WN

3n

WN

4 nk

j x N x 3N

n+

n+

4

4

(3)

, k = 0, 1,........N / 4 1

(4)

Figure 1 explains the operations required to implement

Eqns. (1) to (4). X(2k) and X(2K+2) are calculated by Radix-2

Eqn. (2), which require only complex additions. X(4k+1) and

X(4k+3) are calculated using Radix-4 Eqns. (3) and (4). {x(n),

x(n+N/2)} and {x(n+N/4), x(n+3N/4)} are subtracted and then

multiplied with -j & j respectively. Addition is applied and the

resulting data is multiplied with the twiddle factors, which are

taken from ROM.

Figure 1. L Shaped dragonfly.

Each L-shaped dragonfly contains one Radix-2, and

one Radix-4 butterflies. In Fig. 2, each column represents

one stage. The algorithm has a recursive nature. This means

that the algorithm is first performed as an N-point L-shaped

dragonfly, and then the results are fed to one N/2-point and

two N/4point stages, that themselves can be performed as an

L-shaped dragonfly. This continues until all the points have

been fully transformed3,4. Near the end of the process, 8-point

Figure 2. L-shaped dragonfly structure of SRFFT.

and 4-point transforms using the L-shaped dragonfly yield

2-point outputs. For 2-pt transforms, simple Radix-2 FFT

butterflies are performed.

3. FPGA Implementation of SRFFT

Figure 3 shows the block diagram of the 512-pt SRFFT

implemented in FPGA. The classic SRFFT algorithm proposed

by Duhamel and Hollmann for 512-pt requires 3076 real

multiplications and 12292 real add-sub operations1, performed

in 9 stages. This needs 9222 DSP48Es for implementation in

FPGA.

Contrasted with the above, our algorithm for 512-pt

SRFFT is implemented using only three building blocksdragonfly computing block, commutator block and ROM, with

their connections between adjacent blocks. The implementation

is achieved using seven stages i.e. seven dragonfly computing

blocks, seven commutator blocks and six ROMs. Only 336

DSP48Es have been used to implement the building blocks and

achieve a 1500 MSPS throughput.

The incoming data is multiplexed on to four parallel buses

by retiming with a suitable lower clock and stored in four

FIFOs for processing. To handle the throughput of 1500MSPS,

stage-1 needs to be completed within 64 clock cycles, which

is accomplished by reading the samples simultaneously from

all the four FIFOs and sending to dragonfly stage 1. 512

data points are covered within 32 clock cycles using pipelined

architecture. The twiddle factors, which are stored in ROM2

Figure 3. FPGA implementation of SRFFT block diagram.

211

Def. SCI. J., Vol. 63, No. 2, March 2013

are read in pipeline and sent accordingly to dragonfly stage.

Input data is read from four FIFOs in pipeline and provided

to the dragonfly. Each dragonfly contains 4 L-shaped dragons

to process 16 data points at a time. Original SRFFT algorithm

is modified into 7 stages by executing the 4-pt dragonflies

and 2-pt butterflies in earlier stages to maximise the resource

reusability. At every stage, decomposition of the half- and

quarter-length DFTs leads to full split-radix structure. As

512-pt SRFFT output is in bit reverse order, the output is stored

in output RAM by giving bit reverse ordered addresses2.

Figure 4. Commutator.

Commutator has fifos to store data from and to the

dragonflies1. Data is stored in commutators one after the other

and read at the same time for parallel operation. Commutator

logic comprises of time division multiplexing (TDM) of

available data at individual stages. TDM employs writing of

different stage outputs from previous stage and reading of the

inputs to next stage. Commutator logic also includes reading of

twiddles from a particular ROM.

5. Dragonfly computing block

Because of the limitation on the number of DSP blocks

available in FPGA, all the dragonflies cannot be implemented

at a time1. To overcome this limitation, four dragonflies are

used for computation of a stage and the same dragonflies are

reused by employing pipelined architecture. Input is provided

in sixteen parallel data buses, and output is taken in sixteen

parallel data buses. In every stage, the first output is available

after 12 clock cycles, and the final output is available at the end

of 44thclock cycle. Similarly, subsequent stages get completed

within 44 clock cycles each, taking the total latency to 300

clock cycles.

L-shaped dragonfly requires 12 DSP blocks to compute

212

Figure 5. L-shaped dragonfly.

three complex add-sub operations and two complex

multiplications as shown in the Fig. 5. Since each stage contains

four L-shaped dragonflies, 48 DSP blocks are utilized. Thus, a

total of 336 DSP blocks are used to complete 7 stages of 512-pt

SRFFT.

6. Simulation Results

The SRFFT algorithm is developed in MATLAB with

fixed point tool box for 12-bit input and the results are verified

with built-in MATLAB FFT function. VHDL simulation has

been carried out using Modelsim SE. Xilinx ChipScope is used

for verification in the hardware.

For N-pt FFT, the output data width is [input data width

+log2(N) + 1]. For an input data width of 12, FFT output data

width will be 22-bits. Growth of fractional bits created from

the multiplication is truncated after the every multiplication

to 22-bits. For an input sinusoid of frequency 500 MHz, the

VHDL outputs shown in Fig. 7 are compared with the results

of MATLAB in-built FFT function outputs shown in Fig. 6.

ChipScope capture of the FFT output shows maximum

peak at xk index 323, which is same as the MATLAB outputs

peak index. Error in magnitude between MATLABs built-in

FFT and the FPGA implemented 512-pt SRFFT is shown in

Fig. 8. Maximum error in magnitude is 23, which is due to the

fact that MATLAB functions in 64-bit operating environment

xk magnitude

4. Commutator block

Dragonfly needs data in the format of {x(n), x(n+N/2)

and x(n+N/4), x(n+3N/4)}. To take dragonfly input in required

format, data is stored in 4 FIFOs in the same order and data is

provided simultaneously from FIFOs and given in pipeline to

the next stages2. To ease this data formatting, commutator is

used. Figure 4 shows the block diagram of commutator logic.

xk index

Figure 6. MATLAB inbuilt FFT output.

pavan, et al.: FPGA Implementation of Split-Radix FFT for High Throughput

error

Figure 7. SRFFT output in XC5VSX95T chipscope.

xk index

Figure 8. SRFFT error plot.

whereas in VHDL, only 22-bit output width is used. Fixed

point results from MATLAB shown in Fig. 9 are matching with

VHDL results shown in Fig. 7 for 12-bit input.

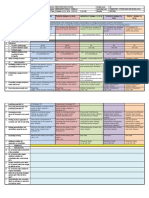

7. FPGA resource usage

Implementation of normal 512-pt SRFFT algorithms

in XC5VSX95T FPGA is not feasible due to the limitations

on the resources available. However, the modifications to

the algorithm proposed by us have made the implementation

feasible. Table 1 gives the actual FPGA utilisation for a 512-pt

SRFFT for a clock rate of 187.5 MHz.

Table 1. Performance of 512-pt SRFFT

No.

Parameter

Value

Number of points

512

Output data width

22-bit

Number of slice registers

51,192

Number of slice LUTs

27,547

Number used as memory

7,000

Number of DSP48Es

336

Initial latency

1.65 s

Frequency

187.5 MHz

FPGA family device

XC5VSX95T

8. Conclusions

This paper describes the design and FPGA implementation

of a 512-pt pipeline SRFFT. The inputs are four parallel data

buses of 12-bit width. The algorithm outputs the transform

coefficients over 16 parallel data channels with a latency of

300 clock cycles. The computing elements have three complex

add-subtract blocks operating in parallel with two complex

multipliers, which have been implemented with the DSP48Es

available within the FPGA in order to attain the highest possible

operational speed. For a clock rate of 187.5 MHz, a latency

of 1.65 s is achieved in implementing the 512-pt SRFFT.

split radix-based FFT algorithm for 512-pt FFT has been

implemented by using 7 stages instead of 9 stages in FPGA

for achieving a throughput of 1500MSPS. The output has

been compared with Matlab simulation results and validated.

Verification is done on Xilinx XC5VSX95T by feeding a single

tone.

References

1. Garca1, Jesus; Michel, Juan A.; Ruiz, Gustavo &

Boron, Angel M. FPGA realization of a Split Radix

FFT processor. SPIE, 6590, 2007, P-1 - P-11.

2. Kannan M. & Srivatsa, S.K. Low power hardware

implementation of high speed FFT core. Int. Arab

J. Info. Technol., 2009, 6(1), 1-7.

3. Jones, Douglas L. Split-radix FFT algorithms. http://

cnx.org/content/m12031/latest/ (Accessed on 12/01/

2012).

4. Yeh, Wen-Chang. High-speed and low-power splitradix FFT. IEEE Trans. Signal Processing, 2003,

51(3), 86474.

Contributors

Mr P.S. Sai Pavan graduated from JNTU

College of Engineering, Kakinada, A.P.

in the year 2010. Currently working as

Deputy Engineer in Bharat Electronics

Ltd, Hyderabads D&E-Core Technologies

group. His area of interest include: Digital

receivers and embedded systems of EW

systems.

Ms B. Renuka graduated from Osmania

University, Hyderabad, A.P. in 2009.

Currently working as Deputy Engineer

in Bharat Electronics Ltd, Hyderabads

D&E-Core Technologies group. Her area

of interest include: Digital receivers for

EW systems, FPGA implementation of

the DSP algorithms.

Mrs B.Vinatha did her BTech from JNTU

College of Engineering, Kakinada, A.P in

2000. Currently she is working as Manager

in Bharat Electronics Ltd, Hyderabads

D&E-Core Technologies Group. Her area of

interest include: Digital signal processing

algorithms development and implementation

on FPGAs for digital receivers of EW

systems.

213

Vous aimerez peut-être aussi

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (894)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- DG Iqs FullDocument126 pagesDG Iqs FullShyamala Venkataramani100% (2)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- Sri Veerabrahmendra The Precursor of KalkiDocument359 pagesSri Veerabrahmendra The Precursor of KalkiSantosh Kumar Ayalasomayajula77% (30)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- Sharepoint Quick Reference-CheatsheetDocument3 pagesSharepoint Quick Reference-Cheatsheethabeeb_matrixPas encore d'évaluation

- Successful Learning TechniquesDocument43 pagesSuccessful Learning TechniquesdgavrilePas encore d'évaluation

- Perl Tutorial PDFDocument551 pagesPerl Tutorial PDFgouthamrajPas encore d'évaluation

- Vishnu SahasranamamDocument43 pagesVishnu SahasranamamSuresh KumarPas encore d'évaluation

- Carry Save Adder Trees in Multipliers: ECEN 6263 Advanced VLSI DesignDocument8 pagesCarry Save Adder Trees in Multipliers: ECEN 6263 Advanced VLSI DesignShashidhar KhPas encore d'évaluation

- Ashtavakra Gita - Bart MarshallDocument60 pagesAshtavakra Gita - Bart Marshallமோகன் புதுவைPas encore d'évaluation

- Booth Recoded 8x8 MultiplierDocument4 pagesBooth Recoded 8x8 MultiplierSuresh KumarPas encore d'évaluation

- Bhagavatham in ShortDocument69 pagesBhagavatham in ShortSuresh KumarPas encore d'évaluation

- AVD Report Dwip Bhavsar Himanshu VermaDocument27 pagesAVD Report Dwip Bhavsar Himanshu VermaSuresh KumarPas encore d'évaluation

- Thesis VHDL CadenceDocument49 pagesThesis VHDL CadenceSuresh KumarPas encore d'évaluation

- Lab 2: Modifying Legup To Limit The Number of Hardware Functional UnitsDocument8 pagesLab 2: Modifying Legup To Limit The Number of Hardware Functional UnitsSuresh KumarPas encore d'évaluation

- Lab 3Document13 pagesLab 3Suresh KumarPas encore d'évaluation

- Gajski Vahid Book Ss SlidesDocument216 pagesGajski Vahid Book Ss SlidesSuresh KumarPas encore d'évaluation

- Lab 1Document11 pagesLab 1Suresh KumarPas encore d'évaluation

- Asynch VHDL CodesDocument155 pagesAsynch VHDL CodesSuresh KumarPas encore d'évaluation

- VLSI Implementation of Pipelined Fast Fourier TransformDocument6 pagesVLSI Implementation of Pipelined Fast Fourier TransformIjarcet JournalPas encore d'évaluation

- All Digital Phase Locked Loop (ADPLL) Design and SimulationDocument27 pagesAll Digital Phase Locked Loop (ADPLL) Design and SimulationSuresh KumarPas encore d'évaluation

- 8-bit Microprocessor Project ReportDocument35 pages8-bit Microprocessor Project ReportSuresh KumarPas encore d'évaluation

- Parallel Pipiline FTT Real Value SignalDocument3 pagesParallel Pipiline FTT Real Value SignalSuresh KumarPas encore d'évaluation

- Pipelined ALU ASICDocument4 pagesPipelined ALU ASICSuresh KumarPas encore d'évaluation

- FPU Thesis FinalDocument68 pagesFPU Thesis FinalSuresh KumarPas encore d'évaluation

- CUSTOMIZING THE KEYBOARDDocument5 pagesCUSTOMIZING THE KEYBOARDengelect2065Pas encore d'évaluation

- Security Best Practices in AOS v1.7 PDFDocument70 pagesSecurity Best Practices in AOS v1.7 PDFAmerica CorreaPas encore d'évaluation

- Digital Marketing PDFDocument2 pagesDigital Marketing PDFMohammed SohailPas encore d'évaluation

- How to fill UG CBCS – TDC Degrees 1st semester registration exam formDocument9 pagesHow to fill UG CBCS – TDC Degrees 1st semester registration exam formLalchand AliPas encore d'évaluation

- Manual Drilling OperationDocument13 pagesManual Drilling OperationnaninoPas encore d'évaluation

- Apache Kafka InstallationDocument3 pagesApache Kafka Installationsurendra yandraPas encore d'évaluation

- How To Create Composite WallsDocument7 pagesHow To Create Composite WallsfloragevaraPas encore d'évaluation

- Optimization of Combined Economic and Emission Dispatch Problem A Comparative Study-10702808Document15 pagesOptimization of Combined Economic and Emission Dispatch Problem A Comparative Study-10702808kanuvietPas encore d'évaluation

- Jitendra Gupta: Program Manager/ Project Manager SAP/ E-CommerceDocument6 pagesJitendra Gupta: Program Manager/ Project Manager SAP/ E-CommerceSamerp KumarPas encore d'évaluation

- En - Slide - CCNA 1 - Module 1 - Introduction To The NetworkDocument54 pagesEn - Slide - CCNA 1 - Module 1 - Introduction To The Networkcamarad77Pas encore d'évaluation

- Digital Design Through Verilog HDLDocument4 pagesDigital Design Through Verilog HDLmukesh_sonuPas encore d'évaluation

- RobotShop Learning Center - Robotic TrendsDocument5 pagesRobotShop Learning Center - Robotic TrendsMC. Rene Solis R.Pas encore d'évaluation

- CICS For Iseries Problem DeterminationDocument124 pagesCICS For Iseries Problem DeterminationKuzumichPas encore d'évaluation

- DLL Ict 10 Week October 15-19, 2018Document3 pagesDLL Ict 10 Week October 15-19, 2018Bernadeth Irma Sawal CaballaPas encore d'évaluation

- Introduction To Java HomeworkDocument2 pagesIntroduction To Java Homeworkstefan16394Pas encore d'évaluation

- Guide To Computer Forensics InvestigationDocument65 pagesGuide To Computer Forensics InvestigationAnthony WilsonPas encore d'évaluation

- SMR Online Users Guide PDFDocument48 pagesSMR Online Users Guide PDFniku100% (1)

- 1162-1619624546635-Unit 16 - Cloud-Computing - Reworded - 2021Document49 pages1162-1619624546635-Unit 16 - Cloud-Computing - Reworded - 2021Vivekan VivekPas encore d'évaluation

- MCSL-054 Solved Assignment 2013-14Document28 pagesMCSL-054 Solved Assignment 2013-14Dibya NandiPas encore d'évaluation

- VACON-ADP-MCAA adapter guideDocument10 pagesVACON-ADP-MCAA adapter guideSharad Soni0% (1)

- Data Domain, Deduplication and MoreDocument6 pagesData Domain, Deduplication and MorebinhPas encore d'évaluation

- JESS Functions and I/O TutorialDocument5 pagesJESS Functions and I/O TutorialolivukovicPas encore d'évaluation

- Sap HR Preview PDFDocument12 pagesSap HR Preview PDFYashika Saraf100% (1)

- Preparation of A Formatted Technical Work For An IEEE Power & Energy Society Transactions/Journal PublicationDocument4 pagesPreparation of A Formatted Technical Work For An IEEE Power & Energy Society Transactions/Journal PublicationSoniaPas encore d'évaluation

- For loops guide: Learn Python loopingDocument10 pagesFor loops guide: Learn Python loopingDJEFOUO FOUODJI ANGE MAGLOIREPas encore d'évaluation

- Regression TestingDocument18 pagesRegression TestingAaka ShPas encore d'évaluation

- It Sba QuestionDocument12 pagesIt Sba QuestionCatherianna SimmsPas encore d'évaluation

- Solving math and logic problems from sample documentsDocument16 pagesSolving math and logic problems from sample documentsSamarth PawaskarPas encore d'évaluation