Académique Documents

Professionnel Documents

Culture Documents

Osaki2012 PDF

Transféré par

Xavier DannyDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Osaki2012 PDF

Transféré par

Xavier DannyDroits d'auteur :

Formats disponibles

1776

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 47, NO. 7, JULY 2012

A Low-Power Level Shifter With Logic Error

Correction for Extremely Low-Voltage Digital

CMOS LSIs

Yuji Osaki, Student Member, IEEE, Tetsuya Hirose, Member, IEEE, Nobutaka Kuroki, and

Masahiro Numa, Member, IEEE

AbstractThis paper presents a level shifter circuit capable of

handling extremely low-voltage inputs. The circuit has a distinctive current generation scheme using a logic error correction circuit that works by detecting the input and output logic levels. The

proposed level shifter circuit can convert low-voltage digital input

signals into high-voltage digital output signals. The circuit achieves

low-power operation because it dissipates operating current only

when the input signal changes. Measurement results demonstrated

that the circuit can convert a 0.23-V input signal into a 3-V output

signal. The power dissipation was 58 nW for a 0.4-V 10-kHz input

pulse.

Index TermsLevel converter, level shifter, low power, low

voltage, subthreshold.

I. INTRODUCTION

HE most effective and direct way to reduce power

dissipation in digital LSIs is to reduce their supply

voltage because of their quadratic dependence of the power

dissipation on the supply voltage. Several low-power design

techniques have been investigated. Subthreshold LSIsLSIs

whose supply voltage is lower than the threshold voltage

of a MOSFEThave attracted much attention for use in

power-aware LSI applications such as wireless sensor networks, implantable bio-medical systems, and environmental

monitoring devices [1][4]. However, there are a number of

design challenges, and several studies have been carried out.

Among them, one of big issues is in a level shifter (LS) circuit

design [5]. In this paper, we describe and demonstrate an LS

circuit suitable for extremely low-voltage digital LSIs [6], [7].

In low-voltage LSI systems, subthreshold digital LSIs will

be implemented with conventional circuits that operate at high

supply voltage. Therefore, an LS circuit is required to enable

correct communication with other circuits. Moreover, it is also

required when LSI designers must test the functionality of the

Manuscript received November 15, 2011; revised January 31, 2012; accepted

February 19, 2012. Date of publication May 11, 2012; date of current version

June 21, 2012. This paper was approved by Guest Editor Atila Alvandpour. This

work was supported in part by the VLSI Design and Education Center (VDEC),

The University of Tokyo with the collaboration with Cadence Design Systems,

Inc. and Mentor Graphics, Inc., STARC, KAKENHI (21680004), and the New

Energy and Industrial Technology Development Organization (NEDO).

The authors are with the Department of Electrical and Electronic Engineering, Kobe University, Nada, Kobe 657-8501, Japan (e-mail: hirose@eedept.kobe-u.ac.jp).

Color versions of one or more of the figures in this paper are available online

at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2012.2191320

low-voltage subthreshold digital circuits. However, communication and function tests are difficult when conventional LS circuits are used because the supply voltage of the subthreshold

digital circuits is below 0.5 V and that of the peripheral circuits is still high (e.g., the supply voltage of input/output (I/O)

peripheral circuits is 3.3 V). This is because the drive current of

the low-voltage circuit significantly lowers as the supply voltage

reduces and conventional LS circuits cannot pull down voltages.

To mitigate this problem, several level shifters and remedies

have been investigated [4], [8][13]. One approach has been to

increase the drive current of the level shifter by enlarging the

transistor channel width. Another is to use a multi-stage level

shifters [4] or inverters with multiple supply voltages. However,

these circuits still depend on the supply voltage difference, the

circuit configuration is complex, and it requires multiple reference voltages. The problem discussed above is thus basically

unresolved.

To solve this problem, we present an LS circuit with a logic

error correction circuit (LECC) capable of handling extremely

low-voltage inputs [6], [7]. The proposed LS circuit can convert extremely low-voltage signals into high-voltage signals.

The circuit is based on a conventional two-stage comparator circuit and has a distinctive feature in a current generation circuit

with an LECC [7].

This paper is organized as follows. Section II briefly describes

the problem with a conventional LS circuit and presents the operation principle of our proposed circuit. Section III shows the

simulation results, Section IV shows the experimental results

with a fabricated proof-of-concept chip, and Section V concludes the paper.

II. LEVEL SHIFTER CIRCUIT

A. Conventional

Fig. 1 shows the schematic of a conventional LS circuit. The

circuit consists of cross-coupled pMOSFETs (MP1 and MP2)

and two nMOSFETs (MN1 and MN2) driven by complementary

input signals IN and INB. The circuit has critical problems when

and

the voltage difference between low supply voltage

becomes large.

high supply voltage

When the voltages of IN and INB are Low and High, MN1

and MN2 are Off and On, respectively. MN2 then pulls down

node OUT, causing MP1 to turn On. Because node OUTB then

, MP2 turns off, and OUT drops to the GND

increases to

level. Note that the voltage of OUT is determined by the drive

0018-9200/$31.00 2012 IEEE

OSAKI et al.: A LOW-POWER LEVEL SHIFTER WITH LOGIC ERROR CORRECTION FOR EXTREMELY LOW-VOLTAGE DIGITAL CMOS LSIs

Fig. 1. Schematic of conventional LS circuit.

Fig. 2. Architecture of proposed LS circuit.

currents of pull-up transistor MP2 and pull-down transistor

MN2. Therefore, if the drive current of MP2 is larger than

that of MN2, OUT cannot be discharged. Moreover, when we

consider the case of extremely low-voltage subthreshold digital

LSIs, because the on-current of MN2 becomes quite low, the

drive currents of the nMOSFETs are significantly smaller than

those of the pMOSFETs, which operate in the strong inversion

region. Thus, OUT cannot be discharged. As a result, a conventional LS circuit cannot correctly operate in this situation.

B. Proposed

The architecture of the proposed LS circuit is shown in Fig. 2.

It consists of a level conversion circuit and a logic error correction circuit (LECC). The complementary input signals (IN and

INB) and the output signal (OUT) are applied to the LECC. The

LECC supplies the operating current for the level conversion

circuit only when the LECC detects a logic error. Fig. 3 shows

the complete schematic of the LS circuit. The operation principles of the circuits are described in the following sections.

1) Level Conversion Circuit: The level conversion circuit,

which is shown on the right in Fig. 3, is based on a conventional two-stage comparator circuit. The comparator generates

output voltage signal, OUT, according to the difference in the

voltage of IN and INB. Note that the voltage of OUT is determined by the drive currents of pull-up transistor MP6 and

pull-down transistor MN8, and that the currents flowing in MP6

and MN8 depend on current flowing through MP2. Therefore,

because both drive currents are determined by the same current,

the circuit is free from the limitations discussed in the conventional ones.

In the conventional comparator design, a current reference

circuit needs to operate steadily. However, because the current

reference circuit dissipates static current and increases power

dissipation, it cannot be used in our design. Therefore, we developed a logic error correction circuit (LECC) in which the

current flowing in the circuit is generated only when the input

signals change.

2) Logic Error Correction Circuit (LECC): The LECC,

which is shown on the left in Fig. 3, consists of two circuit

blocks: 1) a low logic error correction circuit (LLECC) and 2) a

high logic error correction circuit (HLECC). They are driven

1777

by IN, INB, and OUT. The LECC generates an operating

current such that IN and OUT correspond to each other. When

the output logic level of the LS circuit corresponds to the input

logic level, the LECC does not supply current . When they

do not correspond, the LECC detects the logic error, and the

LLECC or HLECC supplies an operating current. In other

words, because the LECC supplies an operating current only

when the input and output logic levels do not correspond to

each other, the power dissipation of the circuit is minimized.

The correction circuit operations are described below.

LLECC: The low logic error correction circuit, LLECC,

consists of two nMOSFETs (MN1 and MN2) connected

in series. The LLECC operates only when OUT does not

correspond to the Low logic of IN. Fig. 4(a) depicts the

waveforms of IN, INB, and OUT. When IN changes from

High to Low, or when INB changes from Low to High,

there is a period during which OUT does not correspond

to IN. During this period, the LLECC generates fall-transition current

until OUT corresponds to the Low logic

of IN.

When the logic levels of IN and OUT are Low, the LLECC

does not supply any current for the level conversion circuit

because MN2 is off due to the Low logic level of OUT.

However, when the logic levels of IN and OUT do not

correspond (i.e., IN, INB, and OUT are Low, High, and

High, respectively),

flows because the voltages of both

INB and OUT are High;

pulls OUT down to GND so

that the input and output logic levels correspond.

HLECC: The high logic error correction circuit, HLECC,

consists of three nMOSFETs (MN3, MN4 and MN5) and

a pMOSFET (MP1). In contrast to the LLECC, the circuit operates only when OUT does not correspond to the

High logic of IN. Fig. 4(b) depicts the waveforms of IN

and OUT. When IN changes from Low to High, there is

a period during which OUT does not correspond to IN.

During this period, the HLECC generates rise-transition

current

until OUT corresponds to the High logic of IN.

When the logic levels of IN and OUT are High, the

HLECC does not supply any current because the output

voltage of the first stage in the HLECC is Low. However,

when the logic levels of IN and OUT do not correspond

(i.e., IN, INB, and OUT are High, Low, and Low, respectively), the HLECC generates current

, and the

LS circuit operates so that the input and output logic

levels correspond. When IN and OUT are High and Low,

the output voltage of the first stage is High because the

overdrive voltage of the MP1 is larger than that of MN3.

This enables MN4 and MN5 to supply current

to the

level conversion circuit, and

pulls OUT up to

.

From the discussion above, current for the level conversion

circuit is expressed as

(1)

and

are not generated and the LECC does

Because

not supply current when the input and output logic levels

correspond, the power dissipation of the circuit is minimized.

The amount of

and

generated depends on lower supply

voltage of

.

1778

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 47, NO. 7, JULY 2012

Fig. 3. Schematic of proposed LS circuit.

Fig. 4. Waveforms (a) when fall-transition current for LS is generated and

(b) when rise-transition current for LS is generated.

TABLE I

TRANSISTOR SIZES OF OUR CIRCUIT

When IN and OUT correspond, the LECC does not supply

any current to the level conversion circuit. However, in fact,

leakage current flows in the circuit. Therefore, because the

voltage gain in the level conversion circuit is sufficient to keep

the output node, OUT is kept at a voltage, i.e.

or GND.

If some unexpected noise ever changes the OUT, the LECC

detects logic errors and supplies the operating current until IN

and OUT once again correspond. On the other hand, if the noise

changes the input logic levels of IN and INB, the LS circuit

cannot operate properly due to the disrupted logic inputs. This

means that the noise immunity of the proposed LS circuit is

limited by that of low-voltage digital circuit. In other words,

the noise margin of the proposed LS circuit is determined by

that of the low-voltage digital circuits themselves.

III. SIMULATION RESULTS

The performance of the proposed LS circuit was evaluated

using SPICE with a set of 0.35- m parameters.

was set

to 3 V. We used an inverter as a load circuit of the LS circuit and

calculated power dissipations including a charge and discharge

current for the load. Table I shows the transistor sizes of the

proposed LS circuit.

Fig. 5. Simulated waveforms of proposed LS circuit. Frequency of input signal

was set to 1 kHz: (a) input signal and output signal; (b)(d) currents flowing in

each circuit in Fig. 3.

A. Waveforms

Fig. 5 shows the simulated waveforms. The amplitude and

frequency

of the input signal were set to 0.4 V and 1 kHz,

respectively. As shown in Fig. 5(a), the 0.4-V input signal was

converted into a 3-V output signal. Fig. 5(b)(d) shows the current flowing in each logic error correction circuit in Fig. 3.

When the input signal of IN changed to High level of

,

there was a period when the logic level of OUT did not correspond to that of IN, as shown in Fig. 5(a). The HLECC detected this and generated current , as shown in Fig. 5(b). This

current was supplied to the level conversion circuit, which converted the 0.4-V input signal into a 3-V output signal. During

this period, the LLECC did not generate current , as shown

in Fig. 5(c). On the other hand, when the input signal of IN

changed to Low level of GND, the LLECC generated current

OSAKI et al.: A LOW-POWER LEVEL SHIFTER WITH LOGIC ERROR CORRECTION FOR EXTREMELY LOW-VOLTAGE DIGITAL CMOS LSIs

Fig. 6. Simulated (a) delays and (b) power dissipations of LS circuits as a function of

at

V.

LS circuits as a function of

while the HLECC did not generate current . This current

was supplied to the level conversion circuit, which converted

the 0.4-V input signal into a 3-V output signal. As shown in

and

were generated alFig. 5(b) and (c), the currents of

ternately in accordance with the logic transition of IN. Fig. 5(d)

generated and supplied to the

shows the current

level conversion circuit. It was generated only when the input

signal changed. Comparing Fig. 5(c) with Fig. 5(d), the current

supplied to the level conversion current was slightly higher

than . This was because the parasitic coupling capacitance between the drain and gate terminals in MP6 in Fig. 3 affected the

gate voltage of MP2 when OUT changed. This effect can be mitigated by reducing the parasitic capacitance (e.g., by changing

the transistor sizes) or by adding a bypass capacitor between the

(or GND).

gate voltage of MP2 and

B. Comparison With Other Level Shifter Circuits

The performance comparison of the proposed LS circuit was

performed using conventional circuit (Fig. 1) and other LS circuits published in [8], [10], [12]. In the conventional circuit

(Fig. 1), MN1 and MN2 were set 100 times larger than MP1

and MP2 so that the low-voltage signals would be converted

correctly. We designed the LS circuits so that they occupy almost same area as the proposed one for fair comparison [8],

[10], [12].

Fig. 6(a) and (b) shows delays and power dissipations of each

LS circuit as function of

at

V and

kHz. The conventional LS circuit could not operate correctly

at

V. This was because the drive current of the

pull-down transistors decreased drastically as

decreased.

at

1779

V. Simulated (c) delays and (d) power dissipations of

TABLE II

MAXIMUM NOISE VOLTAGE

NOTE:

at the

was set to 0.4 V and conventional LS circuit could not operate

.

The LS circuit in [12] dissipated more power than other ones

because it was based on a current mirror circuit to achieve balanced drive current between pull-down and pull-up transistors.

The power dissipation of the proposed LS circuit was comparable to other LS circuits. Fig. 6(c) and (d) shows delays and

power dissipations of each LS circuit as function of

at

V and

kHz. Compared with other LS

circuits, the proposed circuit showed almost the same performances as other ones.

We simulated input noise characteristics in each LS circuit.

and

were set to 0.4 and 3.0 V, respectively. We applied sine wave as a noise signal into IN and INB, respectively.

Because the delays of LS circuits operated at

V

are large as shown in Fig. 6(a), the LS circuits cannot respond

to high frequency signals. Therefore, we applied low frequency

noise signals of 1 Hz. Table II shows the maximum noise voltage

when LS could not operate correctly. When the input noise was

applied to IN, there was no difference among LS circuits. This

1780

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 47, NO. 7, JULY 2012

TABLE III

CHIP AREA COMPARISON AND RESULTS OF MONTE CARLO SIMULATIONS FOR 500 RUNS

NOTE1:

is the simulated minimum supply voltage of Monte Carlo simulation results.

NOTE2: Numbers represent number of successes.

was because the switching voltage of the inverter determines the

noise immunity of the LS circuits. When the input noise was applied to INB, the proposed LS circuit was more tolerant to other

LS circuits because the proposed LS circuit generates OUT according to the difference in the voltage of IN and INB. In contrast, the output node of the other LS circuits were affected directly by the noise voltage at INB because the drive current of

the pull-down transistor for the output node was sensitive to the

noise voltage of INB.

To investigate circuit operation against process and temperature variations, we performed Monte Carlo statistical circuit

simulations assuming die-to-die (D2D) global variations and

within-die (WID) random mismatch variations in all MOSFETs

using the parameters provided by the manufacturer with various

temperature conditions [14]. We compared the performance of

the proposed circuit with those of a conventional circuit and

other circuits [8], [10], [12]. The amplitude of

was set

to 0.4 V, 0.5 V, or 0.6 V. The input pulse frequency

was

set to very slow frequency (i.e., 1 Hz) to evaluate correct level

conversion operation at lower

. Table III shows the evaluated results of each chip area, the number of success runs that

the LS circuits correctly converted the low-voltage signals into

high-voltage signals, and the minimum

, which each LS

circuit could convert all the inputs correctly, with Monte Carlo

simulations for 500 runs. Note that we calculated each chip area

from their transistor sizes and the areas were normalized with

that of the proposed circuit

The conventional and reported LS circuits could not operate

correctly under lower-temperature and lower-supply-voltage

conditions due to their poor drive current. In contrast, the

proposed LS circuit could operate robustly under all conditions because it does not depend on the balance between the

nMOSFET and pMOSFET drive currents. The minimum

of the proposed circuit was 0.35 V. The minimum

was

decided by functional errors either in the low-voltage digital

circuits or in the differential pair of the LS circuit.

In advanced CMOS process technologies, the impact of

process variations will increase [14]. However, from above

simulation results and discussions, it is proved that the proposed

LS circuit is more tolerant to the variations than other ones.

IV. EXPERIMENTAL RESULTS

We fabricated a proof-of-concept chip using a 0.35- m,

2-poly, 4-metal standard CMOS process. Fig. 7 shows a micro-

Fig. 7. Chip micrograph and partially enlarged view (area: 1880 m ).

Fig. 8. Measurement setup.

graph of the chip and a partial enlarged view of the proposed

LS circuit, which had occupied an area of 1880 m . The

transistor sizes of the fabricated LS circuit were the same as

those of the simulated LS circuit (see Table I). Fig. 8 shows a

measurement setup for the LS circuit. We used an inverter as a

load circuit of the LS circuit. The power dissipation of the LS

circuit was measured excluding a charge and discharge current

for the I/O buffer.

A. Logic Error Correction Circuit (LECC)

As discussed in Section II, the characteristics of the LECC depend on output voltage

. Therefore, we measured the circuit performance for various values of

.

and

were set to 0.4 and 3.0 V, respectively.

Fig. 9(a) shows current measured in the LECC shown in

Fig. 3 as a function of

. IN and INB were respectively

set to 0 and 0.4 V. When

increased from Low, the circuit

OSAKI et al.: A LOW-POWER LEVEL SHIFTER WITH LOGIC ERROR CORRECTION FOR EXTREMELY LOW-VOLTAGE DIGITAL CMOS LSIs

Fig. 9. Measured current

as function of

Fig. 10. Measured maximum current

1781

(a) when IN and INB were Low and High and (b) when IN and INB were High and Low.

as function of

(a) when IN and INB were Low and High and (b) when IN and INB were High and Low.

generated when

exceeded 0.5 V. That is, the increase in

under the condition

V caused the logic levels of

IN and OUT to no longer correspond, which caused the circuit

to generate current

(and not ), which pulled OUT down to

GND (Low level). The maximum current was about 20 nA.

Fig. 9(b) shows the measured current in the LECC shown

in Fig. 3 as a function of

. IN and INB were respectively

set to 0.4 and 0 V, the opposite of the case shown in Fig. 9(a).

When

decreased from High, the circuit generated when

dropped below 2.5 V. That is, the decrease in

under

the condition

V caused the logic levels of IN and

OUT to no longer correspond, which caused the circuit to generate current

(and not ), which pulled OUT up to

(High level). The sharp drop in

at 2.5 V was because the

first stage, consisting of MP1 and MN3 in the HLECC, is based

on of a common source amplifier, which leads to sharp current

transitions.

Fig. 10 shows the measured maximum in the LECC as a

function of

(a) when IN and INB were Low and High

and (b) when IN and INB were High and Low. The maximum

currents under both conditions had the same characteristics and

increased exponentially with

in the range 0.4 to 0.6 V.

When the voltage was higher than 0.6 V, they increased gradually with

because both maximum currents are determined

by

.

Fig. 11. Measured waveforms of proposed LS for 10-kHz input pulse.

B. Level Shifter Circuit

Fig. 11 shows the measured input and output waveforms of

the proposed LS circuit at 10 kHz. The circuit converted the

0.4-V signal into a 3-V signal.

Fig. 12 shows a shmoo plot of the operating frequency as a

function of

. The maximum operating frequency increased

Fig. 12. Shmoo plot.

exponentially with

in the range 0.4 to 0.6 V because the

current generated in the LECC increased exponentially with

1782

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 47, NO. 7, JULY 2012

TABLE IV

PERFORMANCE SUMMARY AND COMPARISON

[12] , [13] : Simulation results.

and higher than the threshold voltage

currents are expressed as

of the MOSFET, the

(2)

(3)

Fig. 13. Measured power dissipations as a function of

frequencies of 0.1, 1, and 10 kHz.

at input pulse

respectively, where is the aspect ratio

of the transistor,

is the process-dependent parameter, is the carrier mobility,

is the gate-oxide

capacitance,

is the oxide permittivity,

is the oxide thickness, is the subthreshold slope factor,

is the

thermal voltage,

is the Boltzmann constant, is the absolute temperature, and is the elementary charge [15]. Because

period during which the LECC generates the current depends

on the propagation delay of the low voltage digital circuit, can

be expressed as

(4)

Fig. 14. Measured power dissipation as a function of

frequency of 10 kHz.

at the input pulse

, as shown in Fig. 10. When the voltage was higher than

0.6 V, the operating frequency increased gradually with

because the current when

is above the threshold voltage

also increases in the same manner.

Figs. 13 and 14 show the measured power dissipation as a

functions of

and

, respectively. For Fig. 13, the

power was measured at input pulse frequencies of 0.1, 1, and

10 kHz, and for Fig. 14, it was measured at 10 kHz. As shown

in Fig. 13, the power dissipation decreased as input pulse frequency

decreased and was independent of

at a fixed

pulse frequency. As shown in Fig. 14, the power dissipation increased with the square of

. These results can be explained

as follows.

The maximum current generated by the LECC is expressed

as different equations according to

. When

is lower

where is a constant and

is the next-stage load capacitance

of the LS circuit. Note that, from (2), (3), and (4), we can explain the performance characteristics of measured current and

operating frequency as shown in Figs. 10 and 12. The power

dissipation

of the proposed LS circuit can be expressed as

the sum of the internal power dissipation

of the LS circuit

and the power dissipation

for a charge and discharge current of the load capacitance

. Note that leakage power of the

circuit is ignored in this analysis and that the

includes the

power dissipation for a charge and discharge current of the internal node. Because the LECC generates operating current only

when IN and OUT do not correspond, the power dissipation of

the proposed LS circuit can be expressed as

(5)

where

is the average current flowing through the circuit.

Equation (5) shows that is independent of

and depends

on

and the square of

.

The active power dissipation of the LS circuit was extremely

low, 58 nW at an input frequency

of 10 kHz; the corresponding energy

was 5.8 pJ. Static power dissipation

OSAKI et al.: A LOW-POWER LEVEL SHIFTER WITH LOGIC ERROR CORRECTION FOR EXTREMELY LOW-VOLTAGE DIGITAL CMOS LSIs

without applying input pulses was 225 pW. The measured

minimum

, which the LS circuit converted into 3 V, was

0.23 V.

Table IV summarizes the performance of the proposed LS

circuit and compares it with that of other ones [8][13]. The

s and the input frequencies

for energy

are shown

in parentheses. The proposed circuit can convert low voltage

input signals in subthreshold digital circuits to high output signals independently of the supply voltage difference. In addition,

it reduces the static power dissipation because current is generated only when IN and OUT do not correspond.

[12] S. Ltkemeier and U. Rckert, A subthreshold to above-threshold

level shifter comprising a wilson current mirror, IEEE Trans. Circuits

Syst. II, Exp. Briefs, pp. 721724, 2010.

[13] O.-S. Kwon and K.-S. Min, Fast-delay and low-power level shifter for

low-voltage applications, IEICE Trans. Electron., vol. E90-C, no. 7,

pp. 15401543, 2007.

[14] M. J. M. Pelgrom, A. C. J. Duinmaijer, and A. P. G. Welbers,

Matching properties of MOS transistors, IEEE J. Solid-State Circuits, vol. 24, pp. 14331439, 1989.

[15] Y. Taur and T.H. Ning, Fundamentals of Modern VLSI Devices.

Cambridge, U.K.: Cambridge Univ. Press, 2002.

Yuji Osaki (S09) received the B.E. and M.E.

degrees in electrical and electronic engineering from

Kobe University, Kobe, Japan, in 2008 and 2010,

respectively. He is currently working toward the

Ph.D. degree in electrical and electronic engineering

at Kobe University, Kobe, Japan.

His current research interests are in ultra-lowpower CMOS circuits.

Mr. Osaki is a member of the Institute of Electronics, Information and Communication Engineers

(IEICE).

V. CONCLUSION

We presented a level shifter circuit for extremely low-voltage

digital LSIs. The proposed circuit consists of a logic error correction circuit and a level conversion circuit. It can convert

low-voltage digital input signals into high-voltage digital

output signals and achieve low power operation because it

dissipates current only when the input signal changes. We

fabricated a proof-of-concept chip using a 0.35- m CMOS

process and demonstrated its operation by measurements. The

circuit converted a 0.23-V input signal into a 3-V output signal.

The power dissipation was 58 nW for a 0.4-V 10-kHz input

pulse. The proposed circuit is applicable to ultra-low-voltage

digital circuit systems co-existing with high-voltage digital

circuit systems.

REFERENCES

[1] A. Wang, B. H. Calhoun, and A. P. Chandrakasan, Sub-threshold Design for Ultra Low-Power Systems. New York: Springer, 2006.

[2] A. Wang and A. Chandrakasan, A 180 mV FFT processor using subthreshold circuit techniques, in IEEE ISSCC Dig. Tech. Papers, 2004,

pp. 292293.

[3] K. Ueno, T. Hirose, T. Asai, and Y. Amemiya, CMOS smart sensor

for monitoring the quality of perishables, IEEE J. Solid-State Circuits,

vol. 42, no. 4, pp. 798803, 2007.

[4] B. Zhai, L. Nazhandali, J. Olson, A. Reeves, M. Minuth, R. Helfand,

S. Pant, D. Blaauw, and T. Austin, A 2.60 pJ/inst subthreshold sensor

processor for optimal energy efficiency, in Dig. Symp. VLSI Circuits,

2006, pp. 154155.

[5] S. Henzler, Power Management of Digital Circuits in Deep Sub-Micron

CMOS Technologies. New York: Springer, 2007.

[6] Y. Osaki, T. Hirose, N. Kuroki, and M. Numa, A level shifter

circuit design by using input/output voltage monitoring technique for

ultra-low voltage digital CMOS LSIs, in Proc. NEWCAS Conf., 2011,

pp. 201204.

[7] Y. Osaki, T. Hirose, N. Kuroki, and M. Numa, A level shifter with

logic error correction circuit for extremely low-voltage digital CMOS

LSIs, in Proc. Eur. Solid-State Circuits Conf. (ESSCIRC), 2011, pp.

199202.

[8] Y. Kim, D. Sylvester, and D. Blaauw, LC : Limited contention level

converter for robust wide-range voltage conversion, in Dig. Symp.

VLSI Circuits, 2011, pp. 188189.

[9] Y. Moghe, T. Lehmann, and T. Piessens, Nanosecond delay floating

high voltage level shifters in a 0.35 m HV-CMOS technology, IEEE

J. Solid-State Circuits, vol. 46, pp. 485497, 2011.

[10] H. Shao and C.-Y. Tsui, A robust, input voltage adaptive and low

energy consumption level converter for sub-threshold logic, in Proc.

ESSCIRC, 2007, pp. 312315.

[11] Y. Kanno, H. Mizuno, K. Tanaka, and T. Watanabe, Level converters

with high immunity to power-supply bouncing for high-speed sub-1-V

LSIs, in Dig. Symp. VLSI Circuits, 2000, pp. 202203.

1783

Tetsuya Hirose (M05) received the B.S., M.S., and

Ph.D. degrees from Osaka University, Osaka, Japan,

in 2000, 2002, and 2005, respectively.

From 2005 to 2008, he was a Research Associate at the Department of Electrical Engineering,

Hokkaido University, Japan. He is currently an

Associate Professor of the department of Electrical

and Electronics Engineering, Kobe University,

Kobe, Japan. His current research interests are in

the field of nano-watt-power analog/digital mixed

signal integrated circuits design and human-centric

intelligent electronic systems.

Dr. Hirose is a member of the Institute of Electronics, Information and

Communication Engineers (IEICE) and the Japan Society of Applied Physics

(JSAP).

Nobutaka Kuroki received the B.E., M.E., and

Dr. Eng. degrees in electronic engineering from

Kobe University, Japan, in 1990, 1992, and 1995,

respectively.

From 1995 to 2005, he was a Research Associate

in the Department of Electrical and Electronic

Engineering, Kobe University. He has been an Associate Professor since 2006. His research interests

include digital signal processing and digital image

processing.

Dr. Kuroki is a member of the IEEJ, IEICE, and

ITE.

Masahiro Numa (M96) received the B.E., M.E.,

and Dr. Eng. degrees in precision engineering from

the University of Tokyo, Tokyo, Japan, in 1983,

1985, and 1988, respectively.

He is currently a Professor with the Department of

Electrical and Electronic Engineering, Kobe University, Kobe, Japan. His research interests include CAD

and low-power design methodologies for VLSI, and

image processing.

Prof. Numa served as the Technical Program Committee Chair of the 17th Workshop on Synthesis And

System Integration of Mixed Information technologies (SASIMI 2012). He is a

member of the ACM, IPSJ, and IEICE.

Vous aimerez peut-être aussi

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- Electrico ProStar PDFDocument405 pagesElectrico ProStar PDFJ Angel Wolf Maketas50% (2)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- Bose Lifestyle 28 Repair - Schematics PDFDocument32 pagesBose Lifestyle 28 Repair - Schematics PDFAurelio Machado75% (4)

- DAGR Pocket GuideDocument125 pagesDAGR Pocket GuideDean Hufford100% (1)

- Poly SulfoneDocument15 pagesPoly SulfoneDidit Eko PrasetyoPas encore d'évaluation

- SM65 Supervisory Module Handbook E2 LTRDocument73 pagesSM65 Supervisory Module Handbook E2 LTRdlgt63100% (1)

- Reff2 PDFDocument11 pagesReff2 PDFXavier DannyPas encore d'évaluation

- Parent AFD 2820118 511201505950350 PDFDocument1 pageParent AFD 2820118 511201505950350 PDFXavier DannyPas encore d'évaluation

- Chi2007 PDFDocument12 pagesChi2007 PDFXavier DannyPas encore d'évaluation

- Ultra Low Voltage Level Shifters To Interface Sub and Super Threshold Reconfigurable Logic CellsDocument6 pagesUltra Low Voltage Level Shifters To Interface Sub and Super Threshold Reconfigurable Logic CellsXavier DannyPas encore d'évaluation

- A New Level-Up Shifter For High Speed and Wide Range Interface in Ultra Deep Sub-MicronDocument3 pagesA New Level-Up Shifter For High Speed and Wide Range Interface in Ultra Deep Sub-MicronXavier DannyPas encore d'évaluation

- Small 1447067515 PDFDocument57 pagesSmall 1447067515 PDFXavier DannyPas encore d'évaluation

- Lin2008 PDFDocument4 pagesLin2008 PDFXavier DannyPas encore d'évaluation

- Gate-Level Body Biasing Technique For High-Speed Sub-Threshold CMOS Logic GatesDocument6 pagesGate-Level Body Biasing Technique For High-Speed Sub-Threshold CMOS Logic GatesXavier DannyPas encore d'évaluation

- Chi2007 PDFDocument12 pagesChi2007 PDFXavier DannyPas encore d'évaluation

- Small 1447067515 PDFDocument57 pagesSmall 1447067515 PDFXavier DannyPas encore d'évaluation

- Module 1 Lecture 3 FinalDocument12 pagesModule 1 Lecture 3 Finaltejap314Pas encore d'évaluation

- Selection of Materials and Shapes: IIT, BombayDocument9 pagesSelection of Materials and Shapes: IIT, Bombaytejap314Pas encore d'évaluation

- Additional Course Material: Physical Properties of FluidsDocument43 pagesAdditional Course Material: Physical Properties of Fluidssilswal1988Pas encore d'évaluation

- Engineering ManagementDocument21 pagesEngineering ManagementXavier DannyPas encore d'évaluation

- Tamil Quran Jan TrustDocument714 pagesTamil Quran Jan Trustapi-3702881100% (1)

- Sacred Books 14Document417 pagesSacred Books 14Xavier Danny100% (1)

- Module 2 Mechanics of Machining Lesson 8 Forces and Merchant's Circle DiagramDocument15 pagesModule 2 Mechanics of Machining Lesson 8 Forces and Merchant's Circle DiagramSUBHASH ANURAGPas encore d'évaluation

- SirDocument1 pageSirXavier DannyPas encore d'évaluation

- Vpat 10Document10 pagesVpat 10Xavier DannyPas encore d'évaluation

- Emf Equation of AlternatorDocument2 pagesEmf Equation of AlternatorThe Engineers EDGE, CoimbatorePas encore d'évaluation

- Genaral Catalog PLC PanasonicDocument36 pagesGenaral Catalog PLC Panasonicpeter08068350% (2)

- Telit GE910-QUAD DatasheetDocument2 pagesTelit GE910-QUAD DatasheetChristian Guardia CalderónPas encore d'évaluation

- Ogdcl Test 2018Document8 pagesOgdcl Test 2018MuhammadNaveed100% (1)

- Final Report On I7Document47 pagesFinal Report On I7Avneeshwar SinghPas encore d'évaluation

- 1a33 TDS PDFDocument2 pages1a33 TDS PDFFerrovolPas encore d'évaluation

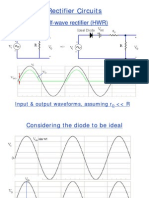

- Rectifier Circuits: Half-Wave Rectifier (HWR)Document18 pagesRectifier Circuits: Half-Wave Rectifier (HWR)Md ArifPas encore d'évaluation

- Switching System PDFDocument27 pagesSwitching System PDFAlamgir Kabir Shuvo100% (1)

- APPENDIX B: Sensor Types: A1. LDR (Light-Dependent Resistor)Document4 pagesAPPENDIX B: Sensor Types: A1. LDR (Light-Dependent Resistor)MostafaDilatyPas encore d'évaluation

- Installation and Use Instructions 7 Day Electronic Timer (TE103)Document2 pagesInstallation and Use Instructions 7 Day Electronic Timer (TE103)eeindustrialPas encore d'évaluation

- Street Lighting Design Guide 4th EditionDocument26 pagesStreet Lighting Design Guide 4th EditionEE PeermadePas encore d'évaluation

- Panasonic Txl42etf62Document0 pagePanasonic Txl42etf62Doru DariusPas encore d'évaluation

- Copie de Tarif - ABB - KAUFEL - 2019 - 02 - v3Document207 pagesCopie de Tarif - ABB - KAUFEL - 2019 - 02 - v3ABELWALIDPas encore d'évaluation

- Summer Internship Report 1Document35 pagesSummer Internship Report 1Hitesh Ahuja0% (1)

- CH 2 (Support) Power Supply CircuitsDocument30 pagesCH 2 (Support) Power Supply CircuitsFazreen Ahmad FuziPas encore d'évaluation

- Base conversion and binary arithmetic practice questionsDocument47 pagesBase conversion and binary arithmetic practice questionsrahul kPas encore d'évaluation

- Editor Hfe Series: X-Ray Generators For Diagnostic RadiographyDocument4 pagesEditor Hfe Series: X-Ray Generators For Diagnostic RadiographyMonooBbuinoPas encore d'évaluation

- Litz Wire Termination GuideDocument5 pagesLitz Wire Termination GuidefdPas encore d'évaluation

- Copeland CRN5 0500 PFV 970 Submittal SheetDocument1 pageCopeland CRN5 0500 PFV 970 Submittal SheetAronis serranoPas encore d'évaluation

- Physics HSSC-II SolutionDocument8 pagesPhysics HSSC-II SolutionThe Right PathPas encore d'évaluation

- Universal Intelligent Controller: UIC-CX9330A (B) Series Screw Air Compressor ControllerDocument48 pagesUniversal Intelligent Controller: UIC-CX9330A (B) Series Screw Air Compressor Controllerchairul wahidPas encore d'évaluation

- ICE SyllabusDocument122 pagesICE SyllabusMaths Is MagicPas encore d'évaluation

- Qab & Hqa Quick-Action Fuses: Overcurrent Protection For Semiconductor Elements and CablesDocument2 pagesQab & Hqa Quick-Action Fuses: Overcurrent Protection For Semiconductor Elements and CablesMAI_QualityPas encore d'évaluation

- Garys Resume'Document2 pagesGarys Resume'gssutherlandPas encore d'évaluation

- 701MRF de PDFDocument92 pages701MRF de PDFPetros TsenesPas encore d'évaluation