Académique Documents

Professionnel Documents

Culture Documents

Dynamic Random Access Memory

Transféré par

MANIKANDANCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Dynamic Random Access Memory

Transféré par

MANIKANDANDroits d'auteur :

Formats disponibles

7/7/2015

DynamicRandomAccessMemory

DynamicRandomAccessMemory(DRAM)memory

cycles

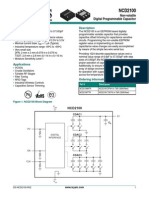

The timing diagrams for the read, write and refreshonly cycles are shown in the Figure below.

For a read cycle /WE must be inactive before the CAS pulse is applied and remain inactive until

the /CAS pulse is over. After the column address is strobed, /RAS is raised and with /RAS high

and /CAS low the data bit is made available on DOUT.

For a write cycle the DIN signal should be applied by the time /CAS goes low, but after the /WE

pin goes low. The write is performed through the DIN pin while /RAS /CAS and /WE are all low.

The DOUT pin is held at its highimpedance state throughout the write cycle. For the refreshonly

cycle, only the row address is strobed and the /CAS pin is held inactive. The DOUT pin is kept in

its highimpedance state.

Note the address lines are A0 to A7 which provide 28 choices. However the memory is arranged

as a 28 x 28 matrix, giving 216 = 64K choices. The /RAS line is used to select the row and then

the /CAS line is used to select the column of the DRAM.

DRAM Read Cycle:

In terms of timing, the following steps must occur:

1. The row address must be applied to the address input pins on the memory device for the

prescribed

amount of time before RAS goes low and held after RAS goes low.

2. RAS must go from high to low and remain low.

3. A column address must be applied to the address input pins on the memory device for the

prescribed amount of time and held after CAS goes low.

4. WE must be set high for a read operation to occur prior to the transition of CAS, and remain

high after the transition of CAS.

http://www.electronics.dit.ie/staff/tscarff/memory/dram_cycles.htm

1/3

7/7/2015

DynamicRandomAccessMemory

5. CAS must switch from high to low and remain low.

6. OE goes low within the prescribed window of time.

7. Data appears at the data output pins of the memory device. The time at which the data

appears depends on when RAS , CAS and OE went low, and when the address is supplied.

8. Before the read cycle can be considered complete, CAS and RAS must return to their inactive

states.

DRAM READ CYCLE

DRAM Write Cycle:

To write to a memory cell, the row and column address for the cell must be selected and data

must be presented at the data input pins. The chip's onboard logic either charges the memory

cell's capacitor or discharges it, depending on whether a 1 or 0 is to be stored. In terms of

http://www.electronics.dit.ie/staff/tscarff/memory/dram_cycles.htm

2/3

7/7/2015

DynamicRandomAccessMemory

timing, the following steps must occur:

1. The row address must be applied to the address input pins on the memory device for the

prescribed amount of time before RAS goes low and be held for a period of time.

2. RAS must go from high to low.

3. A column address must be applied to the address input pins on the memory device for the

prescribed amount of time after RAS goes low and before CAS goes low and held for the

prescribed time.

4. WE must be set low for a certain time for a write operation to occur. The timing of the

transitions are determined by CAS going low.

5. Data must be applied to the data input pins the prescribed amount of time before CAS goes

low and held.

6. CAS must switch from high to low.

7. Before the write cycle can be considered complete, CAS and RAS must return to their inactive

states.

DRAM WRITE CYCLE

http://www.electronics.dit.ie/staff/tscarff/memory/dram_cycles.htm

3/3

Vous aimerez peut-être aussi

- Std10 Science EM 1Document71 pagesStd10 Science EM 1MANIKANDANPas encore d'évaluation

- Memory Timing AnalysisDocument3 pagesMemory Timing AnalysisMANIKANDANPas encore d'évaluation

- Manchester EncodingDocument5 pagesManchester EncodingMANIKANDANPas encore d'évaluation

- Lpc2148 DatasheetDocument38 pagesLpc2148 DatasheetSandeep ThompsonPas encore d'évaluation

- Jump and Branch InstructionsDocument1 pageJump and Branch InstructionsMANIKANDANPas encore d'évaluation

- DramDocument3 pagesDramMANIKANDANPas encore d'évaluation

- MicroC2 eCh15L08ARMDevelopmentToolsDocument39 pagesMicroC2 eCh15L08ARMDevelopmentToolsMANIKANDANPas encore d'évaluation

- SubroutinesDocument1 pageSubroutinesMANIKANDANPas encore d'évaluation

- 6800 Internal RegistersDocument3 pages6800 Internal RegistersMANIKANDANPas encore d'évaluation

- 6800 Address ModesDocument1 page6800 Address ModesMANIKANDANPas encore d'évaluation

- Formal Report 1: Arrange 10 Numbers in Ascending OrderDocument2 pagesFormal Report 1: Arrange 10 Numbers in Ascending OrderMANIKANDANPas encore d'évaluation

- Analogue To Digital Converters (ADC)Document3 pagesAnalogue To Digital Converters (ADC)MANIKANDANPas encore d'évaluation

- VHDL TutorialDocument68 pagesVHDL TutorialPedro Pablo Parra AlbaPas encore d'évaluation

- Electronics GuideDocument22 pagesElectronics GuideFernandes KennethPas encore d'évaluation

- Memory Timing AnalysisDocument3 pagesMemory Timing AnalysisMANIKANDANPas encore d'évaluation

- FT021/3 Computer Systems Summer 2004Document2 pagesFT021/3 Computer Systems Summer 2004MANIKANDANPas encore d'évaluation

- Program Control InstructionsDocument3 pagesProgram Control InstructionsMANIKANDANPas encore d'évaluation

- VHDL FSM Tutorial MY FIRST FSMDocument29 pagesVHDL FSM Tutorial MY FIRST FSMMANIKANDANPas encore d'évaluation

- FT021/3 Computer Systems Summer 2004Document2 pagesFT021/3 Computer Systems Summer 2004MANIKANDANPas encore d'évaluation

- Review QuestionsDocument4 pagesReview QuestionsMANIKANDANPas encore d'évaluation

- Address Modes in The 16F84Document2 pagesAddress Modes in The 16F84MANIKANDANPas encore d'évaluation

- Formal Report 1: Arrange 10 Numbers in Ascending OrderDocument2 pagesFormal Report 1: Arrange 10 Numbers in Ascending OrderMANIKANDANPas encore d'évaluation

- Numbering Systems TutorialDocument5 pagesNumbering Systems TutorialMANIKANDANPas encore d'évaluation

- Delay LoopsDocument2 pagesDelay LoopsMANIKANDANPas encore d'évaluation

- Fetch and ExecuteDocument2 pagesFetch and ExecuteMANIKANDANPas encore d'évaluation

- Using EcalDocument4 pagesUsing EcalMANIKANDANPas encore d'évaluation

- Introduction To Parallel PortsDocument5 pagesIntroduction To Parallel PortsMANIKANDANPas encore d'évaluation

- Pic16f8x PDFDocument126 pagesPic16f8x PDFGilberto MataPas encore d'évaluation

- Memory Timing AnalysisDocument3 pagesMemory Timing AnalysisMANIKANDANPas encore d'évaluation

- 6800 Internal RegistersDocument3 pages6800 Internal RegistersMANIKANDANPas encore d'évaluation

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Sirius 3rb2 DatasheetDocument25 pagesSirius 3rb2 DatasheetCesar IgamiPas encore d'évaluation

- A 256-Radix Crossbar Switch Using Mux-Matrix-Mux Folded-Clos TopologyDocument8 pagesA 256-Radix Crossbar Switch Using Mux-Matrix-Mux Folded-Clos TopologyTim (Dipayan) MazumdarPas encore d'évaluation

- AmgDocument9 pagesAmgSatishReddyPas encore d'évaluation

- Features Description: Non-Volatile Digital Programmable CapacitorDocument20 pagesFeatures Description: Non-Volatile Digital Programmable Capacitorjai_mann-1Pas encore d'évaluation

- Smartech Pricelist September 2016.09.01Document46 pagesSmartech Pricelist September 2016.09.01n_zeinounPas encore d'évaluation

- Us3873779 PDFDocument12 pagesUs3873779 PDFAlex PerezPas encore d'évaluation

- SF31-SF37 Won-Top ElectronicsDocument4 pagesSF31-SF37 Won-Top ElectronicsRudyXPPas encore d'évaluation

- An 41251Document8 pagesAn 41251Eng Alex SilvaPas encore d'évaluation

- Dumont 765 766 767 Oscilloscope FrameDocument63 pagesDumont 765 766 767 Oscilloscope FrameRon LeonardPas encore d'évaluation

- Introduction To Electrical EngineeringDocument895 pagesIntroduction To Electrical EngineeringSer 345Pas encore d'évaluation

- Partial Discharge - Open ElectricalDocument2 pagesPartial Discharge - Open ElectricalHerman DamanikPas encore d'évaluation

- Types of Electrical Splices & JointsDocument23 pagesTypes of Electrical Splices & JointsVic Aziz Gonowon BadiolaPas encore d'évaluation

- Microfabrication Technologies: MECH 466 Microelectromechanical SystemsDocument19 pagesMicrofabrication Technologies: MECH 466 Microelectromechanical SystemsMohana Sundaram Ma NiPas encore d'évaluation

- Fundamental Study of 2-Level and 3-Level Frequency ConvertersDocument5 pagesFundamental Study of 2-Level and 3-Level Frequency ConvertersAhmed BassamPas encore d'évaluation

- Summary of Ee QuestionsDocument15 pagesSummary of Ee Questionsermane awatPas encore d'évaluation

- MB85RC64TA: 64 K (8 K 8) Bit I CDocument28 pagesMB85RC64TA: 64 K (8 K 8) Bit I CRohit MorePas encore d'évaluation

- Orientation: Dr. Paul D. Franzon PurposesDocument9 pagesOrientation: Dr. Paul D. Franzon Purposesnvenkatesh485Pas encore d'évaluation

- Terracene 4 127 PDFDocument124 pagesTerracene 4 127 PDFMaxi De los SantosPas encore d'évaluation

- Noise NotesDocument89 pagesNoise NotesRaj AnPas encore d'évaluation

- EE6301-Digital Logic Circuits QBDocument7 pagesEE6301-Digital Logic Circuits QBariv2009Pas encore d'évaluation

- Boolean Algebra and Logic GatesDocument54 pagesBoolean Algebra and Logic GatesHarshaPas encore d'évaluation

- Unit-V Blocking Oscillators and Time Base Generators Two Marks Question & AnswerDocument3 pagesUnit-V Blocking Oscillators and Time Base Generators Two Marks Question & AnswerJayed Ahmed LaskarPas encore d'évaluation

- Lab 3Document7 pagesLab 3jisteelePas encore d'évaluation

- TT2148 SanyoDocument4 pagesTT2148 Sanyokhawar mukhtarPas encore d'évaluation

- TV Sound Power Amplifier-Tda1030: Youda Integrated CircuitDocument3 pagesTV Sound Power Amplifier-Tda1030: Youda Integrated CircuitJose M PeresPas encore d'évaluation

- ATV31H037N4A: Product Data SheetDocument3 pagesATV31H037N4A: Product Data SheetRim RimpingPas encore d'évaluation

- 500w Power Amplifier Circuit DiagramDocument6 pages500w Power Amplifier Circuit DiagramJoão Alberto0% (1)

- AN2838 Flyback Converter L6562ADocument22 pagesAN2838 Flyback Converter L6562Abetodias30Pas encore d'évaluation

- How-To Design LED 3 PDFDocument8 pagesHow-To Design LED 3 PDFGoutham EzhilarasuPas encore d'évaluation

- 84 - Insulated Gate Bipolar Transistors (Igbts)Document2 pages84 - Insulated Gate Bipolar Transistors (Igbts)Guillermo DelgadoPas encore d'évaluation