Académique Documents

Professionnel Documents

Culture Documents

DSPA 15d

Transféré par

Aravindha BhatCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

DSPA 15d

Transféré par

Aravindha BhatDroits d'auteur :

Formats disponibles

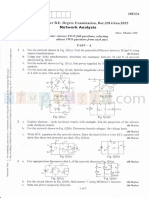

10EC751

USN

Seventh Semester B.E. Degree Examination, Dec.20l4/Jan.20l5

DSP Algorithms &

Architecture

Time: 3 hrs.

'

o

o

:''1,,

.,-.i,...

,,,'''

o.

CO

qJ

(,)

d

o

!

,"',,,, "...

c'

d.

3z

ur::

ua)

50tr

or:

6t

AE

N;

LO

6.Y

>\ (H

C

o{)

(J=

p. :i

tr>

o*

,,:: ,,

i,,i;

,,.r:,,,,,.a

..:j-

,:,

,,"

,.

,.

;i

(03 Marks)

1,.)

Derive tne''iilatonship between DFT and frequency responseijffii'also define frequency

resolution and'signpl record length.

(06 Marks)

An FFT is emplo,pd for determining the frequency co,q,pbfints of a random signal. It is

required that the iesotution of FFT to be <:5 Hz,,for;oa signal with fn,'u* : 1.25 kHz.

Determine i) Sampling."ialprval, TS.

ii) FFT length(,N) as a power of 2. i"j1';r',t

iii) Minimum sr$n4l pecord length. ' ,

(04 Marks)

'1li

,,::,,

:,:

::

:::

't

2 a.

b.

c.

Drawthestructureofa 4x4 Bram,,n'lqhiil[erandalsoexplainitsoperation. (08Marks)

Explain the pointer updating algorithm fbr circular addressing mode.

(08 Marks)

Compute the sequence in which th ,,.-i put data should be ordered for a 16 point DIT FFT

using Bit reversed addressing mode.

(04 Marks)

3 a.

Describe the following units of fffrfs:ZOC54XX processor: i) Barrel shifter iD Central

processing unit.

(0g Marks)

.,,,.,,t't".'

What is meant by addibssing mode? Explain the absolute,.accumulator, direct and indirect

addressing modes of fMS:ZOC54XX DSP processor.

(12 Marks)

!

..'"'',''..d,''..

,...'5;i

=::

o-;

o.v

o .-i

,,,.....:,...t

b.

P6

64

'O6

<)

pART - A

,ir1.,,,,,r.',,,

Max. Marks:100

_--.------

I a. Eiplainp digital signal processing system with the help of a block diagragr:'" (07 Marks)

b. List ih:,ihajor unique architecturil features

in any proqiqr-uble DSP devices.

--'- - implemented

----r --

c.r

=n

-*lt

doo

.=Nrid

oY:

og:

eO

Note: Answer FIVE full questions, selecting

at least TWO questions from each part.

4 a. Describe ,l::l.rilio1 .of tfe following instructions'

i) MAC *AR3-. xAR4+. B. A

ii) MAs

b.

,.

*AR3-, *AIt+, B, A

iii),RpTZ and RPTB.

,,,,,

E*filain the hardware timer of TMS320C54XX DSP with logical block diagr4m.

the pipe line operation of

TMS32}C54xxprocessor.

*.,,.*n*Otutn

a.

b.

;i cl

i)

iii)

iv)

v)

c.

1*

107

'rl ,'"lir.;

Marks)

PART_B

What is the significance of Q-notation in DSP?

Represent each of the following numbers in desired Q-notation format:

ii)

(.)

(06 Marks)

(07 Marks)

-352 as Qs number.

3.125 as Q7 number.

BDAFh in Q7 and Q15 number.

-0.160123 as Qrs number.

(04

Mafkt

,,:":

u,

4400h as Q6 number.

(06 Marks)

Explain with the help of block diagram and mathematical equations implementation of

decimation filter on TMS320C54XX processor.

(10 Marks)

I of2

10EC751

6 a.

b.

c.

..r

.,,.

' ,u,n;,,,

What minimum size FFT must be used to compute 500 points DFT? What must be done tc

(04 Marks)

the samples before the chosen FFT is applied?

(08 Marks)

FFT

butterfly.

for

the

DIT

factor

scaling

Derive the optimum

Write an assernbly language program for implementing following on TMS320C54XX

'lilr

pfOCeSSOr:

,,ur1L

i)

Bit reversed address

generation

"r;;=;",f;,1 ii) Spectrum of the transformed

.+:,

i*'

"

tt

qZ What

*9.

b.

data.

is an intemrpt? With a

processor.

,h,

^

neat flow chart explain handling of ,,:i4!emrpt by

,,,,

ll

,rF

Marks)

$MSSz0C54XX

_*, ,, lr;_' 1to

fitlw.does DMA help in increasing the speed of a DSP processor andplffiexnlain register

(10 Marks)

sub dffifpssing technique for configuring

DMA.

-.,.'0"

\,

reggffii

bio^telemetry

DSP

based

the

8 a. With nearblbbk diagram explain

',:F=.

b.

ffi,t*t

With neat

df@*tgtam

rj,,\

explain the CODEC interface

(10 Marks)

ctrcu;1.6"

circuitffi:'

:: .

:::

(10 Marks)

:::.

I .!n

,\.

t,

;\i.,::

:!i

.1r

f"Du!{s,

9"

.. fF tqp.

,.

,,,,

t 'd"''L

,::1nn

::]'":::::

Ss

-iii,1i,.

""qu,i

{!

siu.'.'l1*!,

?:,

.;;

+ ,{,-.r!

q,"q,j,

,

,,

'"4[t

o'"!i:,{i''

,

ii!l..;

"'q:"''li'

....:..:

of2

Vous aimerez peut-être aussi

- FakdisDocument12 pagesFakdisAravindha BhatPas encore d'évaluation

- Notes For C++Document3 pagesNotes For C++Aravindha BhatPas encore d'évaluation

- ReadmeDocument1 pageReadmeAravindha BhatPas encore d'évaluation

- Pic-Microcontroller Based Neural Network & Image Processing Controlled Low Cost Autonomous VehicleDocument4 pagesPic-Microcontroller Based Neural Network & Image Processing Controlled Low Cost Autonomous VehicleAravindha BhatPas encore d'évaluation

- Notes For C++Document2 pagesNotes For C++Aravindha BhatPas encore d'évaluation

- Ecsyll 5Document22 pagesEcsyll 5Swamy SlrPas encore d'évaluation

- ReadmeDocument1 pageReadmeAravindha BhatPas encore d'évaluation

- Notes For C++Document3 pagesNotes For C++Aravindha BhatPas encore d'évaluation

- I: What It Is, What It Isn't, and How To Use It: by Chris GlaserDocument7 pagesI: What It Is, What It Isn't, and How To Use It: by Chris GlaserAravindha BhatPas encore d'évaluation

- LabView OpportunitiesDocument1 pageLabView OpportunitiesAravindha BhatPas encore d'évaluation

- Chronological Resume Template 3Document1 pageChronological Resume Template 3Jaydeep BairagiPas encore d'évaluation

- 1 ScienceDocument2 pages1 ScienceAravindha BhatPas encore d'évaluation

- ReadmerDocument79 pagesReadmersatyajtiPas encore d'évaluation

- Clipper CircuitDocument27 pagesClipper CircuitAravindha BhatPas encore d'évaluation

- CH 08Document20 pagesCH 08Arpita PaulPas encore d'évaluation

- CH 08Document20 pagesCH 08Arpita PaulPas encore d'évaluation

- Contoh COPYRIGHT TugasDocument1 pageContoh COPYRIGHT TugasBenyNoerBackbonePas encore d'évaluation

- Hilarious Clean Jokes and Funny Stories CollectionDocument22 pagesHilarious Clean Jokes and Funny Stories CollectionHari BabooPas encore d'évaluation

- Aerodynamics Drag Forces on ObjectsDocument5 pagesAerodynamics Drag Forces on ObjectsAravindha BhatPas encore d'évaluation

- The World's Greatest Collection of Clean Jokes PDFDocument16 pagesThe World's Greatest Collection of Clean Jokes PDFAravindha BhatPas encore d'évaluation

- Ordered StructuresDocument25 pagesOrdered StructuresAravindha BhatPas encore d'évaluation

- Hilarious Clean Jokes and Funny Stories CollectionDocument22 pagesHilarious Clean Jokes and Funny Stories CollectionHari BabooPas encore d'évaluation

- Field Theory QPDocument3 pagesField Theory QPAravindha BhatPas encore d'évaluation

- Analog Communication NotesDocument73 pagesAnalog Communication NotesAravindha Bhat100% (1)

- Aerodynamics Drag Forces on ObjectsDocument5 pagesAerodynamics Drag Forces on ObjectsAravindha BhatPas encore d'évaluation

- Fourier TransformsDocument23 pagesFourier TransformsAravindha BhatPas encore d'évaluation

- Microprocessors 8086 (Notes)Document29 pagesMicroprocessors 8086 (Notes)Aravindha BhatPas encore d'évaluation

- Independence Day President's SpeechDocument2 pagesIndependence Day President's SpeechAravindha BhatPas encore d'évaluation

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Isaca: Cobit Assessment Programme (PAM) Tool Kit: Using COBIT 5Document2 pagesIsaca: Cobit Assessment Programme (PAM) Tool Kit: Using COBIT 5lgaleanoc0% (1)

- Social Media: A Powerpoint PresentationDocument35 pagesSocial Media: A Powerpoint PresentationSimon OvidiuPas encore d'évaluation

- SPM TRIAL 2019 - Melaka - P2 PDFDocument18 pagesSPM TRIAL 2019 - Melaka - P2 PDFS SuhaidanPas encore d'évaluation

- "Viewer's Perception Towards OTT Platform" Questionnaire: Name: - AgeDocument3 pages"Viewer's Perception Towards OTT Platform" Questionnaire: Name: - AgeNaman LadhaPas encore d'évaluation

- Hero Honda - Erp SystemDocument10 pagesHero Honda - Erp SystemKaran Gaur0% (1)

- Project ReportDocument56 pagesProject ReportAstha MishraPas encore d'évaluation

- Influenceof ICTin Mathematics TeachingDocument6 pagesInfluenceof ICTin Mathematics TeachingGrasya M.Pas encore d'évaluation

- Full Flow Type Reverse Circulation Junk Basket: Instruction Manual 3105Document10 pagesFull Flow Type Reverse Circulation Junk Basket: Instruction Manual 3105Foros IscPas encore d'évaluation

- Reservoir Structure Planning and Construction MethodsDocument9 pagesReservoir Structure Planning and Construction MethodssinggihPas encore d'évaluation

- Amada Operators ManualDocument110 pagesAmada Operators ManualJeff Dunn86% (7)

- Activation Functions in Neural Networks - GeeksforGeeksDocument12 pagesActivation Functions in Neural Networks - GeeksforGeekswendu felekePas encore d'évaluation

- Systems Manual Simatic ET200S PDFDocument666 pagesSystems Manual Simatic ET200S PDFpandhuPas encore d'évaluation

- Product Recommendation Hyster Forklift Trucks, Diesel H2.5FT Yanmar 4TNE92 (2005 and After)Document1 pageProduct Recommendation Hyster Forklift Trucks, Diesel H2.5FT Yanmar 4TNE92 (2005 and After)Nelson ConselhoPas encore d'évaluation

- Carbon DLS™ 3D Printing Process Engineering Handbook: Updated 06.24.2022Document56 pagesCarbon DLS™ 3D Printing Process Engineering Handbook: Updated 06.24.2022JordiPas encore d'évaluation

- Examen de AWS Certified Cloud Practitioner - PAG18Document5 pagesExamen de AWS Certified Cloud Practitioner - PAG18ALEJANDRO ALZATE ARIASPas encore d'évaluation

- Mark Java ResumeDocument4 pagesMark Java ResumesravanpaulPas encore d'évaluation

- 1SLC009000D0201 CT Combiner LRDocument52 pages1SLC009000D0201 CT Combiner LRJimmy F HernandezPas encore d'évaluation

- 041157X99Z RE18318-20 CompressedDocument2 pages041157X99Z RE18318-20 CompressedmhasansharifiPas encore d'évaluation

- Cambridge International AS & A Level: Information Technology 9626/04 May/June 2022Document13 pagesCambridge International AS & A Level: Information Technology 9626/04 May/June 2022Muhammad MuddassirPas encore d'évaluation

- Turbine Gland Steam CondenserDocument4 pagesTurbine Gland Steam CondenserSai Swaroop100% (1)

- Test of Mathematics For University Admission: Paper 1 2018 Worked AnswersDocument25 pagesTest of Mathematics For University Admission: Paper 1 2018 Worked AnswersNguyễn Hoàng AnPas encore d'évaluation

- Question: Use QGIS With Example Pictures/drawings/sketches ExplainDocument3 pagesQuestion: Use QGIS With Example Pictures/drawings/sketches ExplaintahaPas encore d'évaluation

- Safe Transportation System: A Project Submitted byDocument29 pagesSafe Transportation System: A Project Submitted byshahinPas encore d'évaluation

- 64cc7d3e2b60ad241835f230 - Marshall 8 - EN - Web - 0804Document2 pages64cc7d3e2b60ad241835f230 - Marshall 8 - EN - Web - 0804ahmed gazzarPas encore d'évaluation

- Name Popescu Daniel-Nutu: Personal DetailsDocument3 pagesName Popescu Daniel-Nutu: Personal DetailsToma Liviu AlexandruPas encore d'évaluation

- Railway Operational Communication Solution GTSOFTX3000V200R001C01 Product Description V1.0 (20130311)Document89 pagesRailway Operational Communication Solution GTSOFTX3000V200R001C01 Product Description V1.0 (20130311)Leonardo MorallosPas encore d'évaluation

- POLYCAB - MV Power Cable IEC 60502 2Document32 pagesPOLYCAB - MV Power Cable IEC 60502 2AmitabhaPas encore d'évaluation

- Naylor 1974Document18 pagesNaylor 1974Mario Colil BenaventePas encore d'évaluation

- P34x EN MD M96 V35+V70 Incl P341Document163 pagesP34x EN MD M96 V35+V70 Incl P341tandin.t6393Pas encore d'évaluation

- EPOXY FINISH PAINT - FiveDocument4 pagesEPOXY FINISH PAINT - FiveR K Heavy Engineering Private LimitedPas encore d'évaluation