Académique Documents

Professionnel Documents

Culture Documents

54ACT283 4-Bit Binary Full Adder With Fast Carry: General Description Features

Transféré par

ΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

54ACT283 4-Bit Binary Full Adder With Fast Carry: General Description Features

Transféré par

ΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣDroits d'auteur :

Formats disponibles

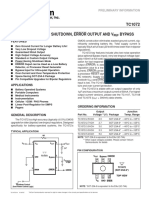

54ACT283

4-Bit Binary Full Adder with Fast Carry

General Description

Features

The ACT283 high-speed 4-bit binary full adder with internal

carry lookahead accepts two 4-bit binary words (A0A3,

B0B3) and a Carry input (C0). It generates the binary Sum

outputs (S0S3) and the Carry output (C4) from the most significant bit. The ACT283 will operate with either active HIGH

or active LOW operands (positive or negative logic).

n

n

n

n

Logic Symbols

Guaranteed 4000V minimum ESD protection

Outputs source/sink 24 mA

TTL-compatible inputs

Available to Mil-Std-883

Pin Assignment for LCC

DS100977-1

IEEE/IEC

DS100977-3

Functional Description

The ACT283 adds two 4-bit binary words (A plus B) plus the

incoming Carry (C0). The binary sum appears on the Sum

(S0S3) and outgoing carry (C4) outputs. The binary weight

of the various inputs and outputs is indicated by the subscript

numbers, representing powers of two.

20 (A0 + B0 + C0) + 21 (A1 + B1)

DS100977-4

Connection Diagrams

Pin Assignment

for DIP and Flatpak

DS100977-2

1998 National Semiconductor Corporation

DS100977

+ 22 (A2 + B2) + 23 (A3 + B3)

= S0 + 2S1 + 4S2 + 8S3 + 16C4

Where (+) = plus

Interchanging inputs of equal weight does not affect the operation. Thus C0, A0, B0 can be arbitrarily assigned to pins 5,

6 and 7 for DIPS, and 7, 8 and 9 for chip carrier packages.

Due to the symmetry of the binary add function, the ACT283

can be used either with all inputs and outputs active HIGH

(positive logic) or with all inputs and outputs active LOW

(negative logic). See Figure 1. Note that if C0 is not used it

must be tied LOW for active HIGH logic or tied HIGH for active LOW logic.

Due to pin limitations, the intermediate carries of the

ACT283 are not brought out for use as inputs or outputs.

However, other means can be used to effectively insert a

carry into, or bring a carry out from, an intermediate stage.

Figure 2 shows how to make a 3-bit adder. Tying the operand inputs of the fourth adder (A3, B3) LOW makes S3 dependent only on, and equal to, the carry from the third adder.

Using somewhat the same principle, Figure 3 shows a way

of dividing the ACT283 into a 2-bit and a 1-bit adder. The

third stage adder (A2, B2, S2) is used merely as a means of

getting a carry (C10) signal into the fourth stage (via A2 and

B2) and bringing out the carry from the second stage on S2.

www.national.com

54ACT283 4-Bit Binary Full Adder with Fast Carry

September 1998

Functional Description

equally weighted. The outputs S0, S1 and S2 present a binary number equal to the number of inputs I1I5 that are

true. Figure 5 shows one method of implementing a 5-input

majority gate. When three or more of the inputs I1I5 are

true, the output M5 is true.

(Continued)

Note that as long as A2 and B2 are the same, whether HIGH

or LOW, they do not influence S2. Similarly, when A2 and B2

are the same the carry into the third stage does not influence

the carry out of the third stage. Figure 4 shows a method of

implementing a 5-input encoder, where the inputs are

C0

A0

A1

A2

A3

B0

B1

B2

B3

S0

S1

S2

S3

C4

Logic Levels

Active HIGH

Active LOW

Active HIGH: 0 + 10 + 9 = 3 + 16

Active LOW: 1 + 5 + 6 = 12 + 0

FIGURE 1. Active HIGH versus Active LOW Interpretation

DS100977-5

FIGURE 2. 3-Bit Adder

DS100977-7

FIGURE 4. 5-Input Encoder

DS100977-6

FIGURE 3. 2-Bit and 1-Bit Adders

DS100977-8

FIGURE 5. 5-Input Majority Gate

www.national.com

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

DS100977-9

Logic Diagram

www.national.com

Absolute Maximum Ratings (Note 1)

3-STATE Output

Current Applied to Output

in LOW State (Max)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Storage Temperature

Ambient Temperature under Bias

Junction Temperature under Bias

VCC Pin Potential to

Ground Pin

Input Voltage (Note 2)

Input Current (Note 2)

Voltage Applied to Output

in HIGH State (with VCC = 0V)

Standard Output

0.5V to +5.5V

twice the rated IOL (mA)

Recommended Operating

Conditions

65C to +150C

55C to +125C

55C to +175C

Free Air Ambient Temperature

Military

Supply Voltage

Military

0.5V to +7.0V

0.5V to +7.0V

30 mA to +5.0 mA

55C to +125C

+4.5V to +5.5V

Note 1: Absolute maximum ratings are values beyond which the device may

be damaged or have its useful life impaired. Functional operation under these

conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

0.5V to VCC

DC Electrical Characteristics for ACT Family Devices

Symbol

VIH

VIL

VOH

Parameter

VCC

TA = 55C to +125C

(V)

Guaranteed Limits

Minimum High Level

4.5

2.0

Input Voltage

5.5

2.0

Maximum Low Level

4.5

0.8

Input Voltage

5.5

0.8

Minimum High Level

4.5

4.4

Output Voltage

5.5

5.4

4.5

3.7

5.5

4.7

Units

Conditions

VOUT = 0.1V

or VCC 0.1V

VOUT = 0.1V

or VCC 0.1V

IOUT = 50 A

VIN = V

VOL

Maximum Low Level

4.5

0.1

Output Voltage

5.5

0.1

4.5

0.5

Maximum Input

or VIH

IOH = 24 mA

IOH = 24 mA

(Note 3)

IOUT = 50 A

VIN = V

IIN

IL

IL

or VIH

IOL = 24 mA

5.5

0.5

5.5

1.0

IOL = 24 mA (Note 3)

VI = V CC, GND

5.5

1.6

mA

VI = V

5.5

50

mA

VOLD = 1.65V Max

5.5

50

mA

VOHD = 3.85V Min

5.5

160.0

VIN = V

Leakage Current

ICCT

Maximum

CC

2.1V

ICC/Input

IOLD

IOHD

Minimum Dynamic

Output Current

(Note 4)

ICC

Maximum Quiescent

Supply Current

or GND

Note 3: All outputs loaded; thresholds on input associated with output under test.

Note 4: Maximum test duration 2.0 ms, one output loaded at a time.

www.national.com

CC

AC Electrical Characteristics for ACT Family Devices

Symbol

54ACT

TA, VCC = Mil

CL = 50 pF

Parameter

Min

Units

Max

tPLH

Propagation Delay

2.5

14.0

tPHL

C0 to Sn

2.5

14.0

tPLH

Propagation Delay

2.0

17.0

tPHL

An or Bn to Sn

2.0

17.0

tPLH

Propagation Delay

2.5

10.0

tPHL

C0 to C4

2.5

11.0

tPLH

Propagation Delay

2.5

10.5

tPHL

An or Bn to C4

2.5

11.5

ns

ns

ns

ns

www.national.com

Physical Dimensions

inches (millimeters) unless otherwise noted

20-Lead Ceramic Leadless Chip Carrier (L)

Package Number E20A

16-Lead Ceramic Dual-In-Line Package (D)

Package Number J16A

www.national.com

54ACT283 4-Bit Binary Full Adder with Fast Carry

Physical Dimensions

inches (millimeters) unless otherwise noted (Continued)

16-Lead Ceramic Flatpak (F)

Package Number W16A

LIFE SUPPORT POLICY

NATIONALS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

2. A critical component in any component of a life support

1. Life support devices or systems are devices or sysdevice or system whose failure to perform can be reatems which, (a) are intended for surgical implant into

sonably expected to cause the failure of the life support

the body, or (b) support or sustain life, and whose faildevice or system, or to affect its safety or effectiveness.

ure to perform when properly used in accordance

with instructions for use provided in the labeling, can

be reasonably expected to result in a significant injury

to the user.

National Semiconductor

Corporation

Americas

Tel: 1-800-272-9959

Fax: 1-800-737-7018

Email: support@nsc.com

www.national.com

National Semiconductor

Europe

Fax: +49 (0) 1 80-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 1 80-530 85 85

English Tel: +49 (0) 1 80-532 78 32

Franais Tel: +49 (0) 1 80-532 93 58

Italiano Tel: +49 (0) 1 80-534 16 80

National Semiconductor

Asia Pacific Customer

Response Group

Tel: 65-2544466

Fax: 65-2504466

Email: sea.support@nsc.com

National Semiconductor

Japan Ltd.

Tel: 81-3-5620-6175

Fax: 81-3-5620-6179

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

Vous aimerez peut-être aussi

- Electronics Explained: Fundamentals for Engineers, Technicians, and MakersD'EverandElectronics Explained: Fundamentals for Engineers, Technicians, and MakersÉvaluation : 5 sur 5 étoiles5/5 (5)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Pas encore d'évaluation

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Évaluation : 2.5 sur 5 étoiles2.5/5 (3)

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosD'EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosÉvaluation : 5 sur 5 étoiles5/5 (1)

- Electroculture 101 (1st Edition)Document48 pagesElectroculture 101 (1st Edition)Taiwo Phillips85% (13)

- G.I. 2.721 - Electrical Arc Flash Mitigation PDFDocument15 pagesG.I. 2.721 - Electrical Arc Flash Mitigation PDFJoypee Macasampon100% (6)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxD'EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxÉvaluation : 4 sur 5 étoiles4/5 (2)

- HV Insulations Comp.190310Document24 pagesHV Insulations Comp.190310M V Ravindra MutyalaPas encore d'évaluation

- 01-Synchronous Motor PDFDocument48 pages01-Synchronous Motor PDFGeneral ZodPas encore d'évaluation

- Temperature Compensated Battery State-Of-Charge (Soc) Table 1.1Document8 pagesTemperature Compensated Battery State-Of-Charge (Soc) Table 1.1Nadeem MirzaPas encore d'évaluation

- IB DP Physics Past Papers Waves QnsDocument21 pagesIB DP Physics Past Papers Waves QnsJessica GuyPas encore d'évaluation

- Digital Signal Processing Using the ARM Cortex M4D'EverandDigital Signal Processing Using the ARM Cortex M4Évaluation : 1 sur 5 étoiles1/5 (1)

- J1939 15 PDFDocument19 pagesJ1939 15 PDFMauro100% (3)

- CNHT'2022Document4 pagesCNHT'2022Talhi Mama0% (1)

- M. Standard Stock Materials For 33kV SystemDocument9 pagesM. Standard Stock Materials For 33kV SystemSandesh PattanashettiPas encore d'évaluation

- 74LS573Document6 pages74LS573Sinué RamírezPas encore d'évaluation

- 4-Bit Binary Adders with Fast Carry Technical DocumentDocument9 pages4-Bit Binary Adders with Fast Carry Technical DocumentZavala DavidPas encore d'évaluation

- 74573Document4 pages74573jamesrychurdPas encore d'évaluation

- 74LS573Document6 pages74LS573Negru P. PlantatiePas encore d'évaluation

- I. 7-Segment Display: Elektronski Fakultet Katedra Za MikroelektronikuDocument39 pagesI. 7-Segment Display: Elektronski Fakultet Katedra Za MikroelektronikuMaki MakicPas encore d'évaluation

- 74LS283Document4 pages74LS283tongers23Pas encore d'évaluation

- Low Voltage Cmos Dual 2 To 4 Decoder/Demultiplexer: Table 1: Order CodesDocument13 pagesLow Voltage Cmos Dual 2 To 4 Decoder/Demultiplexer: Table 1: Order CodesMohammad SoltanmohammadiPas encore d'évaluation

- 74 Ls 390Document6 pages74 Ls 390Yoga AdiPas encore d'évaluation

- 54ABT240 Octal Buffer/Line Driver With TRI-STATE Outputs: General DescriptionDocument8 pages54ABT240 Octal Buffer/Line Driver With TRI-STATE Outputs: General Descriptionmeroka2000Pas encore d'évaluation

- MC74HC541A Octal 3-State Non-Inverting Buffer/Line Driver/ Line ReceiverDocument8 pagesMC74HC541A Octal 3-State Non-Inverting Buffer/Line Driver/ Line ReceivernandobnuPas encore d'évaluation

- 74LVC08A: Low Voltage Cmos Quad 2-Input and Gate High PerformanceDocument11 pages74LVC08A: Low Voltage Cmos Quad 2-Input and Gate High PerformanceFernando QueirozPas encore d'évaluation

- Ai820 PDFDocument12 pagesAi820 PDFRaj ChavanPas encore d'évaluation

- PLC AutomationDocument13 pagesPLC AutomationVamsi KumarPas encore d'évaluation

- 74LS393-Dual 4-Bit Binary CounterDocument6 pages74LS393-Dual 4-Bit Binary Counterkakashi116Pas encore d'évaluation

- 4-Bit Binary Full Adder With Fast Carry SN54/74LS283: Low Power SchottkyDocument5 pages4-Bit Binary Full Adder With Fast Carry SN54/74LS283: Low Power SchottkyItalo QuirozPas encore d'évaluation

- DM9368 7-Segment Decoder/Driver/Latch With Constant Current Source OutputsDocument9 pagesDM9368 7-Segment Decoder/Driver/Latch With Constant Current Source OutputsJose Antonio J DiazPas encore d'évaluation

- DM74ALS373 Octal D-Type TRI-STATE Transparent Latch SpecsDocument6 pagesDM74ALS373 Octal D-Type TRI-STATE Transparent Latch SpecsEduardo Monge JiménezPas encore d'évaluation

- Demp Lab ManualDocument50 pagesDemp Lab ManualNishant AcharyaPas encore d'évaluation

- Automatic Industrial Control LaboratoryDocument21 pagesAutomatic Industrial Control Laboratorytarottaurus54Pas encore d'évaluation

- Nc7Sz373 Tinylogic Uhs D-Type Latch With 3-State Output: General Description FeaturesDocument9 pagesNc7Sz373 Tinylogic Uhs D-Type Latch With 3-State Output: General Description Featuresgreentea601Pas encore d'évaluation

- IL AI 8 V2 1x 001Document9 pagesIL AI 8 V2 1x 001John EvansPas encore d'évaluation

- 170 ADI 350 00 - 32 Pt. Discrete Input Module OverviewDocument14 pages170 ADI 350 00 - 32 Pt. Discrete Input Module OverviewGabriel ZorattiPas encore d'évaluation

- Digital Design Lab ExperimentsDocument11 pagesDigital Design Lab ExperimentsThịnh PhanPas encore d'évaluation

- Analog ModuleDocument13 pagesAnalog ModuleNgọc Đặng VănPas encore d'évaluation

- Dual 4-Bit Binary Counter DatasheetDocument6 pagesDual 4-Bit Binary Counter Datasheetjnax101Pas encore d'évaluation

- Objectives: Experiment 1 Combinational LogicDocument12 pagesObjectives: Experiment 1 Combinational LogicWannaAdnanPas encore d'évaluation

- Lab4 - Digital CircuitDocument12 pagesLab4 - Digital CircuitKIÊN ĐẶNG TRUNGPas encore d'évaluation

- Lab 3A Interfacing Adc804 To The 8051 TrainerDocument4 pagesLab 3A Interfacing Adc804 To The 8051 Trainerramnag4Pas encore d'évaluation

- Lab 2Document4 pagesLab 2Azliana Mohd TaibPas encore d'évaluation

- 7485 Comparador DatasheetDocument9 pages7485 Comparador DatasheetJuan Ramírez SPas encore d'évaluation

- 7Z08Document7 pages7Z08André Frota PaivaPas encore d'évaluation

- All About TTL Ic 258Document7 pagesAll About TTL Ic 258AraoFilhoPas encore d'évaluation

- 74LS11Document7 pages74LS11TrungHiếuPas encore d'évaluation

- MM74HC245A Octal 3-STATE Transceiver: General DescriptionDocument7 pagesMM74HC245A Octal 3-STATE Transceiver: General DescriptionMubarak CePas encore d'évaluation

- DM7474 Dual Positive-Edge-Triggered D Flip-Flops With Preset, Clear and Complementary OutputsDocument6 pagesDM7474 Dual Positive-Edge-Triggered D Flip-Flops With Preset, Clear and Complementary OutputsJuan JoachinPas encore d'évaluation

- DM7414 Hex Inverter With Schmitt Trigger Inputs: General DescriptionDocument6 pagesDM7414 Hex Inverter With Schmitt Trigger Inputs: General DescriptionGeorge Rahul PaulPas encore d'évaluation

- R6510C - IEC 870 Interface GuideDocument12 pagesR6510C - IEC 870 Interface GuideBehzadPas encore d'évaluation

- MC44BC380Document10 pagesMC44BC380judas_priest_12345Pas encore d'évaluation

- MPMC Sample FileDocument64 pagesMPMC Sample FileAakritiPas encore d'évaluation

- Calibrate Digital Multimeter ProcedureDocument15 pagesCalibrate Digital Multimeter ProcedureluroguitaPas encore d'évaluation

- General Description: Dual Supply Translating Transceiver Auto Direction Sensing 3-StateDocument26 pagesGeneral Description: Dual Supply Translating Transceiver Auto Direction Sensing 3-StateJimChenPas encore d'évaluation

- 74164Document6 pages74164luisalex87Pas encore d'évaluation

- Encs211 Experiment 3Document17 pagesEncs211 Experiment 3Prince IshtaPas encore d'évaluation

- 74ls245 (3-State Octal Bus Transceiver)Document7 pages74ls245 (3-State Octal Bus Transceiver)thanhdang8xPas encore d'évaluation

- BMX EHC 0800 Module Wiring GuideDocument3 pagesBMX EHC 0800 Module Wiring GuideJeffery CladiusPas encore d'évaluation

- SN74LS85 4-Bit Magnitude Comparator: LOW Power SchottkyDocument9 pagesSN74LS85 4-Bit Magnitude Comparator: LOW Power SchottkygbrsylarPas encore d'évaluation

- Datasheet 74153Document17 pagesDatasheet 74153Ingga Permana0% (1)

- Tda 8177Document9 pagesTda 8177dinspekPas encore d'évaluation

- 10V Isolated Analog Input Module Specs and InstallationDocument4 pages10V Isolated Analog Input Module Specs and InstallationXa MauPas encore d'évaluation

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142D'EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142Pas encore d'évaluation

- Microelectronic Systems N2 Checkbook: The Checkbook SeriesD'EverandMicroelectronic Systems N2 Checkbook: The Checkbook SeriesPas encore d'évaluation

- Types MC and MCN Multilayer RF Capacitors High-Frequency OptionsDocument9 pagesTypes MC and MCN Multilayer RF Capacitors High-Frequency OptionsΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data SheetDocument16 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Types MC and MCN Multilayer RF Capacitors High-Frequency OptionsDocument9 pagesTypes MC and MCN Multilayer RF Capacitors High-Frequency OptionsΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data SheetDocument8 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data Sheet 1Document17 pagesData Sheet 1ΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data SheetDocument19 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- 3.3 V Ecl/Pecl/Hstl/Lvds: ÷2/4, ÷4/5/6 Clock Generation ChipDocument12 pages3.3 V Ecl/Pecl/Hstl/Lvds: ÷2/4, ÷4/5/6 Clock Generation ChipΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Axial Leads/Spinguard: General DescriptionDocument6 pagesAxial Leads/Spinguard: General DescriptionΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data SheetDocument9 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Datasheet TL082 PDFDocument11 pagesDatasheet TL082 PDFJavier RenanPas encore d'évaluation

- TC1072 50ma Cmos Ldo With Shutdown, Error Output and V BypassDocument12 pagesTC1072 50ma Cmos Ldo With Shutdown, Error Output and V BypassΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data SheetDocument12 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data SheetDocument4 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- VN0610LL FET Transistor: N Channel - EnhancementDocument4 pagesVN0610LL FET Transistor: N Channel - EnhancementΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- LM1117Document21 pagesLM1117dipankaborahPas encore d'évaluation

- DMTH6004SPS: 60V 175°C N-Channel Enhancement Mode Mosfet PowerdiDocument7 pagesDMTH6004SPS: 60V 175°C N-Channel Enhancement Mode Mosfet PowerdiΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data SheetDocument6 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- CD 4023Document12 pagesCD 4023giorgio19741Pas encore d'évaluation

- AX97 Series: SMD Power InductorsDocument3 pagesAX97 Series: SMD Power InductorsΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Wall Plug Ins Electrical SpecsDocument1 pageWall Plug Ins Electrical SpecsΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Patented : SM6S10 Thru SM6S36ADocument5 pagesPatented : SM6S10 Thru SM6S36AΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data SheetDocument4 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data SheetDocument16 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- 8K Microwire Compatible Serial EEPROM: 93AA76A/B/C, 93LC76A/B/C, 93C76A/B/CDocument26 pages8K Microwire Compatible Serial EEPROM: 93AA76A/B/C, 93LC76A/B/C, 93C76A/B/CΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣ100% (1)

- Ece206l SyllDocument7 pagesEce206l SyllBlaze MoorePas encore d'évaluation

- Thesis On Power Quality Improvement Using DstatcomDocument5 pagesThesis On Power Quality Improvement Using DstatcomheatherricedesmoinesPas encore d'évaluation

- Parts List for SPW-CR253EHL8-E Air Conditioner Outdoor UnitDocument4 pagesParts List for SPW-CR253EHL8-E Air Conditioner Outdoor UnitDavid Lemos SanchezPas encore d'évaluation

- Mini Project EEE PDFDocument7 pagesMini Project EEE PDFAmit Kr SinghPas encore d'évaluation

- Leshan Radio Company EGP10A thru EGP10M RectifiersDocument3 pagesLeshan Radio Company EGP10A thru EGP10M RectifiersCarlos AntonioPas encore d'évaluation

- (ELECS2) Exp5 - Class A and Class B Power Amplifier - The GWAPINGSDocument12 pages(ELECS2) Exp5 - Class A and Class B Power Amplifier - The GWAPINGSFrodolfre Reginald LazoPas encore d'évaluation

- 1506D Industrial Engines Electrical System: This Document Has Been Printed From SPI2. NOT FOR RESALEDocument2 pages1506D Industrial Engines Electrical System: This Document Has Been Printed From SPI2. NOT FOR RESALEmohammed mostafaPas encore d'évaluation

- SX80Document8 pagesSX80ColysaPas encore d'évaluation

- 22 MM Push Buttons XB4 Electrical Components: Table 19.89: Body/Mounting CollarDocument2 pages22 MM Push Buttons XB4 Electrical Components: Table 19.89: Body/Mounting CollarMohammed AbdelsalamPas encore d'évaluation

- Ina 110 BGDocument11 pagesIna 110 BGroberto cabreraPas encore d'évaluation

- Internal Resistance IA PDFDocument10 pagesInternal Resistance IA PDFtuvvacPas encore d'évaluation

- Es100 120 Izt40Document64 pagesEs100 120 Izt40Le TamPas encore d'évaluation

- Clean Energy Trainer Experiment GuideDocument9 pagesClean Energy Trainer Experiment GuidePantheia DadpouPas encore d'évaluation

- Ghana Technology University College: Duration:1Hr Section ADocument11 pagesGhana Technology University College: Duration:1Hr Section ANana Agyeman AntwiPas encore d'évaluation

- Complete Syllabus of Class XI & XII: Physics (Document6 pagesComplete Syllabus of Class XI & XII: Physics (Abhijeet ParkhiPas encore d'évaluation

- The Thermoelectric GeneratorDocument8 pagesThe Thermoelectric GeneratorSayed MesallamyPas encore d'évaluation

- Pre-Medical: Physics Allen: Exercise-IDocument6 pagesPre-Medical: Physics Allen: Exercise-IYOYO 1290Pas encore d'évaluation

- Yellow Shaded Questions Are Selected From Ktu Qps Dec 2019, May 2019, Dec 2018Document18 pagesYellow Shaded Questions Are Selected From Ktu Qps Dec 2019, May 2019, Dec 2018ABHIRAM K REJIKUMAR EE19-23Pas encore d'évaluation

- Remediasi Tanah Terkontaminasi Logam Berat Krom (CR) Dengan Teknik Remediasi ElektrokinetikDocument15 pagesRemediasi Tanah Terkontaminasi Logam Berat Krom (CR) Dengan Teknik Remediasi Elektrokinetikfajarbayu prassetyoPas encore d'évaluation

- Lap Report 6 Phy 2Document5 pagesLap Report 6 Phy 2ahmed albualiPas encore d'évaluation