Académique Documents

Professionnel Documents

Culture Documents

Low Power

Transféré par

Anonymous TEWarptvjTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Low Power

Transféré par

Anonymous TEWarptvjDroits d'auteur :

Formats disponibles

Power consumption in CMOS

There are basically

two types of power

consumption in

CMOS

1) Dynamic Power

2) Static Power

(Leakage power)

14/04/15

Dynamic Power

Dynamic power is power consumed by the cell

whenever output changes its value (0 to 1 or 1 to

0)

Consists of two main parts

Switching power(Pswiching)

Internal power(PInternal )

14/04/15

Switching power

Switching power results from the

charging and discharging of the

external capacitive load on the output

of the cell

VDD

S

G

D

G

S

GND

14/04/15

CL

Internal power

14/04/15

Power consumed during short period when

input signal is transitioning, during which

both the PMOS and NMOS transistors can

be conducting

Large current called crowbar or short

circuit current flows from VDD to VSS

Static Power (Leakage power)

14/04/15

The leakage power is consumed by the circuit when the output is at stable

state

Main components:

Gate leakage current

The current that flows directly from the gate

through the oxide to the

substrate due to gate oxide tunneling and hot carrier injection

Sub threshold leakage current

The current that flows from drain to source of a transistor operating in the

weak inversion region

Reverse bias PN junction leakage current

The current that results due to minority carrier drift and generation of

electron/hole pair in the depletion regions

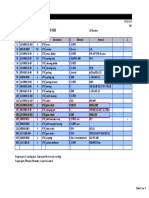

Leakage current components

Leakage current comprises of the following

components

14/04/15

Why Low power ?

Increasing cell count ---> Increasing power

Higher frequencies ---> Increasing power

Smaller geometries ---> Increasing leakage

power

14/04/15

Power reduction techniques

The power has two main components

Dynamic power

Static power (Leakage power)

14/04/15

Dynamic power reduction techniques

Dynamic power is mainly a function of the

supply voltage, output load (Cload) , Frequency

and switching activity of a cell

Reducing any of the above component will

result in the reduction of the dynamic power

There are several techniques employed in

ASIC as following

1) Clock gating

2) Multiple voltage design

3) Dynamic voltage and frequency scaling

(DVFS)

14/04/15

Clock Gating

Clock gating is used to reduce the

switching activity of the clocks at

selected FF's input and thereby

reducing the dynamic power

Clock gating inserts

combinational logic on clock path

to conditionally stop the clock at

FFs inputs

This technique reduces the

dynamic power consumption

14/04/15

Design after clock gating

Q

Input

Enable

clock

D

CK

Multiple Voltage Design

14/04/15

Reducing the supply voltage reduces the power consumption

exponentially

Selectively providing different voltages to different blocks depending on

their performance requirement reduces the power

Reducing voltage also increases delay

Apply higher voltages to the timing critical blocks

Apply lower voltages to the non timing critical blocks

Create voltage islands in the chip area

Needs level shifters at the interfaces of the voltage islands

Multiple Voltage Design

Level shifters are needed at the

block interface to convert the

voltage levels for the receiving

blocks

Needed to make sure the valid

voltage levels for receiving blocks

For signals going from low voltage

block to high voltage block a low to

high level shifter is needed and it

should be placed in high voltage

block

For signals going from high voltage

block to low voltage block a high to

level shifter is needed and it should

be in low voltage block

14/04/15

LOW TO HIGH

LEVEL SHIFTER

LOW

VOLTAGE

BLOCK

HIGH TO LOW

LEVEL SHIFTER

HIGH

VOLTAGE

BLOCK

Multi-Voltage design Example

CPU And RAM operating on

Higher frequency

Hence operated at Higher

voltages

Peripherals operating on

lower frequency

Hence operated at lower Voltage

Level shifters are inserted in

respective domains at block

interfaces

VDD1 = 1.8V

CPU

Higher

voltage

RAM

Higher

voltage

GND=0V

14/04/15

VDD2= 1.2V

Peripherals

Lower voltage

Dynamic voltage and frequency scaling.

14/04/15

Dynamically changing the voltage and the

frequency of the chip depending on the work

load

Reduces dynamic power significantly

14/04/15

Static (Leakage) power reduction techniques

Multi Vt

Power gating

14/04/15

Multi-Vt

14/04/15

Requires libraries having multiple Vt cells

High Vt cells: More delay, Less leakage

Low Vt cells : Less Delay, More leakage

Use Low Vt cells in the timing critical paths

to achieve timing

Use High-Vt cells in the timing non-critical

paths to reduce leakage power

Multi-Vt

Two approaches

Timing critical design

Insert all the low Vt cells to achieve timing

Selectively replace low Vt cells by High-Vt cells in non critical paths to

reduce the leakage

Power critical design

Insert all the high Vt cells to reduce the leakage power

Selectively replace high Vt cells by low-Vt cells in timing critical paths to

reduce the leakage

14/04/15

Power Gating

14/04/15

Portion of the chip (Certain blocks ) are shut down during the period of

inactivity of those blocks

Reduces leakage power of the inactive blocks during powered off state

Power gating -Requirements

14/04/15

Power controller circuits to

decide power on/off sequence of

the power gated block

Power switching network that

VDD

VDD

provides power to the gated

blocks

SLEEPN

Power switches are the

POWER

transistors that connect the

SVDD

GATED

always on power structure to the

BLOCK

POWER

power pins of the cells in the

GATED

power gated blocks

SVSS

BLOCK

Power switches, when switched

SLEEP

on provides power to the gated

block and when switched off it

disconnects power supply from

VSS

the gated block

VSS

GATED

High Vt cells are used as power

GATED VSS

VDD

switches

Power gating -Requirements

14/04/15

Isolation cells : Needed for signal isolation

between power gated blocks and always

on blocks

Needed for the output signals of the power

gated blocks

Provides a known constant voltage

(0/1/last logic value before power down

the block) to the always on block input,

when the power gated domain is switched

off

The isolation cell prevents any unknown

logic values to reach to the input of the

always on block

The output of the gated block does not

decay immediately and it floats near the

threshold level, the isolation cell helps

reducing the crowbar current at the input

of the always on block by providing

constant voltage level

Power

Gated

Block

Power_U

p

Isolation

Cell

Always

On

Block

Power gating -Requirements

Retention registers

Often desirable to save the logic values of the

power gated blocks when it is powered off

Retention register stores the logic values when

the gated block is powered off

Contains one shadow registers in addition to the

normal flip flop, powered by always on power

supply, which stores the logic values when the

gated block is switched off

Restores the stored logic when the gated block is

again powered on

When SAVE is asserted before power down, the

content of the main register is stored in the

shadow register

When RESTORE is asserted after power up, the

content of the shadow register is restored back in

the main register

14/04/15

Q

Main

Register

save

restore

Shadow

Register

CLK

SAVE

RESTORE

14/04/15

Power Management Kit

14/04/15

Special cells for low power techniques

The following special cells are used for various low

power techniques

Level Shifters

Power gating cells (Headers/Footers)

Isolation cells

Retention registers

14/04/15

Level Shifters

Level Shifter : Cell (typically buffers) that translates inputs with one voltage

swing to an output with a different voltage swing

In a multi voltage design, there are multiple voltage islands. In such case when

signal crosses the boundary from one domain to other domain and logic level

switching voltages are not the same, level shifter cells must be inserted to convert

the signal voltage to the correct voltage at the receiving domain

Types of level shifters

1) High to Low level shifter - Down shifting

2) Low to High level shifter - Up shifting

OUTL

14/04/15

vss

High to low level shifter

Low to High level shifter

High to Low Level Shifters

1) High to Low level shifter - Down

shifting

When the signal is entering to low voltage domain from the high

voltage domain, we need to down shift the signal, high voltage level to

low voltage level. So at that time we need high to low level shifters

If we do not use high to low level shifters then there are no latchup or

break down problem but it may cause rise time and fall time faster

However for safe timing closure we need some specially identified

downshift cells High to low level shifters

In the case of down shifting, the level shifter cell can be just a simple

inverter or buffer. As shown in figure, high to low level shifter can be

quite simple, essentially two inverters in series

As shown in the drawing, a high-to-low level shifter only introduces a

buffer delay, so its impact on timing is small

High to low level shifters are very simple compared to low to high level

shifters. It requires single supply voltage

14/04/15

OUTL

vss

Low to High Level Shifters

2) Low to High level shifter - Up

shifting

When the signal is entering to high voltage domain

from

the low voltage domain, we need to up shift

the signal. So

at that time we need low to high level shifters

In the case of shifting up, it is necessary to design a special level

shifter circuit, because a low voltage swing input signal would not

necessarily be strong enough to turn the input transistor fully on.

This could lead to an unacceptably long rise time or fall time. It

causes higher switching current and reduce the noise margin

A slow transition time means that the signal spends more time

near VT, causing the short circuit (crowbar) current to last longer

than necessary

Specially designed level shifter cells solve this problem. They

provide fast signals to the higher voltage domain

14/04/15

Low to High Level Shifters

There are number of design techniques. But a

simple one is shown in the figure

This design takes buffered and inverted form of

the lower voltage signal and use this to drive a

cross-coupled transistor structure running at the

higher voltage

Such level shifters requires two supply and

typically share a comman ground

Low to high level shifters introduce a significant

delay compared to a simple buffer dealy of high

to low level shifters because of its complex

design structure

14/04/15

Placement of the level shifters

Level shifters should be placed in the destination domain for up shifting as well as

down shifting

As we need low voltage supply for high to low level shifter we should place such

level shifters in the low voltage domain. However we can place them in the high

voltage domain also, but then power routing for such cells become a critical task.

For low to high level shifters, output driver has higher supply current requirement.

Thus we need to apply high voltage for output driver. So, we should place low to

high level shifters in to high voltage domain.

Following figures explains the placement of level shifters.

14/04/15

Level Shifter Recommendations and Pitfalls

Recommendations:

Place the level shifters in the receiving domain in the lower domain for Highto-Low level shifters, in the higher domain for High-to-Low level shifters

Pitfalls:

Interfaces between domains that may both be higher or lower voltage with

respect to each other will require specialized level shifter components and make

the setup and hold timing verification across such interfaces very complex

14/04/15

Problems without Level Shifters

Problem without High to low level shifters:

If we do not use high to low level shifters then it may cause rise time and fall

time faster for the receiving domain and that can cause hold violations

So, for safe timing closure we need to insert high to low level shifters when

signal interacts between high voltage domain to low voltage domain

Problem without low to high level shifter:

If the difference between low voltage and high voltage is more then 25% then a

signal from low voltage domain to high voltage domain can turn on both

transistors PMOS as well as NMOS in the receiving cell and cause the crowbar

current that increases the power consumption

If a signal from low voltage domain is driving a cell in high voltage domain, it

may result in significant rise or fall time degradation. This may cause the setup

violations in the receiving domain

So, to prevent power consumption due to crowbar current and setup time

14/04/15

violations, we need to insert proper level shifters

Power Gating Cells

Power gating:

Power gating is the technique to reduce leakage

power

consumption. In this technique we are using

sleep transistor

A sleep transistor is either PMOS or NMOS high VT

transistor and is used as a switch to shut off the power

supplies to parts of a design in standby mode

The PMOS sleep transistor is used to switch VDD

supply and hence is called as a Header Switch

The NMOS sleep transistor controls VSS supply and

hence is called as a Footer switch

Figure shows schematic of header and footer switch.

In

footers VSS is switched ground and VSSG is always

on

ground. While in headers VDD is switched power

and VDDG is always on power

14/04/15

Isolation Cells

Isolation: Isolation is a technique for controlling the behaviour of a signal

that is driven by a powered down domain. Isolation technique driving a

signal to a known state - 1, 0, or latching it to a previous value when the

power domain is powered down

14/04/15

Isolation cells are basically used to isolate the output signals of the power

gated block from the always on block Isolation ensures that there are no

floating inputs to the active power domain, which could result in crowbar

current

Why Isolation cells required?

Why isolation is required in the power gating?

With a header style switch fabric, the internal nodes and outputs of the power gated block

collapse down towards to ground rail when the switch is turned off

With a footer style switch fabric, the internal nodes and outputs of the power gated block

charges towards to supply rail when the switch is turned off

But there is no guarantee that the power gated nodes will ever fully discharge to ground or

fully charged to the supply

So, the challenge for power gating designs is that the outputs of the power gated block may

ramp off very slowly. The result could be that these outputs spend a significant amount of

time at threshold voltage, causing large crowbar currents in the always powered on block

To prevent these crowbar currents, isolation cells are placed between the outputs of the

power gated block and the inputs of the always on block

To Solve this problem we have three types of isolation

techniques:

1) clamp the signal to 0

2) clamp the signal to 1

3) clamp the signal to the last value

14/04/15

Signal Isolation Techniques

Clamp the signal to 0 :

For an output that requires clamping the signal to 0, we can use a NAND gate and

an inverter, as shown in Figure, for signal isolation. This design uses an active-low

isolation control signal which forces the output low even if the other input floats.

The circuit diagram shows why the circuit is immune to a floating signal on IN. As

long as ISOLN is low, the bottom transistor is off, no current can flow through the

gate, and the input to the inverter is pulled up.

14/04/15

Signal Isolation Techniques

Clamp the signal to 1 :

For an input that requires holding a logic 1 when the source power domain is

powered down, we can use a NOR gate, as shown in the figure, for the signal

isolation. This is shown with an active-high isolation control signal which forces the

output high even if the other input floats. The circuit diagram shows why the circuit

is immune to a floating signal on IN.

14/04/15

Signal Isolation Techniques

Clamp the signal to the last value:

The retention latch is controlled by a pulse signal RET which is asserted just before

the logic cell goes into sleep to save the current output state into the retention latch.

Then the isolation control ISOLATION is asserted to switch the output mux to the

retention latch and the logic cell goes into sleep where the virtual power VVDD is

shut off.

14/04/15

Recommendations and Pitfalls for Isolation

Recommendations:

Isolate the outputs of power gated blocks.

Pitfalls:

Make sure the isolation cells really are always powered on.

Isolation clamps on clocks can considerably complicate the clock tree synthesis

and timing closure. Clock tree balancing in particular can become difficult. If

possible, avoid clocks that are generated in a power gated block and used

externally to the block

14/04/15

Retention Registers

Retention: Retention is a technique for retaining the state value of registers in a

powered down domain

Retention Register: A register than extends the functionality of a normal

register(flip-flop) with the ability to retain its state during power down, assuming an

appropriate second (always on) supply as well as save and

restore signal is on

Shadow Register: The section of a retention register retains the register state

during power down. Also known as a balloon registers (due to the topology of

some implementations).

D

Q

Main

Register

save

restore

Shadow

Register

CLK

14/04/15

SAVE

RESTORE

Retention Registers

Retention registers are used in power gating technique. For some power-gated

blocks, it is highly desirable to retain the internal state of the block during

power down, and to restore this state during power up

Such a retention strategy can save significant amounts of time and power

during power up. One way of implementing such a retention strategy is to use

retention registers in place of ordinary flip-flops

Retention registers typically have an auxiliary or shadow register that is slower

than the main register but which has much less leakage current. The shadow

register is always powered up, and stores the contents of the main register

during power gating

Full retention Vs. Partial retention

Full State Retention: Retaining the full state of the block that is, replacing all

registers with retention registers provides the most robust, easily

verified, and most transparent form of power gating

Partial State Retention: Retaining the partial state means retaining only some

14/04/15 of the internal state of the block to reduce the area.

Thank You

14/04/15

Vous aimerez peut-être aussi

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5795)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Ah 1000Document1 pageAh 1000Zafir SihabuddinPas encore d'évaluation

- American Pile Driving Equipment Equipment CatalogDocument25 pagesAmerican Pile Driving Equipment Equipment CatalogW Morales100% (1)

- Unit 3 InfiltrationDocument5 pagesUnit 3 InfiltrationHRIDYA MGPas encore d'évaluation

- 4th Semester Electrical Engg.Document19 pages4th Semester Electrical Engg.Bhojpuri entertainmentPas encore d'évaluation

- Section Thru A-A at S-1: Footing ScheduleDocument1 pageSection Thru A-A at S-1: Footing ScheduleJan GarciaPas encore d'évaluation

- Strange Christmas TraditionsDocument2 pagesStrange Christmas TraditionsZsofia ZsofiaPas encore d'évaluation

- Chapter 9 Material ChangesDocument6 pagesChapter 9 Material ChangesFitria Istikomah DewiPas encore d'évaluation

- A Collection of Ideas For The Chemistry Classroom by Jeff HepburnDocument14 pagesA Collection of Ideas For The Chemistry Classroom by Jeff HepburnPaul SchumannPas encore d'évaluation

- NDT Matrix 12-99-90-1710 - Rev.2 PDFDocument2 pagesNDT Matrix 12-99-90-1710 - Rev.2 PDFEPC NCCPas encore d'évaluation

- Sikagrout®-214 Ae: Product Data SheetDocument3 pagesSikagrout®-214 Ae: Product Data Sheetmohammed rinshinPas encore d'évaluation

- Technical Design of The Bukwimba Open Pit Final 12042017Document31 pagesTechnical Design of The Bukwimba Open Pit Final 12042017Rozalia PengoPas encore d'évaluation

- Moldex Realty, Inc. (Linda Agustin) 2.0 (With Sound)Document111 pagesMoldex Realty, Inc. (Linda Agustin) 2.0 (With Sound)Arwin AgustinPas encore d'évaluation

- 4 Pure BendingDocument42 pages4 Pure BendingOmarfirozPas encore d'évaluation

- Wisconsin Construction Specification 23. Aluminum or Steel Roof GuttersDocument5 pagesWisconsin Construction Specification 23. Aluminum or Steel Roof GuttersAntonio PagaPas encore d'évaluation

- Etl 213-1208.10 enDocument1 pageEtl 213-1208.10 enhossamPas encore d'évaluation

- Mathematics 7 LAS Quarter 3Document97 pagesMathematics 7 LAS Quarter 3Villamor Baculi82% (17)

- Prakab Export 20.8.2018 UkDocument260 pagesPrakab Export 20.8.2018 UkREN JTNPas encore d'évaluation

- Veg Dum Biryani - Hyderabadi Veg Biryani Recipe - Hyderabadi Biryani - Hebbar's KitchenDocument2 pagesVeg Dum Biryani - Hyderabadi Veg Biryani Recipe - Hyderabadi Biryani - Hebbar's KitchenmusicalcarpetPas encore d'évaluation

- Safety Procedures For Vertical Formwork PDFDocument17 pagesSafety Procedures For Vertical Formwork PDFbalya7Pas encore d'évaluation

- HPE 3PAR StoreServ 20000 Storage Service and Upgrade Guide Service EditionDocument282 pagesHPE 3PAR StoreServ 20000 Storage Service and Upgrade Guide Service Editionben boltPas encore d'évaluation

- SFT PresentationDocument16 pagesSFT Presentationapna indiaPas encore d'évaluation

- Chapter 1 - Part 1 Introduction To Organic ChemistryDocument43 pagesChapter 1 - Part 1 Introduction To Organic ChemistryqilahmazlanPas encore d'évaluation

- DLP Physical Science Week1Document2 pagesDLP Physical Science Week1gizellen galvezPas encore d'évaluation

- Battery Installation ProcedureDocument5 pagesBattery Installation ProceduresantoshkumarPas encore d'évaluation

- Magical ExercisesDocument5 pagesMagical ExercisesAnonymous ytxGqZPas encore d'évaluation

- Lesson Notes Lecture 14Document5 pagesLesson Notes Lecture 14Quantum SaudiPas encore d'évaluation

- Daygame by Todd Valentine NotesDocument8 pagesDaygame by Todd Valentine NotesAdnanHassan100% (7)

- Presentation 1Document7 pagesPresentation 1Abdillah StrhanPas encore d'évaluation

- Part 3-Chap 2 - Classification of Buildings Based On OccupanciesDocument60 pagesPart 3-Chap 2 - Classification of Buildings Based On Occupanciesfaruque65Pas encore d'évaluation

- Camouflage Lesson PlanDocument4 pagesCamouflage Lesson Planapi-344569443Pas encore d'évaluation