Académique Documents

Professionnel Documents

Culture Documents

A Novel Bidirectional DC-DC Converter With ZVS and Interleaving For Dual Voltage Systems in Automobiles

Transféré par

PradeepChandraVarmaMandapatiTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

A Novel Bidirectional DC-DC Converter With ZVS and Interleaving For Dual Voltage Systems in Automobiles

Transféré par

PradeepChandraVarmaMandapatiDroits d'auteur :

Formats disponibles

1

A Novel Bidirectional DC-DC Converter with ZVS

and Interleaving for Dual Voltage Systems in

Automobiles

Philip Jose

Ned Mohan

Department of Electrical Engineering

University of Minnesota

200 Union Street SE

Minneapolis, MN 55455, USA

philip@ece.umn.edu

mohan@ece.umn.edu

Abstract This paper presents a novel bidirectional dc-dc converter for 42V/14V dual voltage systems in automobiles. The converter uses Clamped Zero voltage Switching to minimize loses, and

interleaving for reduced current ripple. SABER simulations are

presented to verify the design. The simulation results are confirmed by hardware implementation.

I. I NTRODUCTION

The requirement of a higher electrical system voltage in automobiles has now been widely acknowledged ([1]), and efforts

are on to formulate standards for the same. The MIT/Industry

Consortium for Advanced Automotive Electrical/Electronic

Components and Systems led by the Massachusetts Institute of

Technology, Boston has chosen 42 volts as the preferred electrical system voltage for automobiles of the future. In the short run

however, it is proposed for new automobiles to have two voltage systems onboard till the components and technology for 42

V systems are fully developed. Several architectures are studied for managing two voltage systems in an automobile, many

of them requiring a bidirectional dc-dc converter which interfaces the 42 V and the 14 V electrical subsystems. This paper

explores the possibility of using a simple buck converter featuring clamped Zero Voltage Switching [2] for reduced switching

losses so that the converter can be run at high switching frequencies. To circumvent the problem of high current ripple in

the proposed ZVS scheme, a number of such converters can be

interleaved. Output current sharing for the converters is based

on the scheme proposed by [3].

Section II describes the design of the converter. Experimental

results are presented in section III.

II. D ESIGN

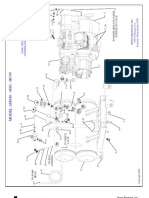

The converter outline is shown in Fig. 1. N converters connected in parallel transfer power between the 42 V bus and the

14 V bus. The voltage error is amplified by the voltage controller, which generates a current reference. This current reference is equally shared by the current controllers . That is, the

current reference divided by the number of converters is given

to each current controller. Each converter then works in average current control. The inner current control loop is designed

using average model analysis of power converters. H control

[4] is used to design a robust current controller which is insensitive to fluctuations in the input voltage. Further, input voltage

feed forward is used to improve the response of the converter so

as to avoid high startup currents. The converters are interleaved

so as to reduce the ripple in output current.

Fig. 1. Outline of Converter

A. Controller Design

The converter has an inner current loop to facilitate current

sharing across several parallel converters. The current controller has to be insensitive to fluctuations in the input and output voltages, and also the load, which is essentially the internal

resistance of the 12 V battery. To achieve these goals, H

control is used with appropriate weighting functions. First, the

converter is modeled in an average sense [5] with the duty ratio

command as input, and the input and output voltages as disturbances (see Fig. 2). The effect of switching frequency is

modeled as a noise input which adds on to the current output.

The weighting functions are chosen so as to give a high steady

state open loop gain, and also to make the controller insensitive

to switching frequency. Hence the weighting function Wn is a

cascade of two transfer functions, as given in eq. 1, one to increase sensitivity at low frequency, and the other to decrease the

0-7803-7420-7/02/$17.00 2002 IEEE

1311

sensitivity at the switching frequency. A weighting function is

also added to the measured inductor current to model the bandwidth of measurement circuit. The chosen weighting functions

are:

Wi

1.5 1011 s2 + 0.00021s + 0.15

1 1010 s2 + 0.0028s + 1

5.674 1013 s2 + 1.337 105 s + 0.07

4.053 1013 s2 + 1.91 106 s + 1

1

Wo

Wz

Wn

1

1.592 107 s + 1

Fig. 3. Hysteresis control for current limiting

(1)

Fig. 4. Duty cycle feedforwarding

Fig. 2. Current controller design

B. Zero Voltage Switching

The controller is designed using MATLAB and the suboptimal controller Kc is reduced in order to yield a third-order

controller.

In order to avoid transient high currents, hysteresis control

is added which kicks in when the inductor current goes above

or below the operating region (see Fig. 3). Further, the input

voltage is sensed to predict the duty cycle. For the converter,

Vo

DVin

(2)

where Vo is the output voltage

Vin is the input voltage

and D is the duty cycle

Now, Vin can be expressed as a variation Vin about a nominal Vin,nom . That is,

Vin

= Vin,nom + Vin

In order to reduce switching losses and improve efficiency

of the converter,the converter uses Zero Voltage Switching with

switch voltage clamped to the input voltage as shown in Fig.

5. As switch T1 is turned off, the inductor current charges capacitor C1 to input voltage and discharges C2 to zero voltage

when the antiparallel diode of T2 starts conducting. Switch T2

can then be turned on. The value of the capacitances and the

dead-time between the high and low side gate pulses are critical to obtain proper ZVS operation. Another constraint is that

the inductor current has to reverse in each cycle so that ZVS

is effective when T2 is turned off and T1 is turned on. This

then means that the inductor peak-peak ripple has to be a little

more than double the maximum average current expected. This

large ripple is indeed a problem, which however is alleviated by

interleaving.

(3)

(4)

Eq. 3 can then be rewritten as

D

=

=

Vo

Vin,nom + Vin

Vo

1

Vin,nom 1 + VVin

in,nom

Vo

Vin,nom

2Vo

Vin,nom

Vin

)

Vin,nom

Vo Vin

2

Vin,nom

(1

Fig. 5. Clamped Zero Voltage Switching Power Circuit

(5)

The expression for duty ratio obtained in Eq. 5 is used to predict the nominal duty cycle about which the controller operates.

The circuit was simulated using SABER to determine the values of capacitors C1 and C2, and the deadtime which gave optimum performance. Zero Voltage Switching Waveforms for the

1312

lower MOSFET are given in Fig. 6.

zero, and the drain-source voltage falls to zero before the gatesource voltage starts to rise, indicating zero voltage turn on and

zero current turn off.

Fig. 7. Clamped Zero Voltage Switching during no load

Fig. 6. Simulation results of Clamped Zero Voltage Switching of Lower MOSFET

C. Interleaving

As mentioned in the previous section, proper ZVS operation

requires that inductor current flows in either direction in each

cycle, which necessitates large inductor current ripple. However, by paralleling several converters and phase shifting their

gate pulses appropriately, this ripple can be reduced to a great

extend. Hence a programmable delay circuit is incorporated

into the gate drive of the converter.

D. Voltage controller

Once the design of the current controller was completed, the

outer voltage loop can be designed. Since the current loop is

much faster than the voltage loop, it could be assumed that the

inductor current is exactly same as the current reference. A

simple integral converter suffices for voltage control so that the

steady state error was zero.

Fig. 8. Clamped Zero Voltage Switching during full load

III. I MPLEMENTATION AND E XPERIMENTAL R ESULTS

The converter was built in two parts: a voltage board, which

generated the current reference, and also the master clock, and

several current controlled ZVS converter boards which were

connected in parallel.

B. Current Loop

A. Zero Voltage Switching

The converter was first tested to see if Zero Voltage Switching was functioning properly. Figures 7 and 8 shows the lower

MOSFET gate-source and drain source voltages, during noload and full-load operation. The MOSFET drain-source rises

only after the gate-source voltage (i.e., drain current) fall to

The current controller was implemented using a linear

OPAMP circuit. The step response of the current loop is shown

in Fig. 9. Fig. 10 shows that the controlled inductor current is

insensitive to a disturbance in input voltage.

1313

Fig. 9. Step response of current loop

Fig. 11. Effect of interleaving on output current ripple

IV. C ONCLUSION

A bidirectional converter for use in dual voltage systems in

automobiles is presented. Zero Voltage Switching and output current interleaving are implemented for reduced switching

losses and current ripple. Interleaving also helps to modularize

the converter design for use in higher power applications. The

design was carried out using MATLAB and verified by SABER

simulations. Experiment observations confirm simulation results.

Fig. 10. Effect of input voltage fluctuation

C. Interleaving

Two converters were interleaved to observe the effect on output ripple current. Fig. 11 shows the results of the experiment,

with the delay between the two boards set to half the switching

time. There is significant reduction in ripple current. The ripple

would be even lower with more converters in parallel.

R EFERENCES

[1] Kassakian, J. G, Automotive Electrical Systems - The Power Electronic

Market of the Future, APEC 2000, vol. 1, pp 3-9.

[2] Henze, C. P, Martin, H. C and Parsley, D. W, Zero-Voltage Switching

in High Frequency Power Converters using Pulse Width Modulation,

APEC 1988, pp 33-40.

[3] Bhinge, A., Mohan N., Giri, R. and Ayyanar R., Series-Parallel Connection of DC-DC Converter Modules with Active Sharing of Input Voltage

and Load Current, APEC 2002.

[4] Zhou, K., Essentials of Robust Control, Prentice Hall, 1998

[5] Nirgude, G., Tirumala, R., Mohan, N., A new, large-signal average

model for single-switch DC-DC converters operating in both CCM and

DCM, Power Electronics Specialists Conference, 2001. PESC. 2001

IEEE 32nd Annual, Volume: 3 , 2001

1314

Vous aimerez peut-être aussi

- 2 AP DemographyDocument12 pages2 AP DemographyYeshWaNthPas encore d'évaluation

- Paper Authors Topic Previous work Methodology Contribution RemarksDocument18 pagesPaper Authors Topic Previous work Methodology Contribution RemarksPradeepChandraVarmaMandapati100% (1)

- A New Torque Control Method For Torque Ripple Minimization of BLDC Motors With Un-Ideal Back EMFDocument9 pagesA New Torque Control Method For Torque Ripple Minimization of BLDC Motors With Un-Ideal Back EMFPradeepChandraVarmaMandapatiPas encore d'évaluation

- Partition of Unity Methods Course at IIT MadrasDocument2 pagesPartition of Unity Methods Course at IIT MadrasPradeepChandraVarmaMandapatiPas encore d'évaluation

- 8085 Microprocessor Ramesh S. GaonkarDocument330 pages8085 Microprocessor Ramesh S. Gaonkarrohit31bark64% (22)

- Mappings Important PDFDocument11 pagesMappings Important PDFPradeepChandraVarmaMandapatiPas encore d'évaluation

- Direct Current Transmission - KimbarkDocument264 pagesDirect Current Transmission - Kimbarksrinathchary100% (13)

- EC GATE 2015 Paper-1 PDFDocument43 pagesEC GATE 2015 Paper-1 PDFPradeepChandraVarmaMandapatiPas encore d'évaluation

- Chap 5 Tra CODocument27 pagesChap 5 Tra COKISHORHASYAGARPas encore d'évaluation

- FAQs NUUP PDFDocument11 pagesFAQs NUUP PDFPradeepChandraVarmaMandapatiPas encore d'évaluation

- 00154140Document6 pages00154140PradeepChandraVarmaMandapatiPas encore d'évaluation

- CS6303 Leature Notes 1Document18 pagesCS6303 Leature Notes 1ammapetPas encore d'évaluation

- k10057 c001Document18 pagesk10057 c001PradeepChandraVarmaMandapatiPas encore d'évaluation

- PDFDocument16 pagesPDFPradeepChandraVarmaMandapatiPas encore d'évaluation

- 01490600Document13 pages01490600PradeepChandraVarmaMandapatiPas encore d'évaluation

- Fuzzy Set Based Models and Methods of Decision Making and Power Engineering ProblemsDocument11 pagesFuzzy Set Based Models and Methods of Decision Making and Power Engineering ProblemsPradeepChandraVarmaMandapatiPas encore d'évaluation

- An Adaptive Controller FR Ps Stability Improvement and Power Flow CTRL by TSSCDocument11 pagesAn Adaptive Controller FR Ps Stability Improvement and Power Flow CTRL by TSSCSunil MotepalliPas encore d'évaluation

- PDFDocument11 pagesPDFPradeepChandraVarmaMandapatiPas encore d'évaluation

- An Energy Management Strategy For A DC Dist System For Plug in Evs IntergrationDocument10 pagesAn Energy Management Strategy For A DC Dist System For Plug in Evs IntergrationPradeepChandraVarmaMandapatiPas encore d'évaluation

- 01532707Document6 pages01532707PradeepChandraVarmaMandapatiPas encore d'évaluation

- Performance Analysis of Bi-Directional DC-DC For HevDocument10 pagesPerformance Analysis of Bi-Directional DC-DC For HevPradeepChandraVarmaMandapatiPas encore d'évaluation

- Half-Bridge Bidirectional DC-DC Converter For Small Electric VehicleDocument5 pagesHalf-Bridge Bidirectional DC-DC Converter For Small Electric VehiclePradeepChandraVarmaMandapati100% (1)

- Energy Mangement and Control of Electric Vehicles Uinsg Hybrid Power Source in Regenrative BrakingoperationDocument16 pagesEnergy Mangement and Control of Electric Vehicles Uinsg Hybrid Power Source in Regenrative BrakingoperationPradeepChandraVarmaMandapatiPas encore d'évaluation

- Fuzzy Set Based Models and Methods of Decision Making and Power Engineering ProblemsDocument11 pagesFuzzy Set Based Models and Methods of Decision Making and Power Engineering ProblemsPradeepChandraVarmaMandapatiPas encore d'évaluation

- Energy Mangement and Control of Electric Vehicles Uinsg Hybrid Power Source in Regenrative BrakingoperationDocument16 pagesEnergy Mangement and Control of Electric Vehicles Uinsg Hybrid Power Source in Regenrative BrakingoperationPradeepChandraVarmaMandapatiPas encore d'évaluation

- 211EE3336Document86 pages211EE3336PradeepChandraVarmaMandapatiPas encore d'évaluation

- InTech-Batteries Charging Systems For Electric and Plug in Hybrid Electric VehiclesDocument20 pagesInTech-Batteries Charging Systems For Electric and Plug in Hybrid Electric VehiclesM VetriselviPas encore d'évaluation

- Fuzzy ExampleDocument10 pagesFuzzy ExamplePradeepChandraVarmaMandapatiPas encore d'évaluation

- STAR DELTA motor starter diagram and working principleDocument2 pagesSTAR DELTA motor starter diagram and working principlePradeepChandraVarmaMandapatiPas encore d'évaluation

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5783)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- DC Machines Lecture Notes by Dr. Mohammed & Dr. JaafarDocument90 pagesDC Machines Lecture Notes by Dr. Mohammed & Dr. JaafarTafhim Bin NasirPas encore d'évaluation

- TLK38 ManualDocument12 pagesTLK38 ManualArtur DomańskiPas encore d'évaluation

- SACE Isomax S: A Single Series of Moulded-Case Circuit-Breakers Enabling Infinite SolutionsDocument28 pagesSACE Isomax S: A Single Series of Moulded-Case Circuit-Breakers Enabling Infinite Solutionsdwiyanto73Pas encore d'évaluation

- Mini Excavator Liugong Dressta 9035e Stage VDocument9 pagesMini Excavator Liugong Dressta 9035e Stage VRadu GălățanPas encore d'évaluation

- Frame Stretching BasicsDocument2 pagesFrame Stretching BasicsMassey FergusonPas encore d'évaluation

- AEAT 9000 1GSH0 Full Option Ultra Precision 17 Bit Absolute Single Turn Encoder PDFDocument8 pagesAEAT 9000 1GSH0 Full Option Ultra Precision 17 Bit Absolute Single Turn Encoder PDFNguyen Quang VinhPas encore d'évaluation

- Ficha Tecnica - Bomba Hidraulica Sauer Danfoss PDFDocument220 pagesFicha Tecnica - Bomba Hidraulica Sauer Danfoss PDFpokebalomanPas encore d'évaluation

- 1Gcf530K0000-Brake Shoe Set - Rear/Front 1Gcf530K0000-Brake Shoe Set - Rear/FrontDocument6 pages1Gcf530K0000-Brake Shoe Set - Rear/Front 1Gcf530K0000-Brake Shoe Set - Rear/FrontArif MamunPas encore d'évaluation

- Catalogue PDFDocument45 pagesCatalogue PDFAbhinavDixit100% (1)

- Beetronics - 17-Inch-Touchscreen-54Document6 pagesBeetronics - 17-Inch-Touchscreen-54mohamedPas encore d'évaluation

- Digital B&W Copier (D159-NA) Parts CatalogDocument128 pagesDigital B&W Copier (D159-NA) Parts CatalogJ Enrique BlancoPas encore d'évaluation

- Am840 4HG HC4VDocument8 pagesAm840 4HG HC4VGlenn0% (1)

- New Grand I10 NiosDocument10 pagesNew Grand I10 NiosslohariPas encore d'évaluation

- Practical Programs For Construction Blasting PatternsDocument10 pagesPractical Programs For Construction Blasting PatternsDinoYancachajllaPas encore d'évaluation

- TMC 49-9 Ewna F029168Document7 pagesTMC 49-9 Ewna F029168Zeevenhooven EquipmentPas encore d'évaluation

- 0.1 General PointsDocument96 pages0.1 General PointsSergeyPas encore d'évaluation

- Cummins: Fault Code: 366 PID: P1287 SPN: FmiDocument5 pagesCummins: Fault Code: 366 PID: P1287 SPN: FmiEnrrique LaraPas encore d'évaluation

- Micro MT Laser Tag System V18-01Document19 pagesMicro MT Laser Tag System V18-01Dylan SenkicPas encore d'évaluation

- Mpa 1600 VF 46288Document4 pagesMpa 1600 VF 46288Leonel Mejia LariosPas encore d'évaluation

- HST-2 Expansion Anchor Technical DatasheetDocument11 pagesHST-2 Expansion Anchor Technical DatasheetThe KeymasterPas encore d'évaluation

- Ip Control Valve Calibration FormDocument1 pageIp Control Valve Calibration FormKester Ndabai0% (1)

- TA7291ASDocument14 pagesTA7291ASGustavo GarciaPas encore d'évaluation

- AA-7000 Atomic Absorption Spectrophotometer Installation RequirementsDocument3 pagesAA-7000 Atomic Absorption Spectrophotometer Installation RequirementsGanesh KashinathPas encore d'évaluation

- Ca and CH Series: Product SpecificationsDocument12 pagesCa and CH Series: Product SpecificationsMark ThomasPas encore d'évaluation

- Inner-Board Connector: Epld External InterfaceDocument13 pagesInner-Board Connector: Epld External InterfaceAgung TewelPas encore d'évaluation

- JetBlue Fueling Instructors GuideDocument13 pagesJetBlue Fueling Instructors GuidevictorPas encore d'évaluation

- 1MRB520308-BEN D en Distributed Busbar Protection REB500Document58 pages1MRB520308-BEN D en Distributed Busbar Protection REB500locomaniacoPas encore d'évaluation

- Ir2153 Overcurrent ProtectionDocument9 pagesIr2153 Overcurrent ProtectionJairo NascimentoPas encore d'évaluation

- Durable and Powerful HF-525Plus X-ray SystemDocument2 pagesDurable and Powerful HF-525Plus X-ray SystemVictor RiquelmePas encore d'évaluation

- 10-Ton Pneumatic Suspension Technical SpecsDocument6 pages10-Ton Pneumatic Suspension Technical SpecsShashidhar ModemPas encore d'évaluation