Académique Documents

Professionnel Documents

Culture Documents

Calicut Univ Embedded Sys 2009 Scheme Questions

Transféré par

labeebmuhammed80Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Calicut Univ Embedded Sys 2009 Scheme Questions

Transféré par

labeebmuhammed80Droits d'auteur :

Formats disponibles

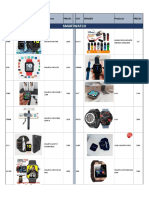

Questions

Sl No.

Marks

What are application specific processors ?

2 Marks

Write about the features of VLIW architecture.

2 Marks

Write about the memory hierarchy.

2 Marks

What do you mean by a state machine ?

2 Marks

Mention about the advantages of using automation in design technology.

2 Marks

Mention about the design metrics of an embedded system.

2 Marks

Write about the advantages of using pipelining..

2 Marks

Write about the cache impact on system performance.

2 Marks

Write about the models vs. languages.

2 Marks

10

What do you mean by logic synthesis?

2 Marks

11

Define general purpose processes and application specific processes

2 Marks

12

Mention about the memory heirarchy

2 Marks

13

Draw the structure of a basic state machine model

2 Marks

14

Define automation.

2 Marks

15

List the bus standards.

2 Marks

16

Mention the design metrics of an embedded system.

2 Marks

17

Enumerate the benefits of pipelining.

2 Marks

18

What do you mean by storage permanence ?

2 Marks

19

What is the need for text and graphics in process modeling ?

2 Marks

20

Mention any two new challenges posed by cores to processor providers and users.

2 Marks

21

What is VLIW architecture?

2 Marks

22

What is cross compiler?

2 Marks

23

What are the different cache replacement policies?

2 Marks

24

What is 'process suspend and resume' ?

2 Marks

25

Define automation and reuse

2 Marks

26

Explain about the design challenges faced in an embedded system.

5 Marks

27

Write about the sequential logic design.

5 Marks

28

Explain about the arbitration methods in detail.

5 Marks

29

Explam about the executable specification design of a digital camera

5 Marks

30

Write about the role of an appropriate model language.

5 Marks

31

Write about the parallel evolution of compilation and synthesis.

5 Marks

32

Explain about the working of Timers and counters.

5 Marks

33

Explain about the compilation/ synthesis mehanism in IC technology.

5 Marks

34

Explain about the memory management unit.

5 Marks

35

Write about the principle of operation involved in wireless communication.

5 Marks

36

Explain about the features of QNX.

5 Marks

37

Explain about FSM synthesis.

5 Marks

38

Write the principal of operation involved in full custom ASIC.

5 Marks

39

Explain about the working of debugging process.

5 Marks

40

Explain the working of DRAM.

5 Marks

41

Write about the state charts language.

5 Marks

42

Explain the various synthesis levels.

5 Marks

43

Explain the PSM model in detail.

5 Marks

44

Write a short nole on VLIW architecture.

5 Marks

45

Explain in detail about working of timers and counters.

5 Marks

46

Explain in detail about memory management unit.

5 Marks

47

Write about the informal functional and non-functional specifications of a simple digital camera.

5 Marks

48

Write about the synchronization methods of concurrent process model.

5 Marks

49

Explain in detail about multilevel logic minimization.

5 Marks

50

What are the different design metrics of embedded system?

5 Marks

51

Describe different cache mapping techniques.

5 Marks

52

Explain HCFSM.

5 Marks

53

Explain Gajski's Y-chart.

5 Marks

54

What is timer?

5 Marks

55

Explain Daisy chain arbitration

5 Marks

56

Explain in detail about the full custom NLSI and semi-custom ASIC technology.

10 Marks

57

Explain about the custom single purpose processor design and optimization.

10 Marks

58

Explain in detail about the replacement and write techniques used in cache memories

10 Marks

59

Explain the principles of operation involved in parallel and serial communication.

10 Marks

60

Explain about the FSM with datapath model FSMD .

10 Marks

61

Write in detail about the concurrent process model.

10 Marks

62

Explain about the register-transfer synthesis and behavioural synthesis.

10 Marks

63

Write about the intellectual property cores aud the new challenges posed by cores to processor provides and users. 10 Marks

64

Explain about the instruction set, program' and data memory space of VLIW architecture.

10 Marks

65

Explain in detail about the custom single purpose precess or design andeptimization.

10 Marks

66

Explain in detail about the cache mapping techniques.

10 Marks

67

Explain about Microprocessor interfacing in detail.

10 Marks

68

Explain in detail about the program state machine model (PSM).

10 Marks

69

Explain about the interprocess communication mechanism.

10 Marks

70

Explain about the two-level and multi-level logic minimization.

10 Marks

71

Write in detail about the intellectual property cores.

10 Marks

72

Expain in detail about the application specific processors.

10 Marks

73

Explain the working of semi-custom ASIC in detail.

10 Marks

74

Explain in detail about the memory mapping techniques

10 Marks

75

Explain the working of different types of memories.

10 Marks

76

Explain in detail about finite state machines.

10 Marks

77

Define inter process communication.Exolain its working.

10 Marks

78

write in detail about the hardware/software co-design.

10 Marks

79

Explain in detail about intellectual property cores in an embedded system.

10 Marks

80

Discuss in detail about optimizing design metric and common design metrics in designing an embedded system.

10 Marks

81

Explain in detail about the working of basic combinational and sequential logic design.

10 Marks

82

Discuss in detail about cache mapping techniques.

10 Marks

83

Explain about microprocessor interfacing in detail.

10 Marks

84

Explain in detail about program state machine model.

10 Marks

85

Discuss in detail about create, terminate, suspend and resume operations of a concurrentprocess model.

10 Marks

86

Explain in detail about the parallel evolution of compilation and synthesis.

10 Marks

87

Explain in detail about intellectual property cores.

10 Marks

88

Explain IC technology and design technology for embedded system design.

10 Marks

89

Design controller part and datapath part for a custom single purpose processor that computes GCD of two numbers. 10 Marks

90

Explain advanced RAM that can be used in embedded systems.

10 Marks

91

Explain interrupts in microprocessor interfacing of embedded system.

10 Marks

92

Describe three computation models commomnly used to describe embedded systems and/or their peripherals.

10 Marks

93

Descibe communication and synchronization among concurrent processes.

10 Marks

94

Describe synthesis techniques at different abstraction levels.

10 Marks

95

Describe intellectual property cores.

10 Marks

Vous aimerez peut-être aussi

- Demarginalizing The Sharia Muslim ActiviDocument20 pagesDemarginalizing The Sharia Muslim Activilabeebmuhammed80Pas encore d'évaluation

- Sample Mechanical Paper2Document10 pagesSample Mechanical Paper2labeebmuhammed80Pas encore d'évaluation

- Sample Mechanical Paper1Document13 pagesSample Mechanical Paper1labeebmuhammed80Pas encore d'évaluation

- Simple Funeral Guide Booklet 5Document23 pagesSimple Funeral Guide Booklet 5labeebmuhammed80Pas encore d'évaluation

- Calicut University 2009 Scheme Civil Engg QuestionsDocument3 pagesCalicut University 2009 Scheme Civil Engg Questionslabeebmuhammed80100% (1)

- Biogas GP4Document9 pagesBiogas GP4Manuel Casillas SalasPas encore d'évaluation

- GateDocument6 pagesGateParveen SwamiPas encore d'évaluation

- Higher Algebra - Hall & KnightDocument593 pagesHigher Algebra - Hall & KnightRam Gollamudi100% (2)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Yamaha 01v96Document331 pagesYamaha 01v96Lopez ManuelPas encore d'évaluation

- Descargar Pergaminos de Cristal Claudio PastenDocument3 pagesDescargar Pergaminos de Cristal Claudio PastenFelipe FernándezPas encore d'évaluation

- Exploiting Intra Warp Parallelism For GPGPUDocument37 pagesExploiting Intra Warp Parallelism For GPGPUUmesh SinghPas encore d'évaluation

- X3650 M3Document43 pagesX3650 M3Tom KielyPas encore d'évaluation

- Comp7 - Quarter 3 Module 2-3Document5 pagesComp7 - Quarter 3 Module 2-3John Mark PrestozaPas encore d'évaluation

- 3 RISC + PipelinesDocument55 pages3 RISC + PipelinesOanaMaria92Pas encore d'évaluation

- 80286Document12 pages80286Dharmanshu Patel100% (1)

- 8254 ModesDocument39 pages8254 ModesVamsi KrishnaPas encore d'évaluation

- Case FBD - Premier PasDocument180 pagesCase FBD - Premier PasjmPas encore d'évaluation

- How To Connect To DSS V6 To Another DSS V6 With An iSCSI Target VolumeDocument15 pagesHow To Connect To DSS V6 To Another DSS V6 With An iSCSI Target VolumeOpen-EPas encore d'évaluation

- Optiplex 5490 All in One Spec SheetDocument7 pagesOptiplex 5490 All in One Spec Sheetdiarasvan-1Pas encore d'évaluation

- Behringer X32-Edit 3.2 Version 3.2 - (16 November 2017)Document2 pagesBehringer X32-Edit 3.2 Version 3.2 - (16 November 2017)Everson CorreaPas encore d'évaluation

- 1 Determine The Features and Capacities Ram Disk Storage ProcessorDocument1 page1 Determine The Features and Capacities Ram Disk Storage ProcessorLet's Talk With HassanPas encore d'évaluation

- Rominit.s File For MPC8377Document8 pagesRominit.s File For MPC8377Saad Bin ShafiquePas encore d'évaluation

- Tivoli Storage Manager Client Commands (DSMC Commands) - TarDocument4 pagesTivoli Storage Manager Client Commands (DSMC Commands) - Tarb.henriqPas encore d'évaluation

- ThinkPad P50 HMMDocument126 pagesThinkPad P50 HMMlove457744Pas encore d'évaluation

- Data Man 48 Pro Plus ManualDocument171 pagesData Man 48 Pro Plus ManualCama ChoPas encore d'évaluation

- Digital Circuits and Microprocessors K-NotesDocument47 pagesDigital Circuits and Microprocessors K-NotesAyan SenguptaPas encore d'évaluation

- 405 - 1200 - 048 - 2 - Commissioning Manual - Rel 2 - 00Document146 pages405 - 1200 - 048 - 2 - Commissioning Manual - Rel 2 - 00Bartolomé Carlos Orfila NadalPas encore d'évaluation

- Xenon3 Manual Placa CompaqDocument31 pagesXenon3 Manual Placa CompaqsexointensoPas encore d'évaluation

- M95128-W M95128-R M95128-DF: 128-Kbit Serial SPI Bus EEPROM With High-Speed ClockDocument54 pagesM95128-W M95128-R M95128-DF: 128-Kbit Serial SPI Bus EEPROM With High-Speed ClockGedeon MJPas encore d'évaluation

- Lecture Raspberry PiDocument26 pagesLecture Raspberry PiAnadiKashyapPas encore d'évaluation

- Mazda Modular Diagnostic SystemDocument8 pagesMazda Modular Diagnostic Systemarthur100% (33)

- Click Hardware User ManualDocument304 pagesClick Hardware User ManualMichael PalmerPas encore d'évaluation

- Catalogo 191022 PubDocument29 pagesCatalogo 191022 PubPpPas encore d'évaluation

- LC3b ISADocument25 pagesLC3b ISASaujal VaishnavPas encore d'évaluation

- Smart Quill ReportDocument12 pagesSmart Quill ReportPadma 18-511Pas encore d'évaluation

- Computer Hardware TroubleshootingDocument29 pagesComputer Hardware TroubleshootingRamzen Raphael DomingoPas encore d'évaluation

- LED ButtonDocument14 pagesLED Buttonlabirint10Pas encore d'évaluation

- Nokia5110 - DatasheetDocument32 pagesNokia5110 - DatasheetVinicius MontenegroPas encore d'évaluation