Académique Documents

Professionnel Documents

Culture Documents

Pratica8 Spi

Transféré par

Rafael SilvaCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Pratica8 Spi

Transféré par

Rafael SilvaDroits d'auteur :

Formats disponibles

Universidade Federal de Uberlndia

Faculdade de Engenharia Eltrica - Prof. Alan Petrnio Pinheiro (www.alan.eng.br - alan@eletrica.ufu.br)

Curso de Engenharia Eletrnica e de Telecomunicaes (campus Patos de Minas) - Disciplina de Microprocessadores - Verso documento: 2.0

Prtica 8:

Comunicao SPI

8.1 Introduo e objetivos

O protocolo SPI (serial peripheral interface) um mtodo de comunicao utilizado para

interconectar dispositivos ou chips de tal forma que estes troquem informaes entre si. Inicialmente,

seu propsito era ser um protocolo de comunicao entre perifricos (cmeras, impressoras, scanners,

etc) e o computador, por exemplo. Contudo, este nicho de aplicao foi largamente tomado por outra

tecnologia (a USB - universal serial bus, vista em prticas posteriores). Mesmo assim, o SPI ainda

amplamente utilizado para troca de dados entre chips ou CIs (circuitos integrados) sendo um

importante mtodo de comunicao para sistemas digitais de alguma complexidade que envolvam,

principalmente, conversores AD e DA, memrias EEPROM e flash, real time clocks (RTC), sensores

com interface de comunicao, cartes de memria, controladores LCD e unidades de transmisso e

recepo de dados UART.

O SPI adota um esquema de comunicao do tipo mestre/escravo e pode ser executado em

modo "full duplex" (e.g., cada componente executando o SPI pode receber e transmitir dados ao

mesmo tempo). Vale destacar que mesmo sendo um protocolo largamente difundido, ele no

padronizado por nenhuma entidade e por isto pode haver variaes de uso dependendo do fabricante

que emprega este protocolo. Em relao ao seu grande "rival", o protocolo I2C (tambm visto em

prticas posteriores), o SPI tem a vantagem de se comunicar com maior rapidez e quando temos

vrios dispositivos intercomunicando-se em um barramento compartilhado, o SPI no requer um

esquema de endereamento de dispositivos to elaborado quanto o I2C.

8.2 Princpios bsicos do protocolo SPI

O SPI requer 4 fios como descrito na Tabela 7.1. O dispositivo mestre, como sugere o nome,

controla a comunicao. Atravs do controle do clock, ele decide quando o dado enviado dele ou

recebido por ele. Dentro de um mesmo ciclo de clock, uma comunicao full duplex pode ser realizada

com o mestre que pode enviar dados para um escravo e receber dados dele ou de outro dispositivo

simultaneamente. Usando o sinal SS, o mestre pode escolher com qual dos escravos se comunicar. A

Figura 7.1 ilustra a arquitetura de ligao entre dispositivos que emprega este protocolo.

Figura 7.1 - Esquema de ligao entre dispositivos mestre e escravo para o protocolo SPI.

24

Universidade Federal de Uberlndia

Faculdade de Engenharia Eltrica - Prof. Alan Petrnio Pinheiro (www.alan.eng.br - alan@eletrica.ufu.br)

Curso de Engenharia Eletrnica e de Telecomunicaes (campus Patos de Minas) - Disciplina de Microprocessadores - Verso documento: 2.0

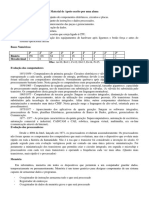

Tabela 8.1 - Fios do barramento SPI

Linha

SCLK

Nome

Serial clock

MOSI ou DO

MISO ou DI

SS ou CS

Master output, slave input ou data output

Master input, slave output ou data input

Slave select ou select device ou chip selec

Descrio

o clock gerado pelo mestre (os escravos apenas leem esta sinal) utilizado

para fazer a sincronizao dos dados.

o pino reservado para enviar dados seja o chip mestre ou escravo.

o pino reservado para receber dados seja o chip mestre ou escravo.

Geralmente ativo baixa e indica no barramento qual dispositivo escravo tem

permisso para enviar/receber dados no barramento de dados. Este fio

opcional em um sistema com um nico escravo

O protocolo estipula ainda quatro mtodos de transmisso e sincronizao de dados entre

transmissor e receptor usando o sinal de clock. Assim, o sinal de clock pode ter sua fase e polaridade

configuradas de formas diferentes para gerar os 4 modos de transmisso. A polaridade dizer respeito

ao sinal CPOL mostrado na Figura 7.2 e a fase a CPHA mostrada no mesmo modo. A Tabela 7.2

mostra como so definidas as quatro combinaes destes modos a partir de CPOL e CPHA.

Tabela 7.1 - Modos de transmisso SPI

Modo

0

1

2

3

CPOL

0

0

1

1

CPHA

0

1

0

1

Figura 7.2 - Diagrama ilustrando os diferentes modos de sincronizao entre mestre e escravo para transmisso de dados.

O diagrama de tempo da Figura 7.2 ajuda a ilustrar como funcionam estes modos.Quando

CPOL=0, temos um sinal de clock similar ao ilustrado na figura do exemplo. Assim, se CPHA=0, os

dados so lidos na borda de subida do clock e os dados so atualizados no barramento na borda de

descida. J para CPHA=1 (ainda considerando CPOL=0), os dados so lidos na borda de descida e a

sada atualizada na borda de subida. Por fim, quando CPOL=1, a referncia do clock invertida

como mostra a Figura 7.2 gerando uma diferena de fase. CPHA age do mesmo modo como no caso

anterior.

8.3 Exemplo de aplicao

Para ilustrar um exemplo verstil de SPI usando as bibliotecas SPI do CCS e tambm o

hardware SPI embutido no 18F4550, ser produzida uma aplicao onde:

so usados 2 PICs 18F4550 sendo um o dispositivo mestre e o outro escravo;

25

Universidade Federal de Uberlndia

Faculdade de Engenharia Eltrica - Prof. Alan Petrnio Pinheiro (www.alan.eng.br - alan@eletrica.ufu.br)

Curso de Engenharia Eletrnica e de Telecomunicaes (campus Patos de Minas) - Disciplina de Microprocessadores - Verso documento: 2.0

o PIC mestre l de trs chaves (S2, S3 e S4) um valor de 3 bits. Estes dados so enviados via

SPI para o PIC escravo.

o estado de uma outra chave S1 tambm enviada em um outro pacote de dados para o PIC

escravo. Esta chave S1 indica um comando onde: S1=0 deve-se ligar um LARANJA do PIC

escravo ou, quando S1=1, o escravo deve pegar o valor de S2S3S4 para um conjunto de 3

LEDs.

uma chave S8 usada para indicar ao mestre que existe um dado ou comando novo que deve

ser lido pelo mestre e enviado por SPI ao escravo que ir ler o comando e realizar a operao

indicada pelo comando.

As prxima sees descrevem esquematicamente o circuito e um exemplo de cdigo fonte para

esta aplicao. A ideia demonstrar como acontece a comunicao SPI entre dois dispositivos. O PIC

escravo poderia ser substitudo por qualquer outro chip capaz de realizar a comunicao SPI. Mesmo

assim foi preferido um emprego de um PIC como escravo para mostrar com mais detalhes como

funciona a recepo de dados em um dispositivo escravo.

8.3.1 - O circuito

A Figura 7.3 mostra o diagrama eltrico da aplicao. Dados e comandos so lidos de uma chave

DIP (dual in package) switch de 8 vias, enviados pelo PIC mestre e interpretados pelo PIC escravo

segundo a sequncia vista na figura (S1 indica comando; S2S3S4 indica um valor de 3 bits e S8

aciona uma interrupo externa no mestre para que ele possa ler os novos valores de S1 a S4 e envilos ao escravo).

Figura 7.3 - Diagrama esquemtico de montagem da transmisso SPI entre um PIC mestre e um escravo conforme descrio

da aplicao feita.

O mestre se decida exclusivamente leitura das chaves e envio de dados SPI. O escravo

monitora - por interrupo de recepo de novos dados - a chegada de novos dados e faz a

interpretao do dois possveis comandos definidos pela chave S1. Este exemplo pode ser facilmente

26

Universidade Federal de Uberlndia

Faculdade de Engenharia Eltrica - Prof. Alan Petrnio Pinheiro (www.alan.eng.br - alan@eletrica.ufu.br)

Curso de Engenharia Eletrnica e de Telecomunicaes (campus Patos de Minas) - Disciplina de Microprocessadores - Verso documento: 2.0

estendido para um maior nmero de comandos e funcionalidades incluindo uma maior transmisso de

dados. A escolha dos pinos deve ser feita segundo indicaes do datasheet e os pinos escolhidos so

exclusivos para transmisso SPI quando este recurso habilitado no wizard do CCS.

8.3.2 - O cdigo

Os comandos mostrados no Cdigo 7.1 definem o comportamento do dispositivo mestre. A

Figura 7.4 ilustra como foi configurada a unidade de transmisso SPI do 18F4550 no wizard do CCS.

(a)

(b)

Figura 7.4 - Configurando o uso do SPI no CCS 5. (a) Configurao do dispositivo mestre e (b) do escravo.

Alm das configuraes indicadas na Figura 7.4, tambm habilite no dispositivo escravo a

interrupo "SPI or 12C activity" que ser acionada toda vez que o escravo receber um novo dado na

porta de entrada SPI. Para o mestre, selecione a interrupo ("external interrupt #2") que ser

executada toda vez que o boto S8 for ativado.

Cdigo 8.1 - Cdigo fonte do dispositivo mestre (compilado para a verso CCS 5)

1

#include <mestre.h>

2

#USE SPI (MASTER, SPI1, ENABLE=PIN_A5, BAUD=5000, MODE=0, BITS=8, STREAM=ALAN1,

3

MSB_FIRST)

4

///////////////////////////////////////////////////////////////////////////////

5

#INT_EXT2 //interupcao externa

6

void EXT2_isr(void)

7

{

8

int dado, comando;

disable_interrupts(GLOBAL);

9

dado = input_e();

10

11

comando = input(PIN_A0);

12

spi_write(comando);

spi_write(dado);

13

output_high(PIN_D0); delay_ms(100); output_low(PIN_D0);

14

enable_interrupts(GLOBAL);

15

16

}

17

///////////////////////////////////////////////////////////////////////////////

void main()

18

{

19

20

enable_interrupts(INT_EXT2);

enable_interrupts(GLOBAL);

21

22

while(TRUE) //pisca led verde

23

{

24

output_high(PIN_D1);

25

delay_ms(50);

26

output_low(PIN_D1);

27

27

Universidade Federal de Uberlndia

Faculdade de Engenharia Eltrica - Prof. Alan Petrnio Pinheiro (www.alan.eng.br - alan@eletrica.ufu.br)

Curso de Engenharia Eletrnica e de Telecomunicaes (campus Patos de Minas) - Disciplina de Microprocessadores - Verso documento: 2.0

28

29

30

delay_ms(500);

}

}

Cdigo 8.2 - Cdigo fonte do dispositivo escravo

1

#include <escravo.h>

2

#USE SPI (SLAVE, SPI1, ENABLE=PIN_A5, BITS=8, STREAM=ALAN1, MSB_FIRST, MODE=0)

3

#DEFINE COMANDO_LIGAR_LED_LARANJA 0

4

#DEFINE COMANDO_MOSTRAR_VALOR_LIDO 1

5

int conta_numero_recepcoes, dados_recebidos[2];

6

///////////////////////////////////////////////////////////////////////////////

7

#INT_SSP //a funcao abaixo tratara a interupcao de recebimento dado SPI

8

void SSP_isr(void)

9

{

10

if( spi_data_is_in() ) //confirma se tem dado novo no buffer recpecao SPI

11

{

12

dados_recebidos[conta_numero_recepcoes] = spi_read();

13

conta_numero_recepcoes++;

14

if (conta_numero_recepcoes > 1)//completou as 2 leituras (COMANDO+DADO)?

15

{

16

conta_numero_recepcoes = 0;

17

if(dados_recebidos[0] == COMANDO_LIGAR_LED_LARANJA)

18

{

19

output_d(0);

20

output_high(PIN_E1);

21

}

22

if(dados_recebidos[0] == COMANDO_MOSTRAR_VALOR_LIDO)

23

{

24

output_d(dados_recebidos[1]);

25

output_low(PIN_E1);

26

}

27

}

28

}

29

}

30

///////////////////////////////////////////////////////////////////////////////

31

void main()

32

{

33

conta_numero_recepcoes = 0;

34

enable_interrupts(INT_SSP);

35

enable_interrupts(GLOBAL);

36

while(TRUE)

37

{

38

//apenas pisca led

39

output_high(PIN_E2);

40

delay_ms(50);

41

output_low(PIN_E2);

42

delay_ms(500);

43

}

44

}

28

Vous aimerez peut-être aussi

- Aprendendo A Programar em ArduinoDocument49 pagesAprendendo A Programar em ArduinoLeandro Teixeira100% (2)

- Dicas Reprogramação de Central e IMMODocument93 pagesDicas Reprogramação de Central e IMMOMecaSoftware90% (10)

- Mecatronica Facil 38Document35 pagesMecatronica Facil 38Deocleciano Araújo de OliveiraPas encore d'évaluation

- Mecatronica Facil 38Document35 pagesMecatronica Facil 38Deocleciano Araújo de OliveiraPas encore d'évaluation

- Eletrônica: Circuitos Analógicos e DigitaisDocument191 pagesEletrônica: Circuitos Analógicos e DigitaisClebson. Cardozo100% (2)

- Slides ATmega328Document145 pagesSlides ATmega328Paulo MonteiroPas encore d'évaluation

- Infraestrutura TI conceitosDocument24 pagesInfraestrutura TI conceitosSérgio Murilo Schütz100% (1)

- Relatorio Flip-Flop - Eletrônica AnalógicaDocument12 pagesRelatorio Flip-Flop - Eletrônica AnalógicaSamuelson BritoPas encore d'évaluation

- Aplicações Práticas de Eletrônica e Microcontroladores em Sistemas ComputacionaisDocument231 pagesAplicações Práticas de Eletrônica e Microcontroladores em Sistemas ComputacionaisRafael Silva100% (1)

- A Natureza da Luz: Ondas e PartículasDocument55 pagesA Natureza da Luz: Ondas e PartículasRafael SilvaPas encore d'évaluation

- Apêndice B - Expansão em Frações ParciaisDocument6 pagesApêndice B - Expansão em Frações ParciaiscarneirocassioPas encore d'évaluation

- Uma Não Tão Pequena Introdução Ao LaTeX 2EDocument155 pagesUma Não Tão Pequena Introdução Ao LaTeX 2EchagarpgPas encore d'évaluation

- Apêndice A - Tabelas para A Transformada de LaplaceDocument7 pagesApêndice A - Tabelas para A Transformada de LaplacePedro GalvaniPas encore d'évaluation

- LatexDocument41 pagesLatexFrederico Fernandes de OliveiraPas encore d'évaluation

- Introducao RNA 2006Document178 pagesIntroducao RNA 2006Rafael SilvaPas encore d'évaluation

- Aula 8 - Hierarquia de MemoriaDocument70 pagesAula 8 - Hierarquia de MemoriaRafael SilvaPas encore d'évaluation

- Aula11 - Protocolo IPDocument20 pagesAula11 - Protocolo IPRafael SilvaPas encore d'évaluation

- Função Transferência Circuitos ElétricosDocument69 pagesFunção Transferência Circuitos Elétricosnefilin28Pas encore d'évaluation

- Eng Inf Sinais ExercíciosDocument266 pagesEng Inf Sinais ExercíciosVanessa RodriguesPas encore d'évaluation

- Aula 8 - Hierarquia de MemoriaDocument70 pagesAula 8 - Hierarquia de MemoriaRafael SilvaPas encore d'évaluation

- Aula11 - Protocolo IPDocument20 pagesAula11 - Protocolo IPRafael SilvaPas encore d'évaluation

- Apêndice B - Expansão em Frações ParciaisDocument6 pagesApêndice B - Expansão em Frações ParciaiscarneirocassioPas encore d'évaluation

- Redes Neurais ArtificialDocument60 pagesRedes Neurais ArtificialFilipe MaiaPas encore d'évaluation

- BOYLESTAD, Robert NASHELSKY, Louis. - Dispositivos Eletrônicos e Teoria de Circuitos 8 Ed.Document674 pagesBOYLESTAD, Robert NASHELSKY, Louis. - Dispositivos Eletrônicos e Teoria de Circuitos 8 Ed.Rafael SilvaPas encore d'évaluation

- Cabos ÓpticosDocument20 pagesCabos ÓpticosRafael SilvaPas encore d'évaluation

- Apêndice A - Tabelas para A Transformada de LaplaceDocument7 pagesApêndice A - Tabelas para A Transformada de LaplacePedro GalvaniPas encore d'évaluation

- 08 Mod Mat Sist EletDocument12 pages08 Mod Mat Sist EletPHXNEOPas encore d'évaluation

- Pelichek DanielDocument51 pagesPelichek DanielRafael SilvaPas encore d'évaluation

- Apostila - Capítulo 01Document25 pagesApostila - Capítulo 01Rafael SilvaPas encore d'évaluation

- VHDL Códigos Eletrônica DigitalDocument6 pagesVHDL Códigos Eletrônica DigitalRafael SilvaPas encore d'évaluation

- Função Transferência Circuitos ElétricosDocument69 pagesFunção Transferência Circuitos Elétricosnefilin28Pas encore d'évaluation

- VHDL Códigos Eletrônica DigitalDocument6 pagesVHDL Códigos Eletrônica DigitalRafael SilvaPas encore d'évaluation

- Dvh-8680avbt Manual OperacissaifoDocument44 pagesDvh-8680avbt Manual OperacissaifoLuzia Aparecida Da Silva Pereira100% (1)

- Verilog - Códigos ProntosDocument4 pagesVerilog - Códigos ProntosBränn FelicisPas encore d'évaluation

- 2-Circuitos Lógicos - Parte 1-1Document25 pages2-Circuitos Lógicos - Parte 1-1Arthur MarquesPas encore d'évaluation

- Aula 3 - ContadoresDocument56 pagesAula 3 - ContadoresVerônica SantosPas encore d'évaluation

- PLC Ladder Diagram ProgrammingDocument92 pagesPLC Ladder Diagram ProgrammingPintasssPas encore d'évaluation

- Prova de Eletrônica Digital com 10 questões objetivas e avaliação discursivaDocument6 pagesProva de Eletrônica Digital com 10 questões objetivas e avaliação discursivaBya SsouzaPas encore d'évaluation

- CI discretos vs integradosDocument22 pagesCI discretos vs integradosRogério MorenoPas encore d'évaluation

- Registradores de deslocamentoDocument51 pagesRegistradores de deslocamentopriscilla.rocha716Pas encore d'évaluation

- Memória e componentes do computadorDocument14 pagesMemória e componentes do computadorJanaina SilvaPas encore d'évaluation

- Memórias RAM e ROM: tipos e funcionamentoDocument19 pagesMemórias RAM e ROM: tipos e funcionamentoHerlon Romualdo LudwigPas encore d'évaluation

- Histórico de Revisões de Produtos STEMACDocument14 pagesHistórico de Revisões de Produtos STEMACClaudesson Nascimento RodriguesPas encore d'évaluation

- Arquitetura e Organização de ComputadoresDocument3 pagesArquitetura e Organização de ComputadoresXavier JoaquimPas encore d'évaluation

- Ass UsDocument50 pagesAss UsJosival SouzaPas encore d'évaluation

- Guia sobre Hardware e SoftwareDocument4 pagesGuia sobre Hardware e SoftwareMelissa NascimentoPas encore d'évaluation

- Circuitos Integrados: Miniaturização e VantagensDocument19 pagesCircuitos Integrados: Miniaturização e VantagensMauro DominguesPas encore d'évaluation

- Teste de Avaliaçâo - TicDocument3 pagesTeste de Avaliaçâo - TiclinesbessaPas encore d'évaluation

- Aula 04 ISA MIPSDocument31 pagesAula 04 ISA MIPSPablo CarvalhoPas encore d'évaluation

- Tutorial Digital WorksDocument22 pagesTutorial Digital WorksNicolas Calheiros100% (1)

- Aula 10Document26 pagesAula 10Igor OliveiraPas encore d'évaluation

- Tudo Sobre ProcessadorDocument5 pagesTudo Sobre ProcessadorJon AraujoPas encore d'évaluation

- Sistemas Microprocessados - Lista de ExercíciosDocument2 pagesSistemas Microprocessados - Lista de ExercíciosMatheus LibórioPas encore d'évaluation

- Microcontroladores PIC18FDocument3 pagesMicrocontroladores PIC18FGielly Campos100% (1)

- Lista 1Document4 pagesLista 1wfsouza2010Pas encore d'évaluation

- Lista1 Gab PDFDocument7 pagesLista1 Gab PDFGustavo GianiniPas encore d'évaluation

- Arquitetura x86: Registradores, Barramentos e Modos de EndereçamentoDocument20 pagesArquitetura x86: Registradores, Barramentos e Modos de EndereçamentoRoberto MartinsPas encore d'évaluation

- ArqComp-UGU 40Document12 pagesArqComp-UGU 40Cesar ClaudioPas encore d'évaluation

- ProcessadorDocument10 pagesProcessadoradmorais24Pas encore d'évaluation